滤波电容的最近放置方法

fpga 滤波电容 放置原则

fpga 滤波电容放置原则

FPGA(现场可编程门阵列)是一种灵活的数字电路设备,而滤

波电容是用于滤波器电路中的元件。

在将FPGA和滤波电容结合使用时,放置原则非常重要,以确保电路性能和稳定性。

以下是关于FPGA和滤波电容放置原则的一些方面:

1. 电源噪声滤波,在FPGA电路中,电源噪声会对其性能产生

负面影响。

因此,放置滤波电容以滤除电源噪声是至关重要的。

通常,滤波电容应该被放置在FPGA芯片的电源引脚附近,以最大限度

地减少电源噪声的影响。

2. 信号完整性,FPGA通常处理高速数字信号,而滤波电容可

以帮助提高信号完整性。

在放置滤波电容时,需要考虑到信号的传

输路径和时序要求。

通常情况下,滤波电容应该尽可能靠近信号源

和接收器,以最大限度地减少信号传输过程中的干扰和失真。

3. 地线布局,良好的地线布局对于FPGA电路的性能至关重要。

滤波电容的放置应考虑到地线的布局,以确保地线回流的有效性。

通常情况下,滤波电容应该被放置在地线引脚附近,以最大限度地

减少地线回流路径的阻抗。

4. 热管理,FPGA在运行过程中会产生一定的热量,而滤波电容的放置也应考虑到热管理的因素。

确保滤波电容不会受到过热的影响,同时也要考虑到与其他热源的隔离,以防止滤波电容受到热干扰。

总的来说,FPGA和滤波电容的放置原则涉及到电源噪声滤波、信号完整性、地线布局和热管理等多个方面。

合理的放置滤波电容可以提高FPGA电路的性能和稳定性,因此在设计电路时需要综合考虑这些因素。

滤波器的安装

滤波器的安装!个人感觉比较重要!!!!!!!图片:图片:图片:图片:网上一篇论文的部分转载!滤波器的安装滤波器如果安装不适当,仍然会破坏滤波器的衰减特性。

只有恰当地安装滤波器才能获得良好的效果,一般考虑:其一,滤波器最好安装在干扰源出口处,再将干扰源和滤波器完全屏蔽起来。

如果干扰源内腔空间有限,则应在靠近干扰源电源线出口外侧,滤波器壳体与干扰源壳体应进行良好的搭接。

其二,滤波器的输入和输出线必须分开,防止输入端与输出端线路耦合,降低滤波特性,通常利用隔板或底盘来固定滤波器。

若不能实施隔离方法,则采用屏蔽引线。

其三,滤波器中电容器导线应尽量短,以防止感抗与容抗在某频率上形成谐振。

其四,滤波器接地线上有很大的短路电流,能辐射电磁干扰,要进行良好的屏蔽。

其五,焊接在同一插座上的每根导线必须进行滤波,否则会使滤波的衰减特性完全失去。

其六,管状滤波器必须完全同轴安装,使电磁干扰电流成辐射状流过滤波器。

图4演示了滤波器安装时的一种常见错误,由于滤波器的输入线过长,外面进来的干扰还没经过滤波,就已经通过空间耦合的方式干扰到线路板上。

而线路板上产生的干扰可以直接耦合到滤波器的输入线上,传导到机箱外面。

造成超标的电磁发射。

图5演示了滤波器安装时的一种常见错误,由于滤波器的输入、输出线靠的太近,高电频干扰可以通过输入、输出线之间的寄生电容直接发生耦合,旁路掉滤波器,使滤波器高频滤波效果变差。

图6演示了滤波器安装时的一种常见错误,大部分滤波器内部的共模滤波电容连接到滤波器的金属外壳上,在安装时,通过将滤波器的金属外壳直接安装在机箱上实现滤波器的接地。

在这种安装方式中,滤波器的外壳没连接到机壳上,因此对于共模滤波电容悬空,起不到滤波的作用。

图7演示了滤波器安装时的正确方式,滤波器的输入线很短,并且利用机箱将滤波器的输入端和输出端隔离开。

电源地滤波电容走线

电源地滤波电容走线

电源地滤波电容走线是电子设备中常用的一种电路设计,用于减少电源信号中的噪音和干扰。

在电子设备中,电源地滤波电容通常被放置在电源线和设备的地线之间,起到隔离和滤波的作用。

电源地滤波电容走线的设计需要考虑以下几个因素:

1. 走线路径:电源地滤波电容应尽量靠近电源输入端和设备的地线,以缩短电流回路,减少电源信号传输的路径,从而提高滤波效果。

2. 走线长度:走线长度应尽量保持短,以减少电源信号在走线中的损耗和干扰。

同时,走线应避免与其他信号线或高频信号线交叉,以减少干扰。

3. 走线材料:走线应选择低阻抗、低电感的导线材料,如铜线或银线,以减少电流回路的电阻和电感,提高滤波效果。

4. 过孔设计:在PCB板上的过孔设计也是电源地滤波电容走线的重要考虑因素之一。

过孔的位置和尺寸应合理设计,以确保电容与地线之间的连接稳定可靠。

5. 接地方式:电源地滤波电容应与设备的地线直接连接,以确保信号的有效接地和滤波效果。

接地点应选择在设备的地平面上,以减少地线的长度和电阻。

电源地滤波电容走线的设计需要综合考虑走线路径、走线长度、走

线材料、过孔设计和接地方式等因素。

合理的走线设计可以有效减少电源信号中的噪音和干扰,提高设备的性能和稳定性。

为了获得更好的滤波效果,工程师在设计电子设备时应仔细考虑电源地滤波电容走线的布局和连接方式。

这样才能确保设备在工作时能够获得稳定可靠的电源信号,提高设备的抗干扰能力和可靠性。

电磁干扰滤波电容器使用方法与作用

电磁干扰滤波电容器使用方法与作用电磁干扰是一种常见的干扰现象,长期以来一直困扰着无线通信、计算机、医疗等领域的工程师和用户。

为了降低电磁干扰的影响,工程师们常常会采用电磁干扰滤波电容器。

本文将简要介绍电磁干扰滤波电容器的使用方法和作用。

一、电磁干扰滤波电容器的概念电磁干扰滤波电容器,又称电容式噪声滤波器,是一种抑制电磁干扰的器件。

它可以将电路中不希望的高频噪声信号直接短路至地,从而有效防止噪声信号对其他电路的干扰。

二、电磁干扰滤波电容器的使用方法1、选择合适的电容值电磁干扰滤波电容器的电容值一般在几微法到数百微法之间,具体值需要根据实际电路的特点来选择。

一般来说,电路中的电容值越大,其滤波效果就越好,但是过大的电容值也会对电路产生负面影响。

2、放置位置的选择电磁干扰滤波电容器一般应放置在电源端,即电源的正电极与地之间。

如果电源只有一个极性,就只在该极性钎接电容器,如果是双极性电源,则在正负两极性钎接电容器。

3、并联电容器在某些情况下,一个电磁干扰滤波电容器可能无法完全抑制电磁干扰。

这时,可以采用并联电容器来增强滤波效果。

三、电磁干扰滤波电容器的作用1、抑制电磁干扰电磁干扰滤波电容器可以将电路中的高频噪声信号直接短路至地,从而有效抑制电磁干扰,保护其他电路的正常运行。

2、提高系统抗干扰能力电磁干扰滤波电容器用于电路设计中,可以提高系统的抗干扰能力,保证系统的稳定性和可靠性。

3、保护设备电磁干扰滤波电容器可以有效地保护设备,降低电子器件的失效率,提高设备的使用寿命。

四、总结电磁干扰滤波电容器是电路设计中常用的一种抗干扰器件。

使用时需要选择合适的电容值和放置位置,对于那些对于只通过一个电容器无法完全抑制干扰的电路,采用并联电容器可以增强滤波效果。

在实际应用中,电磁干扰滤波电容器可以抑制电磁干扰,提高系统抗干扰能力,保护设备等。

电容按键布线规则参考[new]

![电容按键布线规则参考[new]](https://img.taocdn.com/s3/m/bc8162cf4028915f804dc2cc.png)

电容按键布线规则一、布局:1.触摸通道与触控芯片、其它元件布局在不同的层。

2.触摸通道电阻尽量靠近芯片。

3.芯片大小滤波电容靠近芯片放置。

4.预留测试接口,以方便调试。

二、走线:1. 尽量把触摸通道走线放在底层,触摸通道在顶层。

2. 触摸通道、触摸通道走线与铺地之间的间距至少30mil。

3. 不要把触摸通道走线布置在触摸通道下面。

4. 触摸通道走线间距应当至少是触摸通道走线宽度的两倍。

5.时钟、数据或周期信号走线都不应该与触摸通道走线相邻平行布设。

这些信号线应当尽可能地与触摸通道走线垂直,或者布设在PCB的其他区域。

如果时钟、数据或任何周期信号走线确实需要与触摸的信号走线平行布设,它们应当被布设在不同的层并且不能重叠,而且应当尽可能地缩短信号线平行部分的长度。

6.电源走线,触摸芯片最好用一根独立的走线从板子的供电点取电,不要和其他的电路(如LED回路)共用电源回路。

触摸IC的供电从滤波电路输入,保持VDD与VSS并行,输入路径短而粗(40mil左右)。

7.采用星形接地,触摸芯片的地线不要和其他电路共用,应该单独连到板子电源输入的接地点,也就是通常说的采用“星形接地”。

8.单面板走线,如果采用单面PCB板,并用弹簧或其它导电物体做感应通道,感应通道到触控IC引脚的连线不走或少走跳线。

9.Sensor走线长度:或,这样可以减少来自射频的干扰。

10.Sensor通道电阻:500Ω~2K,起衰减共振作用。

三、铺地:1.空白的地方可以网格铺地(线宽6mil、网格大小为30mil)。

2.触摸通道正对背面稍大些面积不要铺地,如果需要在比较潮湿的环境工作时,触摸通道所在层不要铺地。

3.为降低串扰,应当尽可能地增大两个触摸通道之间的间距以及触摸通道与触摸通道走线之间的距离。

在可能的情况下,在两个触摸通道之间铺地、触摸通道走线之间加入铺地。

4.铺地被用来填充PCB的空白区域,铺地能够帮助触摸模块屏蔽外部噪声源,还能够稳定触摸线路的固有电容。

芯片IC附近为什么放0.1uF的电容?1uF不行吗?

芯片IC附近为什么放0.1uF的电容?1uF不行吗?我们在电源滤波电路上可以看到各种各样的电容,100uF、10uF、100nF、10nF不同的容值,那么这些参数是如何确定的?数字电路要运行稳定可靠,电源一定要”干净“,并且能量补充一定要及时,也就是滤波去耦一定要好。

什么是滤波去耦,简单的说就是在芯片不需要电流的时候存储能量,在需要电流的时候又能及时地补充能量。

有读者看到这里会说,这个职责不是DC/DC、LDO的吗?对,在低频的时候它们可以搞定,但高速的数字系统就不一样了。

先来看看电容,电容的作用简单来说就是存储电荷。

我们都知道在电源中要加电容滤波,在每个芯片的电源脚放置一个0.1uF的电容去耦。

但是,怎么有些板子芯片的电源脚旁边的电容是0.1uF的或者0.01uF的,有什么讲究吗?要搞懂这个道道就要了解电容的实际特性。

理想的电容它只是一个电荷的存储器,即C,而实际制造出来的电容却不是那么简单。

分析电源完整性的时候我们常用的电容模型如图1所示。

图1中,ESR是电容的串联等效电阻,ESL是电容的串联等效电感,C才是真正的理想电容。

ESR和ESL是由电容的制造工艺和材料决定的,没法消除。

那这两个东西对电路有什么影响?ESR影响电源的纹波,ESL影响电容的滤波频率特性。

我们知道:电容的容抗Zc=1/ωC电感的感抗Zl=ωL,ω=2πf实际电容的复阻抗为:Z=ESR+jωL-1/jωC=ESR+j2πf L-1/j2πf C可见,当频率很低的时候是电容起作用,而频率高到一定程度电感的作用就不可忽视了;再高的时候电感就起主导作用了,电容就失去滤波的作用了。

所以记住,高频的时候电容就不是单纯的电容了。

实际电容的滤波曲线如图2所示。

上面说了,电容的等效串联电感是由电容的制造工艺和材料决定的。

实际的贴片陶瓷电容,ESL从零点几nH到几个nH不等,封装越小ESL就越小。

从图2中看出,电容的滤波曲线并不是平坦的,它像一个’V’,也就是说有选频特性。

功放电源滤波电容接法

功放电源滤波电容接法

功放电源滤波电容的接法是为了在电源输入端对电压进行滤波和稳压,以保证功放电路正常工作。

一般来说,电源滤波电容通常会与电源输入端的正负极相连,用来平滑电源输入端的直流电压。

在实际接法中,通常会有两种情况:

1. 单端接法,在单端接法中,电容的一个端子连接到电源输入端的正极(一般是电源的正极端子),另一个端子连接到电源输入端的负极(一般是地端),这种接法适用于一些简单的功放电路,能够有效地滤除电源输入端的纹波电压。

2. 双端接法,在双端接法中,电容的两个端子分别连接到电源输入端的正负极,这种接法在一些对电源干扰要求比较高的功放电路中比较常见,能够更好地滤除电源输入端的噪声和纹波。

无论是单端接法还是双端接法,选用的电容参数需要根据功放的功率、工作电压和具体的设计要求来确定,一般来说,电容的容值越大,滤波效果越好,但是也会增加成本和体积。

此外,还需要注意电容的极性,确保连接正确,以免损坏电容或电路。

在实际接

法中,还需要考虑电容的安装方式、布局和线路走向等因素,以确保功放电源的稳定和可靠性。

PCB模块化布局---滤波电容设计

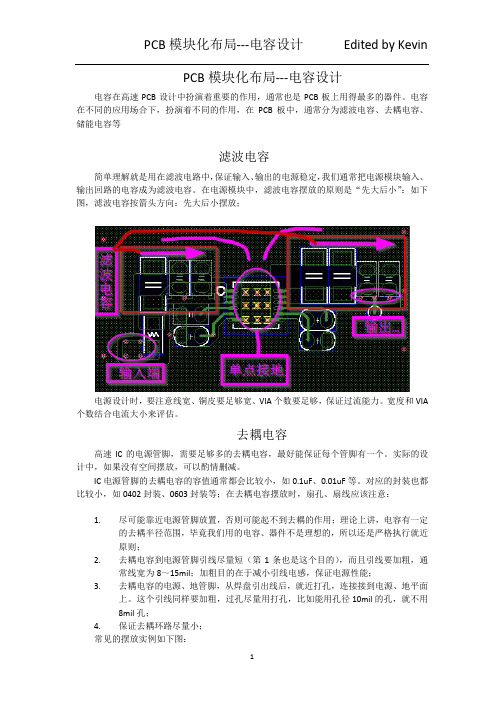

PCB模块化布局---电容设计电容在高速PCB设计中扮演着重要的作用,通常也是PCB板上用得最多的器件。

电容在不同的应用场合下,扮演着不同的作用,在PCB板中,通常分为滤波电容、去耦电容、储能电容等滤波电容简单理解就是用在滤波电路中,保证输入、输出的电源稳定,我们通常把电源模块输入、输出回路的电容成为滤波电容。

在电源模块中,滤波电容摆放的原则是“先大后小”:如下图,滤波电容按箭头方向:先大后小摆放;电源设计时,要注意线宽、铜皮要足够宽、VIA个数要足够,保证过流能力。

宽度和VIA 个数结合电流大小来评估。

去耦电容高速IC的电源管脚,需要足够多的去耦电容,最好能保证每个管脚有一个。

实际的设计中,如果没有空间摆放,可以酌情删减。

IC电源管脚的去耦电容的容值通常都会比较小,如0.1uF、0.01uF等。

对应的封装也都比较小,如0402封装、0603封装等;在去耦电容摆放时,扇孔、扇线应该注意:1.尽可能靠近电源管脚放置,否则可能起不到去耦的作用;理论上讲,电容有一定的去耦半径范围,毕竟我们用的电容、器件不是理想的,所以还是严格执行就近原则;2.去耦电容到电源管脚引线尽量短(第1条也是这个目的),而且引线要加粗,通常线宽为8~15mil;加粗目的在于减小引线电感,保证电源性能;3.去耦电容的电源、地管脚,从焊盘引出线后,就近打孔,连接接到电源、地平面上。

这个引线同样要加粗,过孔尽量用打孔,比如能用孔径10mil的孔,就不用8mil孔;4.保证去耦环路尽量小;常见的摆放实例如下图:12去耦电容和IC 在同一面 去耦电容和IC 不在同一层面去耦电容和IC 不在同一层面上图示例为SOP 封装的IC 去耦电容的摆放方式,QFP 等封装的也类似;常见的BGA 封装,其去耦电容通常放在BGA 下面,即背面。

由于BGA 封装管脚密度大,一般放的不是很多,力争多摆放一些;BGA 封装下面的去耦电容如上图示例,有时为了摆放去耦电容,可能需要移动BGA 的fanout,或者两个电源、3地管脚共用一个VIA ;储能电容它的作用就是保证IC 在用电时,能在最短的时间提供电能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

滤波电容的最近放置方法

一直想找到滤波电容的最近放置方法,但是总是没有思路,有太多标准或者观点了,下面就是其中一个我觉得还合理的,仅做参考:

两层板:

1、滤波电容和退藕电容

不管是模拟还是数字电路,电源布线时都需要一些电容。

滤波电容(也作旁路电容),放置在距离电源较近的位置,用于bypass电源位置引入的高频信号,如果不加旁路电容,高频干扰可能从电源部分引入到器件内部,通常容值为10~100uF。

退藕电容的作用对于模拟和数字电路有所不同。

模拟电路中,小容值退藕电容(0.1uF)安放在离模拟器件引脚较近的位置,其作用与上面提到的滤波电容类似。

而数字电路中,MCU等处理器附近的退藕电容在数字电路高速切换时起到缓冲电压变化的作用,否则信号电平可能不稳定。

高速数字电路(200Mhz以上),可采用较小的退藕(如0.01uF)。

2、电源的布线

两层板布电源线的过程中,必须注意VCC从电源出发走到器件并返回公共地的回路面积,越大的回路面积意味着越大的感应线圈,任何高频信号都可能造成严重的电磁干扰(EMI)。

器件的地线要尽可能的紧靠电源侧,就近回到板子的公共地(电源地)。

地平面是解决电磁干扰的好方法。

电源线电流比较大,通常应比信号线宽两至三倍。

个别过窄的电源走线都会让该处的铜皮过热。

3、模拟与数字的不同策略

PCB的模拟部分与数字部分分开,并远离地线回路,因为高阻抗的模拟线路对开关噪声的抗干扰能力很差。

4、走线

首先,所有的走线尽量的短。

切忌两层信号平行走线,平行意味着电感,模拟电路尤其注意。

走线转弯处可以采用钝角或圆弧走线,通常采用前者。

在能够布通的情况下,过孔越少越好。

每增加一个过孔就引入若干个pF的寄生电容。

总线型数字电路,各信号线长度尽可能一致,以消除信号传递延迟的时间差。

4、地线

避免采用环路地,而要采用星形拓扑结构,或走树形结构。

当然地平面是最好的。

对于数模混合电路(如A/D转换器件),电源和模拟地AGND直接连到地平面,而数字部分应当通过隔离的三态缓冲器连接到CPU等数字器件,DGND最后连到在电源处单点接地。

数模混合器件的各个电源引脚增加适当旁路电容。

5、时钟

晶振和时钟信号远离信号,附近预留铺铜空间。

同步动态内存等器件需要的SCLK等信号三倍距离远离其它信号,防止干扰。

6、布局

器件的布局对于布通率有决定性的影响。

器件摆放平衡,不要头重脚轻。

器件在二维和三维空间都不要产生冲突。

热敏元件远离发热元件,高发热的器件如功率放大器要酌情使用散热片。

接插件的摆放要考虑板子的使用需求和机械结构,过重过大的器件需可能需要物理支撑结构,可调元件须方便调节。

四层及以上PCB:

1、四层及以上PCB的电气性能越来越适应高速电路的需求,应尽可能采用贴片元件。

2、由于有了地平面和电源平面,EMI性能要比两层板好不少。

模拟部分的布线规则如上所述,这里主要是数字部分。

若PCB需要若干个不同的电源电压,需要分割电源平面。

根据个主要器件的电源引脚布局,整块分割(如1.8V和3.3V),对于BGA下方的电源平面,可采取Y字型割发,尽量减少电源跨层飞线。

3、仔细检查线宽和走线安全距离(clearance),包括过孔solder mask和电源层的power plane的clearance,咨询PCB生产厂家后定出线宽和孔径。

4、10mil以下信号线连接到接插件时建议补泪滴,可以增加机械强度。

5、过孔尽量不要放置在内层铺铜的边缘处,防止钻头打滑导致的铜皮碎裂。

6、添加适当测试点,用于调试。

电源部分增加0欧姆串联电阻,在调试无误后

接入,以防整块PCB烧毁。

7、BGA封装退藕电容放置于反面正下方,其它尽可能放置于周边,建议0402或0603封装。

8、电源层过孔(或者地层)可以采用在铜皮周围增加4角(或2角)的隔离遮挡style,即电流从四周的遮挡(不吃铜处)间隙流入过孔。

其作用一个增大阻热系数,降低因电源层迅速导热而引起的焊接难题,另一个据说是改善电源层的高频干扰问题。