EDA技术与Verilog设计第10章

edaverilog课程设计

eda verilog 课程设计一、课程目标知识目标:1. 理解EDA(电子设计自动化)的基本概念及其在电子设计中的应用;2. 掌握Verilog硬件描述语言的基本语法和使用方法;3. 学习并运用Verilog进行简单的数字电路设计与仿真。

技能目标:1. 能够运用Verilog语言编写基础的数字电路模块代码;2. 能够使用EDA工具(如ModelSim)对Verilog代码进行功能仿真和时序分析;3. 能够根据实际需求,设计简单的数字系统并进行验证。

情感态度价值观目标:1. 培养学生对电子设计自动化技术的兴趣,激发其创新意识和探索精神;2. 培养学生团队协作意识,使其在项目实践中体验到合作与交流的重要性;3. 引导学生关注我国电子设计行业的发展趋势,激发其为国家科技进步贡献力量的责任感。

课程性质分析:本课程为电子信息类专业高年级学生开设,具有较强的理论性和实践性。

通过本课程的学习,学生将掌握Verilog硬件描述语言的基本知识和技能,为后续专业课程及实际工程项目打下基础。

学生特点分析:高年级学生已具备一定的电子技术基础和编程能力,具有较强的学习能力和自主意识。

在本课程中,学生需要充分发挥自身优势,通过实践操作,提高自身在电子设计领域的综合素质。

教学要求:1. 紧密联系实际工程案例,注重理论知识与实践技能的结合;2. 采用项目驱动式教学,鼓励学生主动参与,培养其解决问题的能力;3. 注重过程评价,关注学生在课程学习中的成长和进步。

二、教学内容1. EDA与Verilog基础知识- EDA技术概述及其在电子设计中的应用- Verilog语言概述、发展历程及优势特点- 教材章节:第一章 EDA与Verilog概述2. Verilog语法基础- 数据类型、变量声明与赋值- 运算符、表达式与赋值语句- 基本结构(模块、端口、参数)- 教材章节:第二章 Verilog语法基础3. 基本数字电路设计- 组合逻辑电路设计(如编码器、译码器、多路选择器等)- 时序逻辑电路设计(如触发器、计数器、寄存器等)- 教材章节:第三章 基本数字电路设计4. Verilog仿真与验证- ModelSim工具的使用方法- 功能仿真与时序分析- 常见错误及其解决方法- 教材章节:第四章 Verilog仿真与验证5. 实践项目:数字系统设计- 项目需求分析- 设计方案与模块划分- Verilog代码编写与调试- 仿真验证与优化- 教材章节:第五章 实践项目教学内容安排与进度:1. EDA与Verilog基础知识(2课时)2. Verilog语法基础(4课时)3. 基本数字电路设计(4课时)4. Verilog仿真与验证(4课时)5. 实践项目:数字系统设计(6课时)总计:20课时。

EDA技术与Verilog_HDL

1.7 EDA技术的优势

(1)大大降低设计成本,缩短设计周期。 (2)有各类库的支持。 (3)极大地简化了设计文档的管理。 (4)日益强大的逻辑设计仿真测试技术。 (5)设计者拥有完全的自主权,再无受制于人之虞。 (6)软件平台支持任何标准化的设计语言;良好的可移植与可测试性, 为系统开发提供了可靠的保证。 (7)能将所有设计环节纳入统一的自顶向下的设计方案中。 (8)在系统板设计结束后仍可利用计算机对硬件系统进行完整的测试。

Altera 的 SignalTap II Xilinx 的 ChipScope

3.6 FPGA/CPLD产品概述

3.6.1 Lattice公司的CPLD器件系列 1. ispLSI系列器件 2. MACHXO系列 3. MACH4000系列 4. LatticeSC FPGA系列 5. LatticeECP3 FPGA系列

第3章 FPGA/CPLD结构与应用

3.1 概 述

3.1 概 述

3.1.1 可编程逻辑器件的发展历程

(1)20世纪70年代,熔丝编程的PROM和PLA器件是最早的可编程逻辑 器件。 (2)20世纪70年代末,对PLA进行了改进,AMD公司推出PAL器件。 (3)20世纪80年代初,Lattice发明电可擦写的,比PAL使用更灵活的 GAL器件。 (4)20世纪80年代中期,Xilinx公司提出现场可编程概念,生产出了世 界上第一片FPGA器件。同期,A1tera公司推出EPLD器件,较GAL器件 有更高的集成度,可以用紫外线或电擦除。 (5)20世纪80年代末,Lattice公司又提出在系统可编程技术,并且推出 了一系列具备在系统可编程能力的CPLD器件,将可编程逻辑器件的性能 和应用技术推向了一个全新的高度。 (6)进入20世纪90年代后,可编程逻辑集成电路技术进入飞速发展时期。 器件的可用逻辑门数超过了百万门,并出现了内嵌复杂功能模块(如加法 器、乘法器、RAM、CPU核、DSP核、PLL等)的SOPC。

edaverilog课程设计

eda verilog 课程设计一、课程目标知识目标:1. 学生能理解EDA(电子设计自动化)的基本概念,掌握Verilog硬件描述语言的基本语法与结构。

2. 学生能够运用Verilog语言设计简单的数字电路,并了解其仿真过程。

3. 学生了解数字电路的基本测试方法,并能够运用Verilog进行基本测试代码的编写。

技能目标:1. 学生能够使用EDA工具进行Verilog代码的编写、编译和仿真。

2. 学生通过实际操作,掌握数字电路设计中常见的模块搭建和调试技巧。

3. 学生能够通过小组合作,完成一个小型的数字系统设计项目,提高实践操作能力。

情感态度价值观目标:1. 培养学生积极探索、勤于实践的科学态度,激发学生对电子设计领域的兴趣。

2. 培养学生的团队协作精神,提高沟通与表达能力,增强解决问题的信心。

3. 通过课程学习,使学生认识到电子技术在现代社会中的重要作用,培养学生的创新意识和责任感。

二、教学内容本课程教学内容主要包括以下几部分:1. EDA与Verilog基础知识:介绍EDA的基本概念、发展历程及Verilog硬件描述语言的基本语法、结构。

- 教材章节:第一章 EDA技术概述,第二章 Verilog基础知识。

- 内容安排:讲解EDA工具的使用,Verilog基本语法、数据类型、运算符等。

2. 数字电路设计基础:学习组合逻辑电路、时序逻辑电路的设计方法,以及常用数字电路模块的Verilog描述。

- 教材章节:第三章 组合逻辑电路设计,第四章 时序逻辑电路设计。

- 内容安排:介绍组合逻辑电路与时序逻辑电路的设计原理,通过实例讲解Verilog代码编写。

3. 数字电路仿真与测试:学习数字电路的仿真方法,编写测试代码,进行功能验证。

- 教材章节:第五章 数字电路仿真,第六章 数字电路测试。

- 内容安排:讲解仿真工具的使用,编写测试代码,进行电路功能验证。

4. 实践项目:小组合作完成一个小型数字系统设计项目,包括设计、仿真、测试等环节。

《EDAVerilog语言》课件

算术运算符:+、-、*、/、% 关系运算符:==、!=、>、<、>=、<= 逻辑运算符:&&、||、! 条件运算符:?: 赋值运算符:=、+=、-=、*=、/=、%= 递增递减运算符:++、- 数组下标运算符:[] 结构成员运算符:.、-> 强制类型转换运算符:(type) 运算符优先级:算术运算符>关系运算符>逻辑运算符>赋值运算符>条件运算符>递增递减运算符>数组下标运算符>结构成员运算符

设计步骤:定 义输入输出信 号、编写处理 逻辑、仿真验

证

设计实例:FIR 滤波器、IIR滤 波器、FFT算法

等

Cadence是EDA工具的领先提供商 Verilog是Cadence支持的主要硬件描述语言之一 Cadence支持Verilog的仿真、综合和布局布线 Cadence的Verilog集成工具包括Virtuoso、Innovus和Allegro等

,

汇报人:

01

02

03

04

05

06

EDA(Electronic Design Automation): 电子设计自动化,用于设 计、验证和测试电子系统

EDA工具:包括电路设计、 仿真、验证、布局布线等工 具

EDA技术发展:从手工设计 到自动化设计,提高了设计 效率和质量

Verilog语言:硬件描述语言, 用于描述数字电路和系统

Verilog语言特点:易于理解 和使用,支持层次化设计, 支持仿真和验证

Verilog语言应用:广泛应用 于芯片设计、FPGA设计和系 统级设计

什么是Verilog语言:一种硬件描述语言, 用于描述数字电路和系统

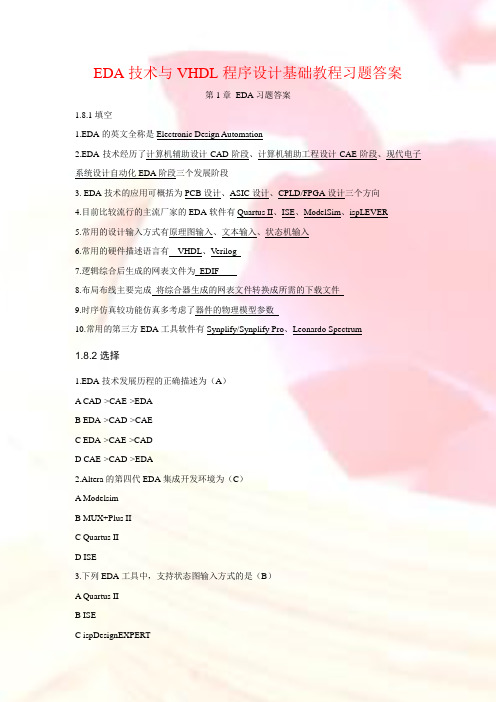

EDA 技术与 VHDL 程序设计基础教程习题答案

2.Altera的第四代EDA集成开发环境为(C)

A Modelsim

B MUX+Plus II

C Quartus II

D ISE

3.下列EDA工具中,支持状态图输入方式的是(B)

A Quartus II

B ISE

C ispDesignEXPERT

D Syplify Pro

D Cyclone

7.下列配置方式不属于FPGA配置模式的是(D)

A主动串行配置模式

B被动串行配置模式

C主动并行配置模式

D被动从属配置模式

8.下列因素中通常不属于CPLD/FPGA选型条件的是(D)

A逻辑资源

B功耗和封装

C价格和速度

D产地

2.8.3

1.结合本章学习的知识,简述CPLD的基本结构?

答:虽然CPLD种类繁多、特点各异,共同之处总结起来可以概括为三个部分:

配置与绕线(Place and Routing)

绕线后的电路功能验证(Post Layout Verification)

8.为什么要进行硬件电路的后仿真验证和测试?

答:后仿真考虑了实际器件的模型参数,能够更好的模拟实际电路工作状态。测试是检验设计合格的最直接的方式。

第2章EDA习题答案

2.8.1

1.可编程逻辑器件的英文全称是Programmable Logic Device

4.目前比较流行的主流厂家的EDA软件有Quartus II、ISE、ModelSim、ispLEVER

5.常用的设计输入方式有原理图输入、文本输入、状态机输入

6.常用的硬件描述语言有VHDL、Verilog

7.逻辑综合后生成的网表文件为EDIF

EDA技术及应用—基于FPGA的电子系统设计:基于Verilog hdl的数字电路设计

10100

1111

15

10101

8421BC 余三码 D码

0000

0011

0001

0100

0010

0101

0011

0110

0100

0111

0101

1000

0110

1001

0111

1010

1000

1011

1001

1100

-

-

-

-

-

-

-

-

-

-

-

-

4位格雷码

0000 0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1010 1011 1001 1000

4'b0011:a_to_g=7'b1111001; //显示3

4'b0100:a_to_g=7'b0110011; //显示4

4'b0101:a_to_g=7'b1011011; //显示5

4'b0110:a_to_g=7'b1011111; //显示6

4'b0111:a_to_g=7'b1110000; //显示7

4: y= {d[2:0],d[3]}; // rol

5: y= {d[3],d[3:1]}; // asr

6: y= {d[1:0],d[3:2]}; // ror2

7: y= d;

// noshift

default: y = d;

图6-2 基本门电路仿真结果

综合结果如图6-3所示。

图6-3 基本门电路综合结果

2、 三态逻辑电路

verilogeda课程设计

verilog eda课程设计一、教学目标本课程的教学目标是使学生掌握Verilog EDA的基本知识和技能,能够运用Verilog进行数字电路的设计和仿真。

具体目标如下:1.理解Verilog语言的基本语法和结构。

2.掌握Verilog中的数据类型、运算符和表达式。

3.学习Verilog中的模块、端口和实例化。

4.理解Verilog中的线(wire)、寄存器(reg)和参数(parameter)。

5.学习Verilog中的逻辑门、触发器和组合逻辑电路的建模。

6.掌握Verilog中的时序逻辑电路的建模和仿真。

7.学习Verilog中的任务和函数的使用。

8.理解Verilog中的仿真测试和调试方法。

9.能够使用Verilog编辑器和仿真工具进行代码编写和仿真。

10.能够独立设计简单的数字电路,并使用Verilog进行建模和仿真。

11.能够分析Verilog代码的性能和资源消耗。

12.能够对Verilog代码进行调试和优化。

情感态度价值观目标:1.培养学生的创新意识和团队合作精神。

2.培养学生的自主学习能力,提高他们对新技术的敏感度和接受能力。

3.培养学生对EDA工具的兴趣,使他们认识到Verilog在数字电路设计中的重要性。

二、教学内容本课程的教学内容主要包括Verilog语言的基本语法、数据类型、运算符和表达式,模块、端口和实例化,线(wire)、寄存器(reg)和参数(parameter),逻辑门、触发器和组合逻辑电路的建模,时序逻辑电路的建模和仿真,任务和函数的使用,以及仿真测试和调试方法。

具体安排如下:1.Verilog语言的基本语法和结构。

2.数据类型、运算符和表达式的使用。

3.模块、端口和实例化的概念和应用。

4.线(wire)、寄存器(reg)和参数(parameter)的定义和使用。

5.逻辑门、触发器和组合逻辑电路的建模方法。

6.时序逻辑电路的建模和仿真技术。

7.任务和函数的编写和使用。

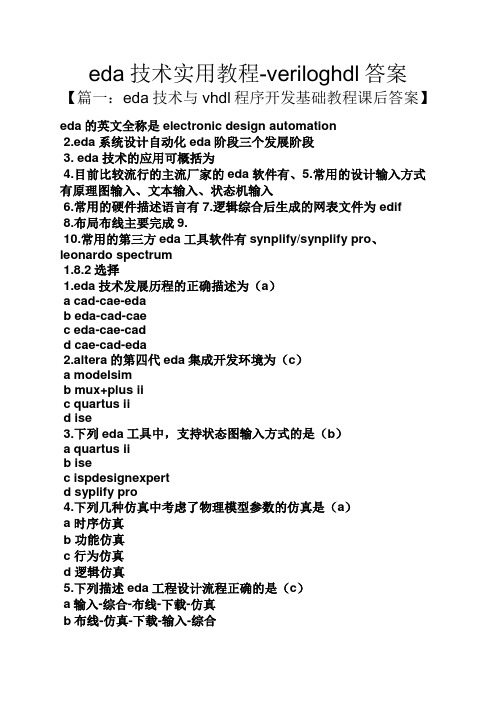

eda技术实用教程-veriloghdl答案

eda技术实用教程-veriloghdl答案【篇一:eda技术与vhdl程序开发基础教程课后答案】eda的英文全称是electronic design automation2.eda系统设计自动化eda阶段三个发展阶段3. eda技术的应用可概括为4.目前比较流行的主流厂家的eda软件有、5.常用的设计输入方式有原理图输入、文本输入、状态机输入6.常用的硬件描述语言有7.逻辑综合后生成的网表文件为 edif8.布局布线主要完成9.10.常用的第三方eda工具软件有synplify/synplify pro、leonardo spectrum1.8.2选择1.eda技术发展历程的正确描述为(a)a cad-cae-edab eda-cad-caec eda-cae-cadd cae-cad-eda2.altera的第四代eda集成开发环境为(c)a modelsimb mux+plus iic quartus iid ise3.下列eda工具中,支持状态图输入方式的是(b)a quartus iib isec ispdesignexpertd syplify pro4.下列几种仿真中考虑了物理模型参数的仿真是(a)a 时序仿真b 功能仿真c 行为仿真d 逻辑仿真5.下列描述eda工程设计流程正确的是(c)a输入-综合-布线-下载-仿真b布线-仿真-下载-输入-综合c输入-综合-布线-仿真-下载d输入-仿真-综合-布线-下载6.下列编程语言中不属于硬件描述语言的是(d)a vhdlb verilogc abeld php1.8.3问答1.结合本章学习的知识,简述什么是eda技术?谈谈自己对eda技术的认识?答:eda(electronic design automation)工程是现代电子信息工程领域中一门发展迅速的新技术。

2.简要介绍eda技术的发展历程?答:现代eda技术是20世纪90年代初从计算机辅助设计、辅助制造和辅助测试等工程概念发展而来的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

//输入数据锁存

两级流水实现的8位加法器

module adder_pipe2(cout,sum,ina,inb,cin,clk); input[7:0] ina,inb; input cin,clk; output[7:0] sum; output cout;reg cout; reg[7:0] sum; reg[3:0] tempa,tempb,firsts; reg firstc; always @(posedge clk) begin {firstc,firsts}=ina[3:0]+inb[3:0]+cin; tempa=ina[7:4]; tempb=inb[7:4];end always @(posedge clk) begin {cout,sum[7:4]}=tempa+tempb+firstc; sum[3:0]=firsts; end endmodule

begin state<=s0; z<=0; end state<=s4; z<=1; end

state<=s0;

基于状态机的设计要点

1.起始状态的选择 起始状态是指电路复位后所处的状态,选择一个合理的起 始状态将使整个系统简洁高效。有的EDA软件会自动为基 于状态机的设计选择一个最佳的起始状态。 2.状态编码 状态编码主要有二进制编码、格雷编码和一位独热编码等方 式。 ◆二进制编码(Binary State Machine) ◆格雷编码(Gray Code State Machine) ◆一位热码编码(One-Hot State Machine Encoding) 一位热码编码即采用n位(或n个触发器)来编码具有n个状 态的状态机。比如对于state0、state1、state2、state3 四个 状态可用码字1000、0100、0010、0001来代表。

第10章 设计的优化

第10章 设计的优化

10.1 设计的可综合性

10.2 流水线设计技术

主要 内容 10.3 资源共享

10.4 有限状态机设计

10.5 多层次结构电路的设计 10.6 进程 10.7 阻塞赋值与非阻塞赋值 10.8 FPGA设计中毛刺的消除

10.1 设计的可综合性

用FPGA/CPLD器件实现的设计中,综合就是将Verilog或 VHDL语言描述的行为级或功能级电路模型转化为RTL级功 能块或门级电路网表的过程

流水线设计的代价是增加了寄存器逻辑,增加了芯 片资源的耗用。

流水线操作的概念

如某个复杂逻辑功能的实现需较长的延时,可将其分解为几 个(如3个)步骤来实现,每一步的延时变小,在各步间加 入寄存器,以暂存中间结果,这样可大大提高整个系统的最 高工作频率。

流水线操作的概念示意图

非流水线方式实现的8位全加器

2个选择器和1个加法器的实现方式

资源共享

器件资源的消耗对比

资源共享

结 论

方式一需要2个加法器,而方式二通过增加一个MUX,共享 一个加法器,由于加法器耗用的资源比MUX更多,因此方式 二更节省资源。所以在电路设计中,应尽可能使硬件代价高的 功能模块资源共享,从而降低整个系统的成本。

10.4 有限状态机(FSM)设计

有限状态机设计

“1111”序列检测器状态转换图

“1111”序列检测器的Verilog描述

module fsm_seq(x,z,clk,reset,state); input x,clk,reset; output z; output[2:0] state; reg[2:0] state; reg z; parameter s0='d0,s1='d1,s2='d2,s3='d3,s4='d4; always @(posedge clk) begin if(reset) begin state<=s0;z<=0; end else casex(state) s0: begin if(x==0) begin state<=s0; z<=0; end else begin state<=s1; z<=0; end end s1: begin if(x==0) begin else begin end s2: if(x==0) begin else begin end s3: if(x==0) begin else begin end s4: if(x==0) begin else begin end default: endcase end endmodule state<=s0; z<=0; end state<=s2; z<=0; end begin state<=s0; z<=0; end state<=s3; z<=0; end begin state<=s0; z<=0; end state<=s4; z<=1; end

四级流水线实现的8位加法器

module pipeline(cout,sum,ina,inb,cin,clk); output[7:0] sum;output cout; input[7:0] ina,inb;input cin,clk; reg[7:0] tempa,tempb,sum; reg tempci,firstco,secondco,thirdco, cout; reg[1:0] firsts, thirda,thirdb; reg[3:0] seconda, secondb, seconds; reg[5:0] firsta, firstb, thirds; always @(posedge clk) begin tempa=ina; tempb=inb; tempci=cin; end //输入数据缓存 always @(posedge clk) begin {firstco,firsts}=tempa[1:0]+tempb[1:0]+tempci; //第一级加(低2位) firsta=tempa[7:2]; firstb=tempb[7:2]; //未参加计算的数据缓存 end always @(posedge clk) begin {secondco,seconds}={firsta[1:0]+firstb[1:0]+firstco,firsts}; //第二级加(第2、3位相加) seconda=firsta[5:2]; secondb=firstb[5:2]; //数据缓存 end always @(posedge clk) begin {thirdco,thirds}={seconda[1:0]+secondb[1:0]+secondco,seconds}; //第三级加(第4、5位相加) thirda=seconda[3:2];thirdb=secondb[3:2]; //数据缓存 end always @(posedge clk) begin {cout,sum}={thirda[1:0]+thirdb[1:0]+thirdco,thirds}; //第四级加(高两位相加) end endmodule

设计综合到不同器件的最高工作频率

10.3 资源共享(Resource Sharing)

尽量减少系统所耗用的器件资源也是我们进行电路设计时所追求的目标 ,在这方面,资源共享是一个较好的方法,尤其是将一些耗用资源较多 的模块进行共享,能有效降低整个系统耗用的资源。

module resource1(sum,a,b,c,d,sel); parameter size=4; output[size:0] sum; input sel; input[size-1:0] a,b,c,d; reg[size:0] sum; always @(a or b or c or d or sel) begin if(sel) sum=a+b; else sum=c+d; end endmodule

基于状态机的设计要点

状态编码的定义方式2:用'define语句定义 'define state1 2'b00 //不要加分号“;” 'define state2 2'b01 'define state3 2'b11 'define state4 2'b10 case(state) 'state1: …; //调用,不要漏掉符号“'” 'state2: …; …… 4.状态转换的描述 一般使用case语句来描述状态之间的转换,用case语句表述比 用if-else语句更清晰明了。

10.2 流水线设计(Pipeline Design)技术

流水线设计是经常用于提高所设计系统运行速度的 一种有效的方法。为了保障数据的快速传输,必须 使系统运行在尽可能高的频率上,但如果某些复杂 逻辑功能的完成需要较长的延时,就会使系统难以 运行在高的频率上,在这种情况下,可使用流水线 技术,即在长延时的逻辑功能块中插入触发器,使 复杂的逻辑操作分步完成,减小每个部分的延时, 从而使系统的运行频率得以提高。

综合

可综合的设计中应注意

不使用初始化语句;不使用带有延时的描述;不使用循环 次数不确定的循环语句。 应尽量采用同步方式设计电路。 用always过程块描述组合逻辑,应在敏感信号列表中列出 块中出现的所有输入信号。 所有的内部寄存器都应该能够被复位,在使用FPGA实现 设计时,应尽量使用器件的全局复位端作为系统总的复位 ,用器件的全局时钟端作为系统外部时钟输入端。 在Verilog模块中,任务(task)通常被综合成组合逻辑的 形式;每个函数(function)在调用时通常也被综合资源共享

module resource2(sum,a,b,c,d,sel); parameter size=4; output[size-1:0] sum; input sel; input[size-1:0] a,b,c,d; reg[size-1:0] atemp,btemp; reg[size:0] sum; always @(a or b or c or d or sel) begin if(sel) begin atemp=a;btemp=b;end else begin atemp=c;btemp=d;end sum=atemp+btemp; end endmodule