FPGA入门教程

《FPGA入门学习》课件

LED闪烁设计

总结词

通过LED闪烁设计,掌握FPGA的基本控制功能和数字逻辑设计。

详细描述

LED闪烁设计是FPGA入门学习的基本项目之一,通过该设计,学习者可以了解FPGA的基本控制功能 ,掌握数字逻辑设计的基本原理和方法。LED闪烁设计通常涉及到LED灯的驱动和控制,需要学习者 掌握基本的数字逻辑门电路和时序控制。

FPGA具有并行处理和高速计算的优点,适 用于数字信号处理中的实时信号处理和算 法加速。

数字滤波器设计

频谱分析和正交变换

FPGA可以实现高性能的数字滤波器,如 FIR滤波器和IIR滤波器,用于信号降噪和特 征提取。

FPGA可以高效地实现FFT等正交变换算法 ,用于频谱分析和信号频率成分的提取。

图像处理应用

优化设计技巧

时序优化

讲解如何通过布局布线、时序分析等手段优化 FPGA设计,提高时序性能。

资源共享

介绍如何通过资源共享减少FPGA资源占用,提 高设计效率。

流水线设计

讲解如何利用流水线设计技术提高系统吞吐量。

硬件仿真与调试技术

仿真工具使用

介绍常用HDL仿真工具(如ModelSim)的使用方法 。

03

CATALOGUE

FPGA开发实战

数字钟设计

总结词

通过数字钟设计,掌握FPGA的基本开发流程和硬件描述语言的应用。

详细描述

数字钟设计是FPGA入门学习的经典项目之一,通过该设计,学习者可以了解FPGA开 发的基本流程,包括设计输入、综合、布局布线、配置下载等。同时,数字钟设计也涉 及到硬件描述语言(如Verilog或VHDL)的应用,学习者可以掌握基本的逻辑设计和

基础语言。

FPGA开发流程

FPGA入门培训教材共45张PPT课件

# STEP#4: run router, report actual utilization and timing, write checkpoint design, run drc, write verilog and xdc out route_design write_checkpoint -force $outputDir/post_route report_timing_summary -file $outputDir/post_route_timing_summary.rpt report_timing -sort_by group -max_paths 100 -path_type summary -file $outputDir/post_route_timing.rpt report_clock_utilization -file $outputDir/clock_util.rpt report_utilization -file $outputDir/post_route_util.rpt report_power -file $outputDir/post_route_power.rpt report_drc -file $outputDir/post_imp_drc.rpt write_verilog -force $outputDir/bft_impl_netlist.v write_xdc -no_fixed_only -force $outputDir/bft_impl.xdc

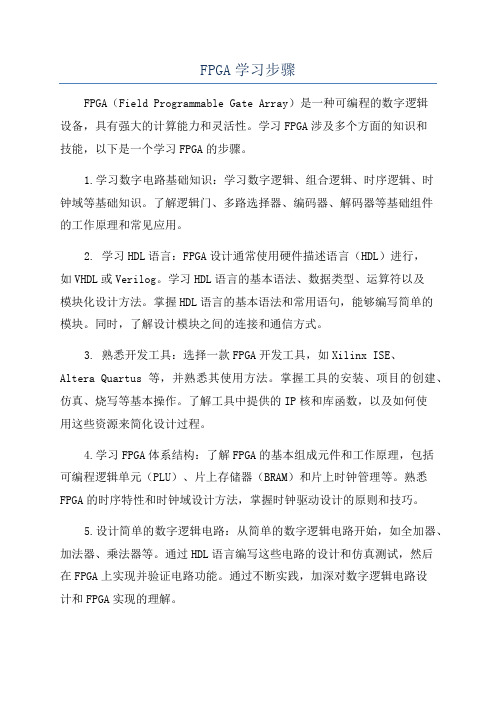

FPGA学习步骤

FPGA学习步骤FPGA(Field Programmable Gate Array)是一种可编程的数字逻辑设备,具有强大的计算能力和灵活性。

学习FPGA涉及多个方面的知识和技能,以下是一个学习FPGA的步骤。

1.学习数字电路基础知识:学习数字逻辑、组合逻辑、时序逻辑、时钟域等基础知识。

了解逻辑门、多路选择器、编码器、解码器等基础组件的工作原理和常见应用。

2. 学习HDL语言:FPGA设计通常使用硬件描述语言(HDL)进行,如VHDL或Verilog。

学习HDL语言的基本语法、数据类型、运算符以及模块化设计方法。

掌握HDL语言的基本语法和常用语句,能够编写简单的模块。

同时,了解设计模块之间的连接和通信方式。

3. 熟悉开发工具:选择一款FPGA开发工具,如Xilinx ISE、Altera Quartus等,并熟悉其使用方法。

掌握工具的安装、项目的创建、仿真、烧写等基本操作。

了解工具中提供的IP核和库函数,以及如何使用这些资源来简化设计过程。

4.学习FPGA体系结构:了解FPGA的基本组成元件和工作原理,包括可编程逻辑单元(PLU)、片上存储器(BRAM)和片上时钟管理等。

熟悉FPGA的时序特性和时钟域设计方法,掌握时钟驱动设计的原则和技巧。

5.设计简单的数字逻辑电路:从简单的数字逻辑电路开始,如全加器、加法器、乘法器等。

通过HDL语言编写这些电路的设计和仿真测试,然后在FPGA上实现并验证电路功能。

通过不断实践,加深对数字逻辑电路设计和FPGA实现的理解。

6.学习FPGA高级应用:掌握FPGA高级应用的设计方法,如时序逻辑设计、状态机设计、数据通路设计等。

了解时分复用(TDM)、频分复用(FDM)、空分复用(SDM)等常用数据传输方式的原理。

学习高级FPGA设计技术,如流水线设计、多周期设计、并行设计等。

7.学习FPGA外设接口:了解FPGA的外设接口标准,如UART、SPI、I2C、PCIe等,以及各种外设的工作原理和接口电路设计。

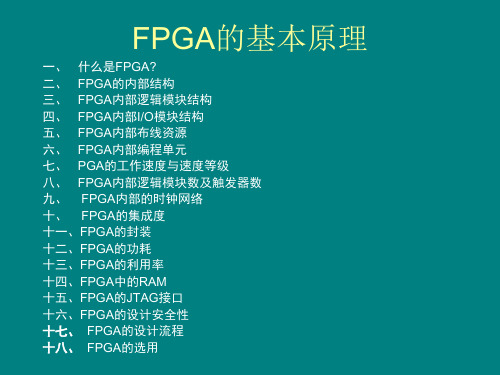

FPGA的基本原理(详细+入门)

门阵等效门:一个门阵等效门定义为一个两输入端的“与非”门。 系统门:是芯片上门的总数,是厂家指定给器件的一个门数。

十一、FPGA的封装

1、引脚数:FPGA芯片总的引脚数。 2、用户I/O数:指除了电源引脚、特殊功能引脚外的引脚,这些引脚可根据用户的需要进行配置。 3、 I/O驱动电流:8mA 或10mA。 4、时钟网络数:FPGA芯片可能包含1个、2个或4个时钟网络。 5、封装:PLCC,PQFP,CPGA等封装形式。 6、工作温度范围:FPGA芯片一般有商用、工业用及军用等不同的工作温度范围。 7、工作环境:一般分普通工作环境和航天工作环境。

ACT1模块是如何实现三输入与门的?

2、查表型FPGA结构 两输入与门: 4 X 1 RAM 表:

A

B

C

0

0

0

0

1

0

1

0

0

1

1

1

A1

A0

(二)、 什么是FPGA? FPGA是英语(Field programmable Gate Array)的缩写,即现场可编程门阵。它的结构类似于掩膜可编程门阵(MPGA),由可编程逻辑功能块和可编程I/O模块排成阵列组成,并由可编程的内部连线连接这些逻辑功能块和I/O模块来实现不同的设计。 1、FPGA与MPGA的区别: MPGA利用集成电路制造过程进行编程来形成金属互连,而FPGA利用可编程的电子开关实现逻辑功能和互连。 2、FPGA与CPLD的区别: 1) 结构不同:FPGA是由可编程的逻辑模块、可编程的分段互连线和I/O模块组成,而CPLD是由逻辑阵列块、可编程连线阵列和I/O模块组成。 2) CPLD延时可预测(Predictable),FPGA的延时与布局布线情况有关。 3) CPLD 组合逻辑多而触发器较少,而FPGA触发器多。

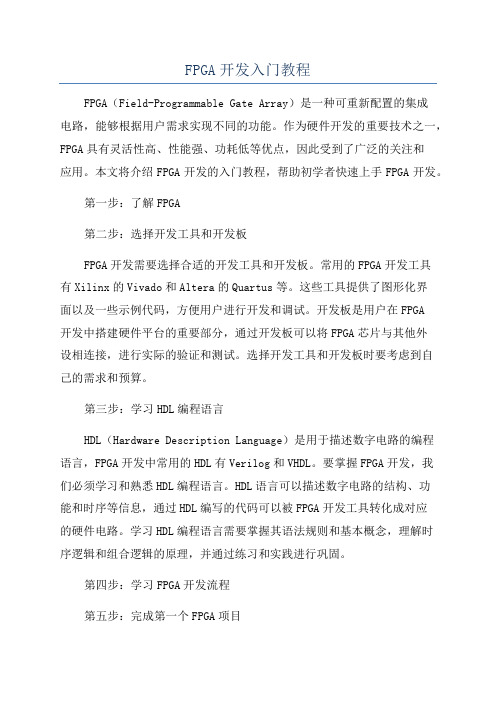

FPGA开发入门教程

FPGA开发入门教程FPGA(Field-Programmable Gate Array)是一种可重新配置的集成电路,能够根据用户需求实现不同的功能。

作为硬件开发的重要技术之一,FPGA具有灵活性高、性能强、功耗低等优点,因此受到了广泛的关注和应用。

本文将介绍FPGA开发的入门教程,帮助初学者快速上手FPGA开发。

第一步:了解FPGA第二步:选择开发工具和开发板FPGA开发需要选择合适的开发工具和开发板。

常用的FPGA开发工具有Xilinx的Vivado和Altera的Quartus等。

这些工具提供了图形化界面以及一些示例代码,方便用户进行开发和调试。

开发板是用户在FPGA开发中搭建硬件平台的重要部分,通过开发板可以将FPGA芯片与其他外设相连接,进行实际的验证和测试。

选择开发工具和开发板时要考虑到自己的需求和预算。

第三步:学习HDL编程语言HDL(Hardware Description Language)是用于描述数字电路的编程语言,FPGA开发中常用的HDL有Verilog和VHDL。

要掌握FPGA开发,我们必须学习和熟悉HDL编程语言。

HDL语言可以描述数字电路的结构、功能和时序等信息,通过HDL编写的代码可以被FPGA开发工具转化成对应的硬件电路。

学习HDL编程语言需要掌握其语法规则和基本概念,理解时序逻辑和组合逻辑的原理,并通过练习和实践进行巩固。

第四步:学习FPGA开发流程第五步:完成第一个FPGA项目通过以上几个步骤的学习和实践,我们已经具备了进行FPGA开发的基本能力。

接下来我们可以尝试完成一个简单的FPGA项目,例如实现一个LED闪烁的功能。

我们可以使用HDL语言编写一个简单的计数器,将计数值输出到FPGA开发板上的LED灯,通过改变计数值的频率实现LED的闪烁。

完成这个项目可以加深对FPGA开发流程的理解,并为后续更复杂的项目奠定基础。

总结FPGA开发入门需要掌握FPGA的基本概念和工作原理,选择合适的开发工具和开发板,学习HDL编程语言,了解FPGA开发流程,并通过实践完成一个简单的FPGA项目。

怎么学习FPGA?菜鸟学习FPGA的步骤

怎么学习FPGA?菜鸟学习FPGA的步骤一、入门首先要掌握HDL(HDL=verilog+VHDL)。

第一句话是:还没学数电的先学数电。

然后你可以选择verilog或者VHDL,有C语言基础的,建议选择VHDL。

因为verilog太像C 了,很容易混淆,最后你会发现,你花了大量时间去区分这两种语言,而不是在学习如何使用它。

当然,你思维能转得过来,也可以选verilog,毕竟在国内verilog用得比较多。

接下来,首先找本实例抄代码。

抄代码的意义在于熟悉语法规则和编译器(这里的编译器是硅编译器又叫综合器,常用的编译器有:Quartus、ISE、Vivado、Design Compiler 、Synopsys的VCS、iverilog、LatTIce的Diamond、Microsemi/Actel的Libero、Synplify pro),然后再模仿着写,最后不看书也能写出来。

编译完代码,就打开RTL图,看一下综合出来是什么样的电路。

HDL是硬件描述语言,突出硬件这一特点,所以要用数电的思维去思考HDL,而不是用C语言或者其它高级语言,如果不能理解这句话的,可以看《什么是硬件以及什么是软件》。

在这一阶段,推荐的教材是《Verilog传奇》、《Verilog HDL高级数字设计》或者是《用于逻辑综合的VHDL》。

不看书也能写出个三段式状态机就可以进入下一阶段了。

此外,你手上必须准备Verilog或者VHDL的官方文档,《verilog_IEEE官方标准手册-2005_IEEE_P1364》、《IEEE Standard VHDL Language_2008》,以便遇到一些语法问题的时候能查一下。

二、独立完成中小规模的数字电路设计。

现在,你可以设计一些数字电路了,像交通灯、电子琴、DDS等等,推荐的教材是《Verilog HDL应用程序设计实例精讲》。

在这一阶段,你要做到的是:给你一个指标要求或者时序图,你能用HDL设计电路去实现它。

FPGA入门教程_ALTERA_Quartus_II__和_XILINX___ISE_CPLD入门教程_教案_VHDL_Verilog_例程讲解

2011-8

FPGA介绍

何为FPGA?

FPGA(Field-Programmable Gate Array),即现 场可编程门阵列,它是在PAL、GAL、CPLD等可编 程器件的基础上进一步发展的产物。它是作为专用 集成电路(ASIC)领域中的一种半定制电路而出现 的,既解决了定制电路的不足,又克服了原有可编 程器件门电路数有限的缺点

Verilog HDL 的抽象级别

语言本身提供了各种层次抽象的表述,可以用详细 程度有很大差别的的多层次模块组合来描述一个 电路系统。 行为级:技术指标和算法的Verilog描述 RTL关级:具体的晶体管物理器件的描述

Verilog HDL 的抽象级别

设计复杂数字系统的工具 和手段

两种硬件描述语言 : Verilog VHDL

有哪几种硬件描述语言? 各有什么特点?

Verilog HDL - 较多的第三方工具的支持 - 语法结构比VHDL简单 - 学习起来比VHDL容易 - 仿真工具比较好使 - 测试激励模块容易编写

Verilog HDL 的发展历史

两者建模能力的比较

行为级 的抽象

系统级

SystemVerilo g

算法级

VHDL Verilog

寄存器传输级

逻辑门级 VITAL

开关电路级

VerilogHDL 与 VHDL 建 模 能 力 的 比 较

Verilog HDL有什么用处?

在各种抽象层次上描述数字电路

测试各种层次数字电路的行为 设计出正确有效的复杂电路结构

数字信号处理系统的实现

非实时系统: 通用的计算机和利用通用计算机改装的设备,主要 工作量是编写 “C” 程序。输入/输出数据大多为文 本 。 实时系统: 信号处理专用的微处理器为核心的设备,主要工作 量是编写汇编程序。输入/输出数据大多为数据流, 直接用于控制 。

FPGA入门教程

FPGA入门教程1.数字电路设计入门2.FPGA简介3.FPGA开发流程4.RTL设计5.QuartusⅡ设计实例6. ModelSim和Testbench1.数字电路设计入门1.1数字电路设计数字电路设计的核心是逻辑设计。

通常,数字电路的逻辑值只有‘1’和‘0’,表征的是模拟电压或电流的离散值,一般‘1’代表高电平,‘0’代表低电平。

高低电平的含义可以理解为,存在一个判决电平,当信号的电压值高于判决电平时,我们就认为该信号表征高电平,即为‘1’。

反之亦然。

当前的数字电路中存在许多种电平标准,比较常见的有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVDS、HSTL、SSTL等。

这些电平的详细指标请见《补充教程1:电平标准》。

数字电路设计大致可分为组合逻辑电路和时序逻辑电路。

一般的数字设计的教材中对组合逻辑电路和时序逻辑电路的定义分别为:组合逻辑电路的输出仅与当前的输入有关,而时序逻辑电路的输出不但与输入有关,还和系统上一个状态有关。

但是在设计中,我们一般以时钟的存在与否来区分该电路的性质。

由时钟沿驱动工作的电路为时序逻辑电路。

大家注意,这两种电路并不是独立存在的,他们相互交错存在于整个电路系统的设计中。

1.1.1组合逻辑电路组合逻辑电路由任意数目的逻辑门电路组成,一般包括与门、或门、非门、异或门、与非门、或非门等。

一般的组合逻辑电路如下图:其中A,B,C,D,E,F为输入,G为输出。

1.1.2时序逻辑电路时序逻辑电路由时钟的上升沿或下降沿驱动工作,其实真正被时钟沿驱动的是电路中的触发器(Register),也称为寄存器。

触发器的工作原理和参数如下图:下面是两个简单的时序逻辑电路例子:(1)、时钟分频电路该时序电路的功能为实现对时钟’clk’的4分频,其中’clk_2’为2分频时钟,’clk_4’为4分频时钟,’enable’为该电路的使能信号。

其功能仿真波形如下图所示:(2)、序列检测器该时序电路实现了一个序列检测器,当输入序列‘datain’中出现‘101’时,标志位F将输出‘1’,其他时刻输出‘0’。