CPLD入门教程

5分钟学会使用CPLD

5分钟学会使用CPLD当今社会,随着电子行业的发展,大规模集成电路的运用越来越普遍,用CPLD/FPGA 来开发新产品是当前很多实际情况的需求。

在此本人结合到自己的所学,利用业余时间草写了一个简单的使用说明,不要求有丰富经验的大虾来驻足观望,只希望对吾辈刚入门的菜鸟们起到一个抛砖引玉的作用。

由于水平有限,文中错误在所难免,望各位提出宝贵的意见。

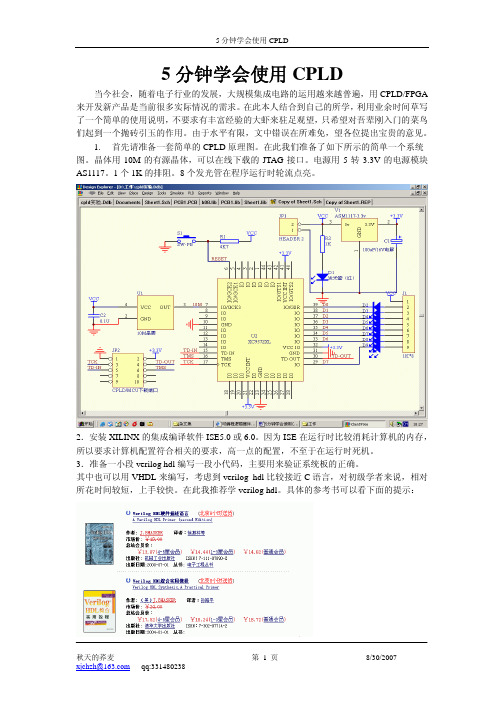

1.首先请准备一套简单的CPLD原理图。

在此我们准备了如下所示的简单一个系统图。

晶体用10M的有源晶体,可以在线下载的JTAG接口。

电源用5转3.3V的电源模块AS1117。

1个1K的排阻。

8个发光管在程序运行时轮流点亮。

2.安装XILINX的集成编译软件ISE5.0或6.0。

因为ISE在运行时比较消耗计算机的内存,所以要求计算机配置符合相关的要求,高一点的配置,不至于在运行时死机。

3.准备一小段verilog hdl编写一段小代码,主要用来验证系统板的正确。

其中也可以用VHDL来编写,考虑到verilog hdl比较接近C语言,对初级学者来说,相对所花时间较短,上手较快。

在此我推荐学verilog hdl。

具体的参考书可以看下面的提示:4.此我们用下面的一小段代码作为范例:其功能是驱动8个发光管轮流点亮,因为是采用了10M频率晶体的边沿触发,所以速度很快,为了使我们肉眼能够看的清楚其工作的流程,我们在里面安放了一个计数器,计数器计每次满一次就点亮一个发光管,依次类推。

其源程序如下:/* 流水灯的Verilog-HDL描述 */module LEDWATER(reset,CLK,LED);input reset, CLK;output [7:0] LED;[7:0]LED;//=8'b11111111;regreg [17:0] buffer;//=0;exchange;regalways@(posedge CLK)if(reset==0) //如果复位了就熄灭全部的灯beginLED=8'b1111_1111;buffer=0;exchange=0;endelsebeginif(exchange==0)begin+1);buffer=(buffer17'b111111111111111111111111)==if(bufferbeginbuffer=0;LED=(LED-1);if(LED==8'b0000_0000)beginLED=8'b1111_1111;exchange=1;endendendif(exchange==1)beginbuffer=(buffer+1);==buffer17'b111111111111111111111111)(ifbeginbuffer=0;LED=(LED>>1);if(LED==8'b00000000)beginLED=8'b1111_1111;exchange=0;endendendendendmodule注意:VERILOG HDL的代码编写风格,begin end 代替了C语言中的大括号{}。

cpld语法-概述说明以及解释

cpld语法-概述说明以及解释1.引言1.1 概述概述:CPLD(Complex Programmable Logic Device)是一种集成电路器件,具有可编程逻辑功能。

它的特点在于其内部包含大量可编程逻辑单元(如门阵列、触发器等),可以根据用户的需求进行编程,实现各种逻辑功能。

CPLD的灵活性和可编程性使其在数字电路设计领域得到广泛应用。

本文将重点介绍CPLD的编程语法,通过学习CPLD的编程语法,读者可以更好地理解和应用CPLD技术,提升自己的电路设计能力和实践经验。

1.2 文章结构本文将分为引言、正文和结论三个部分来逐步展开关于CPLD语法的介绍和讨论。

在引言部分中,我们将简要概述CPLD语法的重要性,并介绍文章的结构和目的。

接着,在正文部分,我们将首先介绍CPLD的定义与特点,然后探讨CPLD在各个应用领域中的具体应用,最后重点讨论CPLD的编程语法,深入探讨其技术细节和使用方法。

最后,在结论部分,我们将总结CPLD语法在现代电子领域中的重要性,展望其未来发展趋势,并得出结论。

整个文章结构清晰逻辑,希望能够对读者有所帮助。

1.3 目的CPLD(Complex Programmable Logic Device)作为一种可编程逻辑器件,在数字电路设计中扮演着重要的角色。

本文旨在探讨CPLD的编程语法,深入了解其语法规则和特点,帮助读者更好地掌握CPLD的编程技巧。

通过对CPLD编程语法的介绍和分析,读者可以更有效地设计和实现数字电路,提高电路设计的效率和准确性。

同时,本文还旨在强调CPLD 语法在现代电子领域的重要性,为读者提供未来学习和应用CPLD的参考依据。

通过本文的阐述,读者能够更全面地了解CPLD的编程语法,为进一步深入研究和应用CPLD打下坚实的基础。

2.正文2.1 CPLD的定义与特点CPLD全称为Complex Programmable Logic Device,即复杂可编程逻辑器件。

fpGa_CPLD设计工具xilinxISE使用详解

1.第一章:FPGA/CPLD简介●FPGA一般是基于SRAM工艺的,其基于可编程逻辑单元通常是由查找表(LUT,look up table)和寄存器(register)组成。

其中内部的查找表通常是4输入的,查找表一般完成纯组合逻辑功能;●Xilinx可编程逻辑单元叫做slice,它由上下两部分组成,每部分都由一个register加上一个LUT组成,被称为LC(logic cell,逻辑单元),两个LC之间有一些共用逻辑,可以完成LC之间的配合工作与级连;●Altera可编程逻辑单元叫做LE(Logic Element,逻辑单元),由一个register加上一个LUT构成;Lattice的底层逻辑单元叫做PFU(programmable Function unit,可编程功能单元),它由8个LUT和9个register组成。

●Ram和dpram/spram/伪双口RAM,CAM(content addressable memory)。

Fpga中其实没有专业的rom硬件资源,实现ROM是对RAM赋初置,并且保存此初值●CAM,即内容地址储存器,在其每个存储单元都包含了一个内嵌的比较逻辑,写入cam的数据会和其内部存储的每一个数据进行比较,并返回与端口数据相同的所以内部数据的地址。

总结:RAM是一种根据地址读/写数据的存储单元;而CAM 和RAM恰恰相反,它返回的是与端口数据相匹配的内部地址。

使用很广,比如路由器中的地址交换表等等●Xilinx块ram大小是4kbit和18kbit两种结构。

Lattice块ram是9kbit●分布式ram适合用于多块小容量的ram的设计;●Dll(delay-locked loop)延迟锁定回环或者pll(phase locked loop)锁相环,可以用以完成时钟的高精度,地抖动的倍频/分频/占空比调整/移相等功能。

Xilinx主要集成的是DLL,叫做CLKDLL,在高端的FPGA中,CLKDLL的增强型模块为DCM (digital clock manager,数字时钟管理模块)。

CPLD部分用户指南

YXDSP-F2812系列开发板V1.00——CPLD部分用户指南声明南京研旭电气科技有限公司保留随时对其产品进行修改、改进和完善的权利,同时也保留在不作任何通告的情况下,终止其任何一款产品的供应和服务的权利。

用户在下订单前应获取相关信息的最新版本,并验证这些信息是当前的和完整的。

版权©2009,南京研旭电气科技有限公司第一章YXDSP-F2812-CPLD入门1.1、MAX3000A的介绍MAX3000A 系列是Altera 公司99年推出的3.3v低价格EEPOM工艺PLD,是满足大批量,成本敏感性应用的非易失性和即用性CPLD理想的解决方案,是ALTERA 公司销量最大的产品,属于主流器件。

Altera 的3.3-V MAX® 3000A 器件基于Altera® MAX 架构,为大批量应用进行了成本优化。

采用先进的0.30 μm CMOS 处理,基于电可擦除可编程只读存储器(EEPROM),MAX 3000A 系列是一种即用性的器件,密度范围从32 到512 个宏单元。

MAX 3000A 器件支持在系统可编程能力(ISP),能够轻松地实现现场重配置。

每个MAX 3000A 宏单元都可以独立地配置成顺序或组合逻辑操作。

表1. MAX 3000A 器件概述(3.3 伏)1. tPD (ns) = 从输入到非寄存器输出的数据路径延迟2. tSU (ns) = 全局时钟建立时间3. tCO1 (ns) = 全局时钟到输出延迟4. fCNT (ns) = 16 比特计数器内部全局时钟频率5. PLCC = 塑封J 引线芯片封装6. TQFP = 薄塑封四角扁平封装7. PQFP = 塑封四角扁平封装8. BGA = 球栅阵列1.3、YXDSP-F2812-CPLD开发板资源◇ALTERA EPM3128A◇6MHz 有源晶振◇四位数码管◇4×2 键盘阵列◇1 个独立按键◇1 个复位按键◇蜂鸣器◇8 个LED1.4、YX-CPLD开发板例程◇实例1: 逻辑功能实现◇实例2: 三态门◇实例3: 三八译码器◇实例4: 数据选择器◇实例5: 比较器◇实例6: D触发器◇实例7: 分频器◇实例8: 霓虹灯演示◇实例9: 按键防抖动◇实例10: 四位数码管扫描◇实例11: 电子时钟◇实例12: 音乐演奏《小星星》第二章Altera 集成开发环境QuartusII 2.1、安装QUARTUS2 开发环境。

cpld第7讲

——基于QuartusⅡ的FPGA/CPLD设计

1、RS触发器

• 功能描述: • r为清零端,s为置数端,q和 qn为输出端,qn为q取反。

1、 RS触发器

• 真值表:

输入 r 0 s 1 q 0

输出 qn 1

1 1 0

0 1 0

1

0

保持 保持 不定 不定

1、 RS触发器

• 代码(1) :

• 代码(2):

• • • • • • • • • • • • •

2、 JK触发器

if r='0' and s='1' then q_temp<='0';qn_temp<='1'; elsif r='1' and s='0' then q_temp<='1';qn_temp<='0'; elsif r='0' and s='0' then null; elsif cp'event and cp='1' then if j='0' and k='1' then q_temp<='0';qn_temp<='1'; elsif j='1' and k='0' then q_temp<='1';qn_temp<='0'; elsif j='1' and k='1' then q_temp<=not q_temp;qn_temp<=not qn_temp; elsif j='0' and k='0' then q_temp<=q_temp;qn_temp<=qn_temp; end if; end if; end process; q<=q_temp;qn<=qn_temp; end one;

CPLD入门教程

CPLD⼊门教程⽬录前⾔ (2)第⼀章 MAX+plusII 软件和license的获得 (6)第⼆章 MAX+plusII 软件的安装和license及驱动的设置2.1 MAX+plusII 软件的安装 (7)2.2 MAX+plusII 软件的license设置 (8)2.3 MAX+plusII 软件的驱动设置 (12)第三章⽤VHDL语⾔设计三⼈表决器3.1打开MAX+plusII (22)3.2新建VHDL⽂档 (23)3.3输⼊设计⽂件 (24)3.4保存⽂件 (25)3.5检查编译 (27)3.6创建symbol (32)3.7波形防真 (33)3.8下载验证 (40)第四章⽤原理图输⼊的⽅式设计三⼈表决器 (47)第五章⽤verilog-HDL语⾔设计三⼈表决器 (51)前⾔编写本⼊门教程(V1.2)的⽬点是为了让FPGA/CPLD初学者快速地⼊门。

该教程的特点是通过基本概念讲解和实际的例⼦来让初学者迅速了解FPGA/CPLD。

该教程是共享⽂件,可以复制、下载、转载,如果转载该⽂章请注明出处:/doc/3da4f780d4d8d15abe234ea3.html ;该教程未经许可,不得⽤于商业⽤途。

FPGA/CPLD是电⼦设计领域中最具活⼒和发展前途的⼀项技术,它的影响丝毫不亚于70年代单⽚机的发明和使⽤。

FPGA/CPLD的基本知识:1.什么是FPGA/CPLDFPGA (Field Programmable Gate Array)是现场可编程门阵列,CPLD是复杂的可编程逻辑器件(Complex Programmable Logic Device)的简称,不同⼚家有不同的称呼,Xilinx把SRAM⼯艺,要外挂配置⽤的EEPROM的PLD叫FPGA,把Flash⼯艺(类似EEPROM⼯艺),乘积项结构的PLD叫CPLD; Altera把⾃⼰的PLD产品MAX系列(EEPROM⼯艺),FLEX/ACEX/APEX 系列(SRAM⼯艺)都叫作CPLD,即复杂PLD(Complex PLD),由于FLEX/ACEX/APEX系列也是SRAM⼯艺,要外挂配置⽤的EPROM,⽤法和Xilinx的FPGA⼀样,所以很多⼈把Altera的FELX/ACEX/APEX系列产品也叫做FPGA.但由于FPGA和CPLD功能基本相同,只是⼯艺和实现形式不同,所以初学者可以不要详细区分,我们可以统称为FPGA/CPLD。

FPGA入门教程_ALTERA_Quartus_II__和_XILINX___ISE_CPLD入门教程_教案_VHDL_Verilog_例程讲解

2011-8

FPGA介绍

何为FPGA?

FPGA(Field-Programmable Gate Array),即现 场可编程门阵列,它是在PAL、GAL、CPLD等可编 程器件的基础上进一步发展的产物。它是作为专用 集成电路(ASIC)领域中的一种半定制电路而出现 的,既解决了定制电路的不足,又克服了原有可编 程器件门电路数有限的缺点

Verilog HDL 的抽象级别

语言本身提供了各种层次抽象的表述,可以用详细 程度有很大差别的的多层次模块组合来描述一个 电路系统。 行为级:技术指标和算法的Verilog描述 RTL关级:具体的晶体管物理器件的描述

Verilog HDL 的抽象级别

设计复杂数字系统的工具 和手段

两种硬件描述语言 : Verilog VHDL

有哪几种硬件描述语言? 各有什么特点?

Verilog HDL - 较多的第三方工具的支持 - 语法结构比VHDL简单 - 学习起来比VHDL容易 - 仿真工具比较好使 - 测试激励模块容易编写

Verilog HDL 的发展历史

两者建模能力的比较

行为级 的抽象

系统级

SystemVerilo g

算法级

VHDL Verilog

寄存器传输级

逻辑门级 VITAL

开关电路级

VerilogHDL 与 VHDL 建 模 能 力 的 比 较

Verilog HDL有什么用处?

在各种抽象层次上描述数字电路

测试各种层次数字电路的行为 设计出正确有效的复杂电路结构

数字信号处理系统的实现

非实时系统: 通用的计算机和利用通用计算机改装的设备,主要 工作量是编写 “C” 程序。输入/输出数据大多为文 本 。 实时系统: 信号处理专用的微处理器为核心的设备,主要工作 量是编写汇编程序。输入/输出数据大多为数据流, 直接用于控制 。

CPLD入门基础

速度

其他资源

慢

-

快

EAB,锁相环

保密性

可加密

一般不能保密

多个CPLD器件串行编程 将多个CPLD器件以串行的方式连接起来,一次完成多个器件 的编程。这种连接方式称为菊花链连接。

TDI TDO TCK

TM S

EPM7032S U1 SDI1 SDO 1 SDI2

EPM7032S U2 SDO 2 SDI3

EPM7032S U3 SDO 3

CPLD与FPGA的区别

T E2CMOS 管 内部连线 可编程连接原理图 宏单元或 I/O 连线

纵线和横线连通;未被编程为截

止时,两线则不通。

I/O单元 I/O单元是CPLD外部封装引脚和内部逻辑间的接口。每个 I/O单元对应一个封装引脚,对I/O单元编程,可将引脚定 义为输入、输出和双向功能。

到 内 部 可 编 程 连 线 区 到其他 I/O 单 元 输入缓冲 VCCIN

T

VCCIO

D1 D2 可编程 上拉 I/O 可编程 接地

数据选择器 提供OE号。 OE=1, I/O引 脚为输出

来 OUT 自 宏 单 PTO 元 E 全 局 输 出 使 能 r r

输出缓冲驱 动 1 r 0 O E 摆率 M 控制

到其他 I/O 单元

2 CPLD编程简介

编程过程(Download或Configure):将编程数据写入这些 单元的过程。 编程的实现:由可编程器件的开发软件自动生成的。 用户在开 发软件中 输入设计 及要求。 检查、分析 和优化。完 成对电路的 划分、布局 和布线

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录前言 (2)第一章 MAX+plusII 软件和license的获得 (6)第二章 MAX+plusII 软件的安装和license及驱动的设置2.1 MAX+plusII 软件的安装 (7)2.2 MAX+plusII 软件的license设置 (8)2.3 MAX+plusII 软件的驱动设置 (12)第三章用VHDL语言设计三人表决器3.1打开MAX+plusII (22)3.2新建VHDL文档 (23)3.3输入设计文件 (24)3.4保存文件 (25)3.5检查编译 (27)3.6创建symbol (32)3.7波形防真 (33)3.8下载验证 (40)第四章用原理图输入的方式设计三人表决器 (47)第五章用verilog-HDL语言设计三人表决器 (51)前言编写本入门教程(V1.2)的目点是为了让FPGA/CPLD初学者快速地入门。

该教程的特点是通过基本概念讲解和实际的例子来让初学者迅速了解FPGA/CPLD。

该教程是共享文件,可以复制、下载、转载,如果转载该文章请注明出处:;该教程未经许可,不得用于商业用途。

FPGA/CPLD是电子设计领域中最具活力和发展前途的一项技术,它的影响丝毫不亚于70年代单片机的发明和使用。

FPGA/CPLD的基本知识:1.什么是FPGA/CPLDFPGA (Field Programmable Gate Array)是现场可编程门阵列,CPLD是复杂的可编程逻辑器件(Complex Programmable Logic Device)的简称,不同厂家有不同的称呼,Xilinx把SRAM工艺,要外挂配置用的EEPROM的PLD叫FPGA,把Flash工艺(类似EEPROM工艺),乘积项结构的PLD叫CPLD; Altera把自己的PLD产品MAX系列(EEPROM工艺),FLEX/ACEX/APEX系列(SRAM工艺)都叫作CPLD,即复杂PLD(Complex PLD),由于FLEX/ACEX/APEX系列也是SRAM工艺,要外挂配置用的EPROM,用法和Xilinx的FPGA一样,所以很多人把Altera的FELX/ACEX/APEX系列产品也叫做FPGA.但由于FPGA和CPLD功能基本相同,只是工艺和实现形式不同,所以初学者可以不要详细区分,我们可以统称为FPGA/CPLD。

2.FPGA/CPLD的用途:FPGA/CPLD能做什么呢?可以毫不夸张的讲,FPGA/CPLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用FPGA/CPLD来实现。

FPGA/CPLD如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法,或是硬件描述语言自由的设计一个数字系统。

通过软件仿真,我们可以事先验证设计的正确性。

在PCB 完成以后,还可以利用FPGA/CPLD的在线修改能力,随时修改设计而不必改动硬件电路。

使用FPGA/CPLD来开发数字电路,可以大大缩短设计时间,减少PCB面积,提高系统的可靠性。

FPGA/CPLD可以做数字IC设计的前端验证,用这种方式可以很大程度上降低IC设计的成本。

FPGA/CPLD的这些优点使得FPGA/CPLD技术在90年代以后得到飞速的发展,同时也大大推动了EDA软件和硬件描述语言(HDL)的进步3.CPLD/FPGA的宏单元是怎么定义?一个宏单元对应多少门?宏单元(或逻辑单元)是PLD/FPGA的最基本单元,不同产品对这种基本单元的叫法不同,如LE,MC,CLB,Slices等,但每个基本单元一般都包括两部分,一部分实现组合逻辑,另一部分实现时序逻辑。

各个厂家的定义可能不一样。

对ALTERA的芯片,每个基本单元含一个触发器;对Xilinx的部分芯片,每个基本单元单元含两个触发器。

一般不用“门”的数量衡量CPLD/FPGA的大小,因为各家对门数的算法不一样,象ALTERA和Xilinx对门的计算结果就差了一倍,推荐用触发器的多少来衡量芯片的大小。

如10万门的Xilinx的XC2S100有1200个slices,即含2400个触发器;5万门的ALTERA的1K50则含2880个LE,即2880个触发器。

4. 如何如何学习FPGA/CPLD其实FPGA/CPLD的使用很简单,学习FPGA/CPLD比学习单片机要简单的多,有数字电路基础,会使用计算机,就可以进行FPGA/CPLD的开发。

开发FPGA/CPLD需要了解两个部分:(1). FPGA/CPLD开发软件(2). FPGA/CPLD本身(芯片);另外最好配置开发系统(或实验板)FPGA/CPLD软件已经发展的相当完善,用户甚至可以不用详细了解FPGA/CPLD的内部结构,也可以用自己熟悉的方法:如原理图输入或HDL语言来完成相当优秀的FPGA/CPLD设计。

所以对初学者,首先应简单了解FPGA/CPLD开发软件和开发流程。

本教程就是本着这种思想编写的。

了解FPGA/CPLD的内部结构,将有助于提高我们设计的效率和可靠性。

本手册以目前使用频率和资料最多的ALTERA公司的软件MAX+plusII10.2和芯片EPM7128SLC84-15为例子来讲述一个完整的CPLD/FPGA设计的全过程。

本手册中实验所需要到软件:max+plus10.2(第一章讲述来源);硬件:JX002开发套件(含CPLD芯片EPM7128)、PC、220V电源。

本手册的设计例子是一个很简单的实际例子:三人表决器。

采用VHDL、Verilog-HDL和图形的方式(以VHDL为主),硬件采用JX002B 型实验板,你可以到下载JX002B型实验板的使用说明书。

三人表决器的功能描述:三个人分别用拨位开关SW1、SW2、SW3来表示自己的意愿,如果对某决议同意,各人就把自己的拨位开关拨到高电平(上方),不同意就把自己的拨位开关拨到低电平(下方)。

表决结果用LED(高电平亮)显示,如果决议通过那么实验板上L2(黄灯)亮;如果不通过那么实验板上L1(红灯)亮;如果对某个决议有任意二到三人同意,那么此决议通过,L2亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,L1亮。

编者将在以后的业余时间编写QUARTUS软件的使用以及FPGA在IC设计中的应用。

该教程参考了FPGA中文网站的部分内容,在此表示感谢。

本手册仅供初学者使用。

由于编者水平有限,本手册难免有错误和不妥之处,恳请读者批评指正:fpga@.2004.2shanghai第一章 MAX+plusII 软件和license的获得你可以通过下面方式来获得MAX+plusII 软件:A:到https:///login/signin.asp上登记、注册申请并下载(那是10.2的baseline版本的)。

B:到上下载(那是10.2的BASELINE 版本的)C:和fpga@联系使用MAX+plusII 软件你需要license.dat文件,你可以到上下载第二章 MAX+plusII 软件的安装和license、驱动的设置2.1 MAX+plusII 软件的安装如果是baseline10.2版本,直接双击下图的图表,按提示安装如果是10.2完全版,双击下图中的setup.exe可执行文件,按提示安装其他版本也都是双击可执行文件*.exe安装后,在开始->程序->altera(或MAX+plusII)中将看到MAX+plusII的图标安装后请按下面步骤进行。

2.2 MAX+plusII 软件的license设置安装完成后,将license文件拷贝到硬盘的任何一个目录,连后按下面过程设置(下面是英文原文,仅WIN2000翻译成中文了),另外根据我们的使用经验,安装后直接在软件中的设置就可以了,如下面两图所示:连后在对话框中填入license.dat所在路径(不要出现中文),点OK就可以了官方标准设置如下:Setting up Licensing in Windows NTTo specify the license file in the Windows NT Control Panel, follow these steps:1)choose Settings > Control Panel from the Windows Start menu. 2)Double-click the System icon in the Control Panel window. 3)Click the Environment tab in the System Properties dialog box.4)Click the System Variable list to highlight it, and then in the Variable box, type LM_LICENSE_FILE.5)Type <path to license file>\license.dat in the Value box.Example: C:\maxplus\license.dat6)Click SET, and then click OK.7)You can now run the Altera software.Setting Up Licensing in Windows 2000在WINDOWS2000中设置licensingTo specify the license file in the Windows 2000 Control Panel, follow these steps:在Windows 2000中设置license文件,按下面流程:choose Settings > Control Panel from the Windows Start menu. 从WINDOWS开始菜单中选择设置>控制面板Double-click the System icon in the Control Panel window. 在控制面板上双击系统Click the Advanced tab in the System Properties dialog box. 点系统特性中的高级Click the Environment Variables button.点环境变量Click the System Variable list to highlight it, and then click New.点系统变量,连后点新建Type LM_LICENSE_FILE in the Variable box.在变量名中填LM_LICENSE_FType <path to license file>\license.dat in the Value box.Example: C:\MAXPLUS\license.dat在变量值中填上license所在路径,如C:\MAXPLUS\license.datClick OK.点确认You can now run the Altera software.你可以使用 Altera软件了Setting up Licensing in Windows 98To specify the license file in Windows 98, follow these steps: pen your PC's autoexec.bat file with a text editor.Type the following environment variable on its own line in the autoexec.bat file: set LM_LICENSE_FILE=<path to license file>\license.dat.Example: set LM_LICENSE_FILE=C:\maxplus\license.datSave the autoexec.bat file.Restart the PC.You can now run the Altera software.2.3 MAX+plusII 软件的驱动设置在Win98下运行MAX+plusII可以自动检测到ByteBlasterMV(ByteBlaster)下载电缆,但在WIN2000、WINXP、WINNT下无法自动检测到它的存在。