TS101的内核结构

一种基于ADSP—TS101的多普勒滤波器组设计

1 引 言

雷 达的 主要任 务 之一就 是从干扰 背景 中提 取 目标 的信 息 。对 雷达 的干扰 主要有两 种 : 源和无 源干扰 , 有 处理 无 源干扰 的主 要方法 就是频 域处 理 , 即多普 勒滤波 。 它是 利用 目标和 干扰相 对 于雷 达 的运动速 度不 同而 引起 的多普 勒频移 不 同滤 掉 杂波信 号 。 D( 目标检 测 ) 通 过很多 的带通 滤波器组 成 滤波器组 对雷 达回 MT 动 是 波进 行 滤波 , 然后对 滤波 结果作 C AR( 虚警 ) F 恒 处理来 检测 目标 是否存 在 。在 杂波背 景下检 测 目标 回波 , 除 了有 杂 波抑 制滤波 器外 , 还必 须有 与脉 冲串匹配 的滤波 器 。 杂波抑 制滤波 器必须 在杂波存 在的频率 处有深 的 凹口, 要对回波脉冲串匹配滤波 , 就须知道 目标的多普勒频移 , 实际中多普勒频移是未知的 , 因此采用一组相

s o t a h e i n i e fc ie h w h tt ed sg fe t . s v Ke wo d ; Do p e i e a k ;FF ;ADS TS1 1 a allp o e sn y rs p lrf trb n s l T P— 0 ;p r l r c s ig e

( 西安 电子科技 大学 西安 707 ) 1 0 1

【 摘要】 MT D雷达的多普勒滤波器组常用F T 来实现。 F 本文提 出一种以 A S . S 0 为核 D PT 11 心 的 高速 并行 实时 系统来 实现 F T 快速算 法 。 系统 速度 快 , F 该 超过相 同数 量 AD P2 00的 十倍 , S 一16 并 可 以做 其他 功 能的扩展 。仿真 和 实验 结 果验证 了设计 的有 效性 。 关 键词: 多普勒滤波;F D P T 11 并行处理 F T A S -S 0;

基于多片TS101的分布式并行信号处理机

Ke r s ywo d :mu - hi TS1 ; d srb t d; sg a r c s o ; Do p e a a 01 it u e i i n lp o e s r p l rr d r

1 引 言

近几年 ,随着超 大规模 集成 电路( L I V S) 技术 的发展 ,数字 信号处 理( S ) D P 的性 能得到 了前所 未有 的提 高 。主 要体 现在 D P内核速 度 的显 著提高 以及各种 并行技术 , 单指令 多数据( I ) S 如 SMD 和超标量 等在单 片 D P研 制 中的 S 引入 。但是 ,现代雷 达和声 纳信号 处理算法 日趋复杂 ,运算量 越来越 大 ,单 片 D P仍无 法满足 需求 ,必须采用 S 高 性能 DS P构 建成 大规模处 理系统 ¨。 J

d v lp d s c c s f ly wh s h r c e sisi c u e h g e o m a c , d / b n wi t ,lw— o r e e o e u e e su l , o e c a a tr tc n l d i h p r r n e wi e IO a d d h o p we , i f

美 国 A I 司 的 A P T 1 1 i rH R D公 DS 。 S 0 g S A C是 一款极 高性 能 的静态 超标量 处理器 【,其主要特 点 :a Te I J )内核 处理 速度高 达 3 0 z ) Mbt 片内静态存储 器(R M) 0 MH ;b 6 i s S A ,3条 1 8 i 内部 数据 总线 ;c 2 bt s )双 运算模 块 ,每个 包

维普资讯

第 5 卷

第5 期

信 息 与 电 子 工 程

TS201芯片与Ts101比较

ADSP-TS201S芯片的功能和应用摘要:介绍了ADI公司的新一代高性能TigerSHARC处理器ADSP-TS201S的结构和性能,并结合与TS101S 的对比说明了TS201S在性能上的改进;给出了基于TS201S进行系统设计的基本方法及设计过程中应该特别注意的问题;最后给出了多片系统的典型设计电路图,同时说明了TS201S外围电路的配置和多片级联的方法。

关键词:ADSP-TS201S;系统设计;多片系统美国模拟器件公司(ADI)在继ADSP-TS101之后,于2003年下半年又推出了新一代高性能Tiger-SHARC处理器ADSP-TS201/202/203。

此系列处理器片内集成了更大容量的存储器,性价比很高。

它们兼有ASIC和FPGA的信号处理性能和指令集处理器的高度可编程性与灵活性。

适用于高性能、大存储量的信号处理和图像应用,例如雷达与声纳应用、无线基站、图像处理系统及工业仪器仪表等领域。

考虑到ADSP-TS202/203与201有许多相似之处,本文仅以TS201S为例进行介绍。

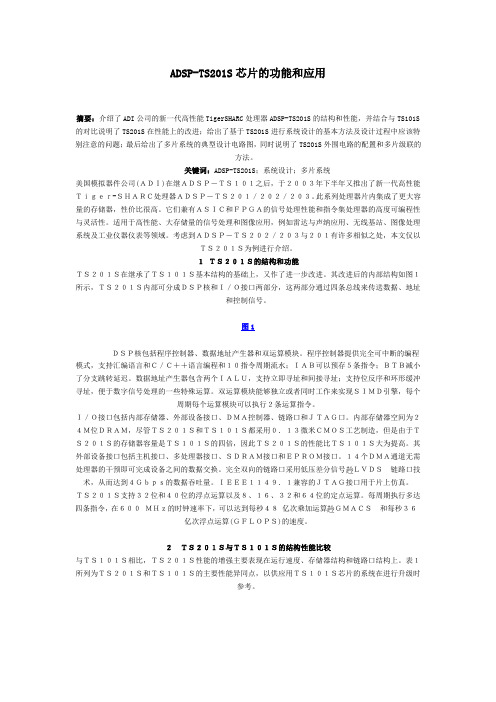

1TS201S的结构和功能TS201S在继承了TS101S基本结构的基础上,又作了进一步改进。

其改进后的内部结构如图1所示,TS201S内部可分成DSP核和I/O接口两部分,这两部分通过四条总线来传送数据、地址和控制信号。

图1DSP核包括程序控制器、数据地址产生器和双运算模块。

程序控制器提供完全可中断的编程模式,支持汇编语言和C/C++语言编程和10指令周期流水;IAB可以预存5条指令;BTB减小了分支跳转延迟。

数据地址产生器包含两个IALU,支持立即寻址和间接寻址;支持位反序和环形缓冲寻址,便于数字信号处理的一些特殊运算。

双运算模块能够独立或者同时工作来实现SIMD引擎,每个周期每个运算模块可以执行2条运算指令。

I/O接口包括内部存储器、外部设备接口、DMA控制器、链路口和JTAG口。

内部存储器空间为24M位DRAM,尽管TS201S和TS101S都采用0.13微米CMOS工艺制造,但是由于TS201S的存储器容量是TS101S的四倍,因此TS201S的性能比TS101S大为提高。

DSP公司各主流芯片比较

DSP公司各主流芯片比较引言DSP芯片也称数字信号处理器,是一种专门适合于进行数字信号处理运算的微处理器具,其主机应用是实时快速地实现各种数字信号处理算法。

依照数字信号处理的要求,DSP芯片一样具有如下要紧特点:〔1〕在一个指令周期内可完成一次乘法和一次加法;〔2〕程序和数据空间分开,能够同时访问指令和数据;〔3〕片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问;〔4〕具有低开销或无开销循环及跳转的硬件支持;〔5〕快速的中断处理和硬件I/O支持;〔6〕具有在单周期内操作的多个硬件地址产生器;〔7〕能够并行执行多个操作;〔8〕支持流水线操作,使取指、译码和执行等操作能够重叠执行。

在我们设计DSP应用系统时,DSP芯片选型是专门重要的一个环节。

在DSP系统硬件设计中只有选定了DSP芯片,才能进一步设计其外围电路及系统的其他电路。

因此说,DSP芯片的选择应依照顾用系统的实际需要而确定,做到既能满足使用要求,又不白费资源,从而也达到成本最小化的目的。

DSP实时系统设计和开发流程如图1所示。

要紧DSP芯片厂商及其产品德州仪器公司众所周知,美国德州仪器〔Texas Instruments,TI〕是世界上最知名的DSP芯片生产厂商,其产品应用也最广泛,TI公司生产的TMS320系列DSP芯片广泛应用于各个领域。

TI公司在1982年成功推出了其第一代DSP芯片TMS32020,这是DSP应用历史上的一个里程碑,从此,DSP 芯片开始得到真正的广泛应用。

由于TMS320系列DSP芯片具有价格低廉、简单易用、功能强大等特点,因此逐步成为目前最有阻碍、最为成功的DSP系列处理器。

目前,TI公司在市场上要紧有三大系列产品:〔1〕面向数字操纵、运动操纵的TMS320C2000系列,要紧包括TMS320C24x/F24x、TMS320LC240x/LF240x、TMS320C24xA/LF240xA、TMS320C28xx等。

一种新型DSPTS101中的链路DMA

TS101 是高性能浮点数字信号处理器 , 它有 8 个链路 DMA 通道 , 可以在内部/ 外部存储器和链路口

之间 、链路口与链路口之间进行多种类型的 DMA 传输 。文章介绍了链路 DMA 及其在雷达信号处理

系统中的实际应用 。

关键词 : TS101 ; 链路 DMA ; TCB ; 转发

分类号 : TN957

图 1 链路口结构图Fra bibliotek© 1995-2005 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved.

- 22 -

《国外电子元器件》2005 年第 2 期 2005 年 2 月

和 LxCL KIN、LxCL KOUT 和 LxDIR( x 为链路口序号 0~3) 三个控制引脚 ,可支持多片 TS101 处理器间点 对点的双向数据传送 。其中 LxDIR 用来指示链路口 的数据流向 。LxCL KIN 和 LxCL KOUT 为链路口的时 钟/ 确认握手信号 。数据发送时 , LxCL KOUT为时钟 信号 , LxCL KIN 为确认信号 ; 数据接收时 , LxCL KIN 为时钟信号 , LxCL KOUT为确认信号 。发送数据时 , 首先传输四字数据到链路发送缓冲寄存器 LBUFTx , 再将其复制到移位寄存器(若移位寄存器为空 ,此时 LBUFTx 可被写入新的数据) , 然后以字节的形式发 送出去 (先发送低字节) , 每个字节在链路时钟的上 升沿和下降沿被驱动和锁存 ( SHARC 系列 DSP 只在 一个时钟沿驱动数据) 。接收器的移位寄存器为空 时 , 系统将开始接收发送方传输的数据并将其送入 移位寄存器 ,同时驱动 LxCL KOUT为低 。当整个四字 到齐后 , 如果接收缓冲寄存器 LBUFRx 为空 , 系统会 将四字数据从移位寄存器复制到 LBUFRx ,并在数据 被取走后驱动其 LxCL KOUT为高 , 以告诉发送方接 收缓冲寄存器为空 , 可以准备接收新数据 。发送方 检测到 LxCL KIN 为高后立即进行下一次传输 。所有 的链路口都可用于 TS101 处理器的引导 ( SHARC 系 列只固定某个链路口引导) 。然而应当注意 : TS101 处理器的链路口与 SHARC 系列的 DSP 是不兼容 的。 2. 2 链路 DMA

TS201内部组成

ADSP-TS201S I/O设备结构图

6

ADSP-TS201S I/O设备构成

外部总线 I/O处理器 片内系统总线(SOC BUS) 和SOC接口 定时器 DMA控制器 FLAG 链路口控制器 外部端口 JTAG端口/Debug端口(用于调试仿真)

7

双运算模块

Computation block X

0

STATUS

ALU

31

Register File

ALU PR

Mult MR

Shift BFOTMP

11

算术逻辑单元(ALU)

ADSP TS201处理器内核中的ALU主要实现算数逻辑操作。

ALU是从它的寄存器组中得到输入操作数,并将它的输出 结果返回到寄存器组中。

浮点乘法操作:2个32位输入操作数,结果为32位浮点 数;2个40位扩展精度输入操作数,结果为40位数

定点数据压缩操作:输入操作数16/32/64位,输出为 16/32位

15

乘法器指令选项

选项 有符号/无符号数

整数/小数 清零 截断

清零/取舍 饱和 共轭

选项代码 U I C T CR S J

默认 有符号数

小数 未清零 不截断 未清零,未取舍 未饱和 非共轭

16

乘法器执行状态

执行状态标志保存在算术状态(XSTAT和

YSTAT)寄存器中,程序使用状态标志控制 条件指令执行和触发软件意外中断。

标志 MZ MN MV MU MI

定义 定点数为0或浮点数下溢出

负数 上溢出 下溢出 浮点非法操作

数据转换

对定点数据操作时,输入操作数可以为64位长字,1个或2

个32位正常字,2个或4个16位短字,4个或8个字节。

DSP公司各主流芯片比较(精)

DSP芯片介绍及其选型引言DSP芯片也称数字信号处理器,是一种特别适合于进行数字信号处理运算的微处理器具,其主机应用是实时快速地实现各种数字信号处理算法。

根据数字信号处理的要求,DSP芯片一般具有如下主要特点:(1)在一个指令周期内可完成一次乘法和一次加法;(2)程序和数据空间分开,可以同时访问指令和数据;(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问;(4)具有低开销或无开销循环及跳转的硬件支持;(5)快速的中断处理和硬件I/O支持;(6)具有在单周期内操作的多个硬件地址产生器;(7)可以并行执行多个操作;(8)支持流水线操作,使取指、译码和执行等操作可以重叠执行。

在我们设计DSP应用系统时, DSP芯片选型是非常重要的一个环节。

在DSP系统硬件设计中只有选定了DSP芯片,才能进一步设计其外围电路及系统的其他电路。

因此说,DSP芯片的选择应根据应用系统的实际需要而确定,做到既能满足使用要求,又不浪费资源,从而也达到成本最小化的目的。

DSP实时系统设计和开发流程如图1所示。

主要DSP芯片厂商及其产品德州仪器公司众所周知,美国德州仪器(Texas Instruments,TI)是世界上最知名的DSP芯片生产厂商,其产品应用也最广泛,TI公司生产的TMS320系列DSP芯片广泛应用于各个领域。

TI公司在1982年成功推出了其第一代DSP芯片TMS32010,这是DSP应用历史上的一个里程碑,从此,DSP芯片开始得到真正的广泛应用。

由于TMS320系列DSP芯片具有价格低廉、简单易用、功能强大等特点,所以逐渐成为目前最有影响、最为成功的DSP系列处理器。

目前,TI公司在市场上主要有三大系列产品:(1)面向数字控制、运动控制的TMS320C2000系列,主要包括TMS320C24x/F24x、TMS320LC240x/LF240x、TMS320C24xA/LF240xA、TMS320C28xx等。

TigerSHARC处理器技术及其应用(冯小平)-第2章

2.1 TS系列DSP的内核结构概述 2.2 TS处理器的运算模块 2.3 TS处理器的整型算术逻辑单元 2.4 TS101S的程序控制器 2.5 TS20XS的程序控制器

第2章 TS系列DSP的内核结构 2.1 TS系列DSP的内核结构概述

第2章 TS系列DSP的内核结构

2) 非存储器映射寄存器 非存储器映射寄存器是一些特殊寄存器,非存储器映射寄 存器包括: (1) 运算模块的状态寄存器(XSTAT和YSTAT); (2) ALU的并行结果寄存器(XPR1~0和YPR1~0); (3) 乘法器定点乘积寄存器(XMR3~0和YMR3~0); (4) 乘法器定点乘积溢出寄存器(XMR4和YMR4); (5) 移位器的位FIFO溢出暂存寄存器(XBFOTMP和 YBFOTMP)。

第2章 TS系列DSP的内核结构

TS201S的内核结构如图2.1-2所示。 TS201S与TS101S在内核结构方面基本相同,因此本章的 后续各节将以TS101S为主,介绍TS处理器的内核中的各个模 块。

第2章 TS系列DSP的内核结构 图2.1-2 TS201S的内核结构

第2章 TS系列DSP的内核结构 2.2 TS处理器的运算模块

2.1.1 TS101S的内核结构概述 ADSP—TS101的内核结构框图如图2.1-1所示。它主要由

双运算模块、双IALU、程序控制器及其内总线等组成。

第2章 TS系列DSP的内核结构 图2.1-1 ADSP—TS101的内核结构框图

第2章 TS系列DSP的内核结构

其内核具有如下特点: (1) 双运算模块:即X和Y运算模块,各包含一套乘法器、 ALU、移位器和一套32字寄存器组。 (2) 双整型ALU:J和K整型ALU,各拥有一套32位ALU和32 字寄存器组。 (3) 程序控制器:用于控制指令流,它包含一个指令对 齐缓冲(IAB)和一个分支目标缓冲(BTB)。 (4) 内部有三套128位宽的总线,为内部存储器块之间提 供每周期48字节的高带宽连接,同时实现与外部存储器、存储 器映射I/O、主机处理器以及其他TigerSHARC的接口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

指令并行规则

• 指令行能够并行执行必须满足一定条件

– 资源约束 – 延迟和相关 – 流水操作 – 一般约束 – 运算块指令限制 – IALU指令限制 – 程序流程控制指令限制

延迟和相关

• 处理器流水操作会被锁住——当一个操作的结果不能 用于另一个操作的输入时,处理器自动插入stall周期 • 流水线相关性类型 –计算块相关性 –IALU相关性 –Ureg 传输相关性 –指令流相关性 –条件执行相关性 • 有效的程序代码会消除大部分计算块和加载/保存的相 关性

在每个处理单元中,有32个寄存器的寄存器组允许通过 编程避免STALL。

汇编优化器帮助程序员监测冲突

TS101原理框图

TS201原理框图

程序加载方法

• 在复位时将程序代码导入DSP的内部RAM • 可以选择四种加载方式之一 – EPROM加载 • 通过外部口连接EPROM,传递程序代码到内部RAM – LINK口加载 • 通过链路口向另外的DSP传递程序代码到内部RAM – HOST加载 • 通过主机口向DSP传递程序代码到内部RAM – 无加载 • 直接从外部存储器开始执行程序

Rn

0x00001234

Rs

0x00000091

移位器操作-移位/循环 (II)

• 逻辑移位举例。

Rs = LSHIFT Rn BY Rm Rn中的内容移位Rm (4)指定的位数,结果放入 Rs 中。 注意Rm = -4是右移 Rm = +4是左移

Rm Rn

xxxx xxxx xxxx xxxx xxxx xxxx xxxx 0100 Shift magnitude = 4 0001 0010 0011 0100 0101 0110 1110 1111

TS101的内核结构

程序控制器

2个 IALU

3套内部总线

Sequencer 128-entry BTB 128b 128b

0

J ALU

0

K ALU K-RF

31

J-RF

31

External Port

DMA

两个计算模块

128b

128b Proc El X

0

Peripherals

位举例

• 右移8位算术移位举例。 Rm包含右移的位数 (-8) Rs = ASHIFT Rn BY Rm Shift value = -8

Rm xxxx xxxx xxxx xxxx xxxx xxxx x111 1000 0xFFFFFFF8

Rn

1001 0010 0011 0100 0101 0110 1110 1111

整数ALU – 寻址方式

• 直接: – YR1:0=L[ J31+0x00015F00] (用J31作为总是包含零的寄存器) (长字传输) • 带更新和寄存器偏移量的间址后修正 : – YR20=[ J1+=J2] • 带更新和8位立即数偏移量的间址修正: – Q[K1+=0xFC]=XYR1:0 ( 四字传输) • 带更新和寄存器偏移量的间址预修正: – J3:2=L[K1+K2] (长字传输) • 带更新和立即数偏移量的间址预修正: – YR3:2=L[K1+0x0003333]

• 一个新的DMA插入到当前的链中

TCB 1 TCB 2

初始化 DMA链 (或者循环)

Chain Pointer

Chain Pointer

TCB 1A TCB 1 Chain Pointer Chain Pointer Chain Pointer TCB 2

插入DMA的TCB 寄存器数据。 这个数据可以在 TCB链加载期间 加载到TCB寄存 器中

流水操作(1)

寄存器的相关性要插入stall周期 例子: 1) R2 = [ j2 + j5];; // stall 3) R7 = R2 + R1;;

// stall

4) R8 = R7 - R0;; 5) R9 = R7 - R0;;

6) R5 = R7 - R8;;

流水操作(2)

汇编语言手动循环展开公式: a[i] = b[i]*c[i], d = d+a[i];

0x923456EF

Sign extended MSBs

Rs

1110 1111 deleted LSBs 0xFF923456 1111 1111 1001 0010 0011 0100 0101 0110

Shift right by 8 bits

Arithmetic left shift is identical to Logical left shift

ALU

Mult Shift

R F

ALU

Mult Shift

M0

M1

M2

内部储存器

31

31

ALU 指令举例

• LR5:4 = R11:10 + R1:0;; // 64-位加,在 CBX和 CBY中执行 • ySR1:0 = R31:30 + R25:24;;//四个短字操作数同时相加,存 储 //到两个寄存器对中,仅在CBY中 // 执行 • xR3 = R5 AND R7;; // CBX中的逻辑 AND 操作 • yR4 = SUM SR3:2;; // R4中短字与 yR3:2中的 内容相加 // 把和放到 R4中 • R9 = R4+R8, R2 = R4-R8;; // 同时加/减, // 在CBX 和 CBY中执行

0x00000004 0x123456EF 0x0123456E

Zero fill bits in MSBs Rs 0000 0001 0010 0011 0100 0101 0110 1110 Shift right by 4 bits

Rs

0010 0011 0100 0101 0110 1110 1111 0000 0x23456EF0 Shift left by 4 bits Zero fill bits in LSBs

N STALLs lc0 = N; loop_begin: r3 = r0*r1; r1:0 =[j0+=2];; STALL r4 = r4+r3;; loop_end: 1 STALL lc0 = N/2;; loop_begin: r3 = r0*r1; r1:0 = l[j0+=2];; r8 = r6*r7; r7:6 = l[j0+=2];; r4 = r4 + r3;; r5 = r5 + r8;; loop_end: STALL r4 = r4 + r5;;

移位器操作-位段处理 (III)

• 从Rn中抽取一个8位字段(FEXT),从 6th 位复制并放在 Rs中的 LSBs。 – Rs = FEXT Rn By Rm; Start at bit 5 Length 8 bits 31 15 8 0 Rm xxxx xxxx xxxx xxxx 0000 0101 x000 1000 0x00000508 bit 5 31 15 0 xxxx xxxx xxxx xxxx 0001 0010 0011 0100 31 15 0 xxxx xxxx xxxx xxxx xxxx xxxx 1001 0001

DMA 传输

• DMA通过加载TCB启动 • 当计数值减小到0时DMA传输完成。 (注意:启 动计数值 = 0 传输 0x10000个字) • 链插入

– – – – – 通过DCNT寄存器停止DMA 在TCB中建立链 建立链式 TCB 通过DCNT 重新启动DMA DMA从它停止的地方继续

DMA 传输 –链插入