第五章 常用Verilog语法之三

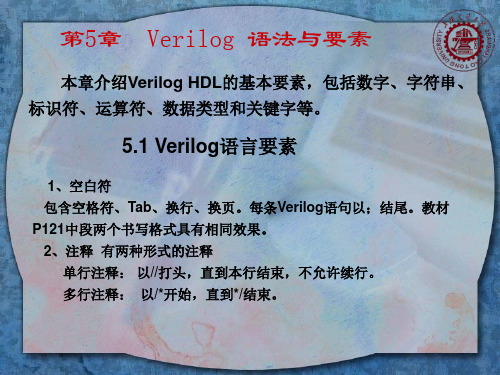

HDL第五章语法与要素

4、关键字 Verilog 系统内部使用的词,关键字用户不可用重定义其它含义。 所有的关键字都是小写字母组成。例如always是关键字,但是 ALWAYS不是关键字。

5. 2 常量

Verilog 中常量主要有三种类型:整数、实数、字符串 5.2.1 整数。 +/-<size>‟<base><value> +/-<二进制位宽>‟<进制><数字序列>

例如:8‟b1001xxxx

8‟b1010zzzz

与 8‟h9x相同

与 8‟haz相同

4)如果没有定义一个整数的位宽,则其宽度为响应数所需的二进制位。 例如:‟o721 // 9位二进制数111010001 „hAF //8位二进制数10101111 5)如果定义的位宽比实际的位数长,则通常左边添0补位,但如果数的 最左边为x或z,则左边添x或z。

wire [ 19:0] addrbus ;

//定义位宽 20位wire型变daddrbus

wire [0:7] a ; // 定义位宽为8位的wire型变量

2)tri型

功能与使用方法与wire型相同,只是为了增加程序的可读性,可更 清楚表示该信号综合后的电路具有三态的功能。 3)supply0 h和supply1型 supply0用于对“地”建模,即低电平0;supply1网用于对电源建 模,即高电平1;例如:

5.3 数据类型

数据类型是用来表示数字电路中的物理连线、数据存储和 传输单元等物理量。 Verilog HDL有下列四种逻辑值状态: 1) 0:低电平、逻辑0或逻辑非(“假”) 2) 1:高电平、逻辑1或“真”

3) x或X:不确定或未知的逻辑状态

verilog 基本语法

verilog 基本语法Verilog基本语法Verilog是一种硬件描述语言,用于描述数字电路的行为和结构。

它具有强大的建模能力,能够描述复杂的数字系统,并用于逻辑设计和硬件验证。

本文将介绍Verilog的基本语法,以帮助读者对这种语言有一个基本的了解。

1. 模块声明在Verilog中,所有的设计都是通过模块来实现的。

模块是Verilog 的基本组织单位,类似于其他编程语言中的函数或类。

模块声明由关键字module开头,后面跟着模块的名称和输入输出端口的定义。

例如:module my_module(input a, b, output c);// 模块的主体endmodule2. 端口声明在模块声明中,使用关键字input和output来声明输入和输出端口。

输入端口用于接收信号,输出端口用于输出信号。

端口可以是单个的信号,也可以是信号的数组。

例如:input a, b; // 单个输入端口output c; // 单个输出端口input [7:0] d; // 输入信号的数组3. 信号声明在Verilog中,使用关键字wire、reg、integer等来声明信号。

wire用于声明连续的信号,reg用于声明时序的信号,integer用于声明整数变量。

例如:wire a, b; // 连续信号reg [7:0] c; // 时序信号,有8位integer d; // 整数变量4. 时钟和复位在数字电路中,时钟和复位信号是非常重要的。

在Verilog中,可以使用关键字input来声明时钟和复位信号,并在模块的输入端口中定义。

例如:input clk; // 时钟信号input rst; // 复位信号5. 运算符Verilog支持各种运算符,包括算术运算符、逻辑运算符、位运算符等。

算术运算符用于执行加减乘除等操作,逻辑运算符用于执行与或非等逻辑操作,位运算符用于执行位操作。

例如:a =b + c; // 加法运算d = ~(a & b); // 与运算和非运算6. 控制结构在Verilog中,可以使用if语句、case语句等控制结构来实现条件判断和多路选择。

Verilog语法简易教程

语法--变量赋值

• 在Verilog中,变量是不能随意赋值的,必 须使用赋值运算符才可以进行赋值。其中 assign称为连续赋值,对应于线网类型变量 wire;initial或always称为过程赋值,对应 于寄存器类型变量reg。下面作具体讲解

语法--assign与wire

• 首先列个例子: wire a; assign a=1’b1; • 可以看出,语法格式就是这么简单,如下: assign 线网型变量名=赋值表达式; • 需要理解的是,assign称为连续赋值的意思 是,等号右端赋值表达式的值会持续对被 赋值变量产生连续驱动,而且只要等号右 端赋值表达式的值改变,左端被赋值变量 的值就会立即改变。对应到电路中去,就 是导线。

拼接运算符与重复操作符

• 拼接运算符是将两个或多个信号的某些位 拼接起来成为一个整体数据的运算操作, 其格式为:{s1,s2,…,sn}; 举例如下: z[3:0]={a,b,c,d}; shr[15:0]={shr[14:1],b,c}; • 重复操作符为{{}},即双重花括号,提供复 制一个常量或变量的简便记法,如: {3{2'b01}}=6'b010101;

语法--条件语句case

当几个分支对应的操作相同时,可以将这些分支放 在一起,如: reg [2:0] cnt; case(cnt) 3'b000,3'b001,3'b010:q=q+1; 3'b011,3'b100:q=q+2; default:q=q; endcase

• 另外,同else一样,default一般不要缺省。

• 触发事件有两种,这是由硬件电路决定的,在数电中已经学过:电平 触发,边沿触发。

verillog语法

verillog语法

Verilog是一种硬件描述语言,用于描述数字电路和系统。

以下是Verilog 的基本语法:

1. 注释:Verilog中的注释以“//”开头,一直延续到该行的末尾。

另外,多行注释以“/”开始,以“/”结束。

2. 数字表达方式:在Verilog中,数字的表示方式可以是十进制、八进制或二进制。

例如,8'b表示一个8位的二进制数。

3. 数据类型:Verilog中有四种数据类型,分别是wire(线网型)、reg (寄存器型)、integer(整数型)和parameter(参数型)。

其中,wire 类型用于表示物理连线,reg类型表示数据存储单元。

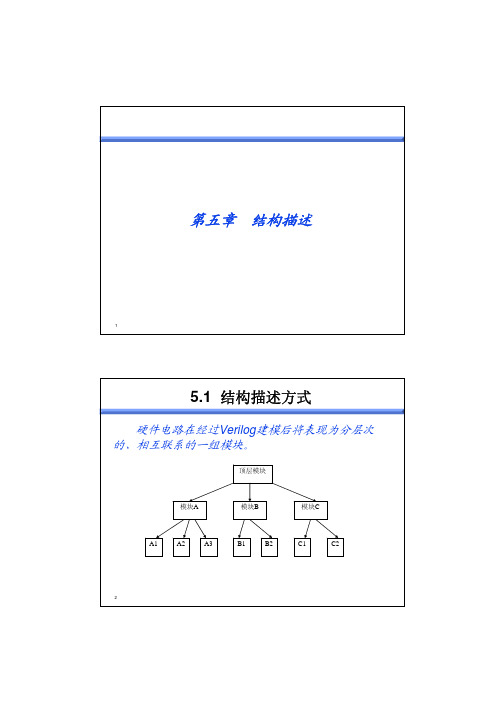

4. 模块:Verilog中的模块是电路的基本单元,由输入、输出和内部信号组成。

模块的端口用于连接外部信号,内部信号用于描述电路的行为。

5. 语句:Verilog中的语句可以分为赋值语句、控制语句和过程语句。

赋值语句用于给变量赋值,控制语句用于控制流程,过程语句用于描述电路的行为。

6. 任务和函数:Verilog中的任务和函数用于实现特定的功能。

任务和函数的使用可以减少代码的重复,提高代码的可维护性。

7. 系统任务和系统函数:系统任务和系统函数是Verilog提供的用于实现特定系统级功能的任务和函数。

例如,$display系统任务用于在仿真时显示信息。

以上是Verilog的基本语法,当然还有更多的语法和概念需要学习和掌握。

建议查阅相关的Verilog教程或书籍,以深入了解Verilog的语法和用法。

Verilog模块与基本语法

用实例元件

and #2 ul (q,a,b); 用 always块

always @(posedge clk or clr) begin if (clr) q <=0; else if (en)q <=d; end

组合逻辑

时序逻辑 组合逻辑

在字符串中可用 C 语言中的各种格式控制符

如:\t, \”, \\…

在字符串中可用 C 语言中的各种数值型式控制符(有些不同)

如:%b二进制%o八进制%d

十进制

%h

十六进制

%t

时间类型

%s

字符串类型

23

Verilog设计

特殊字符表示 \n \t \\

\ooo

%%

意义 换行符 Tab键 符号\ 3位8进制数表示符的ASCII

I/O声明

• 输入口: input [信号位宽-1: 0] 端口名i; • 输出口: output [信号位宽-1: 0] 端口名j; • 输入/输出口: inout [信号位宽-1: 0] 端口名k;

此为VerilogHDL-1995标准 风格

6

Verilog设计

2.1 模块结构—— 端口和I/O声明

a d

b Block1

c

e

思考:如果设计修改添加了若干 端口,“端口命名法”的优势…

Block1 dut1(in_a, in_b, in_c, ou_d, ou_e);

方法2:

Block1 dut2(.a(in_a), .d(ou_d), .b(in_b));

比较:方法2不必严格按照端口的顺序对应,提高了程序 的可读性和可移植性;

verilog语言05

31

5.3

当两个 driven strength不同的 net 相连时,会以 strength level 较高的 net 输出为结果。

Pull 1 Strong 0 Supply 1 Supply 1 Large 1 Strong 0

32

5.3

[例1]四选一多路选择器

33

5.3

module mux4_to_1(out, i0,i1, i2, i3, s1, s0); output out; input i0,i1, i2, i3, s1, s0; //门级实例引用 not (s1n, s1); not (s0n, s0); and (y0, i0, s1n, s0n); and (y1, i1, s1n, s0); and (y2, i2, s1, s0n); and (y3, i3, s1, s0); or (out, y0, y1, y2, y3); endmodule

demo_para #(4,5,6) g1(out, in1, in2);

18

…… endmodule

5.2

注意: 参数值列表中各个参数值的排列次序必须与被调用模块中 各个参数的说明次序保持一致;同时参数的个数也必须相 同; 在只希望对调用模块内的个别参数进行更改的情况下,所 有无需更改的参数值也必须按对应参数的顺序在参数值列 表中全部列出(照抄原值);

15

5.2

实例

module bottom(in); input in; always @(posedge in) begin: keep reg hold; hold=in; end endmodule module middle(stim1,stim2); input stim1,stim2; bottom amod(stim1), bmod(stim2); endmodule 16 module top; reg stim1,stim2; middle a(stim1,stim2); endmodule 模块名:top top.a top.a.bmod

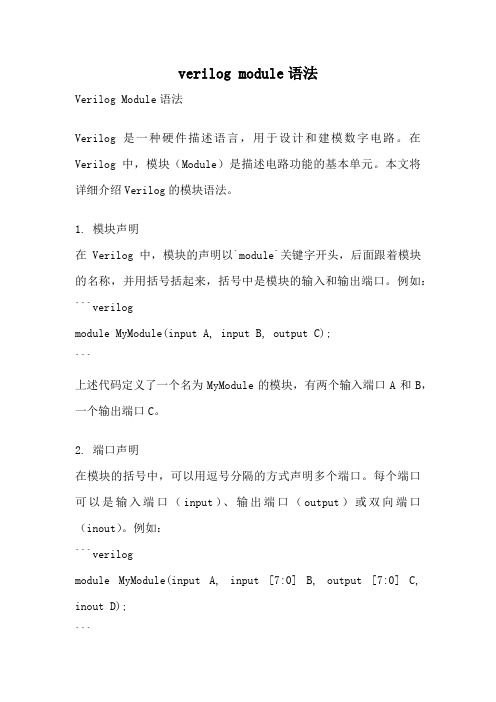

verilog module语法

verilog module语法Verilog Module语法Verilog是一种硬件描述语言,用于设计和建模数字电路。

在Verilog中,模块(Module)是描述电路功能的基本单元。

本文将详细介绍Verilog的模块语法。

1. 模块声明在Verilog中,模块的声明以`module`关键字开头,后面跟着模块的名称,并用括号括起来,括号中是模块的输入和输出端口。

例如:```verilogmodule MyModule(input A, input B, output C);```上述代码定义了一个名为MyModule的模块,有两个输入端口A和B,一个输出端口C。

2. 端口声明在模块的括号中,可以用逗号分隔的方式声明多个端口。

每个端口可以是输入端口(input)、输出端口(output)或双向端口(inout)。

例如:```verilogmodule MyModule(input A, input [7:0] B, output [7:0] C, inout D);```上述代码中,A是一个输入端口,B是一个8位输入端口,C是一个8位输出端口,D是一个双向端口。

3. 内部信号声明在模块中,可以声明内部信号(wire或reg),用于在模块内部进行信号传输或存储。

例如:```verilogmodule MyModule(input A, input B, output C);wire D;reg [7:0] E;// 省略其他代码endmodule```上述代码中,D是一个wire类型的内部信号,E是一个8位reg类型的内部信号。

4. 逻辑表达式在模块中,可以使用逻辑运算符和条件语句来实现电路的逻辑功能。

例如:```verilogmodule MyModule(input A, input B, output C);wire D;assign D = A & B;always @(posedge D)C <= ~C;endmodule```上述代码中,使用`&`逻辑与运算符计算A和B的与运算结果,并将结果赋值给D。

verilog基本语法

verilog基本语法

1. 模块:verilog模块用于描述感兴趣的功能系统以及设备行为,从而给出输入和输出之间的关系。

2. 变量:verilog中的变量可以定义为硬件控制的行为或信号路径。

3. 宏定义:verilog使用宏`define`来定义新的字符或文本,可用于

提高程序可读性和管理性。

4. 注释:verilog支持两种注释形式,即行注释和块注释,行注释以

`//`开头,块注释以`/*`开头,以 `*/`结尾。

5. 关键字:verilog使用了一系列关键字来指定硬件控制行为,输入、输出、时序延迟和引用等。

6. 命令:verilog提供了一系列命令来描述功能,包括`initial`,

`always`,`@`和`begin`等等。

7. 模型:verilog中的模型用于定义和控制硬件的输入和输出行为,

这些模型可以被定义为多个状态和条件的序列。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

module ripple_adder(co,sum,a0,a1,ci); parameter N=4; output[N-1:0] sum; output co; input[N-1:0] a0,a1; input ci; wire[N:0] carry; assign carry[0]=ci; genvar i; generate for(i=0;i<N;i=i+1) begin:r_loop wire t1,t2,t3; xor g1(t1,a0[i],a1[i]); xor g2(sum[i],t1,carry[i]); and g3(t2,a0[i],a1[i]); and g4(t3,t1,carry[i]); or g5(carry[i+1],t2,t3); end endgenerate assign co=carry[4]; endmodule

1/12/2017

8

第五讲 常用Verilog语法之三

注意if与else的配对关系,else总是与它上面 的最近的if配对。如果if与else的数目不一样, 为了实现程序设计者的意图,可以用 begin_end块语句来确定配对关系。

1/12/2017

9

第五章 常用Verilog语法之三

case语句——多分支选择语句

对矢量中的多个位进行重复操作 进行多个模块的实例引用的重复操作 根据参数的定义确定程序中是否应该包含某段 Verilog代码; 生成语句必须用在module内部,用来生成该 module内部的程序代码

生成块

生成实例可以包含以下的一个或多种类型

模块(module instance) 用户定义原语;(primitive instance) 门级原语; 连续赋值语句; initial和always块;(procedural block) task 和funciton

1/12/2017

2

第五章 常用Verilog语法之三

条件语句——if-else

if (表达式1) 语句1; else if (表达式2) 语句2; else if (表达式3) 语句3; …. else if (表达式m) 语句m; else 语句n;

1/12/2017

3

第五章 常用Verilog语法之三

endmodule

5.2 循环语句

forever:连续的执行语句 repeat:连续执行一条语句n次 while: 执行一条语句直到某个条件不满足 for循环

1/12/2017

30

5.2 循环语句

forever:连续的执行语句,用于产生周期性波 形,必须写在initial块中。 forever 语句; or forever begin 多条语句; end

18

1/12/2017

19

第五章 常用Verilog语法之三

使用条件语句不当,在设计中生成了原本没想 到的锁存器

不正确使用if语句

1/12/2017

20

q$latch

PRE

d al

D ENA CLR

Q

q

第五章 常用Verilog语法之三

使用条件语句不当在设计中生成了原本没想到 的锁存器

1/12/2017 4

1/12/2017

5

第五章 常用Verilog语法之三

说明

条件语句必须在过程块语句中使用,即由initial和 always语句引导的执行语句集合。除这两种块语 句引导的“begin-end”块中可以编写条件语句外, 模块的其他地方都不能编写。

1/12/2017

6

第五章 常用Verilog语法之三

1/12/2017

34

1/12/2017

35

5.2 循环语句

for循环语句 for(表达式1;表达式2;表达式3) 语句;

for(循环变量赋初值;循环结束条件;循环变量 增值);

1/12/2017

36

5.2 循环语句

for循环相当于采用while语句建立以下循环结构 begin 循环变量赋初值; while(循环结束条件) begin 执行语句; 循环变量增值; end end

对于xor,相当于生成以下语句 xor_loop[0].g1, xor_loop[1].g1, ... xor_loop[31].g1,

生成语句

生成块的本质是使用循环内的一条语句来代替多条重 复的Verilog语句,简化用户的编程。 关键词genvar用于声明生成变量,只能用在生成块 中,在仿真过程中,生成变量是不存在的 循环生成语句可以嵌套使用,不过使用同一个生成变 量作为索引的循环生成语句不能够相互嵌套; Xor_loop是循环生成语句的名字,目的在于通过它 对循环生成语句中的变量进行层次化引用。因此,循 环生成的各个异或门的相对层次名为: xor_loop[0].g1 , xor_loop[1].g1 , xor_loop[2].g1 ,….,

生成块

编写代码时必须在模块中说明生成的实例范 围,关键字generate——endgenerate 用来指定该范围。 Verilog允许在生成范围内声明下列数据类型

net(网络)、reg(寄存器); integer, real, time, realtime event(事件)

1/12/2017

13

1/12/2017

14

第五章 常用Verilog语法之三

每个case分项分支表达式值必须不同,否则 会出现矛盾。 执行完case分项后的语句,则跳出该case语 句结构,终止case语句的执行; 在用case语句表达式进行比较的过程中,只 有当信号的对应位的值能明确进行比较时,比 较才能成功; case语句的所有表达式值的位宽必须相等;

1/12/2017 15

casez:不考虑高阻z的比较过程; casex: 不考虑高阻z和不定值x的比较过程;

1/12/2017

16

1/12/2017

17

第五章 常用Verilog语法之三

casez:不考虑高阻z的比较过程; casex:不考虑高阻z和不定值x的比较过程;

1/12/2017

生成的数据类型具有唯一的标识名,可以被 层次引用,也可以使用defparam声明的参数 重新定义

生成块

任务和函数的声明也允许出现在生成范围之 中,但不能出现在循环生成当中。 任务和函数具有唯一的标识符名称,可以被 层次引用。 不允许出现在生成范围之中的模块项声明包 括

参数、局部参数; 输入、输出和输入/输出声明; 指定块。

说明

If后面都有表达式,为逻辑表达式或关系表达式。系统 对表达式的值进行判断,若为0,x,z,按假处理;若 为1,按真处理,执行指定的语句。 else前面有一分号,整个语句结束有一分号

if和else后面可以包含一个内嵌的操作语句,也可以有 多个操作语句,此时用begin和end这两个关键词将几 个语句包含起来成为一个复合块语句,此时end之后无需 分号;

不正确使用case语句,缺少default语句。

1/12/2017

26

Equal0

Selector0

sel[1..0]

2' h0 --

A[1..0] OUT B[1..0]

WideNor0

EQUAL

SEL[2..0] OUT

q

Equal1

1' h0 --

பைடு நூலகம்

DATA[2..0]

A[1..0] 2' h3 -OUT B[1..0] SELECTOR

always @(s1 or s0 or i0 or i1 or i2 or i3) begin case({s1,s0}) 2'b00: out=i0; 2'b01: out=i1; 2'b10: out=i2; 2'b11: out=i3; default: out=1'bx; end case end

说明

允许一定形式的表达式简写方式。 if(expression) 等价于 if(expression==1) if(!expression) 等价于 if(expression!=1)

1/12/2017

7

第五章 常用Verilog语法之三

说明

If语句的嵌套。 if(expression1 ) if(expression2) 语句1; else 语句2; else if(expression3 ) 语句3; else 语句4;

生成语句的基本结构

生成块

Verilog中有3种创建生成语句的方法

循环生成; 条件生成; case声成。

生成语句的基本结构

循环生成语句

module bitwise_xor(out,i0,i1);

parameter N=32; output[N-1:0] out; input[N-1:0] i0,i1; genvar j; generate for(j=0;j<N;j=j+1) begin:xor_loop xor g1(out[j],i0[j],i1[j]); end endgenerate endmodule

case(表达式) <case分支项> endcase casez(表达式) <case分支项> endcase casex(表达式) <case分支项> endcase case分支项的一般格式: 分支表达式: 语句; default: 语句;

1/12/2017

12

第五章 常用Verilog语法之三

EQUAL

a b

第五章 常用Verilog语法之三