Verilog基本语法

verilog基本语法

Verilog基本语法【逻辑值】➢逻辑0 表示低电平,GND➢逻辑1 表示高电平,VCC➢逻辑X 表示未知电平,可能是高电平,也可能是低电平➢逻辑Z 表示高阻态,外部没有激励信号,是一个悬空状态注:高阻态的实质:电路分析时高阻态可做开路理解。

可以把它看作输出(输入)电阻非常大,对下级电路无任何影响。

若为0、x、z则按照假处理;若为1,按真处理。

【进制】➢二进制4'b0101 —4位二进制数0101➢十进制数4’d2 —4位十进制数2➢十六进制数4’ha —4位十六进制数aVerilog中若不指定位宽,默认32位;若不指定位宽不指定进制,默认32位宽的十进制数。

【标识符】标识符可以是字母、数字、$和_(下划线)的组合,且开头必须是字母或下划线,区分大小写。

不建议大小写混合使用。

【数据类型】➢寄存器关键字reg,默认初始值位不定值X;reg[31:0] delay_cnt; //[31:0],指定寄存器位宽32位,reg key_reg; // 默认位宽为1.reg类型数据只能在always和initial语句中被赋值。

➢线网表示结构实体的物理连线,包括wire和tri类型➢参数常量,用parameter定义。

parameter H_SYNC = 11'd41;【运算符】➢[条件操作符] ?:例,a?b:c //如果a为真就选b,否则选择c。

result=(a>=b)?a:b;[逻辑运算符] !&& ||[位运算符] ~ & | ^(按位异或)a&b; //自动将位宽小的数高位补零至较大数的位宽,然后按位与操作。

[移位运算符] << >> 用0填补移出的空位。

左移时位宽增加,右移位宽不变。

[位拼接运算符] {}例,{a,b} //将a和b拼接起来,作为一个新信号,a为高位。

c={a,b[3:0]}; //a、b位宽均为8位,c为8+4=12位。

verilog 基本语法

verilog 基本语法Verilog基本语法Verilog是一种硬件描述语言,用于描述数字电路的行为和结构。

它具有强大的建模能力,能够描述复杂的数字系统,并用于逻辑设计和硬件验证。

本文将介绍Verilog的基本语法,以帮助读者对这种语言有一个基本的了解。

1. 模块声明在Verilog中,所有的设计都是通过模块来实现的。

模块是Verilog 的基本组织单位,类似于其他编程语言中的函数或类。

模块声明由关键字module开头,后面跟着模块的名称和输入输出端口的定义。

例如:module my_module(input a, b, output c);// 模块的主体endmodule2. 端口声明在模块声明中,使用关键字input和output来声明输入和输出端口。

输入端口用于接收信号,输出端口用于输出信号。

端口可以是单个的信号,也可以是信号的数组。

例如:input a, b; // 单个输入端口output c; // 单个输出端口input [7:0] d; // 输入信号的数组3. 信号声明在Verilog中,使用关键字wire、reg、integer等来声明信号。

wire用于声明连续的信号,reg用于声明时序的信号,integer用于声明整数变量。

例如:wire a, b; // 连续信号reg [7:0] c; // 时序信号,有8位integer d; // 整数变量4. 时钟和复位在数字电路中,时钟和复位信号是非常重要的。

在Verilog中,可以使用关键字input来声明时钟和复位信号,并在模块的输入端口中定义。

例如:input clk; // 时钟信号input rst; // 复位信号5. 运算符Verilog支持各种运算符,包括算术运算符、逻辑运算符、位运算符等。

算术运算符用于执行加减乘除等操作,逻辑运算符用于执行与或非等逻辑操作,位运算符用于执行位操作。

例如:a =b + c; // 加法运算d = ~(a & b); // 与运算和非运算6. 控制结构在Verilog中,可以使用if语句、case语句等控制结构来实现条件判断和多路选择。

veriloga基础语法

veriloga基础语法VerilogA是一种硅谷团队开发的建模语言,它被广泛应用于集成电路(IC)的设计和仿真中。

本文旨在介绍VerilogA的基础语法。

1. 模块声明在VerilogA中,每个模块都需要进行声明。

声明的语法如下:module 模块名(输入端口1,输入端口2,...输入端口n,输出端口1,输出端口2,...输出端口m);<模块定义代码>endmodule其中,模块名可以由字母、数字和下划线组成,不能以数字开头;输入端口和输出端口可以是标量或向量。

2. 参数声明VerilogA允许在模块中声明参数,以便在实例化时进行配置。

语法如下:parameter 参数名 = 值;参数可以通过assign语句进行连接,也可以在实例化时进行配置。

3. 变量声明在VerilogA中,可以使用不同的变量类型进行声明,如实数、整数、布尔值等。

real: 实数类型,用于存储实数值。

integer: 整数类型,用于存储整数值。

boolean: 布尔类型,用于存储真/假值。

语法如下:real 变量名;integer 变量名;boolean 变量名;4. 函数和任务在VerilogA中,可以使用函数和任务来实现特定的功能。

函数是一段可重用的代码,它接收输入参数并返回一个值。

函数的语法如下:function 返回类型函数名(输入参数);<函数定义代码>return 返回值;endfunction任务是一段可重用的代码,不返回值,但可以通过参数进行输入和输出。

任务的语法如下:task 任务名(输入参数);<任务定义代码>endtask5. 运算符VerilogA支持各种常见的数学和逻辑运算符,如加减乘除、取余、与或非等。

加法运算符:+减法运算符:-乘法运算符:*除法运算符:/取余运算符:%与运算符:&&或运算符:||非运算符:!6. 控制结构在VerilogA中,可以使用if-else、for、while等控制结构来实现条件判断和循环。

Verilog-HDL中的基本语法

一个完整的源程序都应当加上需要的注释, 以加强程序的可读性。

2.2 Verilog HDL的语法

2.2.1 空白符和注释

Verilog HDL的空白符包括空格、tab符号、换行 和换页。

空白符如果不是出现在字符串中,编译源程序 时将被忽略。

8. 条件操作符(Conditional operators)

条件操作符为:?:

条件操作符的操作数有3个,其使用格式为

操作数 = 条件 ? 表达式1:表达式2;

即当条件为真(条件结果值为1)时,操作数 = 表达式1;为假(条件结果值为0)时,操作数 = 表达 式2。

9. 位并接操作符(Concatenation operators) 并接操作符为:{} 并接操作符的使用格式: {操作数1的某些位,操作数2的某些位,…,操作数n 的某些位};

位运算操作符包括:~(按位取反)、&(按位与)、 |(按位或)、^(按位异或)、^~或~^(按位同或)。

在进行位运算时,当两个操作数的位宽不同时, 计算机会自动将两个操作数按右端对齐,位数少的操 作数会在高位用0补齐。

4. 关系操作符(Pelational operators)

关系操作符有:

<(小于)、<=(小于等于)、>(大于)、>=(大 于等于)。

② 每个模块首先要进行端口定义,并说明输入 (input)、输出(output)或双向(inouts),然 后对模块的功能进行逻辑描述。

③ Verilog HDL程序的书写格式自由,一行可以一 条或多条语句,一条语句也可以分为多行写。

④ 除了endmodule语句外,每条语句后必须要有 分号“;”。

veriloga语法 electrical

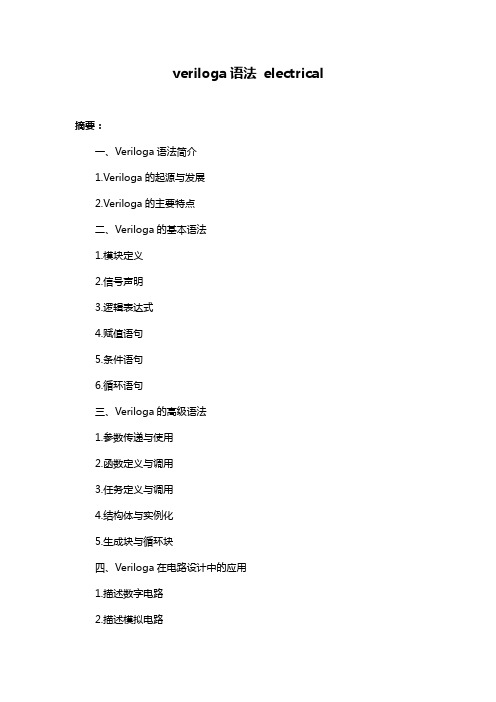

veriloga语法electrical摘要:一、Veriloga语法简介1.Veriloga的起源与发展2.Veriloga的主要特点二、Veriloga的基本语法1.模块定义2.信号声明3.逻辑表达式4.赋值语句5.条件语句6.循环语句三、Veriloga的高级语法1.参数传递与使用2.函数定义与调用3.任务定义与调用4.结构体与实例化5.生成块与循环块四、Veriloga在电路设计中的应用1.描述数字电路2.描述模拟电路3.混合信号电路设计4.验证与仿真五、Veriloga与其他语言的比较1.Veriloga与Verilog的比较2.Veriloga与VHDL的比较3.Veriloga在实际项目中的应用优势正文:Veriloga是一种基于Verilog的硬件描述语言,它继承了Verilog的优点,并在此基础上进行了改进与拓展。

Veriloga的语法结构清晰,易于学习,被广泛应用于电路设计与验证领域。

一、Veriloga语法简介Veriloga起源于2001年,由Cadence公司推出,以满足日益复杂的电路设计需求。

它具有语法简洁、可读性强、设计效率高等特点,逐渐成为硬件描述语言领域的一股新兴力量。

二、Veriloga的基本语法1.模块定义在Veriloga中,一个设计可以被划分为多个模块。

模块定义的基本格式如下:```module module_name (input wire clk,input wire rst,output reg [7:0] data_out);```其中,`module_name`为模块名称,`clk`和`rst`为时钟和复位信号,`data_out`为输出信号。

1.信号声明信号声明用于定义模块内的信号,包括输入、输出和寄存器。

信号声明的基本格式如下:```input wire clk;input wire rst;output reg [7:0] data_out;```1.逻辑表达式Veriloga支持各种逻辑运算,如与(`&`)、或(`|`)、非(`~`)等。

Verilog 常用语法及举例

常用语句之五 for

for (i == 0; i< 100 ; i= i+1)

1,用于循环语句中。 2,循环次数必须是个常量。 3,i为integer(整型)类型。

小练习

1,分频电路设计,设计一个8分频。 2,设计一个0~23的计数器,在数码管上显示出来。 3,改进上述计数器,增加一个拨码输入,当拨码 为0时,数码管上显示一个固定值。当拨码为1时, 计数器继续计数。 4,按键去抖设计。每按键一次,数码管显示加1。 5,电子密码锁设计。

阻塞赋值与非阻塞赋值

阻塞赋值用在组合逻辑中。在always中使用 符号 = 非阻塞赋值用在时序逻辑中。在always中使 用符号 <=

阻塞赋值与非阻塞赋值

阻塞赋值 always @ (a,b,c) begin b = a; c = b; end

a

a

非阻塞赋值

always @ (posedge clk) begin b <= a; c <= b; end

常用语句之三 begin end

If (a == b)

begin c <= d; e <= f; g <= h; end 1,begin—end里面的所 有语句都是顺序执行。

常用语句之四 assign

assign a = b & c; assign a = (d ==1’b0) ? 0 : 1;

a b c b c

组合逻辑和时序逻辑

时序逻辑

时序逻辑需要时钟,输入变化不会引起输出立即变化。 而是要参考时钟沿的变化。 只能用非阻塞赋值的always语句实现。 结果会生产寄存器。

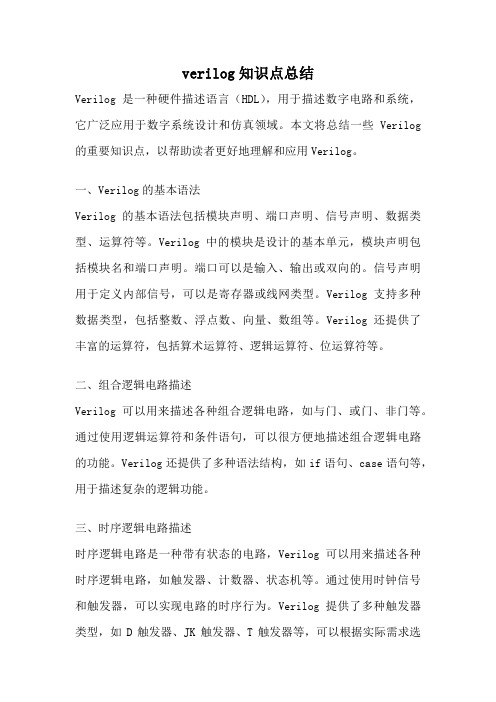

verilog知识点总结

verilog知识点总结Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统,它广泛应用于数字系统设计和仿真领域。

本文将总结一些Verilog 的重要知识点,以帮助读者更好地理解和应用Verilog。

一、Verilog的基本语法Verilog的基本语法包括模块声明、端口声明、信号声明、数据类型、运算符等。

Verilog中的模块是设计的基本单元,模块声明包括模块名和端口声明。

端口可以是输入、输出或双向的。

信号声明用于定义内部信号,可以是寄存器或线网类型。

Verilog支持多种数据类型,包括整数、浮点数、向量、数组等。

Verilog还提供了丰富的运算符,包括算术运算符、逻辑运算符、位运算符等。

二、组合逻辑电路描述Verilog可以用来描述各种组合逻辑电路,如与门、或门、非门等。

通过使用逻辑运算符和条件语句,可以很方便地描述组合逻辑电路的功能。

Verilog还提供了多种语法结构,如if语句、case语句等,用于描述复杂的逻辑功能。

三、时序逻辑电路描述时序逻辑电路是一种带有状态的电路,Verilog可以用来描述各种时序逻辑电路,如触发器、计数器、状态机等。

通过使用时钟信号和触发器,可以实现电路的时序行为。

Verilog提供了多种触发器类型,如D触发器、JK触发器、T触发器等,可以根据实际需求选择合适的触发器类型。

四、模块实例化和层次化设计Verilog支持模块的实例化和层次化设计,可以将一个模块实例化为另一个模块的一部分。

通过模块实例化,可以方便地实现模块的复用和层次化设计。

层次化设计可以使整个系统更加清晰和模块化,方便调试和维护。

五、仿真和验证Verilog可以用于对设计进行仿真和验证,以确保设计的正确性。

Verilog提供了仿真器,可以对设计进行时序仿真和波形查看。

通过仿真,可以验证设计的功能和时序行为是否符合要求。

Verilog 还支持测试向量的生成和自动验证,可以自动生成测试向量并进行自动验证。

Verilog基本语法

”This string formats a value: val = %b”

20

格式符

%h hex %o oct %d dec %b bin %c ACSII %s string %t time

转义符

\t tab \n 换行 \\ 反斜杠 \” \<1-3 digit octal number>

18

整数和实数常量小结

整数的大小可以定义也可以不定义。整数表示为:

数字中(_ )忽略,便于查看 没有定义大小(size)整数缺省为32位 /*特别注意*/ 缺省数基为十进制 数基(base)和数字(16进制)中的字母无大小写之分 当数值value大于指定的大小时,截去高位。如 2'b1101表示的是 2'b01

- 4. 功能定义:

assign d = a | x ; assign x = ( b & ~c ); endmodule

6

3.1.3 逻辑功能描述

两路选择器的RTL级描述1: module mux2to1 (out, a, b, sel); input a, b, sel; output out; wire out; assign out=(sel)?b:a; endmodule

13

3.2.1 术语及定义

1.空白符:空格、tabs及换行

2. 标志符(Identifier):Verilog中对象(如模块或信号)的名字 3.LSB:最低有效位(Lease significant bit) 4.MSB:最高有效位(Most significant bit)

14

3.2.2 空白符和注释

module MUX2_1 (out, a, b, sel); 单行注释 // Port declarations

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

18

整数和实数常量小结

整数的大小可以定义也可以不定义。整数表示为: 数字中(_ )忽略,便于查看 没有定义大小(size)整数缺省为32位 /*特别注意*/ 缺省数基为十进制 数基(base)和数字(16进制)中的字母无大小写之分 当数值value大于指定的大小时,截去高位。如 2'b1101表示的是 2'b01

13

3.2.1 术语及定义

1.空白符:空格、tabs及换行 2. 标志符(Identifier):Verilog中对象(如模块或信号)的名字 3.LSB:最低有效位(Lease significant bit) 4.MSB:最高有效位(Most significant bit)

14

3.2.2 空白符和注释

– include保存在文件中的全局的或经常用到的一些定义,如文本宏

– 在模块内部include一些任务(tasks),提高代码的可维护性。

26

3.2.10 文本替换`define (了解)

编译指导`define提供了一种简单的文本替换的功能 `define <macro_name> <macro_text>

多行注释,在/* */内

and and2 (b1, b, sel);

or or1 (out, a1, b1);

endmodule

15

3.2.3 Verilog采用的四值逻辑系统

‟0‟, Low, False, Logic Low, Ground,VSS, Negative Assertion

„1‟, High, True, Logic High, Power, VDD, VCC, Positive Assertion

21

3.2.6 标识符(identifiers) (重点)

标识符是用户在描述时给Verilog对象(电路模块、信号等)起的名字

标识符必须以字母(a-z, A-Z)或( _ )开头,后面可以是字母、数字、( $ )或( _ )。

最长可以是1023个字符

标识符区分大小写,sel和SEL是不同的标识符

- 2. 输入/输出说明 : input a, b, c ;

output d ;

-// 输入/输出端口信号类型声明,缺省为wire型 :

- 3. 内部信号:

wire x;

- 4. 功能定义:

assign d = a | x ;

assign x = ( b & ~c );

endmodule

6

3.1.3 逻辑功能描述

input a, b, sel; output out;

reg out;

always @( sel or a or b) if (! sel) out = a; else out = b;

endmodule

8

实例化(module instances): 1. 端口信息 2. 输入/输出说明 3. 逻辑功能描述(实例化实现功能描述)

22

有效标识符举例: shift_reg_a busa_index _bus3

无效标识符举例: 34net // 开头不是字母或“_” a*b_net // 包含了非字母或数字, “$” “_” n@238 //包含了非字母或数字, “$” “_”

Verilog区分大小写,所有Verilog关键词如module、 endmodule等都使用小写字母。

例如:

module MUX2_1 (out, a, b, sel);

output out;

input a, b, sel; wire sel_, a1, b1;

Verilog标识符

not not1 (sel_, sel); and and1 (a1, a, sel_); and and2 (b1, b, sel); or or1 (out, a1, b1); endmodule

23

3.2.7 系统任务及函数(了解)

使用方式:$<identifier> $符号指示这是系统任务和函数 系统函数有很多,如:

返回当前仿真时间$time 显示/监视信号值($display, $monitor) 停止仿真$stop 结束仿真$finish 如: $monitor($time, “a = %b, b = %h”, a, b);

编译指导`include在当前内容中插入一个文件

格式: `include “<file_name>” 如 `include "global.v"

`include "parts/count. v"

可以是相对路 径或绝对路径

`include "../../library/mux. v”

`include可用于:

在编译时<macro_text>替换<macro_name>。可提高描述的可读性。

`define not_delay #1 `define and_delay #2 `define or_delay #1 module MUX2_1 (out, a, b, sel); output out; input a, b, sel; wire sel_, a1, b1;

wire sel_, a1, b1;

/*The netlist logic selects input ”a” when sel = 0 and it selects ”b” when sel = 1. */ not not1 (sel_, sel); and and1 (a1, a, sel_);

10

练习:编写V空格中填入适当的符号 使其成为右图的Verilog 模块 :

module block1(a, b, —, —, — );

input —, —, —;

—— d, — ;

a

assign d = a | ( b & ~c) ;

b

assign e = ( b & ~c );

%h %o %d %b %c %s hex oct dec bin ACSII string

%t time

转义符

\t

\n

\\

\”

\<1-3 digit octal number>

tab 换行 反斜杠 双引号 ASCII representation of above

格式符%0d表示没有前导0的十进制数

module MUX2_1 (out, a, b, sel);

// Port declarations

单行注释

output out;

到行末结束

input sel; // control input

input b, a; /* data inputs */

格式自由

使用空白符提高可读性及代码组 织。Verilog忽略空白符除非用于 分开其它的语言标记。

c

_______

d e

11

练习答案:编写Verilog HDL模块

module block1(a, b, c, d, e ); input a, b, c; output d, e ; assign d = a | ( b & ~c) ; assign e = ( b & ~c );

endmodule

整数与实数常量例子

12

„h83a

8'b1100 0001 16'hff01 32'bz01x 3'b1010 1101

6.3 32e- 4 4.1E3

unsized decimal (zeroextended to 32 bits)

unsized hexadecimal (zeroextended to 32 bits)

可以使用一些格式符(如%b)在仿真时产生格式化输出: ”This is a normal string” ”This string has a \t tab and ends with a new line\n” ”This string formats a value: val = %b”

20

格式符

第3章 Verilog 基本语法

主要内容:

3.1 Verilog HDL基本模块说明 3.2 Verilog HDL中的词汇约定 3.3 Verilog HDL 数据类型 3.4 Verilog HDL 运算符

2

3.1 Verilog HDL基本模块说明

module是层 次化设计的基 本构件

逻辑描述放在 module内部 module能够表示:

实数常量 实数可用科学表示法或十进制表示 科学表示法表示方式: <尾数><e或E><指数>, 表示: 尾数×10指数

19

3.2.5 字符串(string)(了解)

Verilog中,字符串大多用于显示信息的命令中。(只用在测 试中!!!!)

字符串要在一行中用双引号括起来,也就是不能跨行。 字符串中可以使用一些转义(escape)符,如\t \n

当信号a或b的值发生变化时,系统任务$monitor显 示当前仿真时间,信号a值(二进制格式), 信号b值(16 进制格式)。

24

3.2.8 编译指导 (了解)

( `)符号说明一个编译指导 这些编译指导使仿真编译器进行一些特殊的操作 编译指导一直保持有效直到被覆盖或解除

25

3.2.9 文本包含`include (了解)

物理块,如IC或ASIC单元 逻辑块,如一个CPU设计的ALU部分 整个系统 每一个模块的描述从关键词module开始,有一个名称(如 SN74LS74,DFF,ALU等等),由关键词endmodule结束。