计算机体系结构部分课后习题答案-清华大学

计算机组成与结构第四版(王爱英著)清华大学出版社课后答案(全)

计算机的算术运算

单精度浮点数

1000 1111 1110 1111 1100 0000 0000 0000 S E F S =(-1)1=-1 E =00011111=3110 F’ =110+(110 1111 1100 0000 0000 0000)2

单精度浮点数=S×F’×2E

WANG Wei, Computer Organization and Architecture, Copyright 2004 TJU

若它分别表示如下所示的三种数,那么他们 的含义各是什么?

2的补码表示的整数 无符号整数 单精度浮点数

WANG Wei, Computer Organization and Architecture, Copyright 2004 TJU

计算机的算术运算

分析与解答:

2的补码表示的整数

(1000 1111 1110 1111 1100 0000 0000 0000)补 =(1111 0000 0001 0000 0100 0000 0000 0000)原 =-(111 0000 0001 0000 0100 0000 0000 0000) =-188011315210

WANG Wei, Computer Organization and Architecture, Copyright 2004 TJU

计算机的逻辑部件

+6

WANG Wei, Computer Organization and Architecture, Copyright 2004 TJU

计算机的逻辑部件

0100 0001 0010 1000 0000 0000 0000 0000

WANG Wei, Computer Organization and Architecture, Copyright 2004 TJU

计算机组成与系统结构课后答案全清华大学出版社袁春风主编

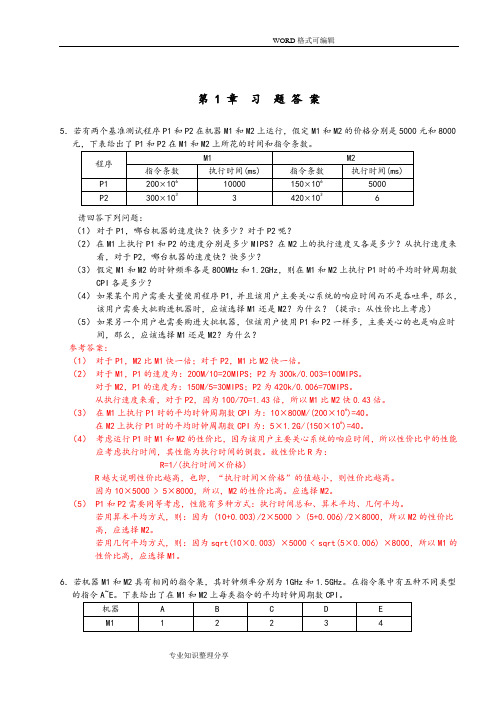

第1章习题答案5.若有两个基准测试程序P1和P2在机器M1和M2上运行,假定M1和M2的价格分别是5000元和8000元,下表给出了P1和P2在M1和M2上所花的时间和指令条数。

请回答下列问题:(1)对于P1,哪台机器的速度快?快多少?对于P2呢?(2)在M1上执行P1和P2的速度分别是多少MIPS?在M2上的执行速度又各是多少?从执行速度来看,对于P2,哪台机器的速度快?快多少?(3)假定M1和M2的时钟频率各是800MHz和1.2GHz,则在M1和M2上执行P1时的平均时钟周期数CPI各是多少?(4)如果某个用户需要大量使用程序P1,并且该用户主要关心系统的响应时间而不是吞吐率,那么,该用户需要大批购进机器时,应该选择M1还是M2?为什么?(提示:从性价比上考虑)(5)如果另一个用户也需要购进大批机器,但该用户使用P1和P2一样多,主要关心的也是响应时间,那么,应该选择M1还是M2?为什么?参考答案:(1)对于P1,M2比M1快一倍;对于P2,M1比M2快一倍。

(2)对于M1,P1的速度为:200M/10=20MIPS;P2为300k/0.003=100MIPS。

对于M2,P1的速度为:150M/5=30MIPS;P2为420k/0.006=70MIPS。

从执行速度来看,对于P2,因为100/70=1.43倍,所以M1比M2快0.43倍。

(3)在M1上执行P1时的平均时钟周期数CPI为:10×800M/(200×106)=40。

在M2上执行P1时的平均时钟周期数CPI为:5×1.2G/(150×106)=40。

(4)考虑运行P1时M1和M2的性价比,因为该用户主要关心系统的响应时间,所以性价比中的性能应考虑执行时间,其性能为执行时间的倒数。

故性价比R为:R=1/(执行时间×价格)R越大说明性价比越高,也即,“执行时间×价格”的值越小,则性价比越高。

计算机组成与系统结构课后答案全(清华大学出版社袁春风主编)之令狐文艳创作

第 1 章习题答案令狐文艳5.若有两个基准测试程序P1和P2在机器M1和M2上运行,假定M1和M2的价格分别是5000元和8000元,下表给出请回答下列问题:(1)对于P1,哪台机器的速度快?快多少?对于P2呢?(2)在M1上执行P1和P2的速度分别是多少MIPS?在M2上的执行速度又各是多少?从执行速度来看,对于P2,哪台机器的速度快?快多少?(3)假定M1和M2的时钟频率各是800MHz和1.2GHz,则在M1和M2上执行P1时的平均时钟周期数CPI各是多少?(4)如果某个用户需要大量使用程序P1,并且该用户主要关心系统的响应时间而不是吞吐率,那么,该用户需要大批购进机器时,应该选择M1还是M2?为什么?(提示:从性价比上考虑)(5)如果另一个用户也需要购进大批机器,但该用户使用P1和P2一样多,主要关心的也是响应时间,那么,应该选择M1还是M2?为什么?参考答案:(1)对于P1,M2比M1快一倍;对于P2,M1比M2快一倍。

(2)对于M1,P1的速度为:200M/10=20MIPS;P2为300k/0.003=100MIPS。

对于M2,P1的速度为:150M/5=30MIPS;P2为420k/0.006=70MIPS。

从执行速度来看,对于P2,因为100/70=1.43倍,所以M1比M2快0.43倍。

(3)在M1上执行P1时的平均时钟周期数CPI为:10×800M/(200×106)=40。

在M2上执行P1时的平均时钟周期数CPI为:5×1.2G/(150×106)=40。

(4)考虑运行P1时M1和M2的性价比,因为该用户主要关心系统的响应时间,所以性价比中的性能应考虑执行时间,其性能为执行时间的倒数。

故性价比R为:R=1/(执行时间×价格)R越大说明性价比越高,也即,“执行时间×价格”的值越小,则性价比越高。

因为10×5000 > 5×8000,所以,M2的性价比高。

计算机组成和系统结构课后答案解析版全(清华大学出版社_袁春风主编)

第 1 章习题答案5.若有两个基准测试程序P1和P2在机器M1和M2上运行,假定M1和M2的价格分别是5000元和8000请回答下列问题:(1)对于P1,哪台机器的速度快?快多少?对于P2呢?(2)在M1上执行P1和P2的速度分别是多少MIPS?在M2上的执行速度又各是多少?从执行速度来看,对于P2,哪台机器的速度快?快多少?(3)假定M1和M2的时钟频率各是800MHz和1.2GHz,则在M1和M2上执行P1时的平均时钟周期数CPI各是多少?(4)如果某个用户需要大量使用程序P1,并且该用户主要关心系统的响应时间而不是吞吐率,那么,该用户需要大批购进机器时,应该选择M1还是M2?为什么?(提示:从性价比上考虑)(5)如果另一个用户也需要购进大批机器,但该用户使用P1和P2一样多,主要关心的也是响应时间,那么,应该选择M1还是M2?为什么?参考答案:(1)对于P1,M2比M1快一倍;对于P2,M1比M2快一倍。

(2)对于M1,P1的速度为:200M/10=20MIPS;P2为300k/0.003=100MIPS。

对于M2,P1的速度为:150M/5=30MIPS;P2为420k/0.006=70MIPS。

从执行速度来看,对于P2,因为100/70=1.43倍,所以M1比M2快0.43倍。

(3)在M1上执行P1时的平均时钟周期数CPI为:10×800M/(200×106)=40。

在M2上执行P1时的平均时钟周期数CPI为:5×1.2G/(150×106)=40。

(4)考虑运行P1时M1和M2的性价比,因为该用户主要关心系统的响应时间,所以性价比中的性能应考虑执行时间,其性能为执行时间的倒数。

故性价比R为:R=1/(执行时间×价格)R越大说明性价比越高,也即,“执行时间×价格”的值越小,则性价比越高。

因为10×5000 > 5×8000,所以,M2的性价比高。

计算机组成与系统结构课后答案全清华大学出版社袁春风主编

第1章习题答案5.若有两个基准测试程序P1和P2在机器M1和M2上运行,假定M1和M2的价格分别是5000元和8000元,下表给出了P1和P2在M1和M2上所花的时间和指令条数。

请回答下列问题:(1)对于P1,哪台机器的速度快?快多少?对于P2呢?(2)在M1上执行P1和P2的速度分别是多少MIPS?在M2上的执行速度又各是多少?从执行速度来看,对于P2,哪台机器的速度快?快多少?(3)假定M1和M2的时钟频率各是800MHz和1.2GHz,则在M1和M2上执行P1时的平均时钟周期数CPI各是多少?(4)如果某个用户需要大量使用程序P1,并且该用户主要关心系统的响应时间而不是吞吐率,那么,该用户需要大批购进机器时,应该选择M1还是M2?为什么?(提示:从性价比上考虑)(5)如果另一个用户也需要购进大批机器,但该用户使用P1和P2一样多,主要关心的也是响应时间,那么,应该选择M1还是M2?为什么?参考答案:(1)对于P1,M2比M1快一倍;对于P2,M1比M2快一倍。

(2)对于M1,P1的速度为:200M/10=20MIPS;P2为300k/0.003=100MIPS。

对于M2,P1的速度为:150M/5=30MIPS;P2为420k/0.006=70MIPS。

从执行速度来看,对于P2,因为100/70=1.43倍,所以M1比M2快0.43倍。

(3)在M1上执行P1时的平均时钟周期数CPI为:10×800M/(200×106)=40。

在M2上执行P1时的平均时钟周期数CPI为:5×1.2G/(150×106)=40。

(4)考虑运行P1时M1和M2的性价比,因为该用户主要关心系统的响应时间,所以性价比中的性能应考虑执行时间,其性能为执行时间的倒数。

故性价比R为:R=1/(执行时间×价格)R越大说明性价比越高,也即,“执行时间×价格”的值越小,则性价比越高。

计算机组成与系统结构课后答案全(清华大学出版社-袁春风主编)

!第 1 章习题答案5.若有两个基准测试程序P1和P2在机器M1和M2上运行,假定M1和M2的价格分别是5000元和8000元,下表给出了P1和P2在M1和M2上所花的时间和指令条数。

请回答下列问题:(1)对于P1,哪台机器的速度快快多少对于P2呢(2)在M1上执行P1和P2的速度分别是多少MIPS在M2上的执行速度又各是多少从执行速度来看,对于P2,哪台机器的速度快快多少(3):(4)假定M1和M2的时钟频率各是800MHz和,则在M1和M2上执行P1时的平均时钟周期数CPI各是多少(5)如果某个用户需要大量使用程序P1,并且该用户主要关心系统的响应时间而不是吞吐率,那么,该用户需要大批购进机器时,应该选择M1还是M2为什么(提示:从性价比上考虑)(6)如果另一个用户也需要购进大批机器,但该用户使用P1和P2一样多,主要关心的也是响应时间,那么,应该选择M1还是M2为什么参考答案:(1)对于P1,M2比M1快一倍;对于P2,M1比M2快一倍。

(2)对于M1,P1的速度为:200M/10=20MIPS;P2为300k/=100MIPS。

对于M2,P1的速度为:150M/5=30MIPS;P2为420k/=70MIPS。

从执行速度来看,对于P2,因为100/70=倍,所以M1比M2快倍。

(3)#6)=40。

(4)在M1上执行P1时的平均时钟周期数CPI为:10×800M/(200×10在M2上执行P1时的平均时钟周期数CPI为:5×(150×106)=40。

(5)考虑运行P1时M1和M2的性价比,因为该用户主要关心系统的响应时间,所以性价比中的性能应考虑执行时间,其性能为执行时间的倒数。

故性价比R为:R=1/(执行时间×价格)R越大说明性价比越高,也即,“执行时间×价格”的值越小,则性价比越高。

因为10×5000 > 5×8000,所以,M2的性价比高。

计算机系统结构课后答案

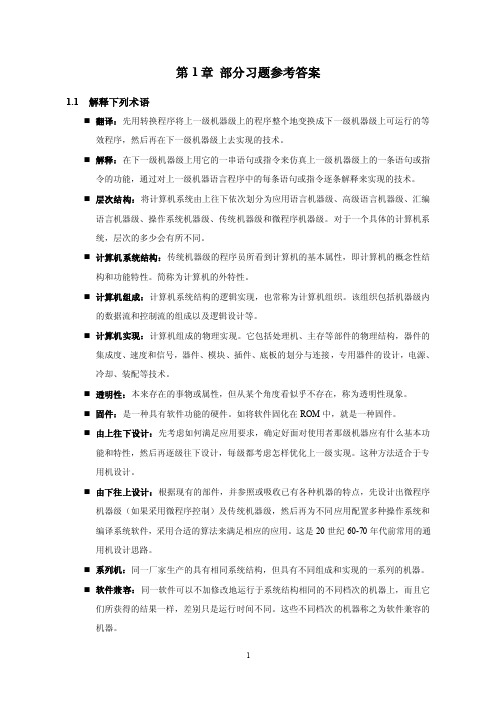

第1章部分习题参考答案1.1 解释下列术语⏹翻译:先用转换程序将上一级机器级上的程序整个地变换成下一级机器级上可运行的等效程序,然后再在下一级机器级上去实现的技术。

⏹解释:在下一级机器级上用它的一串语句或指令来仿真上一级机器级上的一条语句或指令的功能,通过对上一级机器语言程序中的每条语句或指令逐条解释来实现的技术。

⏹层次结构:将计算机系统由上往下依次划分为应用语言机器级、高级语言机器级、汇编语言机器级、操作系统机器级、传统机器级和微程序机器级。

对于一个具体的计算机系统,层次的多少会有所不同。

⏹计算机系统结构:传统机器级的程序员所看到计算机的基本属性,即计算机的概念性结构和功能特性。

简称为计算机的外特性。

⏹计算机组成:计算机系统结构的逻辑实现,也常称为计算机组织。

该组织包括机器级内的数据流和控制流的组成以及逻辑设计等。

⏹计算机实现:计算机组成的物理实现。

它包括处理机、主存等部件的物理结构,器件的集成度、速度和信号,器件、模块、插件、底板的划分与连接,专用器件的设计,电源、冷却、装配等技术。

⏹透明性:本来存在的事物或属性,但从某个角度看似乎不存在,称为透明性现象。

⏹固件:是一种具有软件功能的硬件。

如将软件固化在ROM中,就是一种固件。

⏹由上往下设计:先考虑如何满足应用要求,确定好面对使用者那级机器应有什么基本功能和特性,然后再逐级往下设计,每级都考虑怎样优化上一级实现。

这种方法适合于专用机设计。

⏹由下往上设计:根据现有的部件,并参照或吸收已有各种机器的特点,先设计出微程序机器级(如果采用微程序控制)及传统机器级,然后再为不同应用配置多种操作系统和编译系统软件,采用合适的算法来满足相应的应用。

这是20世纪60-70年代前常用的通用机设计思路。

⏹系列机:同一厂家生产的具有相同系统结构,但具有不同组成和实现的一系列的机器。

⏹软件兼容:同一软件可以不加修改地运行于系统结构相同的不同档次的机器上,而且它们所获得的结果一样,差别只是运行时间不同。

计算机体系结构习题(含答案)

第2章课后习题1、尾数用补码、小数表示,阶码用移码、整数表示,尾数字长p=6〔不包括符号位〕,阶码字长q=6〔不包括符号位〕,为数基值r m=16,阶码基值r e=2。

对于规格化浮点数,用十进制表达式写出如下数据〔对于前11项,还要写出16进值编码〕。

〔1〕最大尾数〔8〕最小正数〔2〕最小正尾数〔9〕最大负数〔3〕最小尾数〔10〕最小负数〔4〕最大负尾数〔11〕浮点零〔5〕最大阶码〔12〕表数精度〔6〕最小阶码〔13〕表数效率〔7〕最大正数〔14〕能表示的规格化浮点数个数2.一台电脑系统要求浮点数的精度不低于10,表数范围正数不小于1038,且正、负数对称。

尾数用原码、纯小数表示,阶码用移码、整数表示。

(1) 设计这种浮点数的格式(2) 计算〔1〕所设计浮点数格式实际上能够表示的最大正数、最大负数、表数精度和表数效率。

3.某处理机要求浮点数在正数区的积累误差不大于2-p-1,其中,p是浮点数的尾数长度。

(1) 选择合适的舍入方法。

(2) 确定警戒位位数。

(3) 计算在正数区的误差范围。

4.假设有A和B两种不同类型的处理机,A处理机中的数据不带标志符,其指令字长和数据字长均为32位。

B处理机的数据带有标志符,每个数据的字长增加至36位,其中有4位是标志符,它的指令数由最多256条减少到不到64条。

如果每执行一条指令平均要访问两个操作数,每个存放在存储器中的操作数平均要被访问8次。

对于一个由1000条指令组成的程序,分别计算这个程序在A处理机和B处理机中所占用的存储空间大小〔包括指令和数据〕,从中得到什么启发?5.一台模型机共有7条指令,各指令的使用频率分别为35%,25%,20%,10%,5%,3%和2%,有8个通用数据寄存器,2个变址寄存器。

(1) 要求操作码的平均长度最短,请设计操作码的编码,并计算所设计操作码的平均长度。

(2) 设计8字长的寄存器-寄存器型指令3条,16位字长的寄存器-存储器型变址寻址方式指令4条,变址范围不小于±127。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LOAD R2, B

LOAD R3, C

CMP R1, R2

BGE NEXT1 ;转移成功时,要取消下一条指令

MOVE R2, R1

NEXT1: CMP R1, R3

BGE NEXT2 ;转移成功时,要取消下一条指令

MOVE R3, R1

NEXT2: STORE R1, MAX

4.3概念略

4.7

5.1略

5.2略

5.3解:

(1)顺序执行:6n*Δt

(2)“取指令”和“执行”重叠:6t + (n-1)5t = (5n+1)Δt

(3)“取指令”、“分析”和“执行”重叠:6t + (n-1)3t = 3(n+1)Δt

(4)先行控制:Δt+5Δt + 3(n-1)Δt,约为3nΔt

10、[(A1*B1)+( A2*B2)]+[ (A3*B3)+( A4*B4)];

11、{[(A1*B1)+( A2*B2)]+[ (A3*B3)+( A4*B4)]}+[ (A5*B5)+( A6*B6)];

时空图:静态,功能需要分开

S6

1

2

3

4

5

6

7

8

9

10

11

S5

1

2

3

4

5

6

S4

1

2

3

4

5

6

C2 C3 C0 C1 C0 C2 C3 C1 C0 C1 C2 C3

(5) FIFO中Cache的块命中率:

图略

3/12=25%

(6) LFU中Cache的块命中率:

4/12=33.3%

(7)改为全相联映象后:

FIFO中块命中率:4/12=33.3%

LFU中块命中率:3/12=25%

(8)这时Cache的命中率:

(2)程序适当调整如下:

START: LOAD R1, A

LOAD R2, B

CMP R1, R2

BGE NEXT1

LOAD R3, C

MOVE R2, R1

NEXT1: CMP R1, R3

BGE NEXT2

NOP

MOVE R3, R1

NEXT2: STORE R1, MAX

3.1题

(1)当S2>>S1时,平均价格接近C2。

习题参考答案

1.1概念略

1.12Байду номын сангаас

1.13

1.15

1.19

1.21

2.1略

2.4证明:

设有两种浮点数表示方法F1, F2,他们二进制字长相同,尾数用原码或补码小数表示,阶码用移码整数表示,阶码均为2,而尾数基不同。

F1:尾数基值rm1 = 2,尾数p1,阶码长q1,二进制字长L1 = p1+q1+2

F1:尾数基值rm2 = 2^k,k为正整数,尾数p2,阶码长q2,二进制字长L2 =kp2+q2+2

一地址:

LOAD FSUB GSTORE XLOAD AADD BMUL CSTORE Y

LOAD DMUL EADD YDIV XSTORE X

零地址:

PUSH APUSH BADDPUSHMULPUSH DPUSH EMULADDPUSH FPUSH GSUBDIVPOP X

累加器:

MOV R1, AADD R1, BMUL R1, CMOV R2, DMUL R2, EADD R1, R2

方式五、高位体号:2位;低位体号:2位;体内地址:20位;

方式六、体内地址:20位;多路选择器:2位;低位体号:2位;

(2)小题

①扩大容量;

②比较简单;

③速度比较快;

④速度快,容量大;

⑤速度快,容量大;

⑥提高速度

(3)小题

①1;

②16;

③接近16;

④接近8;

⑤接近4;

⑥接近16

(4)略

3.12

3.14

2.5题

1)套公式,计算的到q >=6.99,p>=23.9,故去q = 7,p = 24阶码为7+1(1位符号位)

由于p + q + 1 = 33,隐藏最高位(-128-127)

2)计算:

①最大正数:(1-2^-24)×2^127

②最大负数:-2^-1×2^-128

③表数精度:1/2×2^-23=2^-24=10^-7.22

5.11解:

(1)

禁止向量:(6,4,2)

初始冲突向量:(101010)

(2)

状态图:

(3)

(4)

恒定循环:5最小循环:(1+7)/2=4

(5)

最大吞吐率:

(6)

10/40Δt或者10/42Δt

(7)

③9.9946 ns.美元/k字节;

选256k的cache最优

3.7题:

(1)小题解答:

方式一、体号:4位;体内地址:20位;4MB = 2^25b 4MB/32b = 20位

方式二、存贮地址:20位;多路选择器:4位;

方式三、体内地址:20位;存储器体号:4位;

方式四、高位体号:1位;低位体号:3位;体内地址:20位;

cache=128k, c=0.3152美元/k字节;

cache=256k,c=0.4235美元/k字节

(3)

按等效访问时间由小到大排序,容量分别为:

256k,128k,64k

按每字节平均价格由小到大排序,分别为:

64k, 128k, 256k

(4)

①19.129 ns.美元/k字节;

②11.9776 ns.美元/k字节;

MOV R2, FSUB R2, GDIV R1, R2MOV X, R1

2)P= 1B,A = 2B,D = 4B,R = 1/2B

1.6246P+18A = 42B6P+18A+18D = 114B

2.9339P+18A = 45B9P+18A+24D = 141B

3.122412P+12A = 36B12P+12A+12D = 84B

若F1,F2二进制字长相同,则L1=L2;

即p1+q1+2 = L2 =k p2+q2+2;(1)

表数精度相同,则

即1-p1=k(1-q1)(2)

由(1),(2)得q1 = q2+k-1;

表数范围:F1 = ,F2 = ;

显而易见, 在整数范围内恒成立,当且仅当k=1或k=2时,等号成立,因此F1的表数范围在k的整数范围内恒不比F2小,因此只有k=1或k=2时取得最大值,即rm = 2或rm = 4时有最大表数范围。证毕。

(2)ta = h*t1+(1-h)*t2

(3)e = 1/[h+(1-h)r]

(4)略

(5)当r = 100时,h>0.99947

(6)P134公式,H’= (H+n-1)/n=(0.96+5D-1)/5D>0.99947(精度,不能近似)

D = 0.008/(1-h)

计算得:D>15.05,取D=16

S3

7

8

9

10

11

S2

7

8

9

10

11

S1

1

2

3

4

5

6

7

8

9

10

11

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22

流水线性能分析:

吞吐量:TP=11/22t=0.5/Δt

加速比:S=11*4*Δt/(22Δt)=2

效率:E=S/6=1/3

3.3题

(1)t = ht1 + (1–h)t2,

当cache为64k时,t = 0.7*20ns + (1-0.7)*200ns = 74ns;

当cache=128k时,t = 38ns;

当cache=256k时,t=23.6ns

(2)按照公式:

cache=64k, c=0.2585美元/k字节;

有先行指令缓冲栈,忽略取指令时间.

5.6

5.7

5.9题

可将原来的求和算式分为以下11步:

1、A1*B1; 2、A2*B2; 3、A3*B3; 4、A4*B4;

5、A5*B5; 6、A6*B6;

7、(A1*B1)+( A2*B2); 8、(A3*B3)+( A4*B4);

9、(A5*B5)+( A6*B6);

15/16=93.75%第一次冲突,后面15次命中。

4.1

异步性:外围设备相对于处理机通常是异步工作的。

实时性:处理机必须按照不同设备所要求的传送方式和传输速率不失时机的为设备提供服务。

与设备无关性:外围设备的类型、规格、特性多种多样,他们输出数据和接收数据的方式、数据的格式差异很大,因此,设备与处理机的连接方式也很不相同。

3.17

3.18略

3.19题

(1)主存共有2个区,每个区2组,每个组2快,每块16个字节,如果按字节寻址,那么块内地址需要4位,主存要7位。图略

(2)cache地址需要6位,组号1位,块号1位,块内地址4位。图略。

(3)教材图3.44。

(4)Cache的块地址流情况:

B6 B2 B4 B1 B4 B6 B3 B0 B4 B5 B7 B3

④表数效率:100%(如果尾数没有采用隐藏位,那么表数效率为50%)