FT24C16`FT24C08 资料完整版

FT24C32&64_资料完整版

F MDCo nf i de n t i al© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page1Two-Wire Serial EEPROM32K, 64K (8-bit wide)FEATURES❑Low voltage and low power operations:FT24C32A/64A: V CC = 1.8V to 5.5V❑ Maximum Standby current < 1µA (typically 0.02µA and 0.06µA @ 1.8V and 5.5V respectively). ❑ 32 bytes page write mode.❑ Partial page write operation allowed.❑ Internally organized: 4,096 × 8 (32K), 8,192 × 8 (64K). ❑ Standard 2-wire bi-directional serial interface. ❑ Schmitt trigger, filtered inputs for noise protection. ❑ Self-timed Write Cycle (5ms maximum).❑ 800 kHz (5V), 400 kHz (1.8V, 2.5V, 2.7V) Compatibility. ❑ Automatic erase before write operation.❑ Write protect pin for hardware data protection.❑ High reliability: typically 1, 000,000 cycles endurance. ❑ 100 years data retention.❑ Industrial temperature range (-40℃ to 85℃).❑Standard 8-lead DIP/SOP/ MSOP/TSSOP/DFN and 5-lead SOT23/TSOT23 Pb-free packages.DESCRIPTIONThe FT24C32A/64A series are 32,768/65,536 bits of serial Electrical Erasable and Programmable Read Only Memory, commonly known as EEPROM. They are organized as 4096/8192 words of 8 bits (one byte) each. The devices are fabricated with proprietary advanced CMOS process for low power and low voltage applications. These devices are available in standard 8-lead DIP, 8-lead SOP, 8-lead MSOP, 8-lead TSSOP, 8-lead DFN, 5-lead SOT23, and 5-lead TSOT23 packages. A standard 2-wire serial interface is used to address all read and write functions. Our extended V CC range (1.8V to 5.5V) devices enables wide spectrum of applications.PIN CONFIGURATIONPin Name Pin Function A2, A1, A0 Device Address Inputs SDA Serial Data Input / Open Drain Output SCL Serial Clock Input WP Write Protect NC No-ConnectF MDCo nf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page2All these packaging types come in Pb-free certified.VCC WP SCL SDAA2A1A0GND8L DIP 8L SOP8L TSSOP 8L MSOP 8L DFN5L SOT235L TSOT23ABSOLUTE MAXIMUM RATINGSIndustrial operating temperature: -40℃ to 85℃ Storage temperature:-50℃ to 125℃Input voltage on any pin relative to ground: -0.3V to V CC + 0.3V Maximum voltage: 8VESD Protection on all pins: >2000V* Stresses exceed those listed under “Absolute Maximum Rating” may cause permanent damage to the device. Functional operation of the device at conditions beyond those listed in the specification is not guaranteed. Prolonged exposure to extreme conditions may affect device reliability or functionality .F MDCo nf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page3PIN DESCRIPTIONS(A) SERIAL CLOCK (SCL)The rising edge of this SCL input is to latch data into the EEPROM device while the falling edge of this clock is to clock data out of the EEPROM device. (B) DEVICE / CHIP SELECT ADDRESSES (A2, A1, A0)These are the chip select input signals for the serial EEPROM devices. Typically, these signals are hardwired to either V IH or V IL . If left unconnected, they are internally recognized as V IL . (C) SERIAL DATA LINE (SDA)SDA data line is a bi-directional signal for the serial devices. It is an open drain output signal and can be wired-OR with other open-drain output devices. (D) WRITE PROTECT (WP)The FT24C32A/64A devices have a WP pin to protect the whole EEPROM array from programming. Programming operations are allowed if WP pin is left un-connected or input to V IL . Conversely all programming functions are disabled if WP pin is connected to V IH or V CC . Read operations is not affected by the WP pin’s input level.MEMORY ORGANIZATIONThe FT24C32A/64A devices have 128/256 pages respectively. Since each page has 32 bytes, random word addressing to FT24C32A/64A will require 12/13 bits data word addresses respectively.DEVICE OPERATION(A) SERIAL CLOCK AND DATA TRANSITIONSThe SDA pin is typically pulled to high by an external resistor. Data is allowed to change only when Serial clock SCL is at V IL . Any SDA signal transition may interpret as either a START or STOP condition as described below.(B) START CONDITIONWith SCL V IH , a SDA transition from high to low is interpreted as a START condition. All valid commands must begin with a START condition.(C) STOP CONDITIONWith SCL V IH , a SDA transition from low to high is interpreted as a STOP condition. All valid read or write commands end with a STOP condition. The device goes into the STANDBY mode if it is after a read command. A STOP condition after page or byte write command will trigger the chip into the STANDBY mode after the self-timed internal programming finish (see Figure 1).(D) ACKNOWLEDGEThe 2-wire protocol transmits address and data to and from the EEPROM in 8 bit words. The EEPROM acknowledges the data or address by outputting a "0" after receiving each word. The ACKNOWLEDGE signal occurs on the 9th serial clock after each word.F MDCo nf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page4(E) STANDBY MODEThe EEPROM goes into low power STANDBY mode after a fresh power up, after receiving a STOP bit in read mode, or after completing a self-time internal programming operation.Figure 1: Timing diagram for START and STOP conditionsFigure 2: Timing diagram for output ACKNOWLEDGEDEVICE ADDRESSINGThe 2-wire serial bus protocol mandates an 8 bits device address word after a START bit condition to invoke a valid read or write command. The first four most significant bits of the device address must be 1010, which is common to all serial EEPROM devices. The next three bits are device address bits. These three device address bits (5th , 6th and 7th ) are to match with the external chip select/address pin states. If a match is made, the EEPROM device outputs an ACKNOWLEDGE signal after the 8th read/write bit, otherwise the chip will go into STANDBY mode. However, matching may not be needed for some or all device address bits (5th , 6th and 7th ) as noted below. The last or 8th bit is a read/write command bit. If the 8th bit is at V IH then the chip goes into read mode. If a “0” is detected, the device enters programming mode.SCLSDASTART Condition STOP ConditionData Data Valid Transition SCLData inData out START Condition ACKF MDCo nf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page5WRITE OPERATIONS(A) BYTE WRITEA write operation requires two 8-bit data word address following the device address word and ACKNOWLEDGE signal. Upon receipt of this address, the EEPROM will respond with a “0” and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will again output a “0”. The addressing device, such as a microcontroller, must terminate the write sequence with a STOP condition. At this time the EEPROM enters into an internally-timed write cycle state. All inputs are disabled during this write cycle and the EEPROM will not respond until the writing is completed (figure 3). (B) PAGE WRITEThe 32K/64K EEPROM are capable of 32-byte page write.A page write is initiated the same way as a byte write, but the microcontroller does not send a STOP condition after the first data word is clocked in. The microcontroller can transmit up to 31 more data words after the EEPROM acknowledges receipt of the first data word. The EEPROM will respond with a “0” after each data word is received. The microcontroller must terminate the page write sequence with a STOP condition (see Figure 4).The lower five bits of the data word address are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. If more than 32 data words are transmitted to the EEPROM, the data word address will “roll over” and the previous data will be overwritten. (C) ACKNOWLEDGE POLLINGACKNOWLEDGE polling may be used to poll the programming status during a self-timed internal programming. By issuing a valid read or write address command, the EEPROM will not acknowledge at the 9th clock cycle if the device is still in the self-timed programming mode. However, if the programming completes and the chip has returned to the STANDBY mode, the device will return a valid ACKNOWLEDGE signal at the 9th clock cycle.READ OPERATIONSThe read command is similar to the write command except the 8th read/write bit in address word is set to “1”. The three read operation modes are described as follows: (A) CURRENT ADDRESS READThe EEPROM internal address word counter maintains the last read or write address plus one if the power supply to the device has not been cut off. To initiate a current address read operation, the micro-controller issues a START bit and a valid device address word with the read/write bit (8th ) set to “1”. The EEPROM will response with an ACKNOWLEDGE signal on the 9th serial clock cycle. An 8-bit data word will then be serially clocked out. The internal address word counter will then automatically increase by one. For current address read the micro-controller will not issue an ACKNOWLEDGE signal on the 18th clock cycle. The micro-controller issues a valid STOP bit after the 18th clock cycle to terminate the read operation. The device then returns to STANDBY mode (see Figure 5).(B) SEQUENTIAL READThe sequential read is very similar to current address read. The micro-controller issues a START bit and a valid device address word with read/write bit (8th ) set to “1”. The EEPROM will response with an ACKNOWLEDGE signal on the 9th serial clock cycle. An 8-bit data word will then be serially clocked out. Meanwhile the internally address word counter will then automatically increase by one.MDf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page6Unlike current address read, the micro-controller sends an ACKNOWLEDGE signal on the 18th clock cycle signaling the EEPROM device that it wants another byte of data. Upon receiving the ACKNOWLEDGE signal, the EEPROM will serially clocked out an 8-bit data word based on the incremented internal address counter. If the micro-controller needs another data, it sends out an ACKNOWLEDGE signal on the 27th clock cycle. Another 8-bit data word will then be serially clocked out. This sequential read continues as long as the micro-controller sends an ACKNOWLEDGE signal after receiving a new data word. When the internal address counter reaches its maximum valid address, it rolls over to the beginning of the memory array address. Similar to current address read, the micro-controller can terminate the sequential read by not acknowledging the last data word received, but sending a STOP bit afterwards instead (figure 6). (C) RANDOM READRandom read is a two-steps process. The first step is to initialize the internal address counter with a target read address using a “dummy write” instruction. The second step is a current address read.To initialize the internal address counter with a target read address, the micro-controller issues a START bit first, follows by a valid device address with the read/write bit (8th ) set to “0”. The EEPROM will then acknowledge. The micro-controller will then send two address words. Again the EEPROM will acknowledge. Instead of sending a valid written data to the EEPROM, the micro-controller performs a current address read instruction to read the data. Note that once a START bit is issued, the EEPROM will reset the internal programming process and continue to execute the new instruction - which is to read the current address (figure 7).Figure 3: Byte WriteSDA LINES T A R S BDEVICE S B /W C KW R I T FIRST WORD S BC KC KC KS B SECOND WORD S T O DATAFigure 4: Page WriteSDA LINES T A R S BDEVICE S B /W C KW R I T FIRST WORD S BC KC KC KS B SECOND WORD S T OC KFDCo ne nt i a l© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page7Figure 5: Current Address ReadSDA LINES T A R S BDEVICE S B /W C KR E A DO A C KS T O DATAFigure 6: Sequential ReadDEVICE /W R E A DC KO A C KS T O DATA (N)DATA (N+1)DATA (N+2)DATA (N+3)C KC KC KFigure 7: Random ReadS T A R S BDEVICE S B /W C R E A DKO A C KS T O DATA (N)S T A R S BDEVICE S B /W C KW R I T FIRST WORD S BC KS B SECOND WORD C KSDA LINENotes: 1) * = Don’t Care bits2) # = Don’t Care bits for FT24C32F MDCo nf i de nt i© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page8Figure 8: SCL and SDA Bus TimingSCLSDA INSDA OUTAC CHARACTERISTICS1.8V2.5-5.0 VSymbolParameter Min Max Min Max Unitf SCL Clock frequency, SCL400800 kHz t LOW Clock pulse width low 1.20.9µst HIGH Clock pulse width high0.4 0.3 µs t I Noise suppression time (1)180 120 nst AA Clock low to data out valid0.3 1.2 0.2 0.9 µs t BUF Time the bus must be free before a newtransmission can start (1) 1.3 1.2 µst HD.STA START hold time0.6 0.6 µs t SU.STA START set-up time0.6 0.6 µs t HD.DAT Data in hold time 0 0 µs t SU.DAT Data in set-up time 100100nst R Input rise time (1) 0.3 0.3 µst F Input fall time (1)300 300 nst SU.STO STOP set-up time 0.6 0.6 µs t DH Date out hold time 200 50 ns t WRWrite cycle time55msEndurance (1) 25o C, Page Mode, 3.3V1,000,000Write CyclesNotes: 1. This Parameter is expected by characterization but are not fully screened by test.2. AC Measurement conditions: R L (Connects to Vcc): 1.3K ΩInput Pulse Voltages: 0.3Vcc to 0.7VccInput and output timing reference Voltages: 0.5VccF MDe nt i a l© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page9DC CHARACTERISTICSSymbol Parameter Test ConditionsMin Typical Max Units V CC1 24C ××A supply V CC1.8 5.5 V I CC Supply read current V CC @ 5.0V SCL = 400 kHz 0.4 1.0 mA I CCSupply write currentV CC @ 5.0V SCL = 400 kHz2.03.0mAI SB1 Supply current V CC @ 1.8V, V IN = V CC or V SS 0.02 1.0 µA I SB2 Supply current V CC @ 2.5V, V IN = V CC or V SS 1.0 µA I SB3 Supply current V CC @ 5.0V, V IN = V CC or V SS 0.07 1.0 µAI IL Input leakage current V IN = V CC or V SS 3.0 µA I LO Output leakage current V IN = V CC or V SS3.0µA V IL Input low level -0.6V CC × 0.3V V IH Input high levelV CC × 0.7V CC + 0.5VV OL2 Output low level V CC @ 3.0V, I OL = 2.1 mA0.4 VV OL1 Output low levelV CC @ 1.8V, I OL = 0.15 mA0.2 VORDERING INFORMATIONDensity PackageTemperature RangeVcc HSF Packaging Ordering CodeRoHSTube FT24C32A-UDR-BDIP8 -40℃-85℃ 1.8V-5.5VGreenTube FT24C32A-UDG-B Tube FT24C32A-USR-B RoHSTape and Reel FT24C32A-USR-TTube FT24C32A-USG-B SOP8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C32A-USG-TTube FT24C32A-UMR-B RoHSTape and Reel FT24C32A-UMR-TTube FT24C32A-UMG-B 32kbitsMSOP8 -40℃-85℃ 1.8V-5.5VGreenTape and Reel FT24C32A-UMG-TD: DIP8 S: SOP8 M: MSOP8 T: TSSOP8 L: SOT23-5 P: TSOT23-5 N: DFN8PackagingB: TubeT: Tape and Reel HSF R: RoHS G: GreenU:-40F MDCo nf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page10Tube FT24C32A-UTR-B RoHSTape and Reel FT24C32A-UTR-TTube FT24C32A-UTG-B TSSOP8 -40℃-85℃ 1.8V-5.5VGreenTape and Reel FT24C32A-UTG-T RoHS Tape and Reel FT24C32A-ULR-T SOT23-5-40℃-85℃1.8V-5.5VGreen Tape and Reel FT24C32A-ULG-T RoHSTape and Reel FT24C32A-UPR-T TSOT23-5 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C32A-UPG-T RoHSTape and Reel FT24C32A-UNR-T 32kbitsDFN8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C32A-UNG-TRoHSTube FT24C64A-UDR-B DIP8 -40℃-85℃ 1.8V-5.5VGreen Tube FT24C64A-UDG-B Tube FT24C64A-USR-B RoHSTape and Reel FT24C64A-USR-TTube FT24C64A-USG-B SOP8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C64A-USG-TTube FT24C64A-UMR-B RoHSTape and Reel FT24C64A-UMR-TTube FT24C64A-UMG-B MSOP8 -40℃-85℃ 1.8V-5.5VGreenTape and Reel FT24C64A-UMG-TTube FT24C64A-UTR-B RoHSTape and Reel FT24C64A-UTR-TTube FT24C64A-UTG-B TSSOP8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C64A-UTG-T RoHSTape and Reel FT24C64A-ULR-T SOT23-5 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C64A-ULG-T RoHSTape and Reel FT24C64A-UPR-T TSOT23-5 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C64A-UPG-T RoHSTape and Reel FT24C64A-UNR-T 64kbitsDFN8 -40℃-85℃ 1.8V-5.5VGreenTape and Reel FT24C64A-UNG-TF MDCo nf i de nt i al© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page11DIP8 PACKAGE OUTLINEDIMENSIONSDimensions In MillimetersDimensions In InchesSymbolMin Max Min MaxA 3.710 4.310 0.146 0.170 A1 0.510 0.020 A2 3.200 3.600 0.126 0.142B 0.380 0.570 0.015 0.022B1 1.524(BSC ) 0.060(BSC ) C 0.204 0.360 0.008 0.014 D 9.000 9.400 0.354 0.370 E 6.200 6.600 0.244 0.260 E1 7.320 7.920 0.288 0.312 e 2.540 (BSC) 0.100(BSC ) L 3.000 3.600 0.118 0.142 E2 8.400 9.000 0.331 0.354F MDCo nf i de nt i al© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page12SOP8 PACKAGE OUTLINE DIMENSIONSDimensions In MillimetersDimensions In InchesSymbolMin Max Min MaxA 1.350 1.750 0.053 0.069A1 0.100 0.250 0.004 0.010A2 1.350 1.550 0.053 0.061 b 0.330 0.510 0.013 0.020 c 0.170 0.250 0.006 0.010D 4.700 5.100 0.185 0.200E 3.800 4.000 0.150 0.157 E1 5.800 6.200 0.228 0.244 e 1.270 (BSC)0.050 (BSC)L 0.400 1.270 0.016 0.050 θ 0° 8° 0° 8°F MDCo nf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page13MSOP8 PACKAGE OUTLINE DIMENSIONSDimensions In MillimetersDimensions In InchesSymbolMin Max Min MaxA 0.820 1.100 0.320 0.043 A1 0.020 0.150 0.001 0.006 A2 0.750 0.950 0.030 0.037 b 0.250 0.380 0.010 0.015 c 0.090 0.230 0.004 0.009 D 2.900 3.100 0.114 0.122 e 0.65 (BSC) 0.026 (BSC) E 2.900 3.100 0.114 0.122 E1 4.750 5.050 0.187 0.199 L 0.400 0.800 0.016 0.031 θ 0° 6° 0° 6°F MDC o n f i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page14TSSOP8 PACKAGE OUTLINEDIMENSIONSDimensions In Millimeters Dimensions In InchesSymbolMinMax Min Max D 2.900 3.100 0.114 0.122 E4.3004.5000.1690.177b 0.190 0.300 0.007 0.012c 0.090 0.200 0.004 0.008 E1 6.250 6.550 0.246 0.258 A 1.100 0.043 A2 0.800 1.000 0.031 0.039 A1 0.020 0.150 0.001 0.006e 0.65 (BSC) 0.026 (BSC) L 0.500 0.700 0.020 0.028H 0.25 (TYP) 0.01 (TYP)θ 1°7° 1° 7°F MDCo nf i de n t i a l© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page15SOT-23-5 PACKAGE OUTLINE DIMENSIONSDimensions In MillimetersDimensions In InchesSymbolMin Max Min MaxA 1.050 1.250 0.041 0.049 A1 0.000 0.100 0.000 0.004 A2 1.050 1.150 0.041 0.045 b 0.300 0.500 0.012 0.020 c 0.100 0.200 0.004 0.008 D 2.820 3.020 0.111 0.119 E 1.500 1.700 0.059 0.067 E1 2.650 2.950 0.104 0.116 e 0.95 (BSC) 0.037 (BSC) e1 1.800 2.000 0.071 0.079 L 0.300 0.600 0.012 0.024 θ 0° 8° 0° 6°F MDCo nf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page16TSOT-23-5 PACKAGE OUTLINE DIMENSIONSDimensions In MillimetersDimensions In InchesSymbolMin Max Min MaxA 0.700 0.900 0.028 0.035 A1 0.000 0.100 0.000 0.004 A2 0.700 0.800 0.028 0.031 b 0.350 0.500 0.014 0.020 c 0.080 0.200 0.003 0.008 D 2.820 3.020 0.111 0.119 E 1.600 1.700 0.063 0.067 E1 2.650 2.950 0.104 0.116 e 0.95 (BSC) 0.037 (BSC) e1 1.90 (BSC) 0.075 (BSC) L 0.300 0.600 0.012 0.024 θ 0° 8° 0° 8°F MDCo nf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page17DFN8 PACKAGE OUTLINE DIMENSIONSDimensions In MillimetersSymbolMinNomMaxA 0.70 0.75 0.80 A1 - 0.02 0.05 b 0.18 0.25 0.03 c 0.18 0.20 0.25 D 1.902.00 2.10D2 1.50REF e 0.50BSC Nd 1.50BSC E 2.90 3.00 3.10 E2 1.60REFL 0.30 0.40 0.50 h 0.20 0.25 0.30* Information furnished is believed to be accurate and reliable. However, Fremont Micro Devices, Incorporated (BVI) assumes no responsibility for the consequences of use of such information or for any infringement of patents of other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Fremont Micro Devices, Incorporated (BVI). Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. Fremont Micro Devices, Incorporated (BVI) products are not authorized for use as critical components in life support devices or systems without express written approval of Fremont Micro Devices, Incorporated (BVI). The FMD logo is a registered trademark of Fremont Micro Devices, Incorporated (BVI). All other names are the property of their respective owners.© 2012 Fremont Micro Devices Inc. DS24C32_64-A0--page18 DMF。

FM24系列中文资料

引脚说明

串行时钟信号引脚(SCL):在 SCL 输入时钟信号的上升 沿将数据送入 EEPROM 器件,并在时钟的下降沿将数 据读出。

串行数据输入/输出引脚(SDA):SDA 引脚可实现双 向串行数据传输。该引脚为开漏输出,可与其它多个 开漏输出器件或开集电极器件线或连接。

器件/页 地址脚(A2,A1,A0):A2、A1 和 A0 引脚 为 FM24C02 的硬件连接的器件地址输入引脚。在一 个总线上最多可寻址八个 2K 器件。(器件寻址详见器 件寻址章节内容) 。

FM24C08

FM24C08A

全地址(4K)

正常读写 正常读写

全地址(8K)

FM24C16 高半区(8K)

存储器结构

FM24C02,2K 串行电可擦除存储器:内部分为 32 页, FM24C08(A),8K 串行电可擦除存储器:内部分为 64

每页 8 字节,以 8 位地址寻址。

页,每页 16 字节,以 10 位地址寻址。

SCL WP VCC GND NC

引脚功能

器件地址输入 串行数据输入输出 串行时钟输入 写保护 电源 地 不连接

FM24C02/04/08(A)/16 两线制串行 EEPROM

版本 2.2

技术手册

3

图 1.结构框图

FM24C02/04/08(A)/16 两线制串行 EEPROM

版本 2.2

技术手册

版本 2.2

技术手册

6

交流参数

推荐参数的适用工作条件:TA = -40°C ~ +85°C,VCC = +2.2V ~ +5.5V,CL = 1 TTL Gate and 100 pF(除非 另有说明)。测试条件参见“注 2”。

FM24C16A-AT24C16中文资料

第 1页

Figure 1. Block Diagram

引脚定义

名称 I/O

SDA I/O

SCL 输入

WP 输入

VDD VSS NC

电源 电源 空脚

描述

串行地址\数据管脚:这个双向引脚用来传送地址和输入输出数据。这是一个开 漏输出,以便与其它器件通过”线或”并接在双线总线上。输入缓冲区集成施密 特触发器用以提高抗干扰性能,输出驱动器具有下降沿斜率控制。此端口必须 外加上拉电阻。 串行时钟:两线制总线的串行时钟输入。数据在时钟的下降沿移出器件,在时 钟的上升沿移入器件,时钟端口同样具有施密特触发器用以提高抗干扰性能。

对器件进行轮循以等待一个就绪状态,因为器

件是以总线速度进行写操作, 一个新的总线

转输将数据移入器件的同时,一个写操作已经

完成,更为详尽的描述将在下面的接口界面章

ห้องสมุดไป่ตู้

节进行描述。

Figure 2. Typical System Configuration

需要指出的是,FM24C16A没有类似内部电源管

图5描述的是单字节和多字节的操作。

第 5页

Figure 5. Single Byte Write

Figure 6. Multiple Byte Write

读操作

四种正确操作方法如下:

有两种基本类型的读操作:当前地址读操作 1、主机在第9个时钟不发应答信号,在第十个时

和随机地址读操作。对当前地址进行读操作

开始

当主机把SDA从高电平拉为低电平,同时SCL 信号为高电平时被认为是开始信号,所有的读 写操作均由开始信号开始。任何时候发布一个 开始信号,一个进行中的操作都会被中止。使 用开始信号中止一个操作的同时,FM24C04A 也会处于开始一个新操作的就绪状态。在操作 过程中,如果电压降低到规定电压的最低值以 下时,FM24C16A执行另外一个的操作之前,会 认为出现了一个开始信号。

掉电存储模块产品使用手册

ATMEL08掉电存储模块简要说明:一、尺寸:全长30mm宽15mm高10mm二、主芯片:ATMEL24C08芯片三、工作电压:直流5V四、特点:电路简单实用,接线简单。

电路支持:ATMEL24C02\ ATMEL24C04\ ATMEL24C08\ ATMEL24C16\ ATMEL24C32.适用场合:单片机学习、电子竞赛、产品开发、毕业设计。

【标注说明】【参考原理图】【PCB尺寸图】【测试程序】#include <reg52.H>#include <stdio.h>#include <absacc.h>unsigned char code table[]={ 0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0x80,0x90,0x40}; signed char sec=1; //定义计数值,每过1 秒,sec加1unsigned int tcnt; //定时中断次数unsigned char jd=0;unsigned char gd=0;bit write=0; //写24C08 的标志;sbit gewei=P2^6; //个位选通定义sbit shiwei=P2^5; //十位选通定义sbit baiwei=P2^7; //百位选通定义sbit qianwei=P2^4; //千位选通定义sbit P10=P1^0;sbit P11=P1^1;sbit P12=P1^2;sbit P13=P1^3;sbit P14=P1^4;sbit P15=P1^5;sbit P16=P1^6;sbit P17=P1^7;sbit P30=P3^0;sbit P31=P3^1;sbit P32=P3^2;sbit P35=P3^5;sbit jia=P2^0;sbit jian=P2^1;sbit res=P2^2;/////////24C08 读写驱动程序//////////////////// sbit scl=P3^3; // 24c08 SCLsbit sda=P3^4; // 24c08 SDAvoid delay1(unsigned char x){ unsigned int i;for(i=0;i<x;i++);;}void flash(){ ; ; }void x24c08_init() //24c08 初始化子程序{scl=1; flash(); sda=1; flash();}void start() //启动(I方C)总线{sda=1; flash(); scl=1; flash(); sda=0; flash(); scl=0; flash();} void stop() //停止(I方C)总线{sda=0; flash(); scl=1; flash(); sda=1; flash();}void writex(unsigned char j) //写一个字节{ unsigned char i,temp;temp=j;for (i=0;i<8;i++){temp=temp<<1; scl=0; flash(); sda=CY; flash(); scl=1; flash();} scl=0; flash(); sda=1; flash();}unsigned char readx() //读一个字节{unsigned char i,j,k=0;scl=0; flash(); sda=1;for (i=0;i<8;i++){flash(); scl=1; flash();if (sda==1) j=1;else j=0;k=(k<<1)|j;scl=0;}flash(); return(k);}void clock() //(I方C)线时钟{unsigned char i=0;scl=1; flash();while ((sda==1)&&(i<255))i++;scl=0; flash();}////////从24c02 的地址address 中读取一个字节数据/////unsigned char x24c08_read(unsigned char address){unsigned char i;start(); writex(0xa0);clock(); writex(address);clock(); start();writex(0xa1); clock();i=readx(); stop();delay1(10);return(i);}//////向24c02 的address 地址中写入一字节数据info///// void x24c08_write(unsigned char address,unsigned char info){EA=0;start(); writex(0xa0);clock(); writex(address);clock(); writex(info);clock(); stop();EA=1;delay1(50);}/////////////24C08 读写驱动程序完///////////////////// void Delay(unsigned int tc) //延时程序{while( tc != 0 ){unsigned int i;for(i=0; i<100; i++);tc--;}}void LED() //LED显示函数{qianwei=0; P0=0xc0; Delay(3); qianwei=1; baiwei=0; P0=0xc0; Delay(3); baiwei=1; shiwei=0; P0=table[sec/10]; Delay(3); shiwei=1; gewei=0; P0=table[sec%10]; Delay(3); gewei=1;}void t0(void) interrupt 1 using 0 //定时中断服务函数{TH0=(65536-50000)/256; //对TH0 TL0 赋值TL0=(65536-50000)%256; //重装计数初值tcnt++; //每过250ust tcnt 加一if(tcnt==1) //计满20次(1 秒)时{tcnt=0; //重新再计write=1; //1 秒写一次24C08}}void main(void){TMOD=0x01; //定时器工作在方式1ET0=1; EA=1;x24c08_init(); //初始化24C08sec=x24c08_read(2);//读出保存的数据赋于secTH0=(65536-50000)/256; //对TH0 TL0 赋值TL0=(65536-50000)%256; //使定时器0.05 秒中断一次TR0=1; //开始计时*/while(1){if(jia==0){Delay(8); while(!jia){LED();}; {sec++;if(sec==36){sec=0;}} } if(jian==0){ Delay(8); while(!jian){LED();};{sec--;if(sec<0){sec=35;}} }if(res==0){sec=0;}switch(sec){case 0:P1=0X81;P30=1;P31=1;P32=1;P35=1;break;case 1:P1=0X82;P30=1;P31=1;P32=1;P35=1;break;case 2:P1=0X84;P30=1;P31=1;P32=1;P35=1;break;case 3:P1=0X88;P30=1;P31=1;P32=1;P35=1;break;case 4:P1=0X90;P30=1;P31=1;P32=1;P35=1;break;case 5:P1=0XA0;P30=1;P31=1;P32=1;P35=1;break;case 6:P1=0X41;P30=1;P31=1;P32=1;P35=1;break;case 7:P1=0X42;P30=1;P31=1;P32=1;P35=1;break;case 8:P1=0X44;P30=1;P31=1;P32=1;P35=1;break;case 9:P1=0X48;P30=1;P31=1;P32=1;P35=1;break;case 10:P1=0X50;P30=1;P31=1;P32=1;P35=1;break;case 11:P1=0X60;P30=1;P31=1;P32=1;P35=1;break;case 12:P1=0XC1;P30=0;P31=1;P32=1;P35=1;break;case 13:P1=0XC2;P30=0;P31=1;P32=1;P35=1;break;case 14:P1=0XC4;P30=0;P31=1;P32=1;P35=1;break;case 15:P1=0XC8;P30=0;P31=1;P32=1;P35=1;break;case 16:P1=0XD0;P30=0;P31=1;P32=1;P35=1;break;case 17:P1=0XE0;P30=0;P31=1;P32=1;P35=1;break;case 18:P1=0XC1;P30=1;P31=0;P32=1;P35=1;break;case 19:P1=0XC2;P30=1;P31=0;P32=1;P35=1;break; case 20:P1=0XC4;P30=1;P31=0;P32=1;P35=1;break; case 21:P1=0XC8;P30=1;P31=0;P32=1;P35=1;break; case 22:P1=0XD0;P30=1;P31=0;P32=1;P35=1;break; case 23:P1=0XE0;P30=1;P31=0;P32=1;P35=1;break;case 24:P1=0XC1;P30=1;P31=1;P32=0;P35=1;break; case 25:P1=0XC2;P30=1;P31=1;P32=0;P35=1;break; case 26:P1=0XC4;P30=1;P31=1;P32=0;P35=1;break; case 27:P1=0XC8;P30=1;P31=1;P32=0;P35=1;break; case 28:P1=0XD0;P30=1;P31=1;P32=0;P35=1;break; case 29:P1=0XE0;P30=1;P31=1;P32=0;P35=1;break;case 30:P1=0XC1;P30=1;P31=1;P32=1;P35=0;break; case 31:P1=0XC2;P30=1;P31=1;P32=1;P35=0;break; case 32:P1=0XC4;P30=1;P31=1;P32=1;P35=0;break; case 33:P1=0XC8;P30=1;P31=1;P32=1;P35=0;break; case 34:P1=0XD0;P30=1;P31=1;P32=1;P35=0;break; case 35:P1=0XE0;P30=1;P31=1;P32=1;P35=0;break; default:break;}LED();if(write==1) //判断计时器是否计时一秒{write=0; //清零x24c08_write(2,sec); //在24c08 的地址2 中写入数据sec}}}【实物展示】。

AT24Cxx中文数据手册

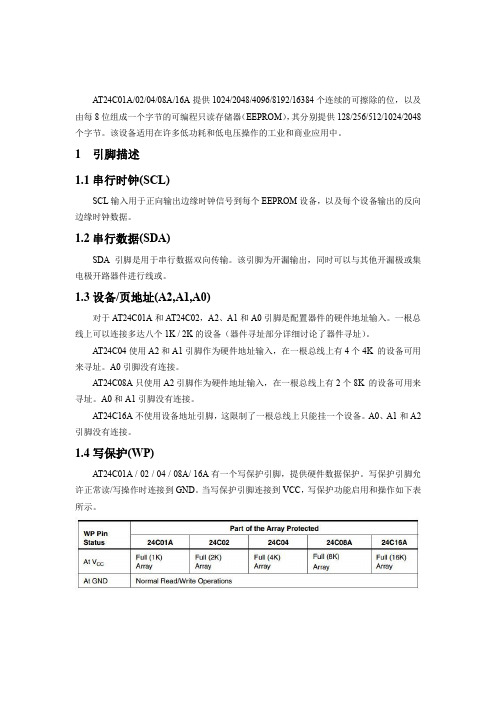

AT24C01A/02/04/08A/16A提供1024/2048/4096/8192/16384个连续的可擦除的位,以及由每8位组成一个字节的可编程只读存储器(EEPROM),其分别提供128/256/512/1024/2048个字节。

该设备适用在许多低功耗和低电压操作的工业和商业应用中。

1引脚描述1.1串行时钟(SCL)SCL输入用于正向输出边缘时钟信号到每个EEPROM设备,以及每个设备输出的反向边缘时钟数据。

1.2串行数据(SDA)SDA引脚是用于串行数据双向传输。

该引脚为开漏输出,同时可以与其他开漏极或集电极开路器件进行线或。

1.3设备/页地址(A2,A1,A0)对于AT24C01A和AT24C02,A2、A1和A0引脚是配置器件的硬件地址输入。

一根总线上可以连接多达八个1K / 2K的设备(器件寻址部分详细讨论了器件寻址)。

AT24C04使用A2和A1引脚作为硬件地址输入,在一根总线上有4个4K 的设备可用来寻址。

A0引脚没有连接。

AT24C08A只使用A2引脚作为硬件地址输入,在一根总线上有2个8K 的设备可用来寻址。

A0和A1引脚没有连接。

AT24C16A不使用设备地址引脚,这限制了一根总线上只能挂一个设备。

A0、A1和A2引脚没有连接。

1.4写保护(WP)AT24C01A / 02 / 04 / 08A/ 16A有一个写保护引脚,提供硬件数据保护。

写保护引脚允许正常读/写操作时连接到GND。

当写保护引脚连接到VCC,写保护功能启用和操作如下表所示。

2设备操作2.1时钟和数据转换SDA引脚通常情况下拉高。

SDA引脚上的数据只能在SCL低时间段内更改,而启动条件或停止条件在SCL为高时进行。

2.2启动条件在任何其他指令之前,SDA由高变为低,且SCL为高。

2.3停止条件SDA由低变为高,且SCL为高。

在读取序列之后,执行停止命令后EEPROM进入备用电源模式。

2.4应答所有地址和数据字都是从EEPROM串行发送和接收8位字节。

AT24C164-10SU-2.7;AT24C164-10PU-1.8;AT24C164-10PU-2.7;AT24C164-10SU-1.8;中文规格书,Datasheet资料

1Features•Low Voltage and Standard Voltage Operation –2.7 (V CC = 2.7V to 5.5V)–1.8 (V CC = 1.8V to 5.5V)•Internally Organized 2048 x 8 (16K)•Two-Wire Serial Interface•Schmitt Trigger, Filtered Inputs for Noise Suppression •Bidirectional Data Transfer Protocol•100 kHz (1.8V, 2.5V, 2.7V) and 400 kHz (5V) Compatibility •Write Protect Pin for Hardware Data Protection •Cascadable Feature Allows for Extended Densities •16-Byte Page Write Mode•Partial Page Writes Are Allowed •Self-Timed Write Cycle (10 ms max)•High Reliability–Endurance: 1 Million Write Cycles –Data Retention: 100 Years•Automotive Grade, Extended Temperature and Lead-free/Halogen-free Devices Available•8-lead PDIP and 8-lead JEDEC SOIC Packages•Die Sales: Wafer Form, Waffle Pack and Bumped WafersDescriptionThe AT24C164 provides 16,384 bits of serial electrically erasable and programmable read only memory (EEPROM) organized as 2048 words of 8 bits each. The device’s cascadable feature allows up to eight devices to share a common two-wire bus. The device is optimized for use in many industrial and commercial applications where low power and low voltage operation are essential. The AT24C164 is available in space saving 8-lead PDIP and 8-lead JEDEC SOIC packages and is accessed via a two-wire serial interface. In addition, this device is available in 2.7V (2.7V to 5.5V) and 1.8V (1.8V to 5.5V) versions.Table 1. Pin ConfigurationsPin Name Function A0 - A2Address Inputs SDA Serial Data SCL Serial Clock Input WPWrite Protect8-lead PDIP 8-lead SOIC2AT24C1640105J–SEEPR–12/06Figure 1. Block DiagramAbsolute Maximum Ratings*Operating Temperature..................................–55°C to +125°C *NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Storage Temperature.....................................–65°C to +150°C Voltage on Any Pinwith Respect to Ground....................................–1.0V to +7.0V Maximum Operating Voltage..........................................6.25V DC Output Current........................................................5.0 mA3AT24C1640105J–SEEPR–12/06Pin DescriptionSERIAL CLOCK (SCL): The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.SERIAL DATA (SDA): The SDA pin is bidirectional for serial data transfer. This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open collector devices.DEVICE SELECT (A2, A1, A0): The A2, A1 and A0 pins are device address inputs that may be hardwired or actively driven to V DD or V SS . These inputs allow the selection for one of eight possible devices sharing a common bus. The AT24C164 can be made compatible with the AT24C16 by tying A2, A1 and A0 to V SS . Device addressing is dis-cussed in detail in the device addressing section.WRITE PROTECT (WP): The write protect input, when tied low to GND, allows normal write operations. When WP is tied to V CC , all write operations are inhibited.Memory OrganizationThe AT24C164 is internally organized with 256 pages of 8 bytes each. Random word addressing requires an 11 bit data word address.4AT24C1640105J–SEEPR–12/06Note:1.This parameter is characterized and is not 100% tested.Note:1.V IL min and V IH max are reference only and are not tested.Table 2. Pin Capacitance (1)Applicable over recommended operating range from T A = 25°C, f = 1.0 MHz, V CC = +1.8V.Symbol Test ConditionMax Units Conditions C I/O Input/Output Capacitance (SDA)8pF V I/O = 0V C IN Input Capacitance (A 0, A 1, A 2, SCL)6pFV IN = 0VTable 3. DC CharacteristicsApplicable over recommended operating range from: T AI = –40°C to +85°C, V CC = +1.8V to +5.5V, T AC = 0°C to +70°C,V CC = +1.8V to +5.5V (unless otherwise noted).Symbol Parameter Test ConditionMin TypMax Units V CC1Supply Voltage 1.8 5.5V V CC2Supply Voltage 2.5 5.5V V CC3Supply Voltage 2.7 5.5V V CC4Supply Voltage4.55.5V I CC Standby Current V CC = 5.0V READ at 100 kHz 0.4 1.0mA I CC Standby Current V CC = 5.0V WRITE at 100 kHz 2.0 3.0mA I SB1Standby Current V CC = 1.8V V IN = V CC or V SS 0.6 3.0µA I SB2Standby Current V CC = 2.5V V IN = V CC or V SS 1.4 4.0µA I SB3Standby Current V CC = 2.7V V IN = V CC or V SS 1.6 4.0µA I SB4Standby Current V CC = 5.0V V IN = V CC or V SS 8.018.0µA I LI Input Leakage Current V IN = V CC or V SS 0.10 3.0µA I LO Output Leakage Current V OUT = V CC or V SS0.05 3.0µA V IL (1)Input Low Level –0.6V CC x 0.3V V IH (1)Input High LevelV CC x 0.7V CC + 0.5V V OL2Output Low Level V CC = 3.0V I OL = 2.1 mA 0.4V V OL1Output Low Level V CC = 1.8VI OL = 0.15 mA 0.2V5AT24C1640105J–SEEPR–12/06Note:1.These parameters are characterized and is not 100% tested.Table 4. AC CharacteristicsApplicable over recommended operating range from T A = –40°C to +85°C, V CC = +1.8V to +5.5V, CL = 1 TTL Gate and 100pF (unless otherwise noted).Symbol Parameter2.7-, 2.5-, 1.8-volt5.0-volt Units MinMax MinMax f SCL Clock Frequency, SCL 100400kHz t LOW Clock Pulse Width Low 4.7 1.2µs t HIGH Clock Pulse Width High 4.00.6µs t I Noise Suppression Time (1)10050ns t AA Clock Low to Data Out Valid0.1 4.50.10.9µs t BUF Time the bus must be free before a new transmission can start (1)4.7 1.2µs t HD.STA Start Hold Time 4.00.6µs t SU.STA Start Set-up Time 4.70.6µs t HD.DAT Data In Hold Time 00µs t SU.DAT Data In Set-up Time 200100ns t R Inputs Rise Time (1) 1.00.3µs t F Inputs Fall Time (1)300300ns t SU.STO Stop Set-up Time 4.70.6µs t DH Data Out Hold Time 10050ns t WRWrite Cycle Time 1010ms Endurance (1) 5.0V, 25°C, Page Mode1M 1MWrite cycles6AT24C1640105J–SEEPR–12/06Device OperationCLOCK and DATA TRANSITIONS: The SDA pin is normally pulled high with an exter-nal device. Data on the SDA pin may change only during SCL low time periods (refer to Data Validity timing diagram). Data changes during SCL high periods will indicate a start or stop condition as defined below.START CONDITION: A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (see Figure 5 on page 8).STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition.After a read sequence, the stop command will place the EEPROM in a standby power mode (see Figure 5 on page 8).ACKNOWLEDGE: All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a zero to acknowledge that it has received each word. This happens during the ninth clock cycle.STANDBY MODE: The AT24C164 features a low power standby mode which is enabled: a) upon power-up and b) after the receipt of the STOP bit and the completion of any internal operations.MEMORY RESET: After an interruption in protocol, power loss or system reset, the AT24C164 can be reset by following these steps:(a) Clock up to 9 cycles, (b) look for SDA high in each cycle while SCL is high and then (c) create a start condition as SDA is high.7AT24C1640105J–SEEPR–12/06Figure 2. Bus TimingSCL: Serial Clock, SDA: Serial Data I/OFigure 3. Write Cycle TimingSCL: Serial Clock, SDA: Serial Data I/ONote:1.The write cycle time t WR is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.Figure 4.Data Validity8AT24C1640105J–SEEPR–12/06Figure 5. Start and Stop DefinitionFigure 6.Output Acknowledge9AT24C1640105J–SEEPR–12/06Device AddressingThe AT24C164 requires an 8-bit device address word following a start condition to enable the chip for read or write operations (see Figure 7 on page 10). The most signifi-cant bit must be a one followed by the A2, A1 and A0 device select bits (the A1 bit must be the compliment of the A1 input pin signal). The next 3 bits are used for memory block addressing and select one of the eight 256 x 8 memory blocks. These bits should be considered the three most significant bits of the data word address. The eighth bit of the device address is the read/write select bit. A read operation is selected if this bit is high or a write operation is selected if this bit is low.Upon a compare of the device address, the EEPROM will output a zero. If a compare is not made, the chip will return to a standby state.Write OperationsBYTE WRITE: A write operation requires an 8-bit data word address following the device address word and acknowledgment. Upon receipt of this address, the EEPROM will again respond with a zero and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a zero and the addressing device, such as a microcontroller, must terminate the write sequence with a stop condi-tion. At this time the EEPROM enters an internally-timed write cycle, t WR , to the nonvolatile memory. All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (see Figure 8 on page 11).PAGE WRITE: The AT24C164 is capable of a 16-byte page write. A page write is initi-ated the same as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to fifteen more data words. The EEPROM will respond with a zero after each data word received. The microcontroller must terminate the page write sequence with a stop condition (see Figure 9 on page 11).The data word address lower 4 bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented retaining the memory page row location. When the word address, internally generated, reaches the page boundary, the following byte is placed at the beginning of the same page. If more than sixteen data words are transmitted to the EEPROM, the data word address will “roll over” and previous data will be overwritten.ACKNOWLEDGE POLLING: Once the internally-timed write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves send-ing a start condition followed by the device address word. The read/write bit is representative of the operation desired. Only if the internal write cycle has completed will the EEPROM respond with a zero allowing the read or write sequence to continue.10AT24C1640105J–SEEPR–12/06Read OperationsRead operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to one. There are three read operations: current address read, random address read and sequential read.CURRENT ADDRESS READ: The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address “roll over” during read is from the last byte of the last memory page to the first byte of the first page. The address “roll over” during write is from the last byte of the cur-rent page to first byte of the same page.Once the device address with the read/write select bit set to one is clocked in and acknowledged by the EEPROM, the current address data word is serially clocked out.The microcontroller does not respond with an input zero but does generate a following stop condition (see Figure 10 on page 11).RANDOM READ: A random read requires a “dummy” byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition. The microcontroller now initiates a current address read by sending a device address with the read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a zero but does generate a following stop condition (see Figure 11 on page 11).SEQUENTIAL READ: Sequential reads are initiated by either a current address read or a random address read. After the microcontroller receives a data word, it responds with an acknowledge. As long as the EEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address limit is reached, the data word address will “roll over” and the sequen-tial read will continue. The sequential read operation is terminated when the microcontroller does not respond with a zero but does generate a following stop condi-tion (see Figure 12 on page 12).Figure 7.Device Address分销商库存信息:ATMELAT24C164-10SU-2.7AT24C164-10PU-1.8AT24C164-10PU-2.7 AT24C164-10SU-1.8。

X24C16S8MB-3.5资料

1Serial E 2PROM© Xicor, 1991 Patents PendingCharacteristics subject to change without noticeDESCRIPTIONThe X24C16 is a CMOS 16,384 bit serial E 2PROM,internally organized 2048 X 8. The X24C16 features a serial interface and software protocol allowing operation on a simple two wire bus.The X24C16 is fabricated with Xicor’s advanced CMOS Textured Poly Floating Gate Technology.The X24C16 utilizes Xicor’s proprietary Direct Write TM cell providing a minimum endurance of 100,000 cycles and a minimum data retention of 100 years.FEATURES •2.7V to 5.5V Power Supply •Low Power CMOS—Active Read Current Less Than 1 mA —Active Write Current Less Than 3 mA —Standby Current Less Than 50 µA •Internally Organized 2048 x 8•2 Wire Serial Interface—Bidirectional Data Transfer Protocol •Sixteen Byte Page Write Mode—Minimizes Total Write Time Per Byte •Self Timed Write Cycle—Typical Write Cycle Time of 5 ms •High Reliability—Endurance: 100,000 Cycles —Data Retention: 100 Years•8 Pin Mini-DIP, 8 Pin SOIC and 14 Pin SOIC Packages16KX24C162048 x 8 BitFUNCTIONAL DIAGRAM3840 FHD F01(8) V (4) V (6) SCL 3840-1.1 7/29/96 T1/C0/D0 SH2X24C16NC A 0A 1NC A 2V SS NC1234567141312111098NC V CC TEST NC SCL SDA NCX24C16A 0A 1A 2V SS12348765V CC TEST SCL SDAX24C16PIN CONFIGURATIONPIN DESCRIPTIONS Serial Clock (SCL)The SCL input is used to clock all data into and out of the device.Serial Data (SDA)SDA is a bidirectional pin used to transfer data into and out of the device. It is an open drain output and may be wire-ORed with any number of open drain or open collector outputs.An open drain output requires the use of a pull-up resistor. For selecting typical values, refer to the Pull-Up Resistor selection graph at the end of this data sheet.Address (A 0, A 1, A 2)The A 0, A 1 and A 2 inputs are unused by the X24C16,however, they must be tied to V SS to insure proper device operation.3840 FHD F023840 FHD F03PIN NAMESSymbol Description A 0–A 2Address Inputs SDA Serial Data SCL Serial Clock TEST Hold at V SS V SS GroundV CC Supply Voltage NCNo Connect3840 PGM T01SOICDIP/SOICX24C163DEVICE OPERATIONThe X24C16 supports a bidirectional bus oriented pro-tocol. The protocol defines any device that sends data onto the bus as a transmitter, and the receiving device as the receiver. The device controlling the transfer is a master and the device being controlled is the slave. The master will always initiate data transfers, and provide the clock for both transmit and receive operations.Therefore, the X24C16 will be considered a slave in all applications.Clock and Data ConventionsData states on the SDA line can change only during SCL LOW. SDA state changes during SCL HIGH are re-served for indicating start and stop conditions. Refer to Figures 1 and 2.Start ConditionAll commands are preceded by the start condition,which is a HIGH to LOW transition of SDA when SCL is HIGH. The X24C16 continuously monitors the SDA and SCL lines for the start condition and will not respond to any command until this condition has been met.Figure 1. Data Validity3840 FHD F06SCLSDADATA STABLEDATA CHANGEX24C16Stop ConditionAll communications must be terminated by a stop con-dition, which is a LOW to HIGH transition of SDA when SCL is HIGH. The stop condition is also used by the X24C16 to place the device into the standby power mode after a read sequence. A stop condition can only be issued after the transmitting device has released the bus.AcknowledgeAcknowledge is a software convention used to indicate successful data transfer. The transmitting device, either master or slave, will release the bus after transmitting eight bits. During the ninth clock cycle the receiver will pull the SDA line LOW to acknowledge that it received the eight bits of data. Refer to Figure 3.The X24C16 will respond with an acknowledge after recognition of a start condition and its slave address. If both the device and a write operation have been se-lected, the X24C16 will respond with an acknowledge after the receipt of each subsequent eight bit word.In the read mode the X24C16 will transmit eight bits of data, release the SDA line and monitor the line for an acknowledge. If an acknowledge is detected and no stop condition is generated by the master, the X24C16 will continue to transmit data. If an acknowledge is not detected, the X24C16 will terminate further data trans-missions. The master must then issue a stop condition to return the X24C16 to the standby power mode and place the device into a known state.Figure 2. Definition of Start and StopSCLSDASTART BIT STOP BIT3840 FHD F07 Figure 3. Acknowledge Response From ReceiverSCL FROMMASTERDATAOUTPUTFROMTRANSMITTER189DATAOUTPUTFROMRECEIVERSTART ACKNOWLEDGE3840 FHD F084X24C165Figure 4. Slave AddressDEVICE ADDRESSINGFollowing a start condition the master must output the address of the slave it is accessing. The most significant four bits of the slave address are the device type identifier (see Figure 4). For the X24C16 this is fixed as 1010[B].The next three bits of the slave address field are the bank select bits. They are used by the host to toggle between the eight 256 x 8 banks of memory. These are, in effect,the most significant bits for the word address.The next three bits of the slave address are an extension of the array’s address and are concatenated with the eight bits of address in the word address field, providing direct access to the whole 2048 x 8 array.Following the start condition, the X24C16 monitors the SDA bus comparing the slave address being transmit-ted with its slave address (device type). Upon a correct compare the X24C16 outputs an acknowledge on the SDA line. Depending on the state of the R/W bit, the X24C16 will execute a read or write operation.WRITE OPERATIONS Byte WriteFor a write operation, the X24C16 requires a second address field. This address field is the word address,comprised of eight bits, providing access to any one of the 2048 words in the array. Upon receipt of the word address the X24C16 responds with an acknowledge, and awaits the next eight bits of data, again responding with an acknowledge. The master then terminates the transfer by generating a stop condition, at which time the X24C16begins the internal write cycle to the nonvolatile memory.While the internal write cycle is in progress the X24C16inputs are disabled, and the device will not respond to any requests from the master. Refer to Figure 5 for the address, acknowledge and data transfer sequence.3840 FHD F09Figure 5. Byte WriteBUS ACTIVITY:MASTERSDA LINE BUS ACTIVITY:X24C16S T A R T SLAVE ADDRESS SS T O P P A C KA C KA C KWORD ADDRESSDATA3840 FHD F1011A2A1A0R/WDEVICE TYPE IDENTIFIER HIGH ORDER WORD ADDRESSX24C16Page WriteFlow 1. ACK Polling Sequence Array The X24C16 is capable of a sixteen byte page writeoperation. It is initiated in the same manner as the bytewrite operation, but instead of terminating the write cycleafter the first data word is transferred, the master cantransmit up to fifteen more words. After the receipt ofeach word, the X24C16 will respond with an acknowl-edge.After the receipt of each word, the four low order addressbits are internally incremented by one. The high orderseven bits of the address remain constant. If the mastershould transmit more than sixteen words prior to gener-ating the stop condition, the address counter will “rollover” and the previously written data will be overwritten.As with the byte write operation, all inputs are disableduntil completion of the internal write cycle. Refer toFigure 6 for the address, acknowledge and data transfersequence.Acknowledge PollingThe disabling of the inputs can be used to take advan-tage of the typical 5 ms write cycle time. Once the stopcondition is issued to indicate the end of the host’s writeoperation the X24C16 initiates the internal write cycle.ACK polling can be initiated immediately. This involvesissuing the start condition followed by the slave addressfor a write operation. If the X24C16 is still busy with thewrite operation no ACK will be returned. If the X24C16has completed the write operation an ACK will bereturned and the host can then proceed with the nextread or write operation. Refer to Flow 1.Figure 6. Page Write6X24C167READ OPERATIONSRead operations are initiated in the same manner as write operations with the exception that the R/W bit of the slave address is set to a one. There are three basic read operations: current address read, random read and sequential read.It should be noted that the ninth clock cycle of the read operation is not a “don’t care.” To terminate a read operation, the master must either issue a stop condition during the ninth cycle or hold SDA HIGH during the ninth clock cycle and then issue a stop condition.Current Address ReadInternally the X24C16 contains an address counter that maintains the address of the last word accessed,incremented by one. Therefore, if the last access (either a read or write) was to address n, the next read operation would access data from address n + 1. Upon receipt of the slave address with the R/W bit set to one, the X24C16 issues an acknowledge and transmits the eight bit word. The read operation is terminated by the master;by not responding with an acknowledge and by issuing a stop condition. Refer to Figure 7 for the sequence of address, acknowledge and data transfer.Random ReadRandom read operations allow the master to access any memory location in a random manner. Prior to issuing the slave address with the R/W bit set to one, the master must first perform a “dummy” write operation. The mas-ter issues the start condition, and the slave address followed by the word address it is to read. After the word address acknowledge, the master immediately reissues the start condition and the slave address with the R/W bit set to one. This will be followed by an acknowledge from the X24C16 and then by the eight bit word. The read operation is terminated by the master; by not responding with an acknowledge and by issuing a stop condition.Refer to Figure 8 for the address, acknowledge and data transfer sequence.Figure 7. Current Address ReadBUS ACTIVITY:MASTERSDA LINE BUS ACTIVITY:X24C16S TAR T SLAVE ADDRESSSS T O P PA C KDATA3840 FHD F13Figure 8. Random ReadBUS ACTIVITY:MASTERSDA LINE BUS ACTIVITY:X24C16S TAR T SLAVE ADDRESS SS T O P PA C KA C K A C KWORD ADDRESS n SLAVE ADDRESSDATA nS T A R T S3840 FHD F14X24C16Sequential ReadSequential reads can be initiated as either a current address read or random access read. The first word is transmitted as with the other read modes, however, the master now responds with an acknowledge, indicating it requires additional data. The X24C16 continues to out-put data for each acknowledge received. The read operation is terminated by the master; by not responding with an acknowledge and by issuing a stop condition.The data output is sequential, with the data from address n followed by the data from n + 1. The address counter for read operations increments all address bits, allowing the entire memory contents to be serially read during one operation. At the end of the address space (address 2047), the counter “rolls over” to 0 and the X24C16 continues to output data for each acknowledge re-ceived. Refer to Figure 9 for the address, acknowledge and data transfer sequence.Figure 9. Sequential ReadFigure 10. Typical System Configuration8X24C169ABSOLUTE MAXIMUM RATINGS*Temperature Under Bias..................–65°C to +135°C Storage Temperature.......................–65°C to +150°C Voltage on any Pin withRespect to V SS ................................–1.0V to +7.0V D.C. Output Current ............................................5 mA Lead Temperature(Soldering, 10 Seconds).............................300°C *COMMENTStresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device.This is a stress rating only and the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating condi-tions for extended periods may affect device reliability.D.C. OPERATING CHARACTERISTICS (Over the recommended operating conditions, unless otherwise specified)LimitsSymbol ParameterMin.Max.Units Test Conditionsl CC1V CC Supply Current (read)1SCL = V CC x 0.1/V CC x 0.9 Levels l CC2V CC Supply Current (write)3mA @ 100 KHz, SDA = Open, All Other Inputs = GND or V CC – 0.3VI SB1(1)V CC Standby Current 150µA SCL = SDA = V CC – 0.3V, All Other Inputs = GND or V CC , V CC = 5.5V I SB2(1)V CC Standby Current 50µA SCL = SDA = V CC – 0.3V, All OtherInputs = GND or V CC , V CC = 3.3V +10%I LI Input Leakage Current 10µA V IN = GND to V CC I LO Output Leakage Current 10µA V OUT = GND to V CCV lL (2)Input Low Voltage –1.0V CC x 0.3V V IH (2)Input High Voltage V CC x 0.7V CC + 0.5V V OLOutput Low Voltage0.4VI OL = 3 mA3840 PGM T03CAPACITANCE T A = 25°C, f = 1.0 MHz, V CC = 5VSymbol ParameterMax.Units Test ConditionsC I/O (3)Input/Output Capacitance (SDA)8pF V I/O = 0V C IN (3)Input Capacitance (A 0, A 1, A 2, SCL)6pFV IN = 0V3840 PGM T05Notes:(1)Must perform a stop command prior to measurement.(2)V IL min. and V IH max. are for reference only and are not tested.(3)This parameter is periodically sampled and not 100% tested.RECOMMENDED OPERATING CONDITIONSTemperature mercial 0°C 70°C Industrial –40°C +85°C Military–55°C+125°C3840 PGM T09Supply Voltage Limits X24C16 4.5V to 5.5V X24C16–3.5 3.5V to 5.5V X24C16–33V to 5.5V X24C16–2.72.7V to 5.5V3840 PGM T1010X24C16A.C. CHARACTERISTICS LIMITS (Over the recommended operating conditions unless otherwise specified.)Read & Write Cycle Limits Symbol ParameterMin.Max.Units f SCL SCL Clock Frequency0100KHz T I Noise Suppression Time Constant at SCL, SDA Inputs 100ns t AA SCL Low to SDA Data Out Valid 0.3 3.5µs t BUF Time the Bus Must Be Free Before a 4.7µs New Transmission Can Start t HD:STA Start Condition Hold Time 4.0µs t LOW Clock Low Period 4.7µs t HIGH Clock High Period4.0µs t SU:STA Start Condition Setup Time (for a Repeated Start Condition) 4.7µs t HD:DAT Data In Hold Time 0µs t SU:DAT Data In Setup Time250ns t R SDA and SCL Rise Time 1µs t FSDA and SCL Fall Time 300ns t SU:STO Stop Condition Setup Time 4.7µst DH Data Out Hold Time300ns3840 PGM T06POWER-UP TIMINGSymbol ParameterMax.Units t PUR (4)Power-up to Read Operation 1ms t PUW (4)Power-up to Write Operation5ms3840 PGM T07Notes:(4)t PUR and t PUW are the delays required from the time V CC is stable until the specified operation can be initiated. These parametersare periodically sampled and not 100% tested.A.C. CONDITIONS OF TEST Input Pulse Levels V CC x 0.1 to V CC x 0.9Input Rise and Fall Times10 ns Input and Output Timing LevelsV CC x 0.53840 PGM T02EQUIVALENT A.C. LOAD CIRCUITWRITE CYCLE LIMITSSymbol Parameter Min.Typ.(5)Max.Units t WR (6)Write Cycle Time510ms3840 PGM T08The write cycle time is the time from a valid stop condition of a write sequence to the end of the internal erase/program cycle. During the write cycle, the X24C16bus interface circuits are disabled, SDA is allowed to remain high, and the device does not respond to its slave address.Write Cycle TimingGuidelines for Calculating Typical Values of Bus Pull-Up ResistorsSYMBOL TABLEMust be steadyWill be steady May change from Low to High Will change from Low to High May change from High to Low Will change from High to Low Don’t Care:Changes AllowedChanging:State Not Known N/ACenter Line is High ImpedanceOUTPUTS INPUTS WAVEFORMNotes:(5)Typical values are for T A = 25°C and nominal supply voltage (5V)(6)t WR is the minimum cycle time from the system perspective when polling techniques are not used. It is the maximum time thedevice requires to perform the internal write operation.3926 FHD F01NOTE:1. ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)2. PACKAGE DIMENSIONS EXCLUDE MOLDING FLASHTYP 8-LEAD PLASTIC DUAL IN-LINE PACKAGE TYPE PMAX.8-LEAD PLASTIC SMALL OUTLINE GULL WING P ACKAGE TYPE SNOTE: ALL DIMENSIONS IN INCHES (IN P ARENTHESIS IN MILLIMETERS)3926 FHD F2214-LEAD PLASTIC SMALL OUTLINE GULL WING P ACKAGE TYPE SNOTE: ALL DIMENSIONS IN INCHES (IN P ARENTHESES IN MILLIMETERS)3926 FHD F10ORDERING INFORMATIONDeviceV CC RangeBlank = 4.5V to 5.5V 3.5 = 3.5V to 5.5V 3 = 3V to 5.5V 2.7 = 2.7V to 5.5VTemperature RangeBlank = Commercial = 0°C to +70°C I = Industrial = –40°C to +85°C M = Military = –55°C to +125°C MB = MIL-STD-883PackageP = 8-Lead Plastic DIP S8 = 8-Lead SOIC S14 = 14-Lead SOICX24C16XX-XLIMITED WARRANTYDevices sold by Xicor, Inc. are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Xicor, Inc. makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Xicor, Inc. makes no warranty of merchantability or fitness tor any purpose. Xicor, Inc. reserves the right to discontinue production and change specifications and prices at any time and without notice.Xicor, Inc assumes no responsibility for the use of any circuitry other than circuitry embodied in a Xicor, Inc. product. No other circuits, patents,licenses are implied.US. PATENTSXicor products are covered by one or more of the following U.S. Patents: 4,263,664; 4,274,012; 4,300,212; 4,314,265; 4,326,134; 4,393,481;4,404,475; 4,450,402; 4,486,769; 4,488,060; 4,520,461; 4,533,846; 4,599,706; 4,617,652; 4,668,932; 4,752,912; 4,829,482; 4,874,967;4,883,976; 4,980,859; 5,012,132; 5,003,197; 5,023,694. Foreign patents and additional patents pending.LIFE RELATED POLICYIn situations where semiconductor component failure may endanger life, system designers using this product should design the system with appropriate error detection and correction, redundancy and back-up features to prevent such an occurrence.Xicor’s products are not authorized for use as critical components in life support devices or systems.1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life,and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its satety or effectiveness.Part Mark ConventionP = 8-Lead Plastic DIP S8 = 8-Lead SOIC S14 = 14-Lead SOICBlank = 4.5V to 5.5V, 0°C to +70°C I = 4.5V to 5.5V, –40°C to +85°C B = 3.5V to 5.5V, 0°C to +70°C C = 3.5V to 5.5V, –40°C to +85°C D = 3.0V to 5.5V, 0°C to +70°C E = 3.0V to 5.5V, –40°C to +85°C F = 2.7V to 5.5V, 0°C to +70°C G = 2.7V to 5.5V, –40°C to +85°C M = 4.5V to 5.5V, –55°C to +125°CX24C16 XX。

FTTH箱体功能使用介绍

箱体功能 适用于一级分光模式的末端分纤,和入

户皮线光缆熔接; 适用弱电井、楼道内等室内安装环境。

7

中国网电络信发广展东部公司

综合部

光分路箱-室外、室内用64芯分路箱

箱体配置 64芯光分路箱有5条光缆固定装置; 可安装1:64机架式分光器1个; 可安装12芯熔储一体框6套; 最大可成端72芯配线光缆(或皮线光缆,

12芯熔配一体化托盘,迷你型,尺寸: 25*212*180。含托盘、12芯0.9束状尾 纤、12个SC法兰盘。

用于144/216/288芯光分路箱,和配线光缆 直熔成端用。

5 12芯一体化托盘

HBBT-12

12芯熔配一体化托盘,集团标准型号,尺寸: 25*302*180。

用于360/576/720芯落地型光分路箱。

箱体功能 适用于一级分光方式1个1:64分光器安

装,配线光缆或皮线光缆可成端跳接分

光器或皮线光缆快速接头跳接分光器;

适用弱电井、楼道内外侧等室内、外安

装环境。

8

中国网电络信发广展东部公司

综合部

光分路箱-室外用144芯分路箱

箱体配置 144芯光分路箱有7条光缆固定装置; 可安装1:64盒式分光器4个,1:8盒式

不含主光盘、备用盘)。 配件12芯熔储一体框包括熔纤盘、储纤

盘、SC2.0全色谱尾纤12条(内外一致, 1.2m),均已成套配好; 室内型皮线光缆熔纤盘可拿到地面安装。

箱体型号:HBFL-64Ⅰ(Ⅱ),尺寸: 550*510*140mm,(高*宽*厚)。

室外用箱体,镀锌钢板厚1.2mm, 室内用冷轧钢板1.0mm。

河北电信FTTH箱体功能介绍

1

FTTH箱体功能介绍 FTTH建设方案推荐

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。