FPGA读写i2c_verilog

iic协议--Verilog及仿真

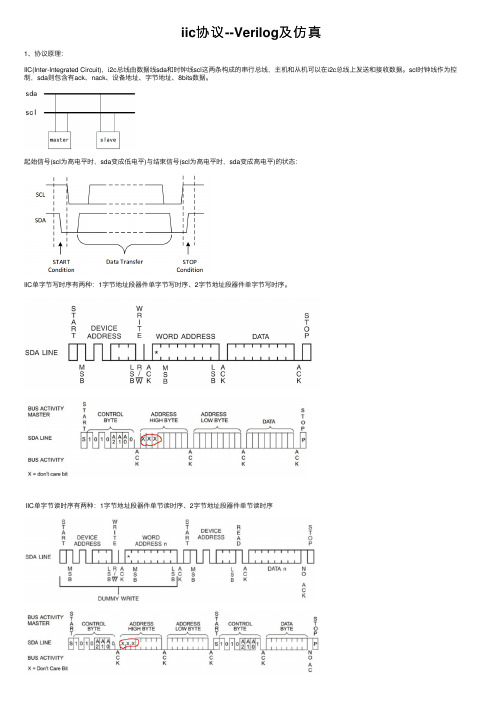

iic协议--Verilog及仿真1、协议原理:IIC(Inter-Integrated Circuit),i2c总线由数据线sda和时钟线scl这两条构成的串⾏总线,主机和从机可以在i2c总线上发送和接收数据。

scl时钟线作为控制,sda则包含有ack、nack、设备地址、字节地址、8bits数据。

起始信号(scl为⾼电平时,sda变成低电平)与结束信号(scl为⾼电平时,sda变成⾼电平)的状态:IIC单字节写时序有两种:1字节地址段器件单字节写时序、2字节地址段器件单字节写时序。

IIC单字节读时序有两种:1字节地址段器件单节读时序、2字节地址段器件单节读时序字节地址⾼三位xxx:这⾥使⽤的EEPROM的存储容量只有8192bits(1024bits*8)=210*23=213,所以16位的字节地址就多余了三位。

2、协议代码:1、这⾥实现的是2字节单次读写。

2、开始和结束时,虽然scl为⾼电平,sda仍要变化;接下来传输字节,scl为低电平,sda才能变化。

这⾥采取在scl⾼电平和低电平中线产⽣标志。

3、通过状态机来实现读写。

综合代码:module IIC_AT24C64(input sys_clk,input sys_rst_n,input iic_en,input [2:0]cs_bit,//可编程地址input [12:0]byte_address,//字节地址input write,input read,input [7:0]write_data,output reg[7:0]read_data,output reg scl,inout sda,output reg done);parameterSYS_CLK=50_000_000,//系统时钟50MHzSCL_CLK=200_000;//scl时钟200KHzreg [7:0]scl_cnt;//时钟计数parameter div_cnt=SYS_CLK/SCL_CLK;always @(posedge sys_clk or negedge sys_rst_n)beginif(!sys_rst_n)scl_cnt<=8'd0;else if(scl_cnt == div_cnt-1'b1)scl_cnt<=8'd0;elsescl_cnt<=scl_cnt+1'b1;end//⽣成scl时钟线always @(posedge sys_clk or negedge sys_rst_n)beginif(!sys_rst_n)scl<=1'b1;else if(scl_cnt == (div_cnt>>1)-1'b1)scl<=1'b0;else if(scl_cnt == div_cnt-1'b1)scl<=1'b1;elsescl<=scl;end//scl电平中线reg scl_high_middle;//scl⾼电平中线reg scl_low_middle;//scl低电平中线always @(posedge sys_clk or negedge sys_rst_n)beginscl_high_middle<=1'b0;scl_low_middle<=1'b0;endelse if(scl_cnt == (div_cnt>>2))scl_high_middle<=1'b1;else if(scl_cnt == (div_cnt>>1)+(div_cnt>>2))scl_low_middle<=1'b1;else beginscl_high_middle<=1'b0;scl_low_middle<=1'b0;endendreg [15:0]state;parameteridle=16'd1,//空闲状态w_or_r_start=16'd2,//设备地址device_ADDR=16'd3,//发送ACK1=16'd4,byte_ADDR_high=16'd5,//字节地址⾼8位ACK2=16'd6,byte_ADDR_low=16'd7,//字节地址低8位ACK3=16'd8,w_data=16'd9,//写数据ACK4=16'd10,r_start=16'd11,//读开始device_ADDR_r=16'd12,//设备地址读ACK5=16'd13,r_data=16'd14,//读数据NACK=16'd15,//⾮应答位stop=16'd16;reg sda_en;//sda数据线使能reg sda_reg;//sda数据暂存位reg [7:0]sda_data_out;//sda数据发给从机暂存reg [7:0]sda_data_in;//sda数据取之从机暂存reg [3:0]bit_cnt;//每⼀bitassign sda=sda_en?sda_reg:1'bz;//读写标志位reg w_flag;reg r_flag;always @(posedge sys_clk or negedge sys_rst_n)beginif(!sys_rst_n)beginstate<=idle;w_flag<=1'b0;r_flag<=1'b0;sda_reg<=1'b1;done<=1'b0;sda_en<=1'b0;endelse begincase(state)idle:beginsda_reg<=1'b1;w_flag<=1'b0;r_flag<=1'b0;sda_en<=1'b0;sda_reg<=1'b1;done<=1'b0;if(iic_en && write)beginw_flag<=1'b1;sda_en<=1'b1;sda_reg<=1'b1;state<=w_or_r_start;endelse if(iic_en && read)beginr_flag<=1'b1;sda_en<=1'b1;sda_reg<=1'b1;state<=w_or_r_start;endelsestate<=idle;endw_or_r_start:beginif(scl_high_middle)beginsda_reg<=1'b0;sda_data_out<={4'b1010,cs_bit,1'b0};//在这⾥装好设备地址bit_cnt<=4'd8;state<=device_ADDR;endelse beginsda_reg<=1'b1;state<=w_or_r_start;endenddevice_ADDR:beginif(scl_low_middle)beginsda_reg<=sda_data_out[7];sda_data_out<={sda_data_out[6:0],1'b0};//在这⾥发出设备地址。

使用Verilog来实现EEPROM的读写,进行一个简单的I2C实战应用

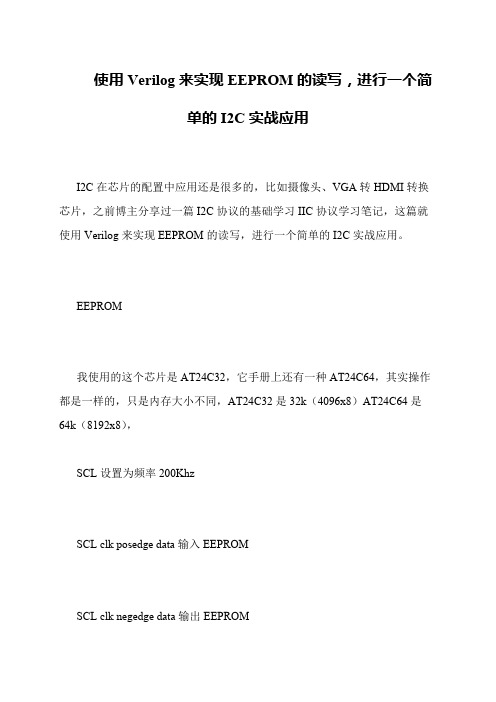

使用Verilog来实现EEPROM的读写,进行一个简单的I2C实战应用 I2C在芯片的配置中应用还是很多的,比如摄像头、VGA转HDMI转换芯片,之前博主分享过一篇I2C协议的基础学习IIC协议学习笔记,这篇就使用Verilog来实现EEPROM的读写,进行一个简单的I2C实战应用。

EEPROM 我使用的这个芯片是AT24C32,它手册上还有一种AT24C64,其实操作都是一样的,只是内存大小不同,AT24C32是32k(4096x8)AT24C64是64k(8192x8), SCL设置为频率200Khz SCL clk posedge data输入EEPROM SCL clk negedge data输出EEPROM SDA 双向Pin A2,A1,A0 Device Addr default all 0,只操作一片可悬空引脚。

WP 接地正常读写,WP接Vcc写操作被禁止 字节寻址地址,是由12(AT24C32)或13bit(AT24C64)的地址组成,需要操作16位字地址高3或4位忽略即可。

Device Address 8’hA0写器件地址,8’hA1读器件地址 写字节操作 随机读字节操作 我这个芯片是双字节数据地址,所以在写数据地址时要写两次,先是高字节后是低字节。

开始结束标志 这个I2C总线的时序是一致的。

EEPROM应答 输出应答sclk的第九个周期给出,低电平应答。

如果主机没有收到应答,需要重新配置。

数据传输时序 sda数据线在scl时钟的下降沿中间变化,可以避免产生误触开始结束标志。

I2C Design i2c_start为高电平有效,传输完成后会产生一个i2c_done结束标志,表示操作完成。

I2C状态转移图 I2C写操作 (1)产生start位 (2)传送器件地址ID_Address,器件地址的最后一位为数据的传输方向位,R/W,低电平0表示主机往从机写数据(W),1表示主机从从机读数据(R)。

fpga常用接口协议

FPGA常用接口协议一、引言FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,广泛应用于数字电路设计和嵌入式系统中。

FPGA常用接口协议是指连接FPGA与其他外部设备的通信协议,它定义了数据传输的格式、时序和规范,为FPGA与外部设备之间的数据交换提供了基础。

二、常见的FPGA接口协议在FPGA设计中,有许多常见的接口协议被广泛应用。

下面将介绍几种常见的FPGA接口协议:1. SPI(Serial Peripheral Interface)SPI是一种同步串行通信接口协议,常用于连接FPGA与外部设备,如存储器、传感器等。

SPI接口由四条线组成:时钟线(SCLK)、数据线(MOSI)、数据线(MISO)和片选线(SS)。

SPI接口的特点是简单、高速和灵活,但需要占用较多的引脚资源。

2. I2C(Inter-Integrated Circuit)I2C是一种串行通信接口协议,常用于连接FPGA与外部设备,如温度传感器、电压监测芯片等。

I2C接口由两条线组成:时钟线(SCL)和数据线(SDA)。

I2C接口的特点是支持多主机通信和多从机设备,并且能够通过地址选择从机设备。

3. UART(Universal Asynchronous Receiver/Transmitter)UART是一种异步串行通信接口协议,常用于连接FPGA与计算机、调试工具等。

UART接口由两条线组成:发送线(TX)和接收线(RX)。

UART接口的特点是简单、易于实现,并且支持较长的通信距离。

4. EthernetEthernet是一种局域网通信协议,常用于连接FPGA与网络设备,如路由器、交换机等。

Ethernet接口使用RJ45接头,支持高速数据传输和广播通信。

FPGA通过以太网接口可以实现与其他设备的远程通信和数据传输。

5. PCIe(Peripheral Component Interconnect Express)PCIe是一种高速串行总线接口协议,常用于连接FPGA与计算机主板。

用VERILOG HDL实现I2C总线功能

摘要:简述了i2c总线的特点;介绍了开发fpga时i2c总线模块的设计思想;给出并解释了用verilog hdl实现部分i2c总线功能的程序,以及i2c总线主从模式下的仿真时序图。

关键词:i2c总线 fpga verilog hdl 时序开发fpga时,利用eda工具设计芯片实现系统功能已经成为支撑电子设计的通用平台,并逐步向支持系统级的设计方向发展。

在软件设计过程中,越来越强调模块化设计。

i2c总线是philips公司推出的双向两线串行通讯标准,具有接口线少、通讯效率高等特点。

把i2c总线设计成相应的模块,有利于相关fpca的开发。

目前有一些介绍相关开发的资料,但都是利用vhdl语言或ahdl语言实现的。

本文给出利用verilog hdl语言设计的i2c总线模块。

1 i2c总线概述i2c总线系统由两根总线即scl(串行时钟)线和sda(串行数据)线构成。

这种总线可以设计成很多种通讯配置,但本文只讨论主从系统的应用。

主器件控制总线通讯,开始/结束传送、发送信息并产生i2c系统时钟。

在写操作过程中,从器件一旦被主控器件寻址,就执行特定的相应功能。

在读操作过程中,主控器件从从器件那里获得数据。

在整个主从传送过程中,所有的事件都通过主控器件的scl 时钟线达到同步。

连到总线上的器件的接口形式必须是漏极开路或集电极开路输出状态。

通过上拉电阻,使得两根总线在空闲的状态下都为高电平状态。

因此i2c总线上具有线与功能,即总线上的所有器件都达到高电子状态时,i2c总线才能达到高电平状态,从而使总线上的高速器件和慢速器件工作同步。

在i2c协议中,从器件地址是一个唯一的7位地址。

接下来是一个读写方向标志位,读状态是高电平、写状态是低电子。

2 i2c模块的设计与实现根据i2c协议中传输过程的特点,i2c模块可以划分为字节发送模块、字节接收模块、开始条件模块、停止条件模块。

其中,字节发送模块、字节接收模块和停止条件模块为基本模块。

fpga常用接口协议

fpga常用接口协议FPGA常用接口协议随着科技的不断发展,FPGA(现场可编程门阵列)在数字电路设计中的应用越来越广泛。

FPGA常用接口协议是指在FPGA与其他设备之间进行数据交换时所使用的通信协议。

本文将介绍几种常见的FPGA接口协议,包括SPI、I2C、UART和PCIe。

一、SPI(串行外设接口)协议SPI是一种串行通信协议,可以实现FPGA与外设之间的数据传输。

SPI接口由四条线组成,分别是时钟信号(SCLK)、主设备输出从设备输入(MOSI)、主设备输入从设备输出(MISO)和片选信号(CS)。

SPI协议采用主从模式,主设备通过控制时钟信号和片选信号来与从设备进行通信。

SPI接口的优点是通信速度快,但只能实现点对点的通信。

二、I2C(串行总线接口)协议I2C是一种串行通信协议,可以实现FPGA与多个外设之间的数据传输。

I2C接口由两条线组成,分别是时钟信号(SCL)和数据信号(SDA)。

I2C协议采用主从模式,主设备通过控制时钟信号和数据信号来与从设备进行通信。

I2C接口的优点是可以同时连接多个从设备,但通信速度相对较慢。

三、UART(通用异步收发传输)协议UART是一种异步串行通信协议,可以实现FPGA与其他设备之间的数据传输。

UART接口由两条线组成,分别是发送线(TX)和接收线(RX)。

UART协议采用点对点通信,通过发送和接收线来进行数据传输。

UART接口的优点是通信简单易用,但通信速度相对较慢。

四、PCIe(外部总线接口)协议PCIe是一种高速串行总线接口协议,可以实现FPGA与计算机之间的数据传输。

PCIe接口由多条差分信号线组成,包括数据传输线(TX和RX)和控制信号线(CLK、RESET等)。

PCIe协议采用主从模式,通过数据传输线和控制信号线来实现高速数据传输。

PCIe接口的优点是通信速度快,但连接和配置相对复杂。

总结:本文介绍了几种常见的FPGA常用接口协议,包括SPI、I2C、UART 和PCIe。

FPGA和单片机串行通信接口的实现

FPGA和单片机串行通信接口的实现FPGA(Field-Programmable Gate Array)和单片机(Microcontroller)是两种常用的数字电子设备,它们在串行通信接口方面有不同的实现方式。

首先,我们需要了解串行通信是一种将数据以位的形式逐个传输的通信方式。

常见的串行通信协议包括UART(Universal Asynchronous Receiver/Transmitter)、SPI(Serial Peripheral Interface)和I2C (Inter-Integrated Circuit)等。

对于FPGA和单片机之间的串行通信,我们可以基于以下几种方式进行实现:1. UART:UART是一种常见的串行通信协议,可以实现全双工的通信。

在FPGA和单片机之间建立UART通信,需要在FPGA中实现UART模块,并将其与单片机的UART接口连接。

在FPGA中,我们可以使用硬件语言(如Verilog或VHDL)来实现UART模块,该模块负责将FPGA内部的数据通过UART协议进行封装和解封装。

单片机与FPGA之间通过TX(发送)和RX (接收)引脚建立连接。

单片机可以通过串口发送数据给FPGA,FPGA接收到数据后进行处理,然后再通过串口将处理后的数据发送给单片机。

2.SPI:SPI是一种用于片上外设之间通信的串行通信协议,常用于FPGA与外部设备(例如传感器、显示器等)之间的通信。

在FPGA和单片机之间建立SPI通信,需要在FPGA中实现SPI控制器,并将其与单片机的SPI接口连接。

FPGA通过把数据写入SPI发送缓冲区或从SPI接收缓冲区读取数据来实现与单片机的通信。

单片机通过控制SPI接口的时钟、数据和使能信号来与FPGA进行数据传输。

3.I2C:I2C是一种双线制串行总线,常用于连接多个设备的系统,例如FPGA、单片机和其他外部设备之间的通信。

在FPGA和单片机之间建立I2C通信,需要在FPGA中实现I2C控制器,并将其与单片机的I2C接口连接。

fpga的iic代码

fpga的iic代码FPGA的IIC代码一、引言随着科技的不断发展,FPGA(Field-Programmable Gate Array)已经成为了数字电路设计领域中不可或缺的一部分。

FPGA具有可编程性强、灵活性高等优点,被广泛应用于各种领域。

而IIC(Inter-Integrated Circuit)作为一种常见的串行通信协议,也是FPGA中常用的模块之一。

本文将介绍FPGA的IIC代码设计及其实现。

二、IIC简介IIC是由飞利浦公司(Philips)提出的一种串行通信协议,用于在集成电路之间进行数据传输。

IIC协议使用两根线,即SDA(串行数据线)和SCL(串行时钟线),实现多个设备之间的通信。

IIC协议具有速度快、使用简单等优点,被广泛应用于各种电子设备中。

三、FPGA中的IIC代码FPGA中的IIC代码可以通过硬件描述语言(如Verilog或VHDL)进行实现。

下面是一个简单的FPGA IIC代码示例:module IIC (input wire clk,input wire rst,input wire sda_in,output wire sda_out,inout wire scl);reg [7:0] data_reg;reg [2:0] state_reg;// 状态定义localparam IDLE = 3'b000; // 空闲状态localparam START = 3'b001; // 起始位发送状态localparam WRITE = 3'b010; // 写数据状态localparam READ = 3'b011; // 读数据状态localparam ACK = 3'b100; // ACK状态// 初始化always @(posedge clk or posedge rst) beginif (rst) begindata_reg <= 8'b0;state_reg <= IDLE;end else begincase (state_reg)IDLE: beginif (sda_in == 1'b0 && scl == 1'b1) begin state_reg <= START;endSTART: begin// 发送起始位sda_out <= 1'b0;state_reg <= WRITE;endWRITE: begin// 发送数据sda_out <= data_reg[7];data_reg <= {data_reg[6:0], 1'b0};state_reg <= ACK;endREAD: begin// 读取数据sda_out <= 1'b1;state_reg <= ACK;endACK: begin// 接收ACKif (sda_in == 1'b0) begindata_reg <= {data_reg[6:0], sda_in};state_reg <= IDLE;endendcaseendend// 时钟延迟always @(posedge clk) beginscl <= ~scl;endendmodule四、代码解析上述代码实现了一个简单的FPGA IIC模块。

i2s的verilog代码

i2s的verilog代码i2s的Verilog代码是指用Verilog语言编写的用于实现i2s (Inter-IC Sound)接口功能的代码。

i2s接口是一种常用的音频数据传输接口,广泛应用于音频芯片、音频设备和数字信号处理器等领域。

i2s接口由三根线组成,分别是时钟线(SCLK)、数据线(SD)和帧同步线(WS)。

时钟线用于同步数据的传输,数据线用于传输音频数据,帧同步线用于标志数据的起始和结束。

在Verilog代码中,首先需要定义i2s接口的输入输出端口,并根据接口规范进行信号的定义和赋值。

接下来可以根据具体的应用需求,编写相应的模块和逻辑来实现i2s接口的功能。

一个简单的i2s接口的Verilog代码示例如下:```verilogmodule i2s_interface (input wire SCLK, // 时钟线input wire SD, // 数据线input wire WS, // 帧同步线output wire audio // 音频数据输出);reg [15:0] audio_data; // 音频数据寄存器always @(posedge SCLK) beginif (WS) beginaudio_data <= SD; // 读取音频数据endendassign audio = audio_data; // 输出音频数据endmodule```上述代码中,定义了一个名为i2s_interface的模块,该模块包含了一个i2s接口,输入端口为SCLK、SD和WS,输出端口为audio。

在always块中,通过检测时钟线的上升沿,判断帧同步线的状态,如果帧同步线为高电平,则将数据线的数据存入音频数据寄存器中。

最后,通过assign语句将音频数据输出到audio端口。

需要注意的是,上述代码仅为示例,实际的i2s接口实现可能需要根据具体的应用需求进行修改和优化。

此外,在实际应用中,还需要考虑时序约束、数据格式、时钟频率等因素,以确保i2s接口的正常工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

parameterACK1= 4'd3;

parameterADD2= 4'd4;

parameterACK2= 4'd5;

parameterSTART2= 4'd6;

parameterADD3= 4'd7;

parameterACK3= 4'd8;

parameterDATA= 4'd9;

`define SCL_NEG(cnt==3'd2)//cnt=2:scl下笛?`define SCL_LOW(cnt==3'd3)//cnt=3:scl偷缙街屑?用于数据变化

always @ (posedge clk or negedge rst_n)

if(!rst_n) scl_r <= 1'b0;

end

ACK2:begin

if(/*!sda*/`SCL_NEG) begin//从机响应信号

if(!sw1_r) begin

cstate <= DATA;//写操作

db_r <= `WRITE_DATA;//写入的数据

end

else if(!sw2_r) begin

db_r <= `DEVICE_READ;//送器件地址(读操作),特定地址读需要执行该步骤以下操作

default: ;

endcase

//sda_r <= db_r[4'd7-num];//送EEPROM地址(高bit开始)

cstate <= ADD2;

end

end

//else if(`SCL_POS) db_r <= {db_r[6:0],1'b0};//器件地址左移1bit

else cstate <= ADD2;

);

input clk;// 50MHz

input rst_n;//复位信号,低有效

input sw1,sw2;//按键1、2,(1按下执行写入操作,2按下执行读操作)

output scl;// 24C02的时钟端口

inout sda;// 24C02的数据端口

output[7:0] dis_data;//数码管显示的数据

cstate <= START2;//读操作

end

end

else cstate <= ACK2;//等待从机响应

end

START2: begin//读操作起始位

if(`SCL_LOW) begin

sda_link <= 1'b1;//sda作为output

sda_r <= 1'b1;//拉高数据线sda

sw2_r <= 1'b1;

end

else if(cnt_20ms == 20'hfffff) begin

sw1_r <= sw1;//按键1值锁存

sw2_r <= sw2;//按键2值锁存

end

//---------------------------------------------

//分频部分

4'd1: sda_r <= db_r[6];

4'd2: sda_r <= db_r[5];

4'd3: sda_r <= db_r[4];

4'd4: sda_r <= db_r[3];

4'd5: sda_r <= db_r[2];

4'd6: sda_r <= db_r[1];

4'd7: sda_r <= db_r[0];

4'd3: sda_r <= db_r[4];

4'd4: sda_r <= db_r[3];

4'd5: sda_r <= db_r[2];

4'd6: sda_r <= db_r[1];

4'd7: sda_r <= db_r[0];

default: ;

endcase

//sda_r <= db_r[4'd7-num];//送器件地址,从高位开始

if(!rst_n) cnt_20ms <= 20'd0;

else cnt_20ms <= cnt_20ms+1'b1;//不断计数

always @ (posedge clk or negedge rst_n)

if(!rst_n) begin

sw1_r <= 1'b1;//键值寄存鞲次唬挥屑 贪聪率奔 刀嘉?

reg[7:0] db_r;//在IIC上传送的数据寄存器

reg[7:0] read_data;//读出EEPROM的数据寄存器

//---------------------------------------------

//读、写时序

parameterIDLE= 4'd0;

parameterSTART1= 4'd1;

if(!rst_n) cnt <= 3'd5;

else begin

case (cnt_delay)

9'd124:cnt <= 3'd1;//cnt=1:scl高电平中间,用于数据采样

9'd249:cnt <= 3'd2;//cnt=2:scl下降沿

9'd374:cnt <= 3'd3;//cnt=3:scl低电平中间,用于数据变化

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////

modulபைடு நூலகம் iic_com(

clk,rst_n,

sw1,sw2,

scl,sda,

dis_data

if(num==4'd8) begin

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

cstate <= IDLE;

sda_r <= 1'b1;

sda_link <= 1'b0;

num <= 4'd0;

read_data <= 8'b0000_0000;

end

else

case (cstate)

IDLE:begin

sda_link <= 1'b1;//数据线sda为input

sda_r <= 1'b1;

if(!sw1_r || !sw2_r) begin//SW1,SW2键有一个被按下

db_r <= `DEVICE_WRITE;//送器件地址(写操作)

cstate <= START1;

if(!rst_n) cnt_delay <= 9'd0;

else if(cnt_delay == 9'd499) cnt_delay <= 9'd0;//计数到10us为scl的周期,即100KHz

else cnt_delay <= cnt_delay+1'b1;//时蛹剖?

always @ (posedge clk or negedge rst_n) begin

end

else cstate <= IDLE;//没有任何键被按下

end

START1: begin

if(`SCL_HIG) begin//scl为高电平期间

sda_link <= 1'b1;//数据线sda为output

sda_r <= 1'b0;//拉低数据线sda,产生起始位信号

cstate <= ADD1;

cstate <= START2;

end

else if(`SCL_HIG) begin//scl为高电平中间

sda_r <= 1'b0;//拉低数据线sda,产生起始位信号

cstate <= ADD3;

end

else cstate <= START2;

end

ADD3:begin//送读操作地址

if(`SCL_LOW) begin

// Module Name: iic_top

// Project Name:

// Target Device:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

//需要写入24C02的地址和数据

`defineDEVICE_READ8'b1010_0001//被寻址器件地址(读操作)

`define DEVICE_WRITE8'b1010_0000//被寻址器件地址(写操作)

`defineWRITE_DATA8'b1101_0001//写入EEPROM的数据

`define BYTE_ADDR8'b0000_0011//写入/读出EEPROM的地址寄存器

sda_link <= 1'b0;//sda置为高阻态(input)

cstate <= ACK1;

end

else begin

cstate <= ADD1;