基于μC/OS-Ⅱ与NiosⅡ的以太网接口软件设计

基于NiosⅡ系统的1553B总线网络存储器设计

冲 。它特 别为可编程逻辑 进行 了优 化设 网络命 令及数据 ,另一部分为存 储器的 使 用 。 计 , 为可编程单 芯片 系统 ( o C)设 读 写。在 NI S I 也 SP O DE环境 中 ,使用 C语 ・ Ja — a t P t g u r:F GA与 P C的通 信

‘

1

’r

一 叫

]

Nis I嵌 入 式 处 理 器 是 Alea公 高 ,15 B协议芯 片的单片价 格在 6 0 o I tr 53 00

司于 2 0 年6 0 4 月推 出的第二代用 于可编 元以上 ,这对于普通 应用来说是一 个不

通过 Q a t s I 7 2 成的 S C u ru I . 集 OP

…

} 一

、

l}  ̄i c 一 B ! 5—一 ——u 5 3 —: 一

1 r

≮’

^

^

r f

、

储压力 ,并可 作为数据 中继 供其他部 分 据。对 于总线协议 ,最 方便 的是使用现

甚至其他组 网使用 。 成 的协 议 芯 片 ,但这 样 做 的成 本 非 常

维普资讯

一 应计信 用 : 设通

基于 N 系统的 1 5 sI i o I 3 5 B总线

网络存储器设计

中国移 动通信集 团江西有 限公司 杨俊

本 文 设计 7 5 3 I 5 B总 线上 的 网络 存储 器 。整个 系统 基 于

・ CPU :选 用标 准 型 CPU 核 ,

对 3 5 b g e 为 e e ,在满足需求 的情 能 与用户逻辑 相结合 ,编程 至 Al r t a的 核可供使用 , 于 1 5 B的协 议则需要 De u g r L v l 1 e F GA中。处理 器具 有 3 位指令集 , 2 自行定制组 件。 P 2 3 位数据通道 和可配置的指令以 及数 据缓 系统程 序为两部 分 ,一部分 为接受 况下尽量节 约片 内资 源的使用 。 ・ S se I y tm—D:下载时 系统认证时

Chap8_嵌入式实时操作系统uCOS-Ⅱ分析PPT共109页

学习嵌入式操作系统

学习一种实时操作系统RTOS,如 C/OS-Ⅱ,掌握实时系统的概念和设 计方法

嵌入式系统以应用为中心,要选择 “适用”的操作系统

嵌入式Linux 自己尝试“写”RTOS

13

RTOS在嵌入式系统中的位置

应用

FS C/C++ 设备驱动

RTOS

KERNEL 调试工具

其它组件 TCP/IP 设备I/O

16

C/OS的性能特点(一)

公开源代码 可移植性(Portable)

绝大部分 C/OS-II的源码是用移植性很强的ANSI C写的。和微 处理器硬件相关的那部分是用汇编语言写的。汇编语言写的部 分已经压到最低限度,使得 C/OS-II便于移植到其他微处理器 上。 C/OS-II可以在绝大多数8位、16位、32位以至64位微处理 器、微控制器 、数字信号处理器(DSP)上运行。 可固化(ROMable) C/OS-II是为嵌入式应用而设计的,这就意味着,只要用户有 固化手段(C编译、连接、下载和固化), C/OS-II可以嵌入 到用户的产品中成为产品的一部分。 可裁剪(Scalable) 可以只使用 C/OS-II中应用程序需要的那些系统服务。也就是 说某产品可以只使用很少几个 C/OS-II调用,而另一个产品则 使用了几乎所有 C/OS-II的功能,这样可以减少产品中的 C/OS-II所需的存储器空间(RAM和ROM)。这种可剪裁性是靠 条件编译实现的。

BSቤተ መጻሕፍቲ ባይዱ 嵌入式硬件平台

14

主要内容

嵌入式操作系统 C/OS-Ⅱ简介 C/OS-Ⅱ内核结构 C/OS-Ⅱ任务管理 C/OS-Ⅱ时间管理 C/OS-Ⅱ任务通信与同步

15

C/OS简介

基于fpga与w5500的以太网接口设计

· 83 ·V ol. 59 No. 3工程与试验 ENGINEERING & TEST Sep. 20191 引 言在当代的工业自动化控制中,以太网接口应用已经非常广泛,基本要完全取代之前的ISA、PCI 及PCIE 等接口方式。

但目前国内的以太网控制器多数都是通过单片机、ARM 或者DSP 等CPU 与以太网接口芯片进行连接,在网络或者很多书籍中也大多介绍该方式。

本文介绍了如何通过FPGA 与以太网控制器W5500设计以太网接口方式,该方法在不改变整体控制系统成本的前提下,不但提升了以太网的传输速度,而且节省了DSP 等主要CPU 的资源,更有利于将来整个控制系统的扩展。

2 NIOS Ⅱ内核及W5500介绍相对于以往的DSP、ARM 等CPU 芯片,FPGA 时序控制能力强,没有指令周期,速度快,可以充分发挥以太网的传输速度。

2.1 NIOS Ⅱ内核的作用FPGA 开发以太网接口有两种方式,一是直接通过FPGA 的逻辑门或者verilog 等语言直接编写接口程序,但过程及其繁琐,容易出错,造成网络传输不稳定,而且对于将来的进一步开发扩展没有好处。

第二种方式就是通过NIOS Ⅱ软核方式,NIOS Ⅱ是altera 公司专为altera 的系列FPGA 开发的软核处理器(也就是MCU,但是它是一个软核,需要手动根据具体需求进行添加,添加后,就会在FPGA 里面得到一个NIOS Ⅱ处理器),对NIOS Ⅱ的软件开发是基于C,C++语言或者汇编的语言,软件开发环境是和Qartus2 配套的NIOS Ⅱ IDE。

NIOS Ⅱ也就是软核,在FPGA 的概念中,所谓软件就是在FPGA 内部镶嵌一块CPU,支配FPGA 完成系统的工作,但这些工作一般都是简单的接口程序,无法发挥出FPGA 真正的功效。

有了NIOS Ⅱ就不同了,NIOS Ⅱ就像在FPGA 内部嵌入了一个类似单片机、DSP 一样的CPU,能够完成非常复杂的系统功能。

基于CMOS图像传感器OV2610的NIOSII采集系统设计

nl i

基于 CMoS图像传 感器 oV2 1 6 N● 0的 oS¨ 采集系统设 计

廖 红华

( 北 民族 学院 信 息 工程 学 院 ,湖 北 恩施 湖 45 0 ) 4 0 0 2 1 0的性 能,阐述 了在 N OS I I I软核处理 器的控 制下 ,通过 F C控 [ 摘要] 介 绍 了数 字 CMOS图像传 感器 OV 6

中国电工同

【】石磊. 3 一种基 于单 片机 的高速数据采集系统的设计 与实现

【. J 电测与仪表 , 0 ( ] 2 5) 0 3

2 0 年 1 期 四衄 06 1

3

维普资讯

In l i

F GA 为 Cy ln IE 2 5 6 2 , 其 串 口配 置芯 片 P co eI P C3 F 7 C6

化 、低廉 的价 格使 其 在静 态 图像 捕捉 、 网络视 频 及 图 像 传 输 等 领 域 得 到 了广 泛 的 应 用 。 文 中 介 绍 了 一

种 利 用 Al r t a公 司 的 D 2开 发 板 实 现 对 C OS图像 e E M 传 感 器 OV2 0 的采 集 与 控 制 , 在 该 采 集 过 程 中 系 6 1 统 的 硬 件 设 计 能 够 按 照 软 件 设 计 的 要 求 而 不 断 变

为 E C 1 , 同 时在 板 上 I 设 备 还 有 :能 通 过 F G P S6 / O P A 配 置 的 US ls r US 2 、 1 位 V BBat 、 B . e 0 0 GA方 式 的 D C、 A

( )显 示 电 路 采 用 L 5 CD 大 屏 幕 , 驱 动 芯 片 采 用 P LP HI I S公 司 生产 的 P F 1 1 T字 符 液 晶 驱动 模 块 , C 2 lC

基于OPENCORE及NiosⅡ处理器的片上系统设计

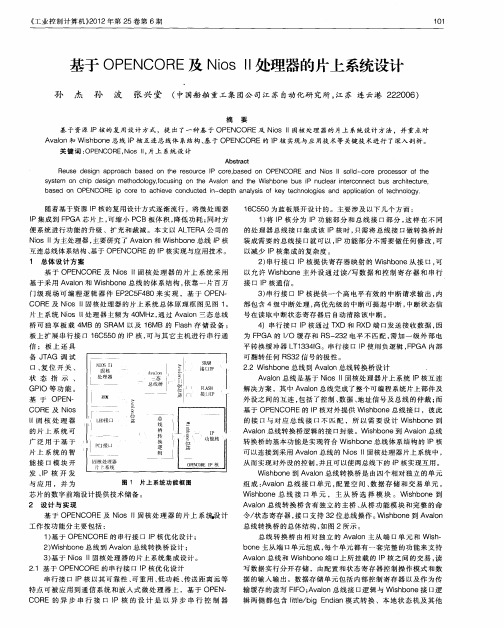

桥可 独享板 载 4 MB 的 S A 以 及 1 MB 的 Fa h存 储 设 备 ; RM 6 ls 板 上 扩 展 串行 接 口 1 C 5 6 5 O的 I P核 , 与 其 它 主 机 进 行 串行 通 可

信 ;板 上 还 具 备 J AG 调 试 T

随着 基 于 资 源 I 的 复用 设 计 方 式逐 渐 流 行 ,将 微 处 理器 P核

1C 5 6 5 0为 蓝板 展 开 设 计 的 。 主要 涉 及 以下 几 个 方 面 :

I 成 到 F GA 芯 片 上 , 缩 小 P P集 P 可 CB板 体 积 , 降低 功 耗 ; 时方 同 便 系 统 进 行 功 能 的 升 级 、扩 充 和 裁减 。本 文 以 A T R L E A公 司 的

Ni l 主处 理 器 , 要研 究 了 A ao o l s 为 主 v ln和 Wi b n s o e总线 I h P核

1 将 I 分 为 J 能 部 分 和 总 线 接 口部 分 , 样 在 不 同 ) P核 P功 这

的处 理 器 总 线 接 口集 成 该 I 时 , 需 将 总线 接 口做 转 换 桥 封 P核 只

Ab ta t s rc

Reu e esgn s d i ap o ch as d pr a b e on h r o c I t e es ure P cor b e on PENCORE e,as d O an Ni l s i d os l ol d—c e r c s r o h or p o es o f t e

4 )串行 接 口 l 通 过 T D 和 R D 端 口发 送 接 收 数 据 , P核 x X 因

基于 Nios Ⅱ的 SOPC 实验教学平台设计

基于Nios Ⅱ的 SOPC 实验教学平台设计陈晓静;吴爱平【摘要】提出了以 EP4CE30F248N FPGA 为核心的 SOPC 实验教学平台设计方案,介绍了平台的硬件组成和软件开发工具,以定时中断为实验案例介绍了 SOPC 实验的具体流程。

该平台由核心板、底板和扩展板组成,可实现的实验项目包括基本模块实验和创新型实验。

其中基本模块实验类似于单片机实验,如定时器、键盘、数码管显示模块等,目的是帮助学生理解 SOPC 系统基本设计方法;创新型实验项目是将 FPGA 并行数据处理和 Nios Ⅱ处理器灵活控制功能相结合的实验,如多通道数据采集、高精度频率计、频谱仪设计等,旨在帮助学生进一步掌握 SOPC系统设计的精髓。

该方案既能实现 SOPC 系统基本模块的实验,又能为电子设计竞赛和实际项目开发提供创新性平台,有助于培养学生的 SOPC 综合设计能力。

【期刊名称】《长江大学学报(自然版)理工卷》【年(卷),期】2016(013)022【总页数】5页(P9-13)【关键词】SOPC;Nios Ⅱ;FPGA;实验教学平台【作者】陈晓静;吴爱平【作者单位】长江大学电子信息学院,湖北荆州434023;长江大学电子信息学院,湖北荆州 434023【正文语种】中文【中图分类】TP368.1SOPC(System On a Programmable Chip)即片上可编程系统,该技术使用FPGA(Field Programmable Gate Array)的逻辑单元以及植入FPGA内部的软核处理器、存储模块和DSP模块,设计出可裁剪、可扩充、可升级的嵌入式处理系统[1]。

该系统不仅具有可编程系统的的灵活性,而且具有高速并行处理数据的能力。

近年来,SOPC技术在数据采集、目标跟踪、电能质量监测等领域得到了广泛的应用[2~4]。

SOPC系统中的处理器通常有硬核和软核2种:硬核是指嵌入在可编程芯片内部的具有固定掩模版图的处理器内核,如ARM内核;软核是指以硬件描述语言文件的形式存在,需经过编译下载,最终固化到可编程芯片内部才可使用的处理器内核,如Altera公司推出的Nios Ⅱ嵌入式软核。

基于NIOSⅡ的多目标脉冲测距系统

下一次触发信号的到来 。 在 Q ats 中启动 S P ul r uruI I O Cb i e 修改时钟为 d 2MHz根据 本次设 计 需求 添加 C U 和外 设 , 0 , P 外设 有 S AM 、 L S 控 制 器 、 C 62 RS3 DR F A H L D10 、 2 2控 制器 、 0 口、 2位 定 时器 。添 加完 成 后 分 配基 地 I / 3

测 量误 差 小等 优 点 。 关 键 词 : 目标 测 距 ; 获 ; OSI;2 定 时 器 多 捕 NI 3 住 I

中 图分 类 号 : TN2 7 4

文献标识码 : A

文 章 编 号 :0 7 2 4 2 1 )3 0 4 — 4 10 —3 6 (0 10 — 0 9 0

图 6 NI 系统配置及其地址映射 OSI I

在 本 设 计 中 采 用 的 FG P A 芯 片 为 E 2 S 0 1, 内部含有 8 5 P C Q288其 2 6个 L 18个 IO E,3 /

第 3期

王 松 , : 于 NI SI 多 目标 脉 冲a / 等 基 O I的 l , a系统

, 目标

分辨距离 D, 即相距大于 D 的不同 目 标才能被测距

收 稿 日期 :0 0 2 0 2 1 —1 —2

作者简介 : 王松 (9 7 ) 男 , 1 8 一 , 硕士研究生 , 研究方向 : 频通信与 S C技术 , - i i 85 @1 3cr ; 扩 OP E ma : 9 7 3 6 .o 葛海 波( 9 3 ) 男 , l1 n 16 一 ,

基 于 NI I 的 多 目标 脉 冲 测 距 系统 OS I

王

( _西安邮电学院 通信 与信 息工程学院, 1 陕西 西安

以太网数传系统在FPGA上的实现

以太网数传系统在FPGA上的实现贲广利;王永成;徐东东;郑佳宁;吴铮【摘要】In digital signal processing or control circuit based on FPGA, in order to export original sampling data or intermediate processing result data for analyzing and processing later, from the view of stabile transmission, easy realization and low cost, a 100 Mbps Embedded Ethernet data transmission system based on FPGA TSE IP core is designed. First, the paper introduces the hardware design thought in SOPC with the main processor NiosII CPU, mainly including the Ethernet MAC designing based on TSE IP core. Uninterrupted data transmission during all transmit time is guaranteed by Pingpang RAM mechanism and a method of controlling data start and stop transmitting is also designed. Then, using MicroC/OS-II real-time operating system of multi task mode, and based on Niche stack TCP/IP protocol, the software design of the system is realized. Also, the software program flow chart which details the software work flow of the system is given. Finally, by transferring designated data, a verification method of rate and stability during data transmission is provided. The test result shows that the system is stable and reliable in data transmission when the rate is up to 51 Mbps.%在含有FPGA的数字信号处理电路和控制电路中,为了实现将原始AD采样数据或中间处理结果数据的导出,供后续分析处理使用,从数据传输的稳定性、系统实现的简易性、价格低廉等角度出发,研究设计了基于FPGA TSE IP核的嵌入式百兆以太网数据传输系统.首先,详细分析了以NiosII CPU软核处理器为核心的以太网数传系统的SOPC各模块的硬件设计,主要包括以TES IP核为主的以太网MAC,采用乒乓缓存方式保证数据的连续不间断传输,以及通过接收客户端指令来控制数传的开始和暂停;然后,利用MicroC/OS-II嵌入式实时操作系统的多任务方式,基于Niche stack TCP/IP协议栈,完成了系统的软件设计,并给出了软件程序流程;最后,通过传输并接收特定的数据,验证了系统数据传输的速率和准确性.结果表明在传输速率达到51 Mbps时,系统稳定可靠.【期刊名称】《液晶与显示》【年(卷),期】2017(032)008【总页数】7页(P607-613)【关键词】嵌入式以太网;数据传输;FPGA【作者】贲广利;王永成;徐东东;郑佳宁;吴铮【作者单位】中国科学院长春光学精密机械与物理研究所,吉林长春 130033;中国科学院长春光学精密机械与物理研究所,吉林长春 130033;中国科学院长春光学精密机械与物理研究所,吉林长春 130033;中国科学院长春光学精密机械与物理研究所,吉林长春 130033;电子科技大学通信与信息工程学院,四川成都 611731【正文语种】中文【中图分类】TN919FPGA以其使用方便灵活、开发周期短、具备并行处理能力等优点,已被广泛应用于各种数字信号处理和控制领域。