微机原理4

微机原理第四章课后习题答案

第四章课后作业(6—27)6.试按下列要求分别编制程序段。

(1)把标志寄存器中符号位SF置“1”。

(2)寄存器AL中高、低四位互换。

(3)由寄存器AX、BX组成一个32位带符号数(AX中存放高16位),试求这个数的负数。

(4)现有三个字节存储单元A、B、C,在不使用ADD和ADC指令的情况下,实现(A)+(B) C。

(5)用一条指令把CX中的整数转变为奇数(如原来已是奇数,则CX中数据不变,如原来是偶数,则(CX)+1 形成奇数)。

答:(1) LAHFOR AH,80HSAHF(2) MOV CL,4ROL AL,CL(3) MOV CX,0NEG BXJC CHGJMP GOCHG: MOV CX,1GO: NEG AXSUB AX,CX(4) MOV CL,AMOV AL,BMOV X,ALCHECK:INC XDEC CLJNZ CHECK(5) OR CX,0001H7.试给出下列各指令的机器目标代码。

(1)MOV BL,12H [SI](2)MOV 12H [SI],BL(3)SAL DX,1(4)AND 0ABH [BP] [DI],1234H答:(1)100010 1 0 01 011 100 00010010=8A5C12H(2)100010 0 0 01 011 100 00010010=885C12H(3)110100 0 1 11 100 010=0D1E2H(4)100000 0 1 10 100 011 10101011 00000000 00110100 00010010=81A3AB003412H8.执行下列指令:STR1 DW ‘AB’STR2 DB 16DUP(?)CNT EQU $-STR1MOV CX,CNTMOV AX,STR1HLT执行完成之后,寄存器CL的值是多少?寄存器AX的值是多少?答:因为CNT=16+2=18,所以CX=18=0012H,所以CL=12H=0001,0010;AX中装入的是‘AB’的ASCII码值,其中‘A’在高位AH中,‘B’在低位AL 中,所以AX=4142H=0100,0001,0100,0010。

微型计算机原理-第4章(4)微机原理与接口技术(第三版)(王忠民)

第四章 80x86 指令系统—累加器专用指令

⑴ 输入指令 ①直接寻址的输入指令 指令格式及操作:

IN acc, port ;(acc) ←(port)

②间接寻址的输入指令

指令格式及操作:

IN acc, DX

;(acc) ←((DX))

第四章 80x86 指令系统—累加器专用指令

⑵ 输出指令

①直接寻址的输出指令 指令格式及操作:

第四章 80x86 指令系统—通用数据传送指令

说明: *堆栈按后进先出原则组织。 *堆栈操作以字为单位进行。 *目的操作数dst不可以是CS。 *指令中的操作数不能是立即数。

第四章 80x86 指令系统—通用数据传送指令

例:已知(AX)=1234H,(BX)=5678H,分析下面程序段的执 行过程。

REG <=> REG/MEM • 段寄存器的内容不能参加交换

例: XCHG BX,[BP+SI]

第四章 80x86 指令系统—累加器专用指令

(二) 累加器专用指令 这类指令中的一个操作数必须是累加器。累加器操作数可以 是8位的,也可以是16位的。

第四章 80x86 指令系统—累加器专用指令 1.输入/输出指令

DI 1234H DS 4000H

DM

34H 2130H 12H 00H 2132H 40H

第四章 80x86 指令系统—地址传送指令

3. 地址指针装入ES指令 指令格式:

LES reg16, mem32 此指令的功能是将源操作数所对应的双字长的内存单元中的高 字内容(一般为16位段基址)送入ES,低字内容(一般为偏移地址) 送入指令所指定的寄存器中。例如:

LES DI, [2130H]

DI 1234H ES 4000H

微机原理 第4章作业答案

第3章指令系统3.9 设段寄存器DS=1000H,SS=2000H,ES=3000H,通用寄存器BX=4000H,BP=5000H,SI=6000H,DI=7000H。

在下列各指令中指出存储器操作数的寻址方式,求出有效地址EA、物理地址PA,并分别用物理地址和逻辑地址说明指令执行结果。

(1)MOV CX, [2300H]直接寻址EA=2300HPA=DS*16+EA=1000H*16+2300H=12300H 执行结果:(12300H)→CL,(12301H)→CH (2)MOV BYTE PTR [BX], 8FH寄存器间接寻址EA=BX=4000HPA=DS*16+EA=1000H*16+4000H=14000H 执行结果:8FH→(14000H)(3)MOV DH, [BP+3000H]基址寻址EA=BP+3000H=8000HPA=SS*16+EA=2000H*16+8000H=28000H 执行结果:(28000H)→DH(4)MOV ES: [SI+1210H], AX变址寻址EA=SI+1210H=7210HPA=ES*16+EA=3000H*16+7210H=37210H 执行结果:AL→(37210H),AH→(37211H) (5)MOV [BX+DI+50H], AL基址变址位移寻址EA=BX+DI+50H=0B050HPA=DS*16+EA=1000H*16+0B050H=1B050 H执行结果:AL→(1B050H)(6)INC WORD PTR [BX+SI]基址变址寻址EA=BX+SI=0A000HPA=DS*16+EA=1000H*16+0A000H=1A000 H执行结果:(1A000H)中存放的字的值加13.11 指出下列指令中源操作数的寻址方式。

(1)MOV BL, 0F9H 立即寻址(2)ADD [BX], SI 寄存器寻址(3)SUB CL, [4000H] 直接寻址(4)CMP DX, [SI] 寄存器间接寻址(5)AND SL, [BX+1] 基址寻址(6)OR BP, [DI+2100H] 变址寻址(7)XOR AX, [BP+SI] 基址变址寻址(8)MOV CX, 300 立即寻址3.12 下列指令都是非法的,指出各指令错在哪里?(1)MOV SI, AH两个操作数字长不一致(2)MOV 70H, BL立即数不能做目的操作数(3)MOV CX, F123H十六进制的数以字母打头必须在前面补0 (4)MOV [BX], 6AH两个操作数的字长不确定(5)MOV ES, 5000H立即数不能直接送段寄存器(6)MOV [DI], [3000H]两个操作数不能同为内存操作数(7)MOV DS, SS两个操作数不能同为段寄存器(8)MOV CS, AX不能对CS赋值(9)MOV AL, [CX]寄存器间接寻址中不能使用CX(10)MOV [BX+BP], DX存储器寻址方式中表示有效地址不能同为两个基址寄存器(11)MOV BH, [SI+DI+2]存储器寻址方式中表示有效地址不能同为两个变址寄存器(12)PUSH AL入栈出栈操作必须以字为单位(13)LEA AX, BXLEA指令中源操作数必须为存储器寻址方式(14)LDS BL, [5100H]LDS指令中目的操作数必须为16位的通用寄存器(15)IN AH, DXIN指令中目的操作数必须为AL或AX (16)OUT 288H, AL输入输出指令中端口地址为16位,必须先送给DX(17)ADD [2400H], 1234H两个操作数的字长不确定(18)XOR [2500H], [BX+10H]两个操作数不能同为内存操作数(19)INC [SI]操作数的字长不确定(20)MUL 10MUL指令的操作数不能为立即数(21)IDIV [BP+DI+1300H]操作数的字长不确定(22)SAL AL, 2移位次数大于1必须先送给CL3.14 设SP=2000H,AX=3000H,BX=5000H,执行以下3条指令后,问SP=?AX=?BX=? PUSH AX ;SP减2,栈顶元素为3000HPUSH BX ;SP减2,栈顶元素为5000HPOP AX ;SP加2,将栈顶元素5000H弹出至AX结果:SP=1FFEH,AX=5000H,BX=5000H3.16 下列程序执行完后,AX=?BX=?CX=? MOV AX, 1122HMOV BX, 3344HPUSH AX ;栈顶元素为1122H POP CX ;将栈顶元素1122H 弹出至CXXCHG BX, CX ;BX=1122H,CX=3344HLEA CX, [BX] ;CX=BX=1122H结果:AX=1122H,BX=1122H,CX=1122H3.17 CPU分别执行下列各程序段后,写出各个执行结果的状态标志位OF、SF、ZF、AF、PF、CF的值。

微机原理4_2

Y

P1

标号1:

N Y P2

条件2成立 ?

标号2:

…

N

条件n成立 ?

Y

Pn

标号n:

N

Pn+1

标号n+Βιβλιοθήκη :TEST/CMP指令(测试条件1) Jx 标号1 ;不满足转标号1 处理体P1… JMP 标号n+1 标号1:TEST/CMP指令(测试条件2) Jx 标号2 ;不满足转标号2 处理体P2… JMP 标号n+1 标号2:TEST/CMP指令(测试条件3) Jx 标号3 ;不满足转标号3 处理体P3… JMP 标号n+1 标号3:TEST/CMP指令(测试条件4) … … 标号n+1:(公共出口)

Y

Z <= 1

结束

EXT:

MOV Z, AL RET

30

程 序 ;-- 数据段定义 ---------------------------------SEGMENT X DB 242 Y DB 67 Z DB ? DAT ENDS ;-- 代码段定义 ---------------------------------COD SEGMENT ASSUME DS: DAT, CS: COD MAIN PROC FAR PUSH DS ; 保存返回地址 SUB AX, AX PUSH AX MOV AX, DAT MOV DS, AX ; 初始化DS

3.源程序的基本结构:顺序、分支、循环、过程

14

如何绘制程序框图(流程图)?

(1)用方框表示工作框,框中用简明语言 标明要完成的功能

(2) 用菱形框表示判断框

?

Y

15

N

框中标明比较、判断和条件

微机原理实验4-逐次比较式ADC0809

实验三 逐次比较式A/D 转换器0809的原理及编程一、实验目的1. 熟悉逐次逼近式A/D 转换器芯片的工作原理。

2. 了解A/D 转换芯片0809的接口设计方法。

3. 掌握A/D 转换器0809简单的应用编程。

二、实验任务1. 分析本实验模板的电路原理,它与EPP 接口数据传送的方法,所使用的端口地址。

2. 编写出逐次逼近式A/D 转换器芯片0809的转换与显示的控制程序。

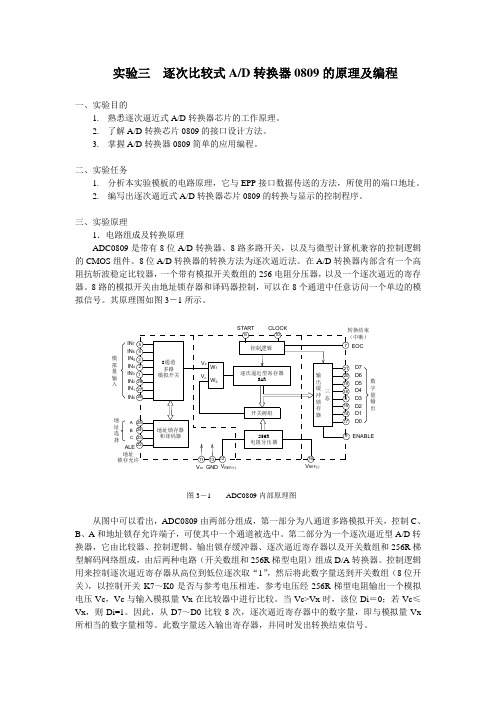

三、实验原理1.电路组成及转换原理ADC0809是带有8位A/D 转换器、8路多路开关,以及与微型计算机兼容的控制逻辑的CMOS 组件。

8位A/D 转换器的转换方法为逐次逼近法。

在A/D 转换器内部含有一个高阻抗斩波稳定比较器,一个带有模拟开关数组的256电阻分压器,以及一个逐次逼近的寄存器。

8路的模拟开关由地址锁存器和译码器控制,可以在8个通道中任意访问一个单边的模拟信号。

其原理图如图3-1所示。

8通道多路模拟开关5432128272625242322地址锁存器和译码器W 1W 2逐次逼近型寄存器SAR控制逻辑开关树组256R 电阻分压器610V x V c7输出缓冲锁存器三态212019188151417916111312模拟量输入A B CA L E地址选择地址锁存允许V cc G N D V R E F (+)V R E F (-)E N A B L E数字量输出转换结束(中断)E O CS TA R TC L O C KD 7D 6D 5D 4D 3D 2D 1D 0IN 7IN 6IN 5IN 4IN 3IN 2IN 1IN 0图3-1 ADC0809内部原理图从图中可以看出,ADC0809由两部分组成,第一部分为八通道多路模拟开关,控制C 、B 、A 和地址锁存允许端子,可使其中一个通道被选中。

第二部分为一个逐次逼近型A/D 转换器,它由比较器、控制逻辑、输出锁存缓冲器、逐次逼近寄存器以及开关数组和256R 梯型解码网络组成,由后两种电路(开关数组和256R 梯型电阻)组成D/A 转换器。

微机原理第4章练习题及答案

微机原理第4章练习题及答案第4章 80x86指令系统一、自测练习题㈠选择题 1.MOV AX,[BX+SI]的源操作数的物理地址是( )。

A.(DS)×16+(BX)+(SI) B. (ES)×16+(BX)+(SI) C.(SS)×10H+(BX)+(SI) D.(CS)×10H+(BX)+(SI)2.MOV AX,[BP+Sl]的源操作数的物理地址是( )。

A.(DS)×10H+(BP)+(SI) A. (ES)×16+(BP)+(SI) C.(SS)×16+(BP)+(SI) D.(CS)×10H+(BP)+(SI) 3.MOV AX,ES:[BX+SI]的源操作数的物理地址是( )。

A.(DS)×16+(BX)+SI) B.(ES)×10H+(BX)+(SI) C.(SS)×10H+(BX)+SI) D.(CS)×16+(BX)+(SI)4.JMP WORD PTR[DI]是( )。

A.段内间接转移B.段间间接转移C.段内直接转移D.段间直接转移5.JMP FAR PTR BlOCK(BLOCK是符号地址)是( )。

A.段内间接转移B.段间间接转移C..段内直接转移D.段间直接转移6.INC指令不影响( )标志。

A.OF B.CF C.SF D.ZF 7.条件转移指令JNE的测试条件是( )。

A.ZF=1 B.CF=0 C.ZF=0 D.CF=1 8.下列指令中,有语法错误的是( )。

A.MOV [SI],[DI] B.IN AL,DX C.JMP WORD PTR[BX+8] D.PUSH WORD PTR 20[BX+S1] 9.假定(SS)=2000H,(SP)=0100H,(AX)=2107H,执行指令PUSH AX后,存放数据21H的物理地址是。

A.20102H B.20101H C.200FEH D.200FFH 10.对于下列程序段:AGAIN:MOV AL,[SI] MOV ES:[DI],AL INC SI INC DI LOOP AGAIN 也可用指令完成同样的功能。

微机原理 第4章 总线 习题及参考

第四章总线1. 什么是总线?答:总线是许多信号线的集合,是微机系统中连接各部件的信息通道,通过它实现数据的相互交换。

具体地说,总线是CPU内部各组成部件之间、微机芯片之间、系统各模块之间,或各设备之间传递数据信息、地址信息、控制和状态信息的通道。

2. 总线结构的优点是什么?答:概括起来有以下四点:1)支持模块结构的设计方法,可以简化系统设计;2)标准总线得到多厂商的广泛支持,便于生产与之兼容的硬件板卡和软件,具有开放性和通用性;3)便于模块的专业化生产和产品的升级换代,便于故障诊断和维修,灵活性好。

4)降低了设计及系统成本。

3. 按照布局范围,总线分为哪几种类型?答:四种类型:①内部总线——是处于CPU内部、用来连接片内运算器和寄存器等各个功能部件的总线。

内部总线的对外引线称为CPU总线。

②局部总线——是主机板上的信息通道,连接主机板上各个主要部件,而且通过扩展槽连接多种适配器(局部总线是组成微机系统的主框架)。

③系统总线——是多处理器系统中连接各CPU插件板的信息通道,用来支持多个CPU的并行处理。

④外部总线——是微机和外部设备之间或者几个微机系统之间的信息通道,又称通信总线。

4. 微机系统中常用的系统总线有哪几种?答:ISA总线、EISA总线、PCI总线、AGP总线等。

5. 按照功能,总线可分为哪几类?答:分为数据总线、地址总线和控制总线等三类。

数据总线、地址总线和控制总线分别用来传输数据、地址、命令和状态信号。

6. 为什么引入PCI总线有利于提高微机系统的整体工作性能和效率?答:随着各种应用软件的发展,需要在CPU与外设之间进行大量的高速数据传输。

以往的ISA总线及以后发展的EISA总线都未能解决总线的高效率传输问题。

PCI总线提供了CPU 与外设之间的高速通道,有利于提高微机系统的整体工作性能和效率。

7. 总线的性能主要从哪几方面来衡量?答:三方面:①总线宽度——指一次可以同时传输的数据位数。

微机原理第4章2-存储器与的连接

解决:

–CPU插入等待周期——降低了运行速度; –采用高速RAM——成本太高; –在CPU和RAM之间插入高速缓存——成本上升不多、但速度 可大幅度提高。 西南交通大学

10

微机原理与应用

字扩展

地址空间的扩展。芯片每个单元中的字长满足,但单元 数不满足。 扩展原则: 每个芯片的地址线、数据线、控制线并联,仅片选 端分别引出,以实现每个芯片占据不同的地址范围。

字位扩展

• • • • 根据内存容量及芯片容量确定所需存储芯片数; 进行位扩展以满足字长要求; 进行字扩展以满足容量要求。 若已有存储芯片的容量为L×K,要构成容量为M ×N 的存储器,需要的芯片数为: (M / L) ×(N / K)

A B C E1 E2 E3 Y7 GND

1 2 3 4 5 6 7 8

16 15 14 13 12 11 10 9

Vcc Y0 Y1 Y2 Y3 Y4 Y5 Y6

74LS138管脚图

西南交通大学

6

微机原理与应用

(3)部分译码:系统的部分高位地址线参与对芯片(组)的译码寻

址。

A19、A18 、A17 不参加译码

× × ×

00000H~01FFFH 02000H~03FFFH 04000H~04FFFH 05000H~05FFFH

17

1 × 西南交通大学

微机原理与应用

4.4 存储器的分层结构

冯.诺依曼计算机体系结构: “存储程序”的概念 访问存储器的活动占了CPU时间的70%左右 CPU工作速度与内存工作速度不匹配

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

标准应用

除以零出错中断 单步(用于Debug)中断 非屏蔽中断(CPU的NMI引脚) 断点(用于Debug)中断 溢出中断 屏幕打印中断 保留

07H

保留

《微机原理与接口技术》教学课件

9

二、硬件中断

硬件中断

包括:非屏蔽中断、可屏蔽中断。 CPU在每执行一条指令的最后一个机器周期,都要检测 NMI和INTR引脚,如果有中断请求,CPU都将进行响应 和处理。

响应中断的条件

①. 可屏蔽中断

㈠. INTR=1,NMI=0且没有DMA请求。 ㈡. CPU当前指令执行完毕。 ㈢. IF=1。

《微机原理与接口技术》教学课件

P.159

10

②. 非屏蔽中断

㈠. NMI=1,系统没有DMA请求。 ㈡. CPU当前指令执行完毕。

中断优先权

DMA 内部中断 NMI INTR 低

屏蔽方式

优先级管理方式 结束方式

自动EOI方式 非自动EOI方式

常规EOI

总线连接方式

缓冲方式 非缓冲方式

特殊EOI

《微机原理与接口技术》教学课件

26

边沿触发

8259A收到第一个负脉冲之前,同一个输入端上不应当出现

第2次上跳沿。

常规屏蔽方式

中断屏蔽寄存器(IMR)对应位置置1,即可屏蔽相应级别 得中断请求。

0

P.167

8259A最初写入的必定是ICW1,由A0=0和ICW1内的D4=1确定。

D7 ~ D5

A7A6A5

D4

1

D3

LTIM

D2

ADI

D1

SNGL

D0

IC4

①. A7A6A5 和ADI :8086/8088 CPU不用。 ②. LTIM:设定中断触发方式。 =0,边沿触发 =1,电平触发 =0,级连方式 =1,单片方式 =0,不写ICW4 =1,要写ICW4

《微机原理与接口技术》教学课件

29

① 初始化命令字(ICW)

ICW1和ICW2是必须写入的,而ICW3和ICW4则由工作方式

决定(ICW1的有关位)。 ICW写入流程图:

ICW1 ICW2

级连?

需ICW4?

N

Y ICW4 N

准备接收中断

Y

ICW3

《微机原理与接口技术》教学课件

30

ICW1(初始化字) A0

中断屏蔽IMR

22

二、引脚定义

D7~D0:双向三态数据总线 IR7~IR0:中断申请信号 WR:写命令信号线 RD:读命令信号线

P.163 CS RD WR D7 · · · · 8259A · · D0 Vcc A0 INTA IR7 · · · · · · IR0 INT SP/ EN CAS2

P.161

4N+0 4N+1 4N+2 4N+3

N型服务程序入口的偏移地址

N型服务程序所在代码段的段基址

因此,存放中断向量的空间就称为中断向量表。

《微机原理与接口技术》教学课件

15

三、中断向量的引导作用 MOV INT Next: ⑤ MOV 堆栈区

Next的有效地址

P.191

② 中断向量表

IP CS

㈠. 中断判别 ㈡. 中断周期(IF=0) ㈢. 装入中断服程序[ CS:IP ]

③. 中断服务(用户自行编制)

由保护现场、具体处理、恢复现场等7个步骤组成。

《微机原理与接口技术》教学课件

7

8.2、微机系统的中断分类

P.158

按照中断源可分:外(硬件)中断、内(软件)中断。 可屏蔽中断INTR

外部(硬件)中断

高

《微机原理与接口技术》教学课件

11

P.189

8.3、80x86的中断指令

1) 开中断指令(STI) 2) 关中断指令(CLI)

3) 软件中断指令(INT N)

4) 中断返回指令(IRET)

《微机原理与接口技术》教学课件

12

一、软件中断指令(INT N)

中断类型N N=0~255 执行功能:调用N型中断服务程序。

①

AH,1 21H DL,AL

YY XX 服务程序 · · · · · · · IRET

③ XX:YY ④

IP CS FLAG

Next的段基址

FLAG寄存器

《微机原理与接口技术》教学课件

16

四、中断类型号

①. 中断号N是CPU系统 分配给每个中断源的代号。

②. 系统外部中断与内部中断、硬中断与软中断一律

5) 8259A初始化

6) 8259A的级连

《微机原理与接口技术》教学课件

21

一、内部结构

INTA

D7 ~ D0

BUFFER RD WR A0 CS CAS0 CAS1 CAS2 SP/ EN 读 /写 逻辑 控制逻辑

P.164 INT

内 部 总 线

ISR 优先 电路 IRR

级连/缓冲 比较器

《微机原理与接口技术》教学课件

《微机原理与接口技术》教学课件

33

ICW3(级连控制字)

8259A在级连工作方式时,要写入ICW3。 主片和从片8259A都必须写入ICW3,但两者含义不同。

P.168

A0 1

D7

D6

D5

D4

D3

D2

D1

D0

S7

S6

S5

S4

S3

S2/ID2

S1/ID1

S0/ID0

①. 对主8259A:ICW3每一位S0~S7表明IR0~IR7上哪些 接有从片。 Si =0,IRi没有连接从片 =1,IRi接有从片

P.161

②. 服务程序入口的偏移地址。

二、中断向量表

微机系统最多允许256种中断,每一种中断分配有一 个中断号(也称中断类型号)。每一种中断对应一

个中断服务程序,因此每一种中断有一个中断向量。

《微机原理与接口技术》教学课件

14

每一种中断向量的为4个字节,256种中断共占1KB空 间。这些中断向量存放在RAM的00000H~003FFH, 这些单元就构成了中断向量表。

安全嵌套方式

固定优先级方式。 高打断低,同级按序。

IR0 IR7

《微机原理与接口技术》教学课件

27

常规EOI方式

在执行IRET之前,向8259A送一个“常规中断结束” 命令。 在安全嵌套方式下,应当使用常规EOI命令结束中断。

缓冲方式

8259A通过总线驱动器与系统数据线相连。

《微机原理与接口技术》教学课件

是外部的。

《微机原理与接口技术》教学课件

4

三、CPU执行流程

P.157

非预料事件1

中断服务程序1

非预料事件 2 中断服务程序 2

《微机原理与接口技术》教学课件

5

四、中断系统基本功能

为了实现中断而采取的硬件和软件措施。 基本功能:

P.154

①. 对于硬件设备的中断请求,应该具有屏蔽和开放的性能。

②. 有多个中断请求时,能够响应优先级别较高的中断,

⑥. 采用非自动中断结束方式;

⑦. 状态读出电路预置为IRR。

《微机原理与接口技术》教学课件

32

ICW2(中断向量字) A0 D7

A15/T7

P.167

D4

A12/T4

D6

A14/T6

D5

A13/T5D3A1/T3D2D0

1

A10 A9 A8

8259A与8086/8088CPU连用时,A10~A8不用,用T7~T3 作为中断类型号的高5位,而低3位由8259A自动按IR输 入端确定。 对应关系: IR0:000 IR1:001 · · · · · · · · IR7:111

非屏蔽中断NMI 中断 内部(软件)中断 执行指令或特殊操作 产生

《微机原理与接口技术》教学课件

8

一、软件中断——中断指令和特殊操作

P.194~195

软件中断的中断源在CPU的内部,主要是由INT 指令、运算过程中错误、设置的断点、单步执行 而引起的中断。软件中断又称内部中断。

中断号

00H 01H 02H 03H 04H 05H 06H

31

③. SNGL: 设定单片/级连方式。 ④. IC4: 设定是否写入ICW4。

《微机原理与接口技术》教学课件

ICW1写入后,8259A内部状态有一初始化过程,它的

动作是: ①. 顺序逻辑复位,准备按ICW2、 ICW3和ICW4接 收其余ICW; ②. 清除ISR和IMR; ③. 设定固定优先级; ④. 从片方式的地址置为7(对应IR7); ⑤. 设定普通屏蔽方式;

《微机原理与接口技术》 第八章 中断系统

《微机原理与接口技术》教学课件

1

第八章

中断系统

1. 中断系统基本概念

2. 中断分类 3. 中断指令 4. 中断向量(矢量) 5. 8259A中断控制器应用

《微机原理与接口技术》教学课件

2

8.1、中断的基本概念

1) 什么是中断?

2) 中断源

P.153

3) 中断系统的基本功能

《微机原理与接口技术》教学课件

ICW4(中断方式字) A0 1 D7 ~ D5 000 D4 SFMN D3 BUF D2 M/S D1 AEOI

P.168

D0 μPM

①. μPM:选用CPU类型

28

五、8259A初始化

定和启动规定的操作。

P.167

8259A可以接受2种命令字对它进行工作方式的设

ICW(Initialization Command Words)