功率LDMOS管以及电阻电容

LDMOS介绍

小了漏、源两极之间的寄生电容,有利于提高频率特性。同时,漂移区在沟道和漏之间起

缓冲作用,削弱了LDMOS的短沟道效应。由于VDS的绝大部分降落在漂移区上,因此在沟

道夹断后,基本上没有沟道的长度调制效应。当VDS增大的时候,输出电阻不会降低,沟

道区也不易穿通,从而LDMOS的击穿电压不受沟道长度和掺杂水平的限制,可以进行独

•

九十年代中后期开始大批量生产LDMOS,作为微波低端大功率(20W以上)器

件的主流技术, 2. 4GHz以下输出峰值可达到200W以上,年产量超过4亿美元。与

传统的双极型晶体管相比, LDMOS器件在2. 4GHz以下频段时,增益、线性度、开

关性能、散热性能、价格等方面都有着明显的优势。今后LDMOS将向更高频率、

LDMOS

(Laterally Diffused Metal Oxide Semiconductor)

横向扩散金属氧化物半导体

简介

•

80年代以来,迅猛发展的超大规模集成电路技术给高压大电流半导体注入了

新的活力,一批新型的声控功放器件诞生了,其中最有代表性的产品就是

VDMOS声效应功率晶体管。这种电流垂直流动的双扩散MOS器件是电压控制型

立的设计。

•

LDMOS中的漂移区是该类器件设计的关键,漂移区的杂质浓度比较低,因此,当

LDMOS 接高压时,漂移区由于是高阻,能够承受更高的电压。图1所示LDMOS的多晶扩

展到漂移区的场氧上面,充当场极板,会弱化漂移区的表面电场,有利于提高击穿电压。

ቤተ መጻሕፍቲ ባይዱ场极板的作用大小与场极板的长度密切相关。要使场极板能充分发挥作用,一要设计好

•

到了90年代,由于器件结构和工艺技术的改进,使得LDMOS性能有了飞跃性的发展,

demos与ldmos工作原理

demos与ldmos工作原理在现代电子设备中,demos(Double-diffused Metal Oxide Semiconductor)和ldmos(Lateral Double-diffused MetalOxide Semiconductor)是常用的半导体器件。

它们在许多领域中都发挥着重要作用,如通信、功率放大器和射频应用。

本文将介绍这两种器件的工作原理和特点。

demos和ldmos都是金属氧化物半导体场效应晶体管(MOSFET)的变种。

它们的工作原理基于PN结和场效应晶体管的结合。

在demos中,PN结的扩散区域被双重扩散,从而形成了一个耐压区。

而在ldmos中,扩散区域是沿着晶体管表面扩散的,这种结构使得器件在导通状态下具有更低的电阻。

在demos中,PN结的双重扩散使得器件具有更高的耐压能力。

当器件处于关断状态时,PN结的扩散区域可以承受较高的电压而不会发生击穿。

这使得demos在高压应用中具有优势,如电源管理和功率放大器。

而ldmos则通过沟道扩散技术,使得器件在导通状态下具有更低的电阻,从而在功率放大器和射频应用中表现出色。

除了耐压能力和导通电阻之外,demos和ldmos还有许多其他特点。

例如,它们通常具有较高的开关速度和较低的漏电流,这使得它们在高频和低功耗应用中具有优势。

此外,它们的制造工艺相对成熟,成本较低,因此在大规模生产中具有竞争优势。

总的来说,demos和ldmos是两种在不同应用领域中发挥作用的重要器件。

它们的工作原理基于PN结和场效应晶体管的结合,具有耐压能力强、导通电阻低、开关速度快和制造成本低等特点。

随着电子技术的不断发展,相信它们将在更多领域中发挥重要作用。

功率半导体器件 LDMOS VDMOS

关于功率MOSFET(VDMOS & LDMOS)的报告---时间日期:2009.11.12---报告完成人:祝靖1.报告概况与思路报告目的:让研一新同学从广度认识功率器件、了解功率器件的工作原理,起到一个启蒙的作用,重点在“面”,更深层次的知识需要自己完善充实。

报告内容:1)从耐压结构入手,说明耐压原理;2)从普通MOS结构到功率MOS结构的发展;(功率MOS其实就是普通MOS结构和耐压结构的结合);3)纵向功率MOS(VDMOS)的工作原理;4)横向功率MOS(LDMOS)的工作原理;5)功率MOSFET中的其它关键内容;(LDMOS和VDMOS共有的,如输出特性曲线)报告方式:口头兼顾板书,点到即止,如遇到问题、疑惑之处或感兴趣的地方,可以随时打断提问。

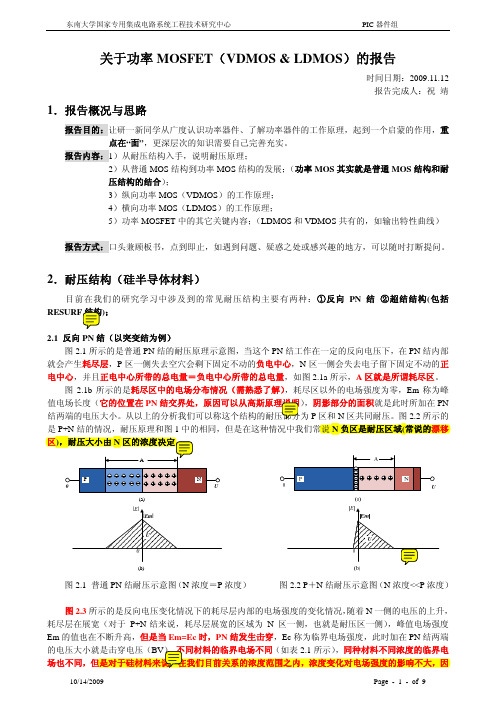

2.耐压结构(硅半导体材料)目前在我们的研究学习中涉及到的常见耐压结构主要有两种:①反向PN结②超结结构(包括);2.1 反向PN结(以突变结为例)图2.1所示的是普通PN结的耐压原理示意图,当这个PN结工作在一定的反向电压下,在PN结内部就会产生耗尽层,P区一侧失去空穴会剩下固定不动的负电中心,N区一侧会失去电子留下固定不动的正电中心,并且正电中心所带的总电量=负电中心所带的总电量,如图2.1a所示,A区就是所谓耗尽区。

图2.1b所示的是耗尽区中的电场分布情况(需熟悉了解),耗尽区以外的电场强度为零,Em称为峰值电场长度(它的位置在PN,阴影部分的面积就是此时所加在PNP区和N区共同耐压。

图2.2所示的是P+N结的情况,耐压原理和图1中的相同,但是在这种情况中我们常说N负区是耐压区域(常说的漂移区)(a)(b)图2.1 普通PN结耐压示意图(N浓度=P浓度)图2.2 P+N结耐压示意图(N浓度<<P浓度)图2.3所示的是反向电压变化情况下的耗尽层内部的电场强度的变化情况,随着N一侧的电压的上升,耗尽层在展宽(对于P+N-结来说,耗尽层展宽的区域为N区一侧,也就是耐压区一侧),峰值电场强度Em的值也在不断升高,但是当Em=Ec时,PN结发生击穿,Ec称为临界电场强度,此时加在PN结两端的电压大小就是击穿电压(BV(如表2.1所示),同种材料不同浓度的临界电场也不同,但是对于硅材料来说,在我们目前关系的浓度范围之内,浓度变化对电场强度的影响不大,因图 2.3 电场强度和电压的关系示意图 Table2.1 不同材料的临界电场2.2 超结结构(SuperJunction )(了解)除了上述所说的P+N-结结构之外,还有一种我们会接触到的耐压结构——超结结构。

LDMOS简介

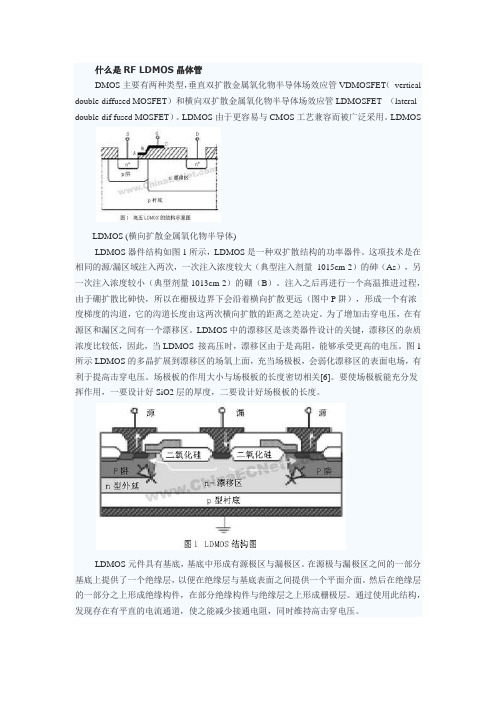

什么是RF LDMOS晶体管DMOS主要有两种类型,垂直双扩散金属氧化物半导体场效应管VDMOSFET(vertical double-diffused MOSFET)和横向双扩散金属氧化物半导体场效应管LDMOSFET (lateral double-dif fused MOSFET)。

LDMOS由于更容易与CMOS工艺兼容而被广泛采用。

LDMOSLDMOS (横向扩散金属氧化物半导体)LDMOS器件结构如图1所示,LDMOS是一种双扩散结构的功率器件。

这项技术是在相同的源/漏区域注入两次,一次注入浓度较大(典型注入剂量1015cm-2)的砷(As),另一次注入浓度较小(典型剂量1013cm-2)的硼(B)。

注入之后再进行一个高温推进过程,由于硼扩散比砷快,所以在栅极边界下会沿着横向扩散更远(图中P阱),形成一个有浓度梯度的沟道,它的沟道长度由这两次横向扩散的距离之差决定。

为了增加击穿电压,在有源区和漏区之间有一个漂移区。

LDMOS中的漂移区是该类器件设计的关键,漂移区的杂质浓度比较低,因此,当LDMOS 接高压时,漂移区由于是高阻,能够承受更高的电压。

图1所示LDMOS的多晶扩展到漂移区的场氧上面,充当场极板,会弱化漂移区的表面电场,有利于提高击穿电压。

场极板的作用大小与场极板的长度密切相关[6]。

要使场极板能充分发挥作用,一要设计好SiO2层的厚度,二要设计好场极板的长度。

LDMOS元件具有基底,基底中形成有源极区与漏极区。

在源极与漏极区之间的一部分基底上提供了一个绝缘层,以便在绝缘层与基底表面之间提供一个平面介面。

然后在绝缘层的一部分之上形成绝缘构件,在部分绝缘构件与绝缘层之上形成栅极层。

通过使用此结构,发现存在有平直的电流通道,使之能减少接通电阻,同时维持高击穿电压。

LDMOS与普通MOS管主要有两点区别:1,采用LDD结构(或称之为漂移区);2,沟道由两次扩散的横向结深控制。

LDMOS 的优势• 卓越的效率,可降低功率消耗与冷却成本• 卓越的线性度,可将信号预校正需求降到最低• 优化超低热阻抗,可缩减放大器尺寸与冷却需求并改善可靠度• 卓越的尖峰功率能力,可带来最少数据错误率的高3G 数据率• 高功率密度,使用较少的晶体管封装• 超低感抗、回授电容与串流闸阻抗,目前可让LDMOS 晶体管在双载子器件上提供7 bB 的增益改善• 直接源极接地,提升功率增益并免除BeO 或AIN 隔离物质的需求• 在GHz 频率下拥有高功率增益,带来更少设计步骤、更简易更具成本效益的设计(采用低成本、低功率驱动晶体管)• 绝佳的稳定性,由于负漏极电流温度常数,所以不受热散失的影响• 比双载子更能忍受较高的负载未匹配现象(VSWR),提高现场实际应用的可靠度• 卓越的射频稳定度,在栅极与漏极间内置隔离层,可以降低回授电容• 在平均无故障时间(MTTF) 上有相当好的可靠度LDMOS主要的缺点1.功率密度低;2.容易受到静电的破坏。

ldmos工作原理

ldmos工作原理LDMOS工作原理。

LDMOS(Laterally Diffused Metal Oxide Semiconductor)是一种常见的功率MOSFET(金属氧化物半导体场效应晶体管),在射频和微波功率放大器中得到广泛应用。

LDMOS器件具有低电阻、高电压和高频特性,因此在无线通信、广播、雷达和其他射频应用中具有重要作用。

本文将介绍LDMOS的工作原理,以便更好地理解其在功率放大器中的应用。

LDMOS的结构。

LDMOS器件通常由N型衬底上的P型沟道和N型扩散层组成。

在P型沟道区域,有一层金属氧化物绝缘层(MOS结构),用于控制沟道中的电子流。

P型沟道和N型扩散层之间的结构使得LDMOS器件具有较高的耐压能力,适合用于高电压应用。

LDMOS的工作原理。

当在LDMOS器件的门极上施加正向电压时,形成的电场使P型沟道中的电子被吸引到N型扩散层,从而形成导通通道。

当信号电压施加在沟道上时,电子将在沟道中形成连续的电流,从而实现信号的放大。

在LDMOS器件中,电子的主要流动路径是沿着P型沟道和N型扩散层的界面。

由于P型沟道的电阻较低,电子在沟道中的移动速度较快,因此LDMOS器件能够实现较高的电流传输能力。

同时,N型扩散层的结构使得LDMOS器件能够承受较高的电压,适合用于功率放大器等高压应用。

LDMOS的优势。

与其他功率MOSFET相比,LDMOS器件具有较低的电阻和较高的耐压能力,适合用于高频、高功率的射频应用。

同时,LDMOS器件的制造工艺成熟,成本相对较低,因此在市场上得到了广泛的应用。

总结。

LDMOS器件是一种常见的功率MOSFET,具有较低的电阻、较高的耐压能力和较高的频率特性。

其工作原理是通过在P型沟道和N型扩散层之间形成导通通道,实现信号的放大。

在射频和微波功率放大器中,LDMOS器件具有重要作用,广泛应用于无线通信、广播、雷达等领域。

通过本文的介绍,相信读者对LDMOS器件的工作原理有了更深入的理解,能够更好地应用于实际工程中。

LDMOS介绍教学提纲

1992年研制出了高效率的靠电池供电移动通信用的低压MO栅LDMOS,其沟道长度为

0.8µm,在6v工作时 1.5GHz下输出2w,增益5dB,漏极效率达65%,功率附加效率为

55%。1994年又研制出了在1.SGHz下连续波输出35W,增益13dB,漏极效率50%的微波

功率LDMOS。到1996年,Motorola的Alan Wood等人研制出了2GHz下连续波输出60w的

LDMOS由于更容易与CMOS工艺兼容而被广泛采用。1971年Y.Tarui等人提出了横向

双扩散MOS的结构。1976年M.J.Declerq和J.D.Plummer采用这种方案,做出了第一个

LDMOS。

LDMOS器件结构如图1所示,LDMOS是一种双扩散结构的功率器件。这项技术是在

相同的源/漏区域相继两次进行硼磷扩散,一次注入浓度较大(典型注入剂量 1015cm-2)

高频率、更大功率方向发展。

LDMOS。80年代末,研究者们利用RESURF原理,对LDMOS进行优化设计,出现了

LDMOS的不同结构。其努力的方向是降低Ron及CGs,CGD,CDs,提高击穿电压BVDSS,

并分析研究了栅电阻对器件微波性能的影响。在LDMOS的研究过程中,研究者们发现,

限制器件增益和效率的主要因素是沟道长度、源极接地电感和栅电阻。

LDMOS介绍

LDMOS( Laterally Diffused Metal Oxide Semiconductor;横向扩散金属氧化物半导体)是 为900MHz蜂窝电话技术开发的,蜂窝通信市场的不断增长保证了LDMOS晶体管的应用, 也使得LDMOS的技术不断成熟,成本不断降低,因此今后在多数情况下它将取代双极型 晶体管技术。与双极型晶体管相比,LDMOS管的增益更高,LDMOS管的增益可达14dB以 上,而双极型晶体管在5~6dB,采用LDMOS管的PA模块的增益可达60dB左右。这表明对于 相同的输出功率需要更少的器件,从而增大功放的可靠性。 LDMOS能经受住高于双极型晶体管3倍的驻波比,能在较高的反射功率下运行而没有 破坏LDMOS设备;它较能承受输入信号的过激励和适合发射数字信号,因为它有高级的 瞬时峰值功率。LDMOS增益曲线较平滑并且允许多载波数字信号放大且失真较小。 LDMOS管有一个低且无变化的互调电平到饱和区,不像双极型晶体管那样互调电平高且 随着功率电平的增加而变化。这种主要特性允许LDMOS晶体管执行高于双极型晶体管二 倍的功率,且线性较好。LDMOS晶体管具有较好的温度特性温度系数是负数,因此可以 防止热耗散的影响。这种温度稳定性允许幅值变化只有0.1dB,而在有相同的输入电平的 情况下,双极型晶体管幅值变化从0.5~0.6dB,且通常需要温度补偿电路。

功率半导体器件(LDMOS VDMOS)

1974 年,VVMOS(Vertical V-groove MOS)诞生,如图 3.1c 所示,此结构缺点:1)靠腐蚀形成 V-Groove, 不易工艺控制;2)V 形槽底部为尖峰,曲率大,电场较大,容易击穿,可靠性差等。

就会产生耗尽层,P 区一侧失去空穴会剩下固定不动的负电中心,N 区一侧会失去电子留下固定不动的正 电中心,并且正电中心所带的总电量=负电中心所带的总电量,如图 2.1a 所示,A 区就是所谓耗尽区。

图 2.1b 所示的是耗尽区中的电场分布情况(需熟悉了解),耗尽区以外的电场强度为零,Em 称为峰 值电场长度(它的位置在 PN 结交界处,原因可以从高斯原理说明),阴影部分的面积就是此时所加在 PN 结两端的电压大小。从以上的分析我们可以称这个结构的耐压部分为 P 区和 N 区共同耐压。图 2.2 所示的 是 P+N 结的情况,耐压原理和图 1 中的相同,但是在这种情况中我们常说 N 负区是耐压区域(常说的漂移 区),耐压大小由 N 区的浓度决定。

S

G

S

S

G

S

N

N

P

P

N

N

P

P

NN

D

图 4.1 处于关断状态下的 VDMOS

NN

D

图 4.2 处于导通状态下的 VDMOS

4.2 VDMOS 中的导通电阻 y在 VDMOS 中,顺着电子流的方向,整个导通电阻包括:沟道电阻、积累层电阻、寄生 JFET 电阻、 扩散电阻、外延层电阻、衬底电阻和金属导线电阻。(每个电阻在不同的耐压情况下所占总的导通 电阻的比例也使不同的,在低压的器件中,沟道电阻是主要的,在高压器件中,外延层的电阻是主 要的<取决于外延层的电阻率和厚度>,) y沟道电阻:取决于沟道长度、栅氧化层的厚度、载流子浓度、阈值电压和栅电压 VG . 一定的栅电压下,沟道电阻随着栅氧化层厚度的减小而减小 y积累层电阻:当器件导通后,栅下的 N-区会形成一层积累层,形成一层电阻很低的电子通道,这些 电子是从沟道出来的 y寄生 JFET 电阻:离开积累层的电子会垂直进入到硅体内(可以看成是一个 N 沟的 JFET),这个电 阻是随着源漏电压的变化而变化的,降低这个电阻的方法可以增加 P 井之间的距离,但是这样会影 响到集成度的提高。 y扩散电阻:当电子再往下走时,电子开始向下扩散流动(也有可能进入到其他的元胞中),由这些 电流流过的漂移区的电阻称为扩散电阻。 y外延层电阻:器件的耐压值决定了外延层的电阻率和厚度,高压器件中这个电阻很重要。外延层的 厚度一般由器件的耐压水平决定。 y衬底电阻:衬底电阻只在耐压值低于 50V 的情况中才比较明显。 y金属线和引线电阻:器件在和外部引脚相连的导线,在一般器件中,此电阻大概有几毫欧。

LDMOS简介及其技术详解

LDMOS简介及其技术详解LDMOS(Laterally Diffused Metal Oxide Semiconductor)横向扩散金属氧化物半导体)是为900MHz蜂窝电话技术开发的,蜂窝通信市场的不断增长保证了LDMOS 晶体管的应用,也使得LDMOS的技术不断成熟,成本不断降低,因此今后在多数情况下它将取代双极型晶体管技术。

与双极型晶体管相比,LDMOS管的增益更高,LDMOS管的增益可达14dB以上,而双极型晶体管在5~6dB,采用LDMOS管的PA模块的增益可达60dB左右。

这表明对于相同的输出功率需要更少的器件,从而增大功放的可靠性。

LDMOS能经受住高于双极型晶体管3倍的驻波比,能在较高的反射功率下运行而没有破坏LDMOS设备;它较能承受输入信号的过激励和适合发射数字信号,因为它有高级的瞬时峰值功率。

LDMOS增益曲线较平滑并且允许多载波数字信号放大且失真较小。

LDMOS 管有一个低且无变化的互调电平到饱和区,不像双极型晶体管那样互调电平高且随着功率电平的增加而变化。

这种主要特性允许LDMOS晶体管执行高于双极型晶体管二倍的功率,且线性较好。

LDMOS晶体管具有较好的温度特性温度系数是负数,因此可以防止热耗散的影响。

这种温度稳定性允许幅值变化只有0.1dB,而在有相同的输入电平的情况下,双极型晶体管幅值变化从0.5~0.6dB,且通常需要温度补偿电路。

LDMOS由于更容易与CMOS工艺兼容而被广泛采用。

LDMOS器件结构如图1所示,LDMOS是一种双扩散结构的功率器件。

这项技术是在相同的源/漏区域注入两次,一次注入浓度较大(典型注入剂量1015cm-2)的砷(As),另一次注入浓度较小(典型剂量1013cm-2)的硼(B)。

注入之后再进行一个高温推进过程,由于硼扩散比砷快,所以在栅极边界下会沿着横向扩散更远(图中P阱),形成一个有浓度梯度的沟道,它的沟道长度由这两次横向扩散的距离之差决定。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

开关电源SPIC—TOP223

2019/5/25

17/84

偏置电路

当发生欠压时,偏置电压1调节锯齿波发生器输出频率 由之前正常工作的100kHz减小为3kHz,减小功耗。

电路控制 电压

C1 R1

M3 偏置电压1

M1

M2

Q1

Q2

Q3 Q4

M6

M7

M5

偏置电压2

M4

Q5

C2

R3

R4

Q6 R2

欠欠压压保保 护护输输入出

2019/5/25

12/84

TOP223芯片管脚

DRAIN:输出管MOSFET的漏极。在启动时,通过一个内部 开关控制的高压电流源提供内部偏置电流。

CONTROL:作为占空比控制时,是误差放大器和反馈电流的 输入端。也用做内部电路和自动重启动/补偿电容的连接点。

SOURCE:Y型封装时,是输出MOSFET的源极,作为高压电 源的回路。原边控制电流的公共参考点。

2019/5/25

13/84

TOP223封装

2019/5/25

14/84

TOP223性能参数

极限参数 漏极电压:-0.3V到700V; 漏极电流增加速度(ΔID/每100ns): 0.1×ILIMIT(MAX) 控制脚电压:-0.3V到9V 控制脚电流:100mA 储存温度:-65到125℃ 工作结温度:-40到150℃

Q6、Q7的栅电压互反,控制C1的充放电

2V

0.7V

2019/5/25

锯齿波输出

偏置 方波脉冲

偏置

21/84

锯齿波电路仿真图

2019/5/25

频率为100KHz

22/84

PWM比较器

2019/5/25

23/84

PWM比较器仿真图

2019/5/25

24/84

驱动电路

偏置电 压

Q1

Q5

栅控电 压 Q4

第七章 智能功率集成电路的设计

2019/5/25

1

主要内容

SPIC设计考虑 PWM开关电源SPIC设计实例 荧光灯驱动SPIC设计实例

2019/5/25

2/84

SPIC设计考虑

工艺流程选择 功率器件关键参数确定 关键工艺参数设计

2019/5/25

3/84

智能功率集成电路SPIC

反馈电流小于2mA,电路以最大占空比67%工作; 反馈电流在2~6mA,电路工作占空比67%~1%工作; 反馈电流大于6mA,电路以最小占空比1%工作;

2019/5/25

PMOS宽长比很大, 实现旁路分流的作用

误差放大器输出

19/84

误差放大84

锯齿波发生器电路

2019/5/25

15/84

TOP223性能参数

电学参数 最大功率:50W(单一值电压输入)

30W(宽范围电压输入) *TO-220(Y)封装

导通电阻:7.8Ω (ID=100mA,Tj=25℃) 保护电流:1.00A(Tj=25℃) 最大占空比:67%

2019/5/25

16/84

LDMOS、VDMOS和IGBT等功率器件是SPIC 的核心,一 般功率器件约占整个芯片面积的1/2~2/3。

设计性能良好的功率器件是整个智能功率集成电路设计的 关键,其中耐压和导通电阻是SPIC的重要指标。

2019/5/25

7/84

功率器件的主要技术参数

击穿电压:源漏击穿电压BVDS、栅源击穿电压BVGS; 静态特性参数:阈值电压、IV特性、栅特性和特征

26/84

组合逻辑电路

2019/5/25

最大占空比不超过67% 最小导通时间(占空比

1%) 综合处理各种保护信号

2019/5/25

9/84

PWM开关电源SPIC设计实例

开关电源原理及开关电源SPIC 开关电源SPIC模块电路 开关电源SPIC的BCD工艺流程 开关电源SPIC的版图设计

2019/5/25

10/84

开关电源原理

311V

t

2t

3t

4t

311V

t

2t

3t

4t

2019/5/25

TOP223

1:8

Q8

Q7

R5

M8

Q9 基准电压

R6 Q10

IR5=(VBE6-VBE7)/R5=Vtln(IS6/IS7)/R5 ; IE9= IE5=2Vtln(IS6/IS7)/R5 ;

2019/5/25

VOUT=VE9=VBE10+2R6Vtln(IS6/IS7)/R5

18/84

误差放大器

反馈电流输入

一般包括: 功率控制 检测 / 保护 接口电路

目标

尽可能少的工艺步骤, 实现最佳功率器件性能

2019/5/25

4/84

工艺流程选择

SPIC一般实现方案:

在已有的CMOS或者BiCMOS工艺上进行改造,增加若干个 工艺步骤而实现。

工艺改造的好处:

一方面可以减小工艺成本和实现难度,另一方面也提高工艺 的稳定性。

11/84

开关电源TOP223

TOP223芯片是一个自我偏置、自我保护的用线性电流控制占空 比转换的开关电源。主要包括: 主电路部分

偏置电路、分流调整器/误差放大器电路、锯齿波发生器电路、 PWM比较器电路、最小导通时间延迟、驱动电路、组合逻辑电路 辅助保护电路部分

温度保护电路、过流保护电路、欠压保护电路、8分频复位延时 电路、高压充电电路

2019/5/25

5/84

SPIC基本工艺流程

SPIC工艺主要可分为外延层结构工艺和无外延层结构工艺。 这两种工艺技术各有特点,根据电路、器件、特性等方面不

同的要求,其最恰当的兼容工艺方式也大不相同。相比而言, 目前无外延层结构工艺较为普遍。

2019/5/25

6/84

功率器件关键参数确定

导通电阻等; 动态特性参数:栅电容、导通时间、关断时间和开关

频率等; 器件安全工作区(SOA)。

2019/5/25

8/84

关键工艺参数的设计

在改造工艺上调整有限的工艺参数使得功率器件性能最 佳是SPIC工艺必须要考虑的问题。

要确定这些最佳工艺参数,可以采用理论推导和TCAD 仿真相结合的方式。

Q2 Q3

偏置电 压 Q11

Q6

Q8

Vc Drain

Q12

Q16

Q7

Q19 Q21 Q23

Q25

Q13

Q14 Q17

C1 Q9 Q10

R1

Q15 Q18

Q22 Q24 Q20

0

2019/5/25

25/84

最小导通时间延迟模块

2019/5/25

• 增加这个电路其实就是加 了一个反馈,利用环路延迟, 使得当误差信号逐步增大到 大于锯齿波信号时,保持一 个最小的占空比。