主板上电时序精华

主板上电时序自己总结

在这里以ASUS的915主板来描述一下INTEL主板的上电及工作时序:1、当ATX Power送出士12V,+3.3V, 士数组Main Power电压后,其它工作电压如+VTT_CPU,+1.5V, +2.5V_DAC,+ 5V_Dual,+3V_Dual,+1.8V_Dual 也将随后全部送出.2、当+VTT_CPU送给CPU后,CPU会送出VTT_PWRGD言号[High]给CPU;ICS;VRM;CP用VTT_PWRGD言号确认VTT_CPU稳定在Spec之内,OK后CPU 会发出VID[0:5].VRM收到VTT_PWRGC后会根据VID组合送出Vcore.3、在VCORE正常发出后‘Processor Voltage Regulato即送出VRMPWRGD 言号给南桥ICH6以通知南桥此时VCORE已经正常发出.在VTT_PWRGDE常发出后,此信号还通知给Clock Generator(ICS以通知Clock Generator在可以正常发出所有Clock.4、当提供给的南桥工作电压及Clock都OK后由南桥发出PLTRST及PCIRST 给各个Device.The ICH6drives PLTRST#inactive a minimum of 1ms after both PWROK and VRMPWRGD are driven high.翻译:ICH6驱动PLTRST为无效的至少1毫秒,在PWROK和VRMPWRGD被置为高电平以后。

这里我的理解为在PWROK和VRMPWGRD发出后,至少IMS, ICH6才会发出PLTRST给北桥和SIO复位。

PLTRST与PCIRST K别如下:PLTRST# :Platform (翻译:平台指的是北桥+CPU)Reset PCIRST#:PLTRST# is higher than PCIRST#.在北桥NB接收到南桥送出的PLTRST大约1ms后,北桥送出CPURST给CPU以通知CPU可以开始执行第一个指令动作•(不过要北桥送出CPURST的前提是在北桥的各个工作电压&Clock都0K的情况下);下面是一个时序图,按照顺序,对应上述文字。

Intel主板上电时序讲解(3)

Intel主板上电时序讲解(3)

网芯;sio收到pfmrst#信号后,然后由sio的31脚输出pcierst#、33脚输出iderst#、34脚输出pfmrst1到bios和北桥。

(主板上的很多复位电路的复位端,有时候是直接并联在一起的,有时候是在复位端前面加一个缓冲器进行隔离,常用的缓冲器就是74f125。

)

在北桥nb接收到南桥送出的pfmrst1后,北桥送出cpurst#给775cpu,以通知cpu可以开始执行第一个指令动作.(不过要北桥送出cpurst#的前提是在北桥的各个工作电压&clock都ok的情况下)。

之后电脑就进入软启动状态,即bios开始工作,将控制权交给bios的post程序,由post程序检查硬件的工作状态和配置信息,产生各种总线信号,初始化硬件,点亮显示器,然后将控制权交给操作系统,完成软启动。

[1][2] [3]

分享到:0。

微星MS7309主板上电时序

微星MS7309主板上电时序第一部分:等待开机待机有三个条件:3VSB、25M晶振、PWRGD_SB。

一、纽扣电池供电:纽扣电池(此时不插电源线)BAT经过双二极管D22以及D28为桥(PBGA692)提供基本供电VBAT,25M晶振起振。

同时BAT还通过双二极管D22和电阻R699产生VBAT0链接到F71882的82脚,用于检测电池电量。

-1-VBAT通过R6产生信号COPEN#送到I/O(F71889ED的83脚,使该脚为高电平。

二、插入AT某电源,+5SB为主板供电1、5VDRV1的产生:当插入AT某电源,+5VSB为主板的部分电路供电,I/O的71脚(VCCGATE)为高电平,通过Q41产生5VDRV1.它的主要作用控制Q37-2-的导通,提升3VDUAL的输出功率(用UP7704产生);应用在3VSB_WAKE产生电路,同样提升3VSB_WAKE的功率。

-3-2、VCC_5SB的产生:当插入AT某电源,+5VSB通过Q110转换成VCC_5SB,主要是把电流从4A降低到2A。

5VSBDRV1的产生:IO的72脚产生DUALGATE信号,VCC5_SB经电阻R465和R466分压,产生此信号。

3、+3.3VDUAL的产生:产生方式可以有两种,一是通过1117来产生,二是通-4-过UP7501来产生。

(1)、通过U28(RC117S)产生:通过(2)通过UP7704产生,其2脚受控于信号y5VSB_OFF,这个信号由IO的47脚产生,同时控制USB接口和5vSBPOWERSWITH。

4、VSB3V的产生:3VDUAL(1.2A)通过D32产生VSB3V为IO的65脚供电。

-5--11-6、MEM_VLD信号的产生VCC_DDR产生后,加到Q33(CMKT3904-SOT363-6)的5脚,6脚产生MEM_VLD信号,送到桥的J3端,通知桥内存供电已经稳定。

-12-7、DDR_PWRGD产生:当内存供电产生后,由Q9产生DDR_PWRGD信号,送到940座的F3端,通知CPU内存供电已经准备好。

主板开机部分时序

主板开机部分时序以MS01 MB_DVT(SONY 915)为例一,静态(当电源适配器插到笔记本在未按开关之前,主板已有一部分电路在工作,为按开关做准备)。

具体上电时序:①主板供电DCBATOUT产生插入适配器到主板后经过保险丝送给MOS管,经过转换后将电源适配器的电转化为笔记本的主供电,主板各单元电路的供电都由主供电产生。

主供电会首先供给待机电源IC,电源IC会先产生EC和BIOS的主供电。

当EC和BIOS获得供电后发出触发信号给待机电源IC产生3V,5V待机电压(AIW/ON)供给南桥内部的待机电路,此时EC 发出静态OK(PM-RESMRST)信号告诉南桥静态OK。

此信号发出即标志着静态上电OK。

SONY915 详细过程:DC-IN经过电感PL1,PL2后再经过保险丝PF1和稳压二极管PD4送给MAX1909第1PIN,然后由第四PIN产生参考电压REF(标准电压4V),再由第27PIN输出一个低电平信号MAX109_PDS(9.0V),送给PQ51的第四PIN控制极,控制PQ51导通,把DC_IN转换成DC_IN_MOS送给PQ50的1,2,3PIN等待控制极的控制,同事由MAX1909第27PIN产生的低电平信号MAX1909_PDS经过一个电阻延时后送给PQ50的第四PIN控制极,控制PQ50导通,吧DC_IN_MOS转换成为DC_IN_R后送给电流传感器(PR155),由PR155侦测其通过本身的电流大小载反馈给MAX1909,由MAX1909根据此信息再调节第27PIN输出一个标准的低电平信号,从而控制PQ51,PQ50的导通状态,最终输出一个标准的DCBATOUT(18.6V)电压(此时主板主供电DCBATOUT已经标准的产生,电压电流够标准)MAX1909在给27PIN发出低电平的同时,就会由第28PIN输出一个高电平,控制PU1不导通。

为什么不让PQ1导通?是由于当同时插上直流电源与电池供电的时候,MAX1909就会主动优先选择直流电源供电,此时电池就不工作。

必备主板上电时序图,强烈推荐

POWER_CHARGER

输出低电平信号CHG_PDS开启A/D_DOCK_IN转化AC_BAT_SYS 输出低电平信号CHG_PDL开启BAT_CON转化AC_BAT_SYS

ACIN

输入电压

DCIN

ProTek MQC.

POWER PATH A/D_DOCK_IN→AC_BAT_SYS

EC-工作电压

+3VS是SB工作后由 SUSB#_PWR开启

ProTek MQC.

EC-RESET

+3VA_EC输入给芯片U3001产生EC_RST# 从pin19输入 ECProTΒιβλιοθήκη k MQC.EC-CLOCK

当EC接收到工作电压后就开始从pin160发出EC_XOUT 给晶振提供电压使其产生 32.768KHz的频率给EC工作

ProTek MQC.

返回南桥

PM_PWRBTN#

按下SW5605,则PWR_SW# 瞬间拉低

ProTek MQC.

+3VA_EC经过电阻到PWR_SW#,给 PWR_SW#一个高电平

南桥开机最后一个条件 返回南桥

南桥开机条件

+3VSUS PM_RSMRST# +VCC-RTC CLK(32.768KHz) PM_PWRBTN#

ProTek MQC.

PM_RSMRST

南桥开机条件之一 当EC pin54接收到SUS_PWRGD后从pin105发出PM_RSMRST#

ProTek MQC.

返回南桥

+VCC_RTC

南桥开机条件之一

C-MOS电池

+RTCBAT经过电阻R2001经过D2000产生+VCC_RTC

主板上电时序及名词解答

待机的时候,还是在开机触发后?

这个信号是南桥输出的时钟信号,外部晶谐频率一样,32.768K,是一个方波!只 要南桥被触发PWRBTN信号就会有

* 按下电源的开关后,送出PWRBTN#给 IO

或南桥或其它专门的开机复位芯片收到这一个方波信号后(在其它工作条件正常的情况下)就会发出下一步的工作信号(IO_PWRBTN)

IO_PWRBTN 就是IO收到开关信号后发出的一个同PWRBTN#一样的高低高变化的方波信号,这个信号送给南桥通知南桥开机

而按下开关的时候该信号变为0V低电平(开关的另一端是接地的,按下开关时就是把PWRBTN信号接到地上了),

然后松开开关PWRBTN又回到3.3V或5V的高电平。

8这一高低高的变化信号会送给IO或南桥或其它专门的开机复位芯片(有些中间会有一些电阻或门芯片中转一下)

INTEL芯片组主板上电时序 一, * 装入电池后首先送出RTCRST#, 3V—BAT 给南桥

* 晶振提供 32.768KHZ频率给南桥

* +5SB 转换出+3VSB, IO 检查 5VSB 是否正常,若正常则发出 RSMRST#

通知南桥待机电压OK

* 北桥接收到南桥发出的PLTRST#,且其电压,时钟都正常,大约1SMS后发 出CPURST#给CPU,通知CPU可以开始执行第一个指令动作

相关资料

/view/a72c961dc5da50e2524d7f7b.html

这个是一个开机信号,是一个低电平有效的信号 (南桥的触发信

号,低电平有效,常态为高电平)

PWRBTN 主板上电时的一个信号,即电脑开关就是这个信号,在电脑接通电源的时候,3VSB或5VSB通过一个4.7K或8.2K等的电阻给该信号提供上拉,所以在接通电 源时该信号的电压是3.3V或5V的高电平,

最新主板上电时序专业知识讲座

文档来源于网络,文档所提供的信息仅供参考之用,不能作为科学依据,请勿模

+2.5V_Dual 仿。文档如有不当之处,请联系本人或网站删除。

1.提供给内存和北桥部分的内存接口部分 使用,对于A8内存控制器集成在CPU中.

2.一般利用Linear Regulator由+3V_Dual 得到.或者是利用Switch Regulator由 +5V_Dual得到.

文档来源于网络,文档所提供的信息仅供参考之用,不能作为科学依据,请勿模

+2.5V 仿。文档如有不当之处,请联系本人或网站删除。

+2.5V的电压直接由+2.5V_Dual通过一个MOS开关提供,用 +12V作为MOS的gaห้องสมุดไป่ตู้e控制.从而保证进入S3时+2.5V可以被 关闭.避免漏电.

+2.5V_DUAL =-> +2.5V

文档来源于网络,文档所提供的信息仅供参考之用,不能作为科学依据,请勿模 仿。文档如有不当之处,请联系本人或网站删除。

±12V

1.+12V提供给Vcore(P5&P4&K8使用,K7使 用5V给Vcore供电).

2.+12V提供给PCI slot,AGP slot,COM芯 片,FAN power等.

主板的上的电压有+12V、-12V、+5V、(-5V)、+3V、+5VSB、 +3VSB、+1.5VSB、+1.5V、+5V_Dual、+3V_DUAL、+2.5V_DUAL、+ 2.5V_DAC、1.8V_Dual、VCORE、VTT_DDR、VTT+_CPU ect.

主板的上电时序及维修思路

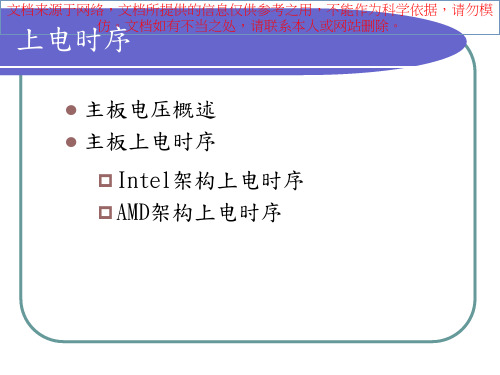

一般插上ATX电源后,先不要直接去将主板通电试机,而是要量测主板在待机状态下的一些重要工作条件是否是正常的。

在这里我们要引入“Power Sequencing”——上电时序这个概念,主板对于上电的要求是很严格的,各种上电的必备条件都要有着先后的顺序,也就是我们所说的“Power Sequencing”,一项条件满足后才可以转到下一步,如果其中的某一个环节出现了故障,则整个上电过程不能继续下去,当然也就不能使主板上电了。

主板上最基本的Power Sequencing可以理解为这样一个过程,RTCRST#-VSB 待机电压-RTCRST#-SLP_S3#-PSON#,掌握了Power Sequencing的过程,我们就可以一步的来进行反查,找到没有正常执行的那一个步骤,并加以排除。

下面具体介绍一下整个Power Sequencing的详细过程:1.在未插上ATX电源之前,由主板上的电池产生VBAT电压和CMOS跳线上的RTCRST#来供给南桥,RCTRST#用来复位南桥内部的逻辑电路,因此我们应首先在未插上ATX电源之前量测电池是否有电,CMOS跳线上是否有2.5V-3V的电压。

2.检查晶振是否输出了32.768KHz的频率给南桥(在nFORCE芯片组的主板上,还要量测25MHz的晶振是否起振)3.插上ATX电源之后,检查5VSB、3VSB、1.8VSB、1.5VSB、1.2VSB等待机电压是否正常的转换出来(5VSB和3VSB的待机电压是每块主板上都必须要有的,其它待机电压则依据主板芯片组的不同而不同,具体请参照相关芯片组的DATASHEET中的介绍)4.检查RSMRST#信号是否为3.3V的高电平,RSMRST#信号是用来通知南桥5VSB和3VSB待机电压正常的信号,这个信号如果为低,则南桥收到错误的信息,认为相应的待机电压没有OK,所以不会进行下一步的上电动作。

RSMRST#可以在I/O 、集成网卡等元件上量测得到,除了量测RSMRST#信号的电压外,还要量测RSMRST#信号对地阻值,如果RSMRST#信号处于短路状态也是不行的,实际维修中,多发的故障是I/O或网卡不良引起RMSRST#信号不正常。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ATX Power Supply

+12V: Pin3,4 主要用来给CPU Vcore部分供电 GND: Pin1,2

ATX2.2

ATX Power Supply

Voltage Tolerances

+5VSB

+5VSB: Standby power提供power down state下主板需 要的各种电压,包括:Standby and Dual power. ATX规定提供的电流不低于10mA.但是目前的主板为了提 供USB设备启动,网罗唤醒等功能,需要很大的电流.一般 的Power supply都可以提供2A左右. Tolerance: +5V± 5% 需要用到stand by power的包括:Super I/O, South Bridge,LAN chip,etc.在S3状态下,除了上述部分需要 之外Memory所需的+2.5V dual.

±12V

1.+12V提供给Vcore(P5&P4&K8使用,K7使 用5V给Vcore供电). 2.+12V提供给PCI slot,AGP slot,COM芯 片,FAN power等. 3.-12V提供给PCI slot和COM芯片.

+2.5V_Dual

1.提供给内存和北桥部分的内存接口部分 使用,对于A8内存控制器集成在CPU中. 2.一般利用Linear Regulator由+3V_Dual 得到.或者是利用Switch Regulator由 +5V_Dual得到.

CPU

PLTRST#

NB

CPURST#

PCIRST#

PCI Device

+VTT_CPU

3 3

+VTT_PWRGD

+

.

PWROK

v

v

v

AMD架构 上电时序

A8 k8 k8 A8

+ + + +

Nforce4 K8T800+VT8237 Sis760+Sis965 ATIRD480+M1573

SLP_S3# 5 SIO_PWBTIN 4.

SIO

ATX_PWRGD 8.

+12V&+5V&+3V 7

ATX

PSON# 6. VCORE_PG 13 HTT_VLD 13 HTT_EN PWRGD_SB 2. PWRBTIN

10

10 +1.2V_HT 11

VCORE&HTT

VCORE 12 +12V 7

• 当User按下Power Button后,一般由Super I/O将此信号 拉low,从而通知Power Supply送电.

PWROK

PWROK是电源准备OK信号.当电源送出的+3.3V and +5V 达到Normal值的95%时,由Power Supply送出此信号. 当+3.3V or +5V 掉到Normal的95%以下时,Power Supply就会把此信号拉Low. 当主板收到此信号时,表明电源已经准备ok,可以开始动 作. 但是大部分情况下,我们不会使用此信号来通知主板动 作.而是使用专门的ASIC来侦测+3.3V and +5V电压,当 电源发出的电压符合要求时,由ASIC发出PWROK信号通知 主板动作.由此功能的ASIC包括AS016,W83627EHF等. 主板上此PIN一般空接

主板上电时序

Intel架构上电时序

AMD架构上电时序

Intel架构上电时序

P5+Intel915G (P5GD2-VM为例).

1.未插电源时的主板准备上电状态. 2.插上电源后的主板动作时序. 3.按下Power Buttom后的动作时序.

1.未插电源时的主板准备上电状态

装入电池后首先送出RTCRST#&V_3V_BAT给南桥. Crystal 提供32.768KHz频率给南桥.

3.按下Power Buttom后的动作时 序

当电源送出的+3.3V and +5V达到Normal值的 95%时,由ATX Power Supply开始送出PWROK_PS 信号给Super IO,以通知Super IO ATX Main Power OK. Super IO接收到VCC&PWROK_PS后,即送出PWROK 给南北桥.以通知南北桥此时ATX Main Power 送出OK.

3.按下Power Buttom后的动作时 序

在北桥NB接收到南桥送出的PLTRST#大约1ms后,北桥 送出CPURST#给CPU,以通知CPU可以开始执行第一个指 令动作.(不过要北桥送出CPURST#的前提是在北桥的 各个工作电压&Clock都OK的情况下);

P5GD2-VM 上电时序图

+3.3V

主板上有很多地方都需要+3.3V. +3.3V一般是最晚从Power Supply供出的. 一般电源提供5A左右的电流. 电压供给: Audio Chipset; PCI; PCIEX; South Bridge; SIO; Bios;

±5V

1.主板上IO几乎全部使用+5V,比如: KB&MS,USB,F_PANEL等.同时提供给IO控制 器Super I/O. 2.-5V现在已经不使用.

A8N-SLI 上电时序

CPU_PWOK 14 VCORE 12 +1.2V_HT 11 CPURST# 15 PWROK 9. +5VSB 1

A8 + Nforce4 (A8N-SLI为例)

+ 3 1

25MHZ 1

vsb

CPU

3.3&1.5PLL 电压 7

+1.5v 7

Nforce4

CPUVDD_EN

VRMPWRGD PWROK_PS +VTT_PWRGD CPUPWRGD

3

V R M

+VID[ 0:5 ] Vcore

+ VSB

3v_Bat RTC_RST#

RSMRST#

IO_PWRBTN#

SLP_S3#

32.768

+3Vsb

SB

SLP_S4# PWRBTN#

SIO

PS_ON#

ATX

+ 12 5 +

+ V DDA _E N <3 4>

2

P CE6 10 UF/25 V /X

GND

PSON#

• PSON# 是低有效信号,当此信号为Low时,Power Supply 送出+3.3V,+5V,-5V,+12V,-12V等电压. 而当此信号被 拉High时,Power Supply停止送出上面的电压. • 利用此信号可以设计“ Soft Power down” 的关机功 能. 当使用者对操作系统下关机命令时. 操作系统亦 可关闭所有的应用程序并利用此脚的功能达到自动关机 的动作. • 在主板上需要把此信号 pull up到+5VSB.

3.按下Power Buttom后的动作时 序

当ATX Power送出±12V, +3.3V, ±5V数组Main Power电 压后,其它工作电压如+VTT_CPU,+1.5V, +2.5V_DAC,+ 5V_Dual,+3V_Dual,+1.8V_Dual也将随后全部送出. 当+VTT_CPU送给CPU后,CPU会送出VTT_PWRGD信号[High] 给CPU;ICS;VRM; CPU用VTT_PWRGD信号确认VTT_CPU稳定在Spec之内,OK 后CPU会发出VID[0:5]. VRM收到VTT_PWRGD后会根据VID组合送出Vcore. 在VCORE正常发出后,Processor Voltage Regulator即 送出VRMPWRGD信号给南桥ICH6,以通知南桥此时 VCORE 已经正常发出.

3

.

K8V-MX 上电时序图

K8 + K8M800+VT8237 (K8V-MX为例)

CPU_PWOROK 18 CPU_RST# 20

PWRBTIN# 3 .

2.插上电源后的主板动作时序

SIO Check电源是否正常提供+5VSB电压. +5Vsb正常转换出+3VSB. SIO发出RSMRST#信号通知南桥+5VSB已经准备OK. 南桥正常送出SUSCLK (32KHZ).

பைடு நூலகம்

3.按下Power Buttom后的动作时 序

+2.5V

+2.5V的电压直接由+2.5V_Dual通过一个MOS开关提供,用 +12V作为MOS的gate控制.从而保证进入S3时+2.5V可以被 关闭.避免漏电.

+2.5V_DUAL =-> +2.5V

+2 .5V _DA UL Q23 NDS3 51 N

2 S 3 D

+2 .5V

G

1

1

+1 2V P R12 1 2 8.2 KOhm

MB上电时序

2005.12

Caspar_zhang

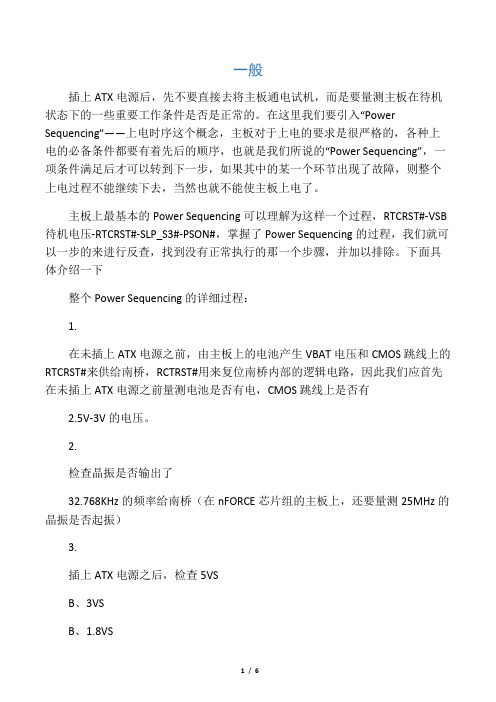

上电时序

主板电压概述 主板上电时序

Intel架构上电时序 AMD架构上电时序