Protel中英文对照表

Protel 99 元器件中英文对照表以及库对照表

CUSIICProtel 99各元器件名字中英文对照表以及各种库的对照电阻AXIAL无极性电容RAD电解电容RB-电位器VR二极管DIODE三极管TO电源稳压块78和79系列TO-126H和TO-126V场效应管和三极管一样整流桥D-44 D-37 D-46单排多针插座CON SIP双列直插元件DIP晶振XTAL1电阻:RES1,RES2,RES3,RES4;封装属性为axial系列无极性电容:cap;封装属性为RAD-0.1到rad-0.4电解电容:electroi;封装属性为rb.2/.4到rb.5/1.0电位器:pot1,pot2;封装属性为vr-1到vr-5二极管:封装属性为diode-0.4(小功率)diode-0.7(大功率)三极管:常见的封装属性为to-18(普通三极管)to-22(大功率三极管)to-3(大功率达林顿管)电源稳压块有78和79系列;78系列如7805,7812,7820等79系列有7905,7912,7920等常见的封装属性有to126h和to126v整流桥:BRIDGE1,BRIDGE2: 封装属性为D系列(D-44,D-37,D-46)电阻:AXIAL0.3-AXIAL0.7 其中0.4-0.7指电阻的长度,一般用AXIAL0.4瓷片电容:RAD0.1-RAD0.3。

其中0.1-0.3指电容大小,一般用RAD0.1电解电容:RB.1/.2-RB.4/.8 其中.1/.2-.4/.8指电容大小。

一般<100uF用B.1/.2,100uF-470uF用RB.2/.4,>470uF用RB.3/.6二极管:DIODE0.4-DIODE0.7 其中0.4-0.7指二极管长短,一般用DIODE0.4发光二极管:RB.1/.2集成块:DIP8-DIP40, 其中8-40指有多少脚,8脚的就是DIP8贴片电阻0603表示的是封装尺寸与具体阻值没有关系但封装尺寸与功率有关通常来说0201 1/20W0402 1/16W0603 1/10W0805 1/8W1206 1/4W电容电阻外形尺寸与封装的对应关系是:0402=1.0x0.50603=1.6x0.80805=2.0x1.21206=3.2x1.61210=3.2x2.51812=4.5x3.22225=5.6x6.5关于零件封装我们在前面说过,除了DEVICE。

protel99se中英文对照

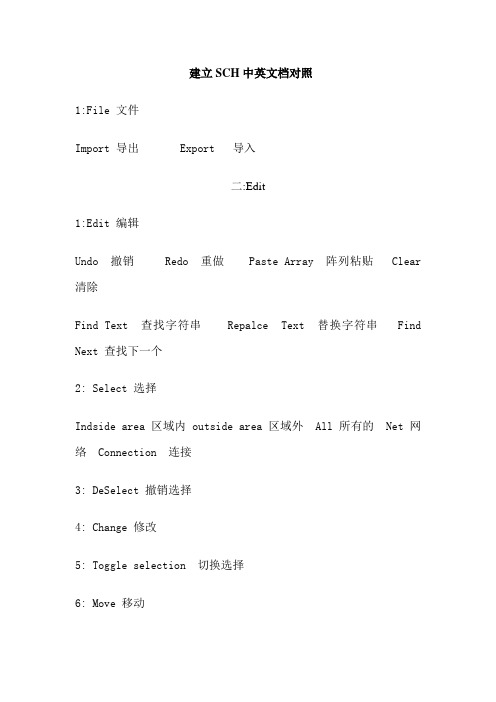

建立SCH中英文档对照1:File 文件Import 导出 Export 导入二:Edit1:Edit 编辑Undo 撤销 Redo 重做 Paste Array 阵列粘贴 Clear 清除Find Text 查找字符串 Repalce Text 替换字符串 Find Next 查找下一个2: Select 选择Indside area 区域内 outside area 区域外 All所有的 Net 网络 Connection 连接3: DeSelect 撤销选择4: Change 修改5: Toggle selection 切换选择6: Move 移动Drog 拖拉move 移动move selection 移动选择部分drag selection 拖拉选择部分 Move to Front 移动前面 bring to frint 带到前面 send to back 送到后面 bring to frint of 带到某个前面send to back of 送到某个后面7: Align 排齐Align 排齐Align left 左排齐Align Right 右排齐Center Horizontally 水平队中 Distribute Horizontally 水平均布Align top 顶端对齐 Align bottom 底部对齐Center ventical 垂直对中 diatribute vertically 垂直分布8: JUMP 跳转Jump to eroor marker 跳到错误标记 origin 原点 new location 新坐标 location market标记9: SET location marks 设置位置标记10: Incerment park number 增加部件号11: Export to spread 导出电子表格三:View 视图1: View 视图Fit document 适合文档 Around point 以点为中心 zoom in 放大zoom out 缩小 pan摇景 refresh 刷新 visible grid 可视网格 electrical 电气网格 snap grid 捕获网格2: Place 放置Bus 总线 bus entry 总线入口 part 元件 juncttion 节点power port 电源端口 wire电线 net lable 网络标号 port 端口 sheet symbol sheet 符号 add sheet entry 添加sheet入口3: Directives 标志No erc 不做电气规格检查 probe 探测点 text vector index 测试矢量索引 stimulus 激励 pcb layout pcb设计 annotation 注释 text frame 字符帧4: Drawing tools 绘图工具Arcs 弧 elipses 椭圆 elipses arcs椭圆弧 line 线 round rectangle 圆角矩形 polygoncs 多边形 Beziers 贝尔赛曲线graphic 图形 pie charts 陷饼型 rectangle 矩形5: Process container 过程容器四:Design 视图1: Design 设计Update pcb 更新pcb browse library 元件库浏览 add/remove library 添加/删除原件库 marke project library 生成方案群update parts in cashe 更新缓冲器中的部件2: Template模块Update 更新 set Template name 设置模块文件名 remove current template 删除当前模块3: Creat Netlist创建网络表4: Creat sheet from symbol从符号生成图纸5: Creat symbol from sheet从图纸生成符号6: Option选项Sheet option 选项 Template 模块 file name to template file 没有模块文件 orientation 方向 land scape 风景 portrait 肖像 title blo 标题块 standard 标准 show reference zoom显示参考区域 show template graphic 显示模块图形 Border Grids 网格 snap 捕获 visib 可视 electrical grib 电气网格 enble 可用 grid 网格排列 stand style 标准风格custom width 定制宽度 custom height定制高度X ref 区域数7:Design 设计中的Update pcb选项Synchronization 同步sheet symbol/port connection sheet 符号/端口连接 connectivety 连接net labels and ports global 网络标签和端口全局 only ports and ports global 仅端口全局 append sheet numbers to net 添加sheet数到本地网络assign net to connected cop分配网络到连接的铜 descend into sheet ports 下来到sheet部件 components 元件Update component footprinted 更新元件的封装delete component 删除元件 generate pcbRules according to schematic layout 依照原理图规划指示创建pcb规则 classes 类Genrate component class for all schematic sch 为全部在项目的原理图sheets生成元件类Genrate net class form all busses in project 为全部在项目的总线生成网络类Preview change 预览改变 execute 执行 cancel 取消五:Tools工具1: Tools工具Erc 电气规则检查 up/down hierarchy 变换层次 find component 查找元件 complex to simple 复杂变简单2: Annotate注释Options 选项 all parts 全部部件 reset designators 复位元件的标号 update sheets number only 仅仅更新sheet数字 current sheet only 当前的唯一的sheet ignore selection part 忽略已选择的部件 group parts together if match by 如果匹配合并成部件组 re-annotate method重新注释方法 up then across 向上然后横过 down then across 向下然后横过 across then up 横过然后向上across then down 横过然后向下 advance options 高级选项3: Back Annotate反向注释Up/down hiercrchy 变换层次 complex to simple 复杂变简单4: Database links数据连接5: Process containers过程容器Configure 配置6: Cross probe交叉检索7: Preferences 优选项Pin options 引脚选项 pin name 加注引脚名字 pin number 加注引脚数multi-part suffix muti-部件后缀orcad load options orcad载入选项 codv footprint from/to 复制封装从/到Part filed 部件域 1 auto-juntion 自动-接点 drag orthqonal 画直角 enable in-place editing 启用—放置编辑的 Default powerobject names 默认电源项目名 power gound 是GND的意思signal ground sgnd SGND8: Preferences 中的graphical editing 图形编辑Options 选项Clipboard reference 剪贴板参考 add template to clip 增加模块到剪贴板 convert special string 转换特殊字符串 display printer fonts 显示打印机字体 center of object 物体的中心Objects electrical junction 实体的电气节点 auto zoom 自动缩放singnel/negation 单一的拒绝color options 颜色选项seletion 选项 grid 风格颜色 autopan options 自动摇景选项Auto pan fixed 自动摇景固定跳跃 Auto pan off 自动摇景固定关闭 Auto pan recenter自动摇景回到中心 Cursor/grid options 光标/网格选项 visible 可视网格 line grid 线网格Dot line 点网格 undo/redo 撤销/重做 stack size 层堆大小ignore seletion 忽略选择Defult primitives 默认原始的 primitives tyle 原始的类型all 所有的 wiring 连线 drawing画图directives 指令part fields 部件域sheet symbol fileds sheet符号域 library symbol fields 库部件 others 其他9: Primitives 原始的Arc 弧bus 总线bus entry 总线入口designator 元件标号elliptical arc 椭圆弧eroor marker 错误标记ieee symbolieee符号 image 图像 junction 节点 line 线 net lable 网络标签 part 部件 part fileld1 部件域 1 part type 部件类型pin 引脚 polygon 多边形 port 端口 power object 电源实体 probe 检索 process containe 过程容器六:Siumlate仿真1:Siumlate仿真Run 执行sources 源+5v volts +5vDC 1khz sine wave 1khz 正弦波 1khz pulse 1khz脉冲 create spice netlist 设计层次建立表格库文件(lib)一: Place 放置Pains 管脚 pie charts 馅饼型二: Tools 工具New component 新建文件 remove component 删除元件 rename component 元件重命名add component 添加元件名copy component 复制元件 move component 移动元件 new part 新建文件 remove part 删除元件 next component 下一个元件find component 查找元件description 描述remove duplicates 删除附件 update schematic 更新原理图三: options 选项Preferences 引脚选项 pin name 加注引脚名字 pin number 加注引脚数 alpha 字母 numeric 数字四: Document options 文档选项Setting 设置 stvle 风格 standard 标准 size 大小 show border 显示边界 show Hidden 显示隐藏引脚 custom size 定制大小 use custom size 使用定制大小Border 边界 workspace 工作空间 library options 库选项建立PCB中英文档表格对照1:Edit 编辑Select 选择 off grid pads 不再网格的焊盘 hole size 孔径 toggle selection 取消选择2:Move 移动break track 折断连线 drag track end 拖拉终点Move selection 移动选择 rotute selection 旋转选择 flipselection 翻转选择3:Set reference 设置参考点Pin1 管脚1 center 中心 location 坐标4:Jump 跳转Reference 参考点 new location 新坐标 x-location x-位置5:View 视图Around point 以点中心design manager 设计管理器status bar状态栏 command status 命令状态栏 toolbars 工具条 main toolbars主工具条 customize 定制6:Place 放置arc(center)弧 arc(Any angle)尺寸标注 Arc(edge)坐标 full circle 大循环 full 填充track 铜膜走线 string 字符串 pad 焊盘 via常规 keep out 放置布线区域7:Tools 工具Library options 库选项 grids 网格 snap x 捕获X snap Y 捕获Y component X 元件Xmponent Y 元件Y electrical grid 电气网格 range 排列visible kin 可视种类 lines 线dots 点 measurement 测量单位 imperial 英制 metric 米制Document options 文档选项 layers层 singal layers 信号层 mechanical layers机械层 masks 面 top solder 顶焊层 bottom solder 底助焊层 top paste 顶层阻焊层Bottom paste 底层阻焊层 silkscreen 丝印层 top overlayer 顶层丝印层bottom overlayer 底层丝印层others 其他keepout layers 禁止层 multi layer multi层Drill guide 钻孔机指南 Drill drawing 钻孔机图画System 系统 drc errors drc错误 connections 连接 pad holes 焊盘孔 via holes过孔 all on 全部打开 all off 全部关闭 used on 使用Tools 工具中的 preferencesOptions 选项 editing options 编辑选项 online drc 联机DRC Snap to center 捕获中心 extend selection 扩展选择 remove Duplio 删除副本 confirm golbal 确认全局编辑 project locked Object 保护锁定物体 autopan options 自动摇景 style 风格Adaptive 适应的 disable 禁用 re-center 在中心 fixed size Jump 固定大小跳转shift accelerate 移动加速shift decelerate移动减速 ballistic 冲击 polygon repour 多边形重新覆铜Never 决不 threshold 开始 always 总是P references 优选项Other 其他 rotation ste 旋转步 interactive routing 交互布线Undo/redo 撤销/重做 mode 方式 avoid obstacle 避免障碍ignore obstacle忽略障碍 push obstacle 推动障碍 cursor type 光标类型automaticany remove自动删除环 component 元件拖拉 connected tracks 已连接的轨迹Display 显示Convert special 转换特殊字符串 highlight in full 加亮区网络颜色 use net color for 加亮区的网络颜色 redraw layer 重画层 single layer mode 单一的层方式 transparent layer 透明层 show 显示 pad nets 焊盘网络 pad numbers 焊盘数 via nets 过孔网络Text points 测试点origin marker 原点坐标status information 状态信息 draft thresholds 草稿极限 tracks 轨迹 string 字符串 layer drawing order 层画图规则Colors 颜色Signal layers 信号层 internal planes 内电层 mechanical layers 机械层 system 系统 background 背景Default 默认值Primitive type 默认值 dlmension 尺寸 radius 半径 start angle 开始角 end angle 末端角 locked 锁定的 selection 选择Component 元件的 properties 属性的 designator 元件标号rotation 旋转 locks prims 锁原始的 font 字体 autoposition 自动位置建立PCB中英文档表格对照(PCB)1:View 视图Around point 以点为中心 board in 3D pcb3D显示 connections 连接 show net 显示网络 hide component nets 隐藏元件网络 toggle units 公/英制转换2:Place 放置Plane settings 网层设置grid size 网格尺寸track width 轨迹宽度 hatching style 阴影风格 90-degree hatch 90度开口 45-degree hatch 45度开口 wertical hatch 垂直开口horizontal hatch 水平开口 no hatching 没有开口2:T00lS 工具Design rule check 设计规则检查 report 报告 on-line 在一线routing rules 布线规则Clearance constraints 强制清除 max/min width const 强制最大/最小宽度 short circuitConstrair 强制短路 un-routed net constor 强制解除网络布线maufucturing 手动规则High speed rules 高速规则 max/min hole size最大/最小孔进大小 layer pains 层对Test point user 定制测试点 options 选项 create report 创建报告文件 create violation创建冲突记录 sub-net 子网络目录 stop whe 中止(500)冲突发现 internal plane warm内部电层警告reset error markers 清除错误标志auto placement 自动布局1。

protel99se中英文对照

建立SCH中英文档对照1:File 文件Import 导出Export 导入二:Edit1:Edit 编辑Undo 撤销Redo 重做Paste Array 阵列粘贴Clear 清除Find Text 查找字符串Repalce Text 替换字符串Find Next 查找下一个2: Select 选择Indside area 区域内outside area 区域外All所有的Net 网络Connection 连接3: DeSelect 撤销选择4: Change 修改5: Toggle selection 切换选择6: Move 移动Drog 拖拉move 移动move selection 移动选择部分drag selection 拖拉选择部分Move to Front 移动前面bring to frint 带到前面send to back 送到后面bring to frint of 带到某个前面send to back of 送到某个后面7: Align 排齐Align 排齐Align left 左排齐Align Right 右排齐Center Horizontally 水平队中Distribute Horizontally 水平均布Align top 顶端对齐Align bottom 底部对齐Center ventical 垂直对中diatribute vertically 垂直分布8: JUMP 跳转Jump to eroor marker 跳到错误标记origin 原点new location 新坐标location market 标记9: SET location marks 设置位置标记10: Incerment park number 增加部件号11: Export to spread 导出电子表格三:View 视图1: View 视图Fit document 适合文档Around point 以点为中心zoom in 放大zoom out 缩小pan摇景refresh 刷新visible grid 可视网格electrical 电气网格snap grid 捕获网格2: Place 放置Bus 总线bus entry 总线入口part 元件juncttion 节点power port 电源端口wire 电线net lable 网络标号port 端口sheet symbol sheet 符号add sheet entry 添加sheet入口3: Directives 标志No erc 不做电气规格检查probe 探测点text vector index 测试矢量索引stimulus 激励pcb layout pcb设计annotation 注释text frame 字符帧4: Drawing tools 绘图工具Arcs 弧elipses 椭圆elipses arcs椭圆弧line 线round rectangle 圆角矩形polygoncs 多边形Beziers 贝尔赛曲线graphic 图形pie charts 陷饼型rectangle 矩形5: Process container 过程容器四:Design 视图1: Design 设计Update pcb 更新pcb browse library 元件库浏览add/remove library 添加/删除原件库marke project library 生成方案群update parts in cashe 更新缓冲器中的部件2: Template模块Update 更新set Template name 设置模块文件名remove current template 删除当前模块3: Creat Netlist创建网络表4: Creat sheet from symbol从符号生成图纸5: Creat symbol from sheet从图纸生成符号6: Option选项Sheet option 选项Template 模块file name to template file 没有模块文件orientation 方向land scape 风景portrait 肖像title blo?标题块standard 标准show reference zoom 显示参考区域show template graphic 显示模块图形BorderGrids 网格snap 捕获visib 可视electrical grib 电气网格enble 可用grid 网格排列stand style 标准风格custom width 定制宽度custom height定制高度X ref 区域数7:Design 设计中的Update pcb选项Synchronization 同步sheet symbol/port connection sheet 符号/端口连接connectivety 连接net labels and ports global 网络标签和端口全局only ports and ports global 仅端口全局append sheet numbers to net 添加sheet数到本地网络assign net to connected cop? 分配网络到连接的铜descend into sheet ports 下来到sheet部件components 元件Update component footprinted 更新元件的封装delete component 删除元件generate pcb Rules according to schematic layout 依照原理图规划指示创建pcb规则classes 类Genrate component class for all schematic sch? 为全部在项目的原理图sheets生成元件类Genrate net class form all busses in project 为全部在项目的总线生成网络类Preview change 预览改变execute 执行cancel 取消五:Tools工具1: Tools工具Erc 电气规则检查up/down hierarchy 变换层次find component 查找元件complex to simple 复杂变简单2: Annotate注释Options 选项all parts 全部部件reset designators 复位元件的标号update sheets number only 仅仅更新sheet数字current sheet only 当前的唯一的sheet ignore selection part 忽略已选择的部件group parts together if match by 如果匹配合并成部件组re-annotate method 重新注释方法up then across 向上然后横过down then across 向下然后横过across then up 横过然后向上across then down 横过然后向下advance options 高级选项3: Back Annotate反向注释Up/down hiercrchy 变换层次complex to simple 复杂变简单4: Database links数据连接5: Process containers过程容器Configure 配置6: Cross probe交叉检索7: Preferences 优选项Pin options 引脚选项pin name 加注引脚名字pin number 加注引脚数multi-part suffix muti-部件后缀orcad load options orcad载入选项codv footprint from/to 复制封装从/到Part filed 部件域1 auto-juntion 自动-接点drag orthqonal 画直角enable in-place editing 启用—放置编辑的Default powerobject names 默认电源项目名power gound 是GND的意思signal ground sgnd SGND8: Preferences 中的graphical editing 图形编辑Options 选项Clipboard reference 剪贴板参考add template to clip 增加模块到剪贴板convert special string 转换特殊字符串display printer fonts 显示打印机字体center of object 物体的中心Objects electrical junction 实体的电气节点auto zoom 自动缩放singnel/negation 单一的拒绝color options 颜色选项seletion 选项grid 风格颜色autopan options 自动摇景选项Auto pan fixed 自动摇景固定跳跃Auto pan off 自动摇景固定关闭Auto pan recenter自动摇景回到中心Cursor/grid options 光标/网格选项visible 可视网格line grid 线网格Dot line 点网格undo/redo 撤销/重做stack size 层堆大小ignore seletion 忽略选择Defult primitives 默认原始的primitives tyle 原始的类型all 所有的wiring 连线drawing 画图directives 指令part fields 部件域sheet symbol fileds sheet符号域library symbol fields 库部件others 其他9: Primitives 原始的Arc 弧bus 总线bus entry 总线入口designator 元件标号elliptical arc 椭圆弧eroor marker 错误标记ieee symbol ieee符号image 图像junction 节点line 线net lable 网络标签part 部件part fileld1 部件域1 part type 部件类型pin 引脚polygon 多边形port 端口power object 电源实体probe 检索process containe 过程容器六:Siumlate仿真1:Siumlate仿真Run 执行sources 源+5v volts +5vDC 1khz sine wave 1khz 正弦波1khz pulse 1khz脉冲create spice netlist 设计层次建立表格库文件(lib)一: Place 放置Pains 管脚pie charts 馅饼型二: Tools 工具New component 新建文件remove component 删除元件rename component 元件重命名add component 添加元件名copy component 复制元件move component 移动元件new part 新建文件remove part 删除元件next component 下一个元件find component 查找元件description 描述remove duplicates 删除附件update schematic 更新原理图三: options 选项Preferences 引脚选项pin name 加注引脚名字pin number 加注引脚数alpha 字母numeric 数字四: Document options 文档选项Setting 设置stvle 风格standard 标准size 大小show border 显示边界show Hidden 显示隐藏引脚custom size 定制大小use custom size 使用定制大小Border 边界workspace 工作空间library options 库选项建立PCB中英文档表格对照1:Edit 编辑Select 选择off grid pads 不再网格的焊盘hole size 孔径toggle selection 取消选择2:Move 移动break track 折断连线drag track end 拖拉终点Move selection 移动选择rotute selection 旋转选择flip selection 翻转选择3:Set reference 设置参考点Pin1 管脚1 center 中心location 坐标4:Jump 跳转Reference 参考点new location 新坐标x-location x-位置5:View 视图Around point 以点中心design manager 设计管理器status bar状态栏command status 命令状态栏toolbars 工具条main toolbars主工具条customize 定制6:Place 放置arc(center)弧arc(Any angle)尺寸标注? Arc(edge)坐标full circle 大循环full 填充track 铜膜走线string 字符串pad 焊盘via常规keep out 放置布线区域7:Tools 工具Library options 库选项grids 网格snap x 捕获X snap Y 捕获Y component X 元件Xmponent Y 元件Y electrical grid 电气网格range 排列visible kin 可视种类lines 线dots 点measurement 测量单位imperial 英制metric 米制Document options 文档选项layers层singal layers 信号层mechanical layers 机械层masks 面top solder 顶焊层bottom solder 底助焊层top paste 顶层阻焊层Bottom paste 底层阻焊层silkscreen 丝印层top overlayer 顶层丝印层bottom overlayer 底层丝印层others 其他keepout layers 禁止层multi layer multi层Drill guide 钻孔机指南Drill drawing 钻孔机图画System 系统drc errors drc错误connections 连接pad holes 焊盘孔via holes 过孔all on 全部打开all off 全部关闭used on 使用Tools 工具中的preferencesOptions 选项editing options 编辑选项online drc 联机DRC Snap to center 捕获中心extend selection 扩展选择remove Duplio 删除副本confirm golbal 确认全局编辑project locked Object 保护锁定物体autopan options 自动摇景style 风格Adaptive 适应的disable 禁用re-center 在中心fixed sizeJump 固定大小跳转shift accelerate 移动加速shift decelerate 移动减速ballistic 冲击polygon repour 多边形重新覆铜Never 决不threshold 开始always 总是P references 优选项Other 其他rotation ste 90.000 旋转步90.000 interactive routing 交互布线Undo/redo 撤销/重做mode 方式avoid obstacle 避免障碍ignore obstacle忽略障碍push obstacle 推动障碍cursor type 光标类型automaticany remove自动删除环component 元件拖拉connected tracks 已连接的轨迹Display 显示Convert special 转换特殊字符串highlight in full 加亮区网络颜色use net color for 加亮区的网络颜色redraw layer 重画层single layer mode 单一的层方式transparent layer 透明层show 显示pad nets 焊盘网络pad numbers 焊盘数via nets 过孔网络Text points 测试点origin marker 原点坐标status information 状态信息draft thresholds 草稿极限tracks 轨迹string 字符串layer drawing order 层画图规则Colors 颜色Signal layers 信号层internal planes 内电层mechanical layers 机械层system 系统background 背景Default 默认值Primitive type 默认值dlmension 尺寸radius 半径start angle 开始角end angle 末端角locked 锁定的selection 选择Component 元件的properties 属性的designator 元件标号rotation 旋转locks prims 锁原始的font 字体autoposition 自动位置建立PCB中英文档表格对照(PCB)1:View 视图Around point 以点为中心board in 3D pcb3D显示connections 连接show net 显示网络hide component nets 隐藏元件网络toggle units 公/英制转换2:Place 放置Plane settings 网层设置grid size 网格尺寸track width 轨迹宽度hatching style 阴影风格90-degree hatch 90度开口45-degree hatch 45度开口wertical hatch 垂直开口horizontal hatch 水平开口no hatching 没有开口2:T00lS 工具Design rule check 设计规则检查report 报告on-line 在一线routing rules 布线规则Clearance constraints 强制清除max/min width const 强制最大/最小宽度short circuit Constrair 强制短路un-routed net constor 强制解除网络布线maufucturing 手动规则High speed rules 高速规则max/min hole size最大/最小孔进大小layer pains 层对Test point user 定制测试点options 选项create report 创建报告文件create violation创建冲突记录sub-net 子网络目录stop whe? 中止(500)冲突发现internal plane warm 内部电层警告reset error markers 清除错误标志auto placement 自动布局1。

PROTEL99中的中英文对照名称

PROTEL99中的中英文对照名称一、综合词汇1、印制电路:printed circuit2、印制线路:printed wiring3、印制板:printed board4、印制板电路:printed circuit board (PCB)5、印制线路板:printed wiring board(PWB)6、印制元件:printed component7、印制接点:printed contact8、印制板装配:printed board assembly9、板:board10、单面印制板:single-sided printed board(SSB)11、双面印制板:double-sided printed board(DSB)12、多层印制板:mulitlayer printed board(MLB)13、多层印制电路板:mulitlayer printed circuit board14、多层印制线路板:mulitlayer prited wiring board15、刚性印制板:rigid printed board16、刚性单面印制板:rigid single-sided printed borad17、刚性双面印制板:rigid double-sided printed borad18、刚性多层印制板:rigid multilayer printed board19、挠性多层印制板:flexible multilayer printed board20、挠性印制板:flexible printed board21、挠性单面印制板:flexible single-sided printed board22、挠性双面印制板:flexible double-sided printed board23、挠性印制电路:flexible printed circuit (FPC)24、挠性印制线路:flexible printed wiring25、刚性印制板:flex-rigid printed board, rigid-flex printed board26、刚性双面印制板:flex-rigid double-sided printed board, rigid-flex double-sided printed27、刚性多层印制板:flex-rigid multilayer printed board, rigid-flex multilayer printed board28、齐平印制板:flush printed board29、金属芯印制板:metal core printed board30、金属基印制板:metal base printed board31、多重布线印制板:mulit-wiring printed board32、陶瓷印制板:ceramic substrate printed board33、导电胶印制板:electroconductive paste printed board34、模塑电路板:molded circuit board35、模压印制板:stamped printed wiring board36、顺序层压多层印制板:sequentially-laminated mulitlayer37、散线印制板:discrete wiring board38、微线印制板:micro wire board39、积层印制板:buile-up printed board40、积层多层印制板:build-up mulitlayer printed board (BUM)41、积层挠印制板:build-up flexible printed board42、表面层合电路板:surface laminar circuit (SLC)43、埋入凸块连印制板:B2it printed board44、多层膜基板:multi-layered film substrate(MFS)45、层间全内导通多层印制板:ALIVH multilayer printed board46、载芯片板:chip on board (COB)47、埋电阻板:buried resistance board48、母板:mother board49、子板:daughter board50、背板:backplane51、裸板:bare board52、键盘板夹心板:copper-invar-copper board53、动态挠性板:dynamic flex board54、静态挠性板:static flex board55、可断拼板:break-away planel56、电缆:cable57、挠性扁平电缆:flexible flat cable (FFC)58、薄膜开关:membrane switch59、混合电路:hybrid circuit60、厚膜:thick film61、厚膜电路:thick film circuit62、薄膜:thin film63、薄膜混合电路:thin film hybrid circuit64、互连:interconnection65、导线:conductor trace line66、齐平导线:flush conductor67、传输线:transmission line68、跨交:crossover69、板边插头:edge-board contact70、增强板:stiffener71、基底:substrate72、基板面:real estate73、导线面:conductor side74、元件面:component side75、焊接面:solder side76、印制:printing77、网格:grid78、图形:pattern79、导电图形:conductive pattern80、非导电图形:non-conductive pattern81、字符:legend82、标志:mark二、基材:1、基材:base material2、层压板:laminate3、覆金属箔基材:metal-clad bade material4、覆铜箔层压板:copper-clad laminate (CCL)5、单面覆铜箔层压板:single-sided copper-clad laminate6、双面覆铜箔层压板:double-sided copper-clad laminate7、复合层压板:composite laminate8、薄层压板:thin laminate9、金属芯覆铜箔层压板:metal core copper-clad laminate10、金属基覆铜层压板:metal base copper-clad laminate11、挠性覆铜箔绝缘薄膜:flexible copper-clad dielectric film12、基体材料:basis material13、预浸材料:prepreg14、粘结片:bonding sheet15、预浸粘结片:preimpregnated bonding sheer16、环氧玻璃基板:epoxy glass substrate17、加成法用层压板:laminate for additive process18、预制内层覆箔板:mass lamination panel19、内层芯板:core material20、催化板材:catalyzed board ,coated catalyzed laminate21、涂胶催化层压板:adhesive-coated catalyzed laminate22、涂胶无催层压板:adhesive-coated uncatalyzed laminate23、粘结层:bonding layer24、粘结膜:film adhesive25、涂胶粘剂绝缘薄膜:adhesive coated dielectric film26、无支撑胶粘剂膜:unsupported adhesive film27、覆盖层:cover layer (cover lay)28、增强板材:stiffener material29、铜箔面:copper-clad surface30、去铜箔面:foil removal surface31、层压板面:unclad laminate surface32、基膜面:base film surface33、胶粘剂面:adhesive faec34、原始光洁面:plate finish35、粗面:matt finish36、纵向:length wise direction37、模向:cross wise direction38、剪切板:cut to size panel39、酚醛纸质覆铜箔板:phenolic cellulose paper copper-clad laminates(phenolic/paper CCL)40、环氧纸质覆铜箔板:epoxide cellulose paper copper-clad laminates (epoxy/paper CCL)41、环氧玻璃布基覆铜箔板:epoxide woven glass fabric copper-clad laminates42、环氧玻璃布纸复合覆铜箔板:epoxide cellulose paper core, glass cloth surfaces copper-clad laminates 43、环氧玻璃布玻璃纤维复合覆铜箔板:epoxide non woven/woven glass reinforced copper-clad laminates 44、聚酯玻璃布覆铜箔板:ployester woven glassfabric copper-clad laminates45、聚酰亚胺玻璃布覆铜箔板:polyimide woven glass fabric copper-clad laminates46、双马来酰亚胺三嗪环氧玻璃布覆铜箔板:bismaleimide/triazine/epoxide woven glass fabric copper-clad lamimates47、环氧合成纤维布覆铜箔板:epoxide synthetic fiber fabric copper-clad laminates48、聚四乙烯玻璃纤维覆铜箔板:teflon/fiber glass copper-clad laminates49、超薄型层压板:ultra thin laminate50、陶瓷基覆铜箔板:ceramics base copper-clad laminates51、紫外线阻挡型覆铜箔板:UV blocking copper-clad laminates三、基材的材料1、A阶树脂:A-stage resin2、B阶树脂:B-stage resin3、C阶树脂:C-stage resin4、环氧树脂:epoxy resin5、酚醛树脂:phenolic resin6、聚酯树脂:polyester resin7、聚酰亚胺树脂:polyimide resin8、双马来酰亚胺三嗪树脂:bismaleimide-triazine resin9、丙烯酸树脂:acrylic resin10、三聚氰胺甲醛树脂:melamine formaldehyde resin11、多官能环氧树脂:polyfunctional epoxy resin12、溴化环氧树脂:brominated epoxy resin13、环氧酚醛:epoxy novolac14、氟树脂:fluroresin15、硅树脂:silicone resin16、硅烷:silane17、聚合物:polymer18、无定形聚合物:amorphous polymer19、结晶现象:crystalline polamer20、双晶现象:dimorphism21、共聚物:copolymer22、合成树脂:synthetic23、热固性树脂:thermosetting resin24、热塑性树脂:thermoplastic resin25、感光性树脂:photosensitive resin26、环氧当量:weight per epoxy equivalent (WPE)27、环氧值:epoxy value28、双氰胺:dicyandiamide29、粘结剂:binder30、胶粘剂:adesive31、固化剂:curing agent32、阻燃剂:flame retardant33、遮光剂:opaquer34、增塑剂:plasticizers35、不饱和聚酯:unsatuiated polyester36、聚酯薄膜:polyester37、聚酰亚胺薄膜:polyimide film (PI)38、聚四氟乙烯:polytetrafluoetylene (PTFE)39、聚全氟乙烯丙烯薄膜:perfluorinated ethylene-propylene copolymer film (FEP)40、增强材料:reinforcing material41、玻璃纤维:glass fiber42、E玻璃纤维:E-glass fibre43、D玻璃纤维:D-glass fibre44、S玻璃纤维:S-glass fibre45、玻璃布:glass fabric46、非织布:non-woven fabric47、玻璃纤维垫:glass mats48、纱线:yarn49、单丝:filament50、绞股:strand51、纬纱:weft yarn52、经纱:warp yarn53、但尼尔:denier54、经向:warp-wise55、纬向:weft-wise, filling-wise56、织物经纬密度:thread count57、织物组织:weave structure58、平纹组织:plain structure59、坏布:grey fabric60、稀松织物:woven scrim61、弓纬:bow of weave62、断经:end missing63、缺纬:mis-picks64、纬斜:bias65、折痕:crease66、云织:waviness67、鱼眼:fish eye68、毛圈长:feather length69、厚薄段:mark70、裂缝:split71、捻度:twist of yarn72、浸润剂含量:size content73、浸润剂残留量:size residue74、处理剂含量:finish level75、浸润剂:size76、偶联剂:couplint agent77、处理织物:finished fabric78、聚酰胺纤维:polyarmide fiber79、聚酯纤维非织布:non-woven polyester fabric80、浸渍绝缘纵纸:impregnating insulation paper81、聚芳酰胺纤维纸:aromatic polyamide paper82、断裂长:breaking length83、吸水高度:height of capillary rise84、湿强度保留率:wet strength retention85、白度:whitenness86、陶瓷:ceramics87、导电箔:conductive foil88、铜箔:copper foil89、电解铜箔:electrodeposited copper foil (ED copper foil)90、压延铜箔:rolled copper foil91、退火铜箔:annealed copper foil92、压延退火铜箔:rolled annealed copper foil (RA copper foil)93、薄铜箔:thin copper foil94、涂胶铜箔:adhesive coated foil95、涂胶脂铜箔:resin coated copper foil (RCC)96、复合金属箔:composite metallic material97、载体箔:carrier foil98、殷瓦:invar99、箔(剖面)轮廓:foil profile100、光面:shiny side101、粗糙面:matte side102、处理面:treated side103、防锈处理:stain proofing104、双面处理铜箔:double treated foil四、设计1、原理图:shematic diagram2、逻辑图:logic diagram3、印制线路布设:printed wire layout4、布设总图:master drawing5、可制造性设计:design-for-manufacturability6、计算机辅助设计:computer-aided design.(CAD)7、计算机辅助制造:computer-aided manufacturing.(CAM)8、计算机集成制造:computer integrat manufacturing.(CIM)9、计算机辅助工程:computer-aided engineering.(CAE)10、计算机辅助测试:computer-aided test.(CAT)11、电子设计自动化:electric design automation .(EDA)12、工程设计自动化:engineering design automaton .(EDA2)13、组装设计自动化:assembly aided architectural design. (AAAD)14、计算机辅助制图:computer aided drawing15、计算机控制显示:computer controlled display .(CCD)16、布局:placement17、布线:routing18、布图设计:layout19、重布:rerouting20、模拟:simulation21、逻辑模拟:logic simulation22、电路模拟:circit simulation23、时序模拟:timing simulation24、模块化:modularization25、布线完成率:layout effeciency26、机器描述格式:machine descriptionm format .(MDF)27、机器描述格式数据库:MDF databse28、设计数据库:design database29、设计原点:design origin30、优化(设计):optimization (design)31、供设计优化坐标轴:predominant axis32、表格原点:table origin33、镜像:mirroring34、驱动文件:drive file35、中间文件:intermediate file36、制造文件:manufacturing document.tion37、队列支撑数据库:queue support database38、元件安置:component positioning39、图形显示:graphics dispaly40、比例因子:scaling factor41、扫描填充:scan filling42、矩形填充:rectangle filling43、填充域:region filling44、实体设计:physical design45、逻辑设计:logic design46、逻辑电路:logic circuit47、层次设计:hierarchical design48、自顶向下设计:top-down design49、自底向上设计:bottom-up design50、线网:net51、数字化:digitzing52、设计规则检查:design rule checking53、走(布)线器:router (CAD)54、网络表:net list55、计算机辅助电路分析:computer-aided circuit analysis56、子线网:subnet57、目标函数:objective function58、设计后处理:post design processing (PDP)59、交互式制图设计:interactive drawing design60、费用矩阵:cost metrix61、工程图:engineering drawing62、方块框图:block diagram63、迷宫:moze64、元件密度:component density65、巡回售货员问题:traveling salesman problem66、自由度:degrees freedom67、入度:out going degree68、出度:incoming degree69、曼哈顿距离:manhatton distance70、欧几里德距离:euclidean distance71、网络:network72、阵列:array73、段:segment74、逻辑:logic75、逻辑设计自动化:logic design automation76、分线:separated time77、分层:separated layer78、定顺序:definite sequence五、形状与尺寸:1、导线(通道):conduction (track)2、导线(体)宽度:conductor width3、导线距离:conductor spacing4、导线层:conductor layer5、导线宽度/间距:conductor line/space6、第一导线层:conductor layer No.17、圆形盘:round pad8、方形盘:square pad9、菱形盘:diamond pad10、长方形焊盘:oblong pad11、子弹形盘:bullet pad12、泪滴盘:teardrop pad13、雪人盘:snowman pad14、V形盘:V-shaped pad15、环形盘:annular pad16、非圆形盘:non-circular pad17、隔离盘:isolation pad18、非功能连接盘:monfunctional pad19、偏置连接盘:offset land20、腹(背)裸盘:back-bard land21、盘址:anchoring spaur22、连接盘图形:land pattern23、连接盘网格阵列:land grid array24、孔环:annular ring25、元件孔:component hole26、安装孔:mounting hole27、支撑孔:supported hole28、非支撑孔:unsupported hole29、导通孔:via30、镀通孔:plated through hole (PTH)31、余隙孔:access hole32、盲孔:blind via (hole)33、埋孔:buried via hole34、埋/盲孔:buried /blind via35、任意层内部导通孔:any layer inner via hole (ALIVH)36、全部钻孔:all drilled hole37、定位孔:toaling hole38、无连接盘孔:landless hole39、中间孔:interstitial hole40、无连接盘导通孔:landless via hole41、引导孔:pilot hole42、端接全隙孔:terminal clearomee hole43、准表面间镀覆孔:quasi-interfacing plated-through hole44、准尺寸孔:dimensioned hole45、在连接盘中导通孔:via-in-pad46、孔位:hole location47、孔密度:hole density48、孔图:hole pattern49、钻孔图:drill drawing50、装配图:assembly drawing51、印制板组装图:printed board assembly drawing52、参考基准:datum referan原理图常用库文件:Miscellaneous Devices.ddbDallas Microprocessor.ddbIntel Databooks.ddbProtel DOS Schematic Libraries.ddbPCB元件常用库:Advpcb.ddbGeneral IC.ddbMiscellaneous.ddb分立元件库部分分立元件库元件名称及中英对照AND 与门ANTENNA 天线BATTERY 直流电源BELL 铃,钟BVC 同轴电缆接插件BRIDEG 1 整流桥(二极管)BRIDEG 2 整流桥(集成块) BUFFER 缓冲器BUZZER 蜂鸣器CAP 电容CAPACITOR 电容CAPACITOR POL 有极性电容CAPV AR 可调电容CIRCUIT BREAKER 熔断丝COAX 同轴电缆CON 插口CRYSTAL 晶体整荡器DB 并行插口DIODE 二极管DIODE SCHOTTKY 稳压二极管DIODE V ARACTOR 变容二极管DPY_3-SEG 3段LEDDPY_7-SEG 7段LEDDPY_7-SEG_DP 7段LED(带小数点) ELECTRO 电解电容FUSE 熔断器INDUCTOR 电感INDUCTOR IRON 带铁芯电感INDUCTOR3 可调电感JFET N N沟道场效应管JFET P P沟道场效应管。

protel_dxp 2004 原件英文对照表

protel 元件库中英文对照表(5)CD4553 三位BCD计数器CD4555 双二进制四选一译码器/分离器CD4556 双二进制四选一译码器/分离器CD4558 BCD八段译码器CD4560 "N"BCD加法器CD4561 "9"求补器CD4573 四可编程运算放大器CD4574 四可编程电压比较器CD4575 双可编程运放/比较器CD4583 双施密特触发器CD4584 六施密特触发器CD4585 4位数值比较器CD4599 8位可寻址锁存器CD40110 十进制加/减,计数,锁存,译码驱动STCD40147 10-4线编码器NSC\\MOTCD40160 可预置BCD加计数器NSC\\MOTCD40161 可预置4位二进制加计数器NSC\\MOTCD40162 BCD加法计数器NSC\\MOTCD40163 4位二进制同步计数器NSC\\MOTCD40174 六锁存D型触发器NSC\\TI\\MOTCD40175 四D型触发器NSC\\TI\\MOTCD40181 4位算术逻辑单元/函数发生器CD40182 超前位发生器CD40192 可预置BCD加/减计数器(双时钟) NSC\\TI CD40193 可预置4位二进制加/减计数器NSC\\TICD40194 4位并入/串入-并出/串出移位寄存NSC\\MOT CD40195 4位并入/串入-并出/串出移位寄存NSC\\MOT CD40208 4×4多端口寄存器型号器件名称厂牌备注CD4501 4输入端双与门及2输入端或非门CD4502 可选通三态输出六反相/缓冲器CD4503 六同相三态缓冲器CD4504 六电压转换器CD4506 双二组2输入可扩展或非门CD4508 双4位锁存D型触发器CD4510 可预置BCD码加/减计数器CD4511 BCD锁存,7段译码,驱动器CD4512 八路数据选择器CD4513 BCD锁存,7段译码,驱动器(消隐)CD4514 4位锁存,4线-16线译码器CD4515 4位锁存,4线-16线译码器CD4516 可预置4位二进制加/减计数器CD4517 双64位静态移位寄存器CD4518 双BCD同步加计数器CD4519 四位与或选择器CD4520 双4位二进制同步加计数器CD4521 24级分频器CD4522 可预置BCD同步1/N计数器CD4526 可预置4位二进制同步1/N计数器CD4527 BCD比例乘法器CD4528 双单稳态触发器注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

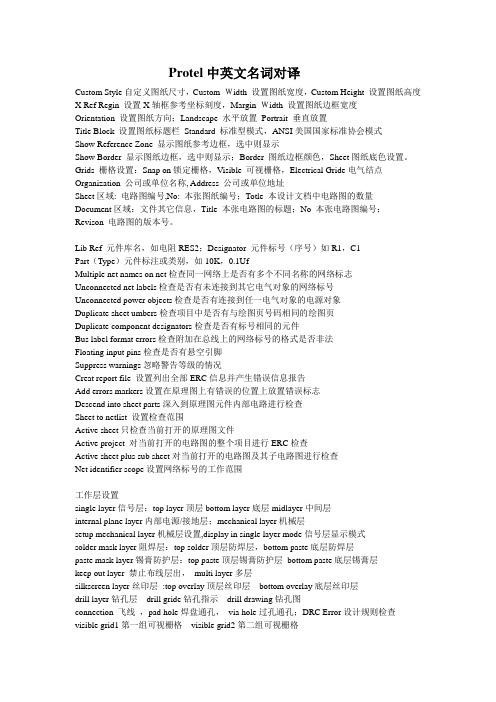

Protel中英文名词对译

Protel中英文名词对译Custom Style自定义图纸尺寸,Custom Width 设置图纸宽度,Custom Height 设置图纸高度X Ref Regin 设置X轴框参考坐标刻度,Margin Width 设置图纸边框宽度Orientation 设置图纸方向;Landscape 水平放置Portrait 垂直放置Title Block 设置图纸标题栏Standard 标准型模式,ANSI美国国家标准协会模式Show Reference Zone 显示图纸参考边框,选中则显示Show Border 显示图纸边框,选中则显示;Border 图纸边框颜色,Sheet图纸底色设置。

Grids 栅格设置:Snap on锁定栅格,Visible 可视栅格,Electrical Gride电气结点Organization 公司或单位名称, Address 公司或单位地址Sheet区域: 电路图编号,No: 本张图纸编号;Totle 本设计文档中电路图的数量Document区域:文件其它信息,Title 本张电路图的标题;No 本张电路图编号;Revison 电路图的版本号。

Lib Ref 元件库名,如电阻RES2;Designator 元件标号(序号)如R1,C1Part(Type)元件标注或类别,如10K,0.1UfMultiple net names on net检查同一网络上是否有多个不同名称的网络标志Unconnected net labels检查是否有未连接到其它电气对象的网络标号Unconnected power objects检查是否有连接到任一电气对象的电源对象Duplicate sheet umbers检查项目中是否有与绘图页号码相同的绘图页Duplicate component designators检查是否有标号相同的元件Bus label format errors检查附加在总线上的网络标号的格式是否非法Floating input pins检查是否有悬空引脚Suppress warnings忽略警告等级的情况Creat report file 设置列出全部ERC信息并产生错误信息报告Add errors markers设置在原理图上有错误的位置上放置错误标志Descend into sheet parts深入到原理图元件内部电路进行检查Sheet to netlist 设置检查范围Active sheet只检查当前打开的原理图文件Active project 对当前打开的电路图的整个项目进行ERC检查Active sheet plus sub sheet对当前打开的电路图及其子电路图进行检查Net identifier scope设置网络标号的工作范围工作层设置single layer信号层:top layer顶层bottom layer底层midlayer中间层internal plane layer内部电源/接地层;mechanical layer机械层setup mechanical layer机械层设置,display in single layer mode信号层显示模式solder mask layer阻焊层:top solder顶层防焊层,bottom paste底层防焊层paste mask layer锡膏防护层:top paste顶层锡膏防护层bottom paste底层锡膏层keep out layer 禁止布线层出,multi layer多层silkscreen layer丝印层:top overlay顶层丝印层bottom overlay底层丝印层drill layer钻孔层drill gride钻孔指示drill drawing钻孔图connection 飞线,pad hole焊盘通孔,via hole过孔通孔;DRC Error设计规则检查visible grid1第一组可视栅格visible grid2第二组可视栅格layer stack manager工作层堆栈管理器add layer添加层midlayer中间层add plane 增加一个内部电源接地层copper thickness覆铜厚度snap x ,snap y性XY方向的捕获栅格间component x ,component y元件XY方向移动间距range范围,Electrical Grid电气栅格Lines线状Dots点状Metric公制Imperial 英制设置PCB工作参数option 特殊功能display显示状态color工作层面颜色show/hide 显示/隐藏default 默认online DRC在线DRC检查snap tocenter光标移到参考点extend selection连续选取多个对象remove duplicate 自动删除重复对象confirm global edit确认整体编辑出现对话框protect locked object保护锁定对象autopan options自动移边style 功能模式disable关闭自动移边re- center以光标位置为新的编辑区中心adaptive 自适应模式ballistic非定速自动移边fixed size jump以设定值为移动量向未显示部分移动shift accelerate加快移边速度shift decelerate减慢移边速度speed 移动速率mils/sec移动速率单位pixels/sec另一个移动速率单位polygon repour多边形填充的绕过never是否重建多边形填充threshold绕过的临界值always直接重建多边形区域interactive routing 交互式布线的参数设置ignore obstacle忽略障碍直接覆盖avoid obstacle绕开障碍push obstacle 推开障碍plow through polygons多边形填检测布线障碍automatically remove loops自动删除形成回路的走线component drag元件拖动模式none只拖动元件本身connected track元件的走线也跟着拖动rotation step旋转角度undo/redo撤销重复命令次数cursor type 光标形状convert special string特殊字符串转化为代表的文字highlight in full设置高亮度的状态use net color for highlight以该网络所设置的颜色来显示redraw layer重画电路板时系统将一层一层重画single layer mode只显示当前编辑的板层transparent layer所有层的内容和被覆盖的对象都会显示出来pad nets 焊盘的网络名称pad number焊盘序号via nets 过孔的网络名称test point测试点origin marker原点status info 状态信息final精细draft 简易hidden不显示arc圆弧component元件封装coordinate坐标dimension尺寸fill金属填充pad焊点polygon多边形敷铜string字符串track铜膜导线via 过孔selection选取对象background背景default color默认颜色classic color 传统颜色。

Protel DXP集成元件库分类 中英文对照

555系列

TI Converter Digital to Analog.IntLib

D/A转换器

TI Converter Analog to Digital.IntLib

A/D转换器

TI Logic Decoder Demux.IntLib

电源LM系列

National Semiconductor

NSC Audio Power Amplifier.IntLib

LM38、48系列

NSC Analog Timer Circuit.IntLib

LM555

NSC Analog Timer Circuit.IntLib

三极管

NSC Discrete Diode.IntLib

TL、LM38系列

STPower Mgt Voltage Regulator.IntLib

电源块子78、LM317系列

Teccor Electronics

Teccor Discrete TRIAC.IntLib

双向可控硅

Teccor Discrete SCR.IntLib

可控硅

Texas Instruments

40系列

FSC Logic Latch.IntLib

4LS系列

C-MAC MicroTechnology(Rakon公司【专业生产晶振】)

C-MAC MicroTechnology

晶振

Dallas Semiconductor

DallasMicrocontroller 8-Bit.IntLib

存储器

International Rectifier

1N系列稳压管

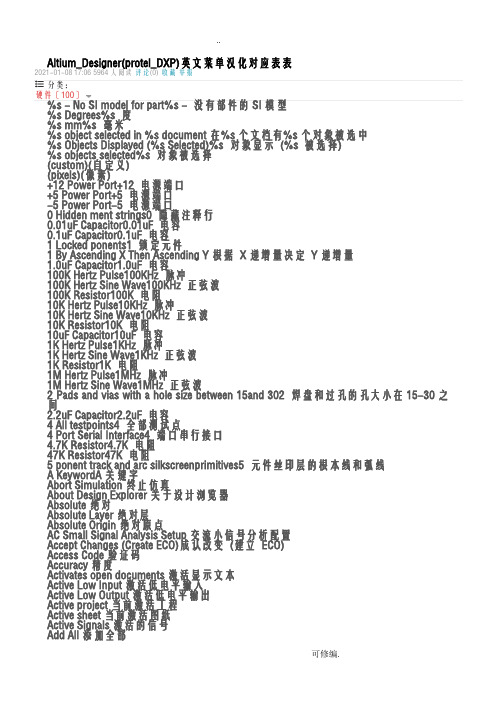

altium窗口菜单中英文对照表

- ..Altium_Designer(protel_DXP)英文菜单汉化对应表表2021-01-08 17:065964人阅读评论(0)收藏举报分类:硬件〔100〕%s - No SI model for part%s - 没有部件的SI模型%s Degrees%s 度%s mm%s 毫米%s object selected in %s document在%s个文档有%s个对象被选中%s Objects Displayed (%s Selected)%s 对象显示(%s 被选择)%s objects selected%s 对象被选择(custom)(自定义)(pixels)(像素)+12 Power Port+12 电源端口+5 Power Port+5 电源端口-5 Power Port-5 电源端口0 Hidden ment strings0 隐藏注释行0.01uF Capacitor0.01uF 电容0.1uF Capacitor0.1uF 电容1 Locked ponents1 锁定元件1 By Ascending X Then Ascending Y根据X递增量决定Y递增量1.0uF Capacitor1.0uF 电容100K Hertz Pulse100KHz 脉冲100K Hertz Sine Wave100KHz 正弦波100K Resistor100K 电阻10K Hertz Pulse10KHz 脉冲10K Hertz Sine Wave10KHz 正弦波10K Resistor10K 电阻10uF Capacitor10uF 电容1K Hertz Pulse1KHz 脉冲1K Hertz Sine Wave1KHz 正弦波1K Resistor1K 电阻1M Hertz Pulse1MHz 脉冲1M Hertz Sine Wave1MHz 正弦波2 Pads and vias with a hole size between 15and 302 焊盘和过孔的孔大小在15-30之间2.2uF Capacitor2.2uF 电容4 All testpoints4 全部测试点4 Port Serial Interface4 端口串行接口4.7K Resistor4.7K 电阻47K Resistor47K 电阻5 ponent track and arc silkscreenprimitives5 元件丝印层的根本线和弧线A KeywordA关键字Abort Simulation终止仿真About Design Explorer关于设计浏览器Absolute绝对Absolute Layer绝对层Absolute Origin绝对原点AC Small Signal Analysis Setup交流小信号分析配置Accept Changes (Create ECO)成认改变(建立ECO)Access Code验证码Accuracy精度Activates open documents激活显示文本Active Low Input激活低电平输入Active Low Output激活低电平输出Active project当前激活工程Active sheet当前激活图纸Active Signals激活的信号Add All添加全部- ..Add All Waveforms添加全部波形Add as Rule作为规那么添加Add Assembly Outputs增加装配输出Add Class添加分类Add ponent Part添加元件部件Add Document增加文本Add Document to Focused Project添加文档到当前工程Add Documentation Outputs增加文本输出Add Existing Project添加已存在的工程Add Fabrication Outputs增加生产输出Add first condition添加首要条件Add From To添加From ToAdd Internal Plane增加电层Add Layer添加层Add Library添加库Add License添加许可证Add Net添加网络Add Net Class添加网络分类Add Netlist Outputs增加网表输出Add New Cursor增加标Add New Model添加新模式Add New Project添加新工程Add One添加一个Add or Remove Libraries添加或移出库文件Add Other Outputs添加其他输出Add Plane添加电层Add Plot增加图表Add Project To Version Control将工程添加到版本控制Add Remove ponent Libraries添加移出元件库Add Remove Libraries添加/移出库文件Add Reports增加报告Add Selected添加选择的Add Selected Primitives to ponent添加所选根本元素到元件Add Sheet Entry添加图纸入口Add Signal Layer增加信号层Add Suffix加后缀Add Template to Clipboard添加模板到剪贴板Add To Current Sheet添加到当前图纸Add to Custom Colors添加到自定义颜色Add To Design添加到设计Add To Entire Project添加到整个工程Add to new Y axis增加到新Y轴Add to Project添加到工程Add To Sheet添加到图纸Add To Version Control添加到版本控制Add top level signals to waveform给波形增加顶层信号Add Variant添加变量Add Watch增加监视Add Wave增加波形Add Wave To Plot给图表增加波形Add Waveform增加波形Add waveforms to the new plot给新图表增加波形Add Y Axis增加Y 轴Add/Edit Model增加/编辑模型Add/Remove Libraries装载/移出库文件Add/Remove Library装载/移出库AddAlias添加别名Advanced (Query)高级(查询)Advanced Mode高级模式Affected Document所影响的文本- ..Affected Object所影响的对象Aggregate合计Align Bottom底部对齐Align ponents对齐元件Align ponents by Bottom Edges根据元件下缘对齐Align ponents by Horizontal Centers元件居中对齐Align ponents by Left Edges元件左边对齐Align ponents by Right Edges元件右边对齐Align ponents by Top Edges元件对齐顶部边缘Align ponents by Vertical Centers根据垂直中心对其元件Align Left左对齐Align Right右对齐Align Top顶部对齐Aligned - Bottom对齐- 底部Aligned - Center对齐- 中心Aligned - Inside Left对齐- 部左边Aligned - Inside Right对齐- 部右边Aligned - Left对齐- 左边Aligned - Right对齐- 右边Aligned - Top对齐- 顶部all全部All ponents全部元件All Draft全部草图All Final全部最终All Hidden全部隐藏All Locked全部锁定All Nets全部网络All Off全部关闭All On全部翻开All On Current Document全部当前文档All on Layer全部翻开层All open schematic documents所有翻开原理图文档All Orientations所有方向All schematic documents in the currentproject当前工程中所有原理图文档All Text Docs全部文本文件Allow Dock允许停放Allow multiple testpoints on same net允许同一网络多个测试点Allow Ports to Name Nets允许端口到网络名Allow Sheet Entries to Name Nets允许图纸入口到网络名Allow Short Circuit允许电路短路Allow Synchronization With Database允许和数据库同步Allow Synchronization With Library允许和库同步Allow testpoint under ponent元件下允许测试点Allow Vias under SMD PadsSMD焊盘下允许过孔Allowed Orientations允许方向Allowed Side and Order允许边和定制Alpha字母Alpha Numeric字母数字Alpha Numeric Suffix字母数字下标Alphabetically字母顺序Alternate 1另一选择1Alternative其他选择Always load error file总是加载错误文件Amplitude振幅Analog模拟Analog +12V (+12V)模拟+12V (+12V)Analog +5V (+5V)模拟+5V (+5V)Analog Ground (AGND)模拟地(AGND)Analog Routing 1模拟布线层1Analog Routing 2模拟布线层2- ..Analog Routing 3模拟布线层3Analog Signal In模拟信号输入Analyse分析Analyses Setup分析配置Analyses/Options分析/选项Analysis分析Analysis Errors分析错误Analyze Design分析设计Analyze Document分析文档And Gate与门And to wrap long lines增加到可交换长行Angular角形Angular Dimension角度Angular Step角幅Animation speed动画速度Annotate标注Annotation注释Anode正极ANSIANSIAny任何Aperture File (using Wizard formats)光圈文件(利用向导格式) Aperture Library光圈库Aperture List光圈列表Aperture Matching TolerancesD码表匹配公差Append Sheet Numbers to Local Nets附加图纸编号到本地网络Applicable Binary Rules适用的二元规那么Applicable Rules适用的规那么Applicable Unary Rules适用的一元规那么Apply Filter应用过滤器Apply to Active Chart Only仅适用于激活图表Apply to Entire Document适用于整个文本Arc弧线Arc (Any Angle)弧形(任何角度)Arc (Center)弧形(定中心)Arc (Edge)弧形(边限)Arc Line Width弧线宽度Arc Radius圆弧半径Architecture构造Archive project document存档工程文件Arcs弧形Arithmetic算法Around Point附近的点Arrange All Windows Horizontally水平排列所有窗口Arrange All Windows Vertically垂直排列所有窗口Arrange ponents Inside Area在区域排列元件Arrange ponents Within Room在布局空间排列元件Arrange Outside Board在底边界外排列Arrange Within Rectangle在矩形里排列Arrange Within Room在布局空间里排列Arrow Length箭头长度Arrow Line Width箭头线宽度Arrow Position箭头位置Arrow Size箭头大小Arrow Style Power Port发射型电源端口Arrow Width箭头宽度Articles and Tutorials文章和教程Assembly %s装配%sAssembly Drawings装配制图Assembly Outputs装配输出At Margin在页边距- ..At Window在窗口Attributes on Layer层上属性Auto Create posite自动创立合成Auto indent mode自动缩进模式Auto Pan Fixed Jump自动平移固定围Auto Pan Off自动平移关闭Auto Pan Options自动平移选项Auto Pan ReCenter自动平移至中心Auto Placement自动布局Auto Placer自动放置Auto Route自动布线Auto save every自动保存间隔Auto Zoom自动缩放Auto-Increment During Placement在布局时自动增加Auto-Junction自动加节点Auto-Position Sheet自动定位图纸Automatic (Based on project contents)自动〔基于工程容〕Automatically crossprobe first error自动穿插检索第一个错误Automatically Remove Loops自动去除回路Autopan Options自动位移选项Autoposition自动定位Autosave desktop自动保存桌面设置Available Libraries当前库Available Routing Strategies可用的布线策略Available Signals可用的信号Average Track Length (mil)平均铜线长度〔mil〕Avg平均Avoid Obstacle避开障碍物Back Annotate反向标注Background背景Backspace unindents回车取消缩进Backup Files备份文件Backup Options备份选项Ball Grid Arrays (BGA)BGABallistic可变速度移动Bank1组列1Bank2组列2Bar Style Power Port条型电源端口Bar to use as Main Menu栏作为主菜单使用Bar Type栏类型Bars栏Base Value低电平Baseline基线Baseline Dimension基线尺度Basic DC根本直流Batch批处理Batch Mode批命令模式Begin Group开场分组Below is a list of all the processesprovided by this server以以下表是此效劳提供的所有处理模块Beta DegBeta降级Bezier曲线BGA OptionsBGA 选项Bidirectional Signal Flow双向信号流向Bill of Materials材料清单Bill of Materials (By PartType) For Project[%]工程[%s]物料清单(元件类型)Bill of Materials For PCB%sPCB %s材料清单Bill of Materials For Project %s工程材料清单%sBitmap File位图文件Blank Project (Embedded)空白工程(嵌入式)- ..Blank Project (FPGA)空白工程(FPGA)Blank Project (Library Package)空白工程(库包) Blank Project (PCB)空白工程(PCB)Block Indent块缩进Block Name块名称Block Name : %s块名称: %sBoard板Board Area Color板区域颜色Board Dimensions板尺寸Board in 3D3D 板视图Board Information板信息Board La&yers & Colors板层和颜色Board La&yers && Colors板层和颜色Board Layers Colors板层颜色Board Layers & Colors板层和颜色Board Layers and Colors板层和颜色Board Line Color板层线颜色Board Options板选项Board Shape板形Board Specifications板技术参数Bold Waveforms实线波形BOOLEAN布尔数学体系Border (Auto-Detect)边界(自动探测)Border Color边框颜色Border On边框显示Border Width边框宽度Bottom底层Bottom Dielectric底部绝缘层Bottom Layer底层Bottom Layer Annular Ring Size底层圆环尺寸Bottom Overlay底层丝印层Bottom Paste底层焊锡层Bottom Solder底层阻焊层Bottom Solder Mask底层阻焊层BottomLayer底层BottomOverlay底层丝印层Brackets支架Break All ponent Unions从单元中别离出所有元件Break ponent from Union从单元中别离出元件Break Track断开轨迹Breakpoints断点Brightness亮度Bring To Front Of带到某对象前面Browse浏览Browse ponent Libraries浏览元件库Browse ponents浏览元件Browse Libraries浏览库Browse Library浏览库文件Bubble Help Advisor (Shift+F1)浮动帮助参谋(Shift+F1) Build posite构造合成Build Later后来再建Build PCB Project构造PCB 工程Build Project构造工程Build Query构造智能语句Build Sooner立即创立Build-Up绝缘层对Building Query from Board从板构造查询Bus总线Bus Entry总线入口Bus indices out of range总线超出围- ..Bus range syntax errors总线围语法错误Bus Width总线线宽By class通过类By document type通过文本类型C MenuC 菜单C StandardC 标准Calc. Copper Area计算.铜面积Calculated Impedance =计算阻抗=Calculated Trace Width =计算线宽=CAM DocumentCAM 文档CAM EditorCAM 编辑器Cannot Locate Document %s无法找到%s文档信息Capacitance电容Capacitor电容Capacitors电容Categories类别Cathode负极Center Dimension中心点尺度Center Horizontal水平居中Center of Object对象中心Center Vertical垂直居中Change Language更换语言Change Order改变顺序Change System Font改变系统字体Change Technology改变封装技术Channel Offset通道偏移Characteristic Impedance Driven Width特性阻抗驱动线宽Chart制图Chart name is blank图表名称为空Chart Options图表选项Check All ponents检查所有元件Check In签入Check Mode校验模式Check Out签出Check Syntax校验语法Choose a snap grid size选择捕获网格尺寸Choose Color选择颜色Choose cursor to delete选择要光标删除Choose cursor to jump to选择要跳转到的光标Choose Default Backup Folder选择缺省的备份文件夹Choose Default Document Folder选择缺省文档文件夹Choose Design Rule Type选择设计规那么类型Choose Document选择文档Choose Document Scope选择文档围Choose Document to Open选择要翻开的文档Choose Document to Place选择文档放置Choose Documents选择文档Choose Documents to Add to Project %s选择文档加到工程%sChoose Documents To pare选择比拟文档Choose documents to pare - one from theleft list and one from the right list选择比拟文档- 一个从左面列表另一个从右面列表选择Choose Project选择工程Choose Project Group to Open选择要翻开的工程组Choose Project to Open选择要翻开的工程Choose second corner选择第二角Choose the document to pare against thedesign hierarchy of %s选择与设计层次%s进展比拟的文本Choose the document to pare against thedesign hierarchy of Documents.PRJPCB选择与工程文本的层次设计进展比拟的文本Choose Top Level选择顶层- ..Choose WAS-IS File for Back-Annotation fromPCB从PCB选择WAS-IS文件作为反向注释Circle Style Power Port循环型电源端口Circuit电路Circuit Simulation电路仿真CKTCKTClamping箝位Class I分类IClass II分类IIClass Type类型Classes分类Classic Color Set典型颜色设置Clean All Nets去除全部网络Clean Single Nets去除单一网络Clear All Nets去除全部网络Clear All Test points去除全部检测点Clear All Testpoints去除全部测试点Clear Browser Marks去除浏览器标记Clear Class去除类别Clear Current Filter去除当前过滤器Clear Current Filter (Shift+C)去除当前过滤器(Shift+C)Clear Existing去除已存在Clear Filter去除过滤器Clear History去除历史Clear Memory去除存储器Clear non-numerical values去除非数字的值Clear Selected去除已选Clear Status去除状态Clear workspace pile messages onpile编译时去除工作空间编译信息Clearance间距Click Clears Selection单击去除选择Click on the finish button to plete thetask在完毕按钮上点击完成任务Client客户端Client License Usage客户端许可证用法Client Setup客户端设置Clip to Area显示框文本Clipboard Reference剪贴板属性clock时钟Close 'pile Errors'关闭‘编译错误’面板Close 'piled Object Debugger'关闭‘编译对象调试器’面板Close 'Differences'关闭‘差异’面板Close 'Files'关闭‘文件’面板Close 'Help Advisor'关闭‘帮助参谋’面板Close 'Inspector'关闭'检视器'Close 'Libraries'关闭'库'Close 'List'关闭'列表'Close 'Messages'关闭‘消息’面板Close 'navigator'关闭‘浏览器’面板Close 'Projects'关闭‘工程’面板Close All Documents关闭全部文件Close posite关闭合成Close Documents关闭文档Close Focused Project关闭当前工程Close Project关闭工程Close Project Documents关闭工程文档Collapse Row折叠行Collect Data For数据收集类型Collector集电极Color Options颜色选项Color Set颜色设置- ..Colors && Gray Scales色彩/灰度级Colours颜色Column Best Fit适应列宽mand Reference命令参考mand Status命令状态栏ment type注释类型p Drag拖动比拟parator比拟器parison Type Description比拟类型描述pile Active Document编译当前文档pile Active Project编译当前工程pile All编译全部pile All Open Projects编译全部已翻开的工程pile All Projects编译所有工程pile Current Project编译当前工程pile Document编译文档pile Errors编译错误pile FPGA Project编译FPGA 工程pile Later后来再编译pile Library编译库pile only if modified仅编译修改之后pile PCB Project编译PCB 工程pile Project编译工程pile Sooner立即编译piled编译piled Object Debugger编译对象调试器piler Options编译选项piling %s正在编译%spiling Flattened Project编译平行工程plex Data复杂数据ponent元件ponent %s元件%sponent Actions元件操作ponent Class Generator元件分类发生器ponent Classes元件分类ponent ment元件注释ponent Connections元件连接ponent Cross Reference元件互相参照ponent Cross Reference Report ForProject %s工程元件穿插参考报告%s ponent Designator%s元件标识符%sponent Grid元件网格ponent Links元件ponent Name部件名ponent Names元件名称ponent Naming元件命名ponent Nets元件网络ponent Parameter元件参数ponent Pin Designator元件引脚标识符ponent Pin Editor元件引脚编辑器ponent Pins元件引脚ponent Placement元件布局ponent Primitives元件根本元素ponent Properties元件属性ponent Report元件报告ponent Rule Check元件规那么检查ponent scope for filtering andselection过滤及选择元件的围ponent Side元件层ponent Type元件类型ponent Types元件类型ponent Wizard元件向导- ..ponent Wizard - Pin Grid Arrays (PGA)元件向导- PGAponents元件ponents Cut Wires元件切线posite Drill Guide合成钻孔向导posite Layers合并层posite Properties合成特性Condition Type / Operator类型/操作状态Condition Value条件值Conductor Width导体宽度Conductors导体Configure Drill Pairs配置钻孔层对Configure Licenses配置软件许可证Configure PLD piler配置PLD编译Configure Project Options for ActiveProject为当前工程配置工程选项Confirm Delete Parameter确认删除参数Confirm Global Edit确定全局编辑Confirm Remove %s确认删除%sConfirm remove the layer %s确认是删除层%sConfirm Selection Memory Clear选择存储器去除时确认Connect Layer连接层Connect Style连接样式Connect To连接到Connect to Net连接到网络Connect Wire Check接线检查Connect Wire Extractor接线数据Connected Copper连接铜线Connected Tracks连接铜线Connection Color连接颜色Connection Matrix连接矩阵Connector连接器Connector Type连接器类型Constant Level常数等级Constraints约束限制Contract All全部压缩Convert Part To Sheet Symbol转换元件为图纸符号Convert Selected Free Pads to Vias将所选自由焊盘转换为过孔Convert Selected Vias to Free Pads将所选过孔转换为自由焊盘Convert Special Strings转换特殊字符串Convert to DXP Plane Mode转换为DXP电层模式Coordinate坐标Coordinate Positions坐标位置Copper thickness铜厚度Copy (Ctrl+C)复制(Ctrl+C)Copy ponent复制元件Copy Footprint From/To复制封装从/到Copy on Field复制域Copy preexisting edif models whenavailable当可访问到时拷贝已经存在的EDIF模型Copy Room Formats复制布局空间格式Copy to Layers复制到层Copyright ?Altium Limited 2002 Altium 所有2002Core (%s)核心(%s)Corner角Corner 1角1Corner 2角2Corrections校正Coupling耦合Create a new Board Level Design Project创立新的板级设计工程Create a new FPGA Design Project创立新的FPGA设计工程Create a new Integrated Library Package创立新的集成库包Create backup files创立备份文件- ..Create piled SimCode output file创立编译SimCode输出文件Create ponent创立元件Create Engineering Change Order创立工程改变顺序(ECO)Create Expression创立表达式Create FFT Chart新建FFT图表Create Library创立库Create List From PCB从PCB建表Create Netlist From Connected Copper从连接的铜板创立网表Create New Chart新建图表Create New Database新建数据库Create Non-Orthoganal Room from selectedponents根据所选元件创立非正交布局空间Create Non-Orthogonal Room from ponents根据元件创立非正交布局空间Create Orthogonal Room from ponents根据元件创立正交布局空间Create Orthogonal Room from selectedponents根据所选元件创立正交布局空间Create Pairs From Layer Stack从层堆栈中创立层对Create Pairs From Used Vias从所用过孔中创立层对Create Projects from Path从指定路径创立工程Create Rectangle Room from selectedponents根据所选元件创立矩形布局空间Create Rectangular Room from ponents根据元件创立矩形布局空间Create Report建立报告Create Report File创立报告文件Create Rule创立规那么Create Sheet From Symbol从符号创立图纸Create Symbol From Sheet从图纸创立符号Create Union from ponents从元件创立单元Create Union from Selected ponents根据所选元件创立单元Create VHDL File From Symbol从符号创立VHDL 文件Create VHDL from FPGA-Part从FPGA 零件创立VHDLCreate VHDL Testbench创立VHDL 测试平台Create Violations创立违规信息Cross Probe插入探针Cross Probe to Documents文档中插入探针Cross Probe to Schematic穿插检索到原理图Crossing Window穿插窗口Crossprobe schematic穿插检索原理图Crosstalk串扰Crosstalk Analysis串扰分析Crosstalk Waveforms串扰分析CTRL+Double Click Opens SheetCTRL+双击翻开图纸Current ponent当前元件Current Document当前文档Current Font当前字体Current Layer当前层Current Origin当前原点Current Page当前页Cursor A光标ACursor B光标BCursor beyond EOFEOF的光标Cursor beyond EOLEOL的光标Cursor Grid Options指针网格选项Cursor through tabs通过Tab移动光标Cursor Type光标类型Curve Width曲线宽度Custom Aperture Library File (*.LIB)自定义光圈库文件(*.LIB)Custom Height自定义高Custom Size自定义大小Custom Step定制调试Custom Style自定义风格Custom Width自定义宽- ..Customize Resources自定义资源Customizing DefaultEditor Editor用户缺省自定义编辑器Customizing PCB Editor自定义PCB 编辑器Customizing PCBLib Editor自定义PCBLib编辑器Customizing Sch Editor自定义原理图编辑器Customizing SchLib Editor定制原理图库编辑器Customizing VHDL Editor自定义VHDL编辑器Cut (Ctrl+X)剪切(Ctrl+X)Cutout挖除局部Darken调暗Data Process接线数据处理Database Connection数据库连接Database key field数据库关键字段Database Link File数据库文件Database Link Options数据库选项Database Linking数据库Database Linking Menu数据库菜单Database Links数据库DatabaseLink数据库Datasheet数据表Datum数据Datum Dimension数据尺度DC AnalysisDC分析DC Sweep Analysis Setup直流扫描分析配置Debugging Options调试选项Decision判定Declare ponent At Cursor在指针指向元件显示说明Decrease减少Decrease Horizontal Spacing of ponents减小元件水平间距Decrease Priority降低优先级Decrease Vertical Spacing of ponents减小元件的垂直间距default默认Default Background默认背景Default Bars缺省面板Default Color Set默认颜色设置Default Designator缺省名称Default File Name缺省文件名Default Locations默认位置Default Power Object Names默认电源对象名称Default Primitives默认根本元素Default Prints默认打印Default Shortcuts默认快捷方式Default Stimulus默认鼓励Default Template Name缺省模板名Default time units默认时间单位Default Value默认值Default Vendor Family默认厂家芯片系列DefaultEditor默认编辑DefaultRowHeight默认行高Define from selected objects从所选对象定义Define the layout of the PGA footprint byselecting the proper values选择适当的值定义PGA封装引脚布局degrees度数Delete All全部删除Delete All Cursors删除全部光标Delete All Waveforms删除全部波形Delete Chart删除图表Delete Class删除分类Delete Current Cursor删除当前光标Delete Cursor删除光标- ..Delete generated files before pile编译之前删除生成的文件Delete Net删除网络Delete Net Class删除网络分类Delete Plot删除坐标图Delete Watch删除监视Delete Waveform删除波形Delta Step增量调试Demote降级Density Map密度图Deselect All取消全部选择DeSelect All On Current Document取消选择当前的全部文档Design设计Design Documents设计文本Design Explorer DXP DXP 设计浏览器Design Explorer DXP - %s设计浏览器DXP - %sDesign Explorer Error设计浏览器错误Design Explorer Information设计浏览器信息Design Explorer Preferences设计浏览器属性Design Explorer Project Manager设计浏览器工程管理器Design Explorer Version 7.1.70设计浏览器版本7.1.70 Design Explorer Version 7.2.92设计浏览器版本7.2.92 Design Explorer Warning设计浏览器告警Design Rule Check设计规那么检查Design Rule Checker设计规那么检查Design Rules设计规那么Designator标识符Designator Display标识符显示Designator Format标识符格式Designator Index Control标识符指针控制Designators标识符Destination Library目标库Device Family器件系列Dielectric constant绝缘材料常数Dielectric Properties绝缘体属性Differences差异Different不同Digital Ground (GND)数字地层(GND)Digital Objects数字对象Digital Power (VCC)数字电源层(VCC)Digital Routing 1数字布线层1Digital Routing 2数字布线层2Digital Routing 3数字布线层3Digital Routing 4数字布线层4Digital Routing 5数字布线层5Digital Routing 6数字布线层6Digital Signal In数字信号输入Digital supply VCC数字电源VCCDigital Supply VDD数字电源VDDDimension标注线Dimensions标注线Diode二极管Diodes二极管Direction From Pad出焊盘方向Directive Options提示选项Directives指令Disable不激活Disable All全部禁用Disable All Watches禁用全部监视Disable dragging取消拖动Disable Update All取消修改全部- ..Disable Update Selected取消修改选择的Disable Watch禁用监视Display Cross Sheet Connectors显示图纸间连接符Display FFT Charts显示FFT图表Display Full Hierarchy显示全部层次Display Graphical Lines显示图形线条Display Logical Designators显示逻辑标识符Display Mode显示模式Display Name显示名称Display Net Labels显示网络标志Display No Hierarchy显示没有层次图Display Options显示选项Display Physical Designators显示物理标识符Display Pins显示引脚Display Ports显示端口Display Printer Fonts显示打印字体Display Report显示报告Display shadows around menus, toolbars andpanels显示菜单, 工具栏, 面板的阴影Display Sheet显示图纸Display Sheet Entries显示图纸入口Display Sheet Symbols显示图纸符号Display Symbols显示符号Display System Information显示系统信息Distance factor距离因素Distribute Horizontally水平居中分布Distribute Vertically垂直居中分布Division Size分割尺度Do not group不分组Do you wish to delete the Parameter你希望删除这个参数Documen文本Document Editors文档编辑器Document Name文档名称Document Options文档选项Document Order文档顺序Document Parameters文本参数Document Path文档路径Document scope for filtering and selection过滤选择文档围Documentation %s文本%sDocumentation Output文本输出Documents for %s%s 文档Documents for Free Documents文档为自由文档Does nothing无任何操作Don't Annotate ponent不注释元件Don't care不关注dot点Dot Grid网格点Dotted点Double click line双击行Double Click Runs Inspector鼠标双击那么运行检视器Double Sided双面Draft Thresholds草图起点Drag拖动Drag a column header here to group by thatcolumn拖动一列标头到这列用于分组Drag Orthogonal直角拖动Drag Selection拖动选择容Drag Track End拖动轨迹末端Draw Solid画实线Draw to Custom Aperture自定义光圈绘图Drawing制图Drawing Tools制图工具- ..DRC Error MarkersDRC 错误标记DRC Report OptionsDRC报告选项DRC ViolationsDRC违规数Drill钻孔机Drill Drawing钻孔图Drill Drawing Plots钻孔绘制图Drill Drawing Symbols钻孔绘制符号Drill Drawings钻孔图Drill Guide钻孔向导Drill Guide Plots钻孔导向图Drill Pair Properties钻孔层对属性Drill Pairs钻孔配对层Drill-Pair Manager钻孔层对管理器Drill-Pair Properties钻孔对属性DrillDrawing钻孔图DrillGuide钻孔向导Dual in-line Package (DIP)DIPDuplicate Selected复制被选DXP Help AdvisorDXP 帮助指导DXP Knowledge BaseDXP 知识库DXP Learning GuidesDXP 学习指南DXP Online helpDXP 在线帮助Dynamic动态Dynamic transparency动态透明效果Earth接地Earth Power Port接地电源端口ECO GenerationECO 启动EDA ServersEDA 效劳Edge Connectors边缘连接器EDIF MacroEDIF宏EDIF MenuEDIF 菜单EDIF StandardEDIF 标准Edit Buffer编辑缓冲Edit mand编辑命令Edit ment编辑注释Edit Full Pad Layer Definition编辑完整的焊盘层Edit Keyword Properties编辑关键字属性Edit Language Syntax编辑语言语法Edit Layer编辑层Edit Library编辑库Edit Net编辑网络Edit Net Class编辑网络分类Edit Nets编辑网络Edit Number编辑编号Edit Pins编辑引脚Edit Polygonal Room Vertices编辑多边形空间的顶点Edit Rule Priorities编辑规那么优先级Edit Rule Values编辑规那么数值Edit Selected编辑被选Edit Simulation Signals编辑仿真信号Edit String编辑字符串Edit Style编辑风格Edit Values编辑值Edit Variant编辑变量Edit Wave编辑波形Editing Options编辑选项Editor Preferences参数选择编辑器EditScript编辑脚本Eight Layer (5 x Signal, 3 x Plane)八层〔5信号层,3电层〕Elaborate and generate on pile编译时详细阐述和产生- ..Electrical Grid电子网格Electrical Type电气类型Ellipse椭圆形Elliptical Arc椭圆的弧线Embedded嵌入Embedded apertures (RS274X)嵌光圈表[RS274X]Embedded Project嵌入式工程Embedded Projects嵌入式工程Emitter发射极Enable All全部启用Enable All Watches启用全部监视Enable Font Substitution允许字型替换Enable In-Place Editing启用位置编辑Enable Update All使能修改全部Enable Update Selected使能修改选择的Enable Version Control允许版本控制Enable Watch启用监视Enabled激活End Angle完毕角度End Layer完毕层Enforce layer pairs settings执行层对设置Engineering Change Order工程改变单Entity/Configuration实体/配置Equalize Net Lengths补偿网络长度Error Marker错误标记Error Reporting错误报告Errors Detected监测到错误Errors or warnings found发现错误或告警Esc取消Example Layer Stacks层堆栈举例Examples例Excel Template FilenameExcel 模板文件名Exclude IEEE Directory不包括IEEE目录Exclude System Parameters拒绝系统参数Execute Changes执行改变Expand Row扩展行Expansion扩展Expansion value from rules从规那么扩展值Expiry Date有效期限Explode拆解Explode ponent to Free Primitives将元件拆解为自由的根本元素Explode posite拆解合成Explode Coordinate to Free Primitives将坐标拆解为自由的根本元素Explode Dimension to Free Primitives将尺度标注拆解为自由的根本元素Explode Polygon to Free Primitives将多边形敷铜拆解为自由的根本元素Explore浏览Explore Differences探测差异ExplorerFramePanel管理器框架面板Exponential/Logarithmic指数/对数Export Grid Contents导出容Export Netlist From PCB从PCB 导出网表Export Selected Waveforms导出选择的波形Export to PCB导出到PCBExport Using Template导出使用模板Expression表达式Extension Width延伸宽度Fabrication %s生产%sFabrication Outputs生产输出Falling Edge Flight Time下降沿延迟时间Falling Edge Overshoot下降沿过冲- ..Falling Edge Slope下降沿斜率Falling Edge Undershoot下降沿下冲False错误Fanout扇出Fanout DirectionFanout 方向Fanout OptionsFanout 选项Fanout StyleFanout 风格faster快Fatal Error严重错误File Mask文件过滤Files Found on All Search Paths在全部路径上查找到的文件Fill Color填充颜色Fills填充Film Box胶片盒Film Size胶片尺寸Film Wizard胶片向导Filter过滤Filter browsed objects过滤浏览对象Filter For过滤Filtered Objects过滤对象Final最终Final Properties最终属性Find and Replace Text查找并替换文本Find and Set Testpoints选择和设置测试点Find ponent查找部件Find Coupled Nets发现耦合网络Find Selections查找选择容Find Similar Objects找出相似对象Find text at cursor光标位置查找文本First ponent第一个元件First Layer首层First Page首页First Transition首次转换Fit All Objects适合全部对象Fit Board适合底板Fit Document适合大小文档Fit Document (Ctrl+PgDn)适合大小文档(Ctrl+PgDn)Fit Filtered Objects适合过滤对象Fit Selected适合选择Fit Selected Objects适合选中对象Fit Sheet适合图纸Fit Specified Area适合指定区域Fit Waveforms适合波形Fixed Size Jump固定步长跳转Flat (Only ports global)平面〔只对全局端口〕Flip Selection翻转被选FLOAT浮点Focus Wave主波形Font Substitutions字型置换Footprint封装Footprint Model封装模型Footprint not found没有发现封装Footprints封装For a parallel gap of平行线间距Force Columns Into View所有列显示Force plete tenting on bottom在底部强制完全伸展Force plete tenting on top在顶部强制完全伸展Foreground前景Formal Type格式类型Format and Radix格式和基数- ..Format Axis格式化轴Format Wave格式化波形Format Y Axis格式化Y 轴Formats格式Formatting格式化Found in发现于Four Layer (2 x Signal, 2 x Plane)四层〔2信号层,2电层〕FPGA OptionsFPGA 选项FPGA PreferencesFPGA 参数选择FPGA ProjectFPGA工程FPGA ProjectsFPGA工程Free Documents自由文档Free Objects自由对象From To Display Settings飞线显示设置From Tos飞线From-To Editor飞线编辑器Full Circle圆环Full line ment全行注释Full Query完全查询Full Results全部结果Full Stack完全层叠Function Definitions函数定义Gap间隙Gear 2齿轮2Gear 3齿轮3Gear 4齿轮4Gear 5齿轮5Gear 6齿轮6Gear's Method 1st Order齿轮方法第1命令Gear's Method 2nd Order齿轮方法第2命令Gear's Method 3rd Order齿轮方法第3命令Generate Change Orders产生改变命令Generate DRC Rules产生DRC规那么Generate implicit modules for LPM, XBLOX orLogicB为LPM, XBLOX orLogicB产生隐含模块Generate Print Preview of Active Document生成激活文档的打印预览Generate Report生成报告Generate XSPICE Netlist生成XSPICE 连线表Generates pick and place files生成拾取和摆放文件Gerber FilesGerber文件Gerber SetupGerber设置Get Latest Version得到最后的版本Global (Netlabels and ports global)全局〔网络标号和全局端口〕GND Power Port接地电源端口Goto Line Number转到连线编号Graph图表Graphic图形Graphical图形Graphical Editing图形编辑Greater Equal大于等于Grid栅格Grid 1网格1Grid 2网格2Grid Color网格颜色Grid Range网格围Grid Size网格尺寸Grid Type栅格类型Grids网格Ground Plane 1 (GND)地平面层1(GND)Ground Plane 2 (GND)地平面层2(GND)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.PROTEL主要中英文对照原理图常用库文件:Miscellaneous Devices.ddbDallas Microprocessor.ddbIntel Databooks.ddbProtel DOS Schematic Libraries.ddbPCB元件常用库:Advpcb.ddbGeneral IC.ddbMiscellaneous.ddb部分分立元件库元件名称及中英对照Relay 继电器AND 与门ANTENNA 天线BATTERY 直流电源BELL 铃,钟BVC 同轴电缆接插件BRIDEG 1 整流桥(二极管) BRIDEG 2 整流桥(集成块) BUFFER 缓冲器BUZZER 蜂鸣器CAP 电容CAPACITOR 电容CAPACITOR POL 有极性电容CAPVAR 可调电容CIRCUIT BREAKER 熔断丝COAX 同轴电缆CON 插口CRYSTAL 晶体整荡器DB 并行插口DIODE 二极管DIODE SCHOTTKY 稳压二极管DIODE VARACTOR 变容二极管DPY_3-SEG 3段LED DPY_7-SEG 7段LEDDPY_7-SEG_DP 7段LED(带小数点) ELECTRO 电解电容FUSE 熔断器INDUCTOR 电感INDUCTOR IRON 带铁芯电感NDUCTOR3 可调电感JFET N N沟道场效应管JFET P P沟道场效应管LAMP 灯泡LAMP NEDN 起辉器LED 发光二极管METER 仪表MICROPHONE 麦克风MOSFET MOS管MOTOR AC 交流电机MOTOR SERVO 伺服电机NAND 与非门NOR 或非门NOT 非门NPN三极管NPN-PHOTO 感光三极管OPAMP 运放OR 或门PHOTO 感光二极管PNP 三极管NPN DAR NPN三极管PNP DAR PNP三极管POT 滑线变阻器PELAY-DPDT 双刀双掷继电器RES1.2 电阻RES3.4 可变电阻RESISTOR BRIDGE ? 桥式电阻RESPACK 电阻SCR 晶闸管PLUG 插头PLUG AC FEMALE 三相交流插头SOCKET 插座SOURCE CURRENT 电流源SOURCE VOLTAGE 电压源SPEAKER 扬声器SW ? 开关SW-DPDY ? 双刀双掷开关SW-SPST 单刀单掷开关SW-PB 按钮THERMISTOR 电热调节器TRANS1 变压器TRANS2 可调变压器TRIAC ? 三端双向可控硅TRIODE 三极真空管VARISTOR 变阻器ZENER 齐纳二极管DPY_7-SEG_DP 数码管SW-PB 开关其他元件库Protel Dos Schematic 4000 Cmos .Lib (40.系列CMOS管集成块元件库)4013 D 触发器4027 JK 触发器Protel Dos Schematic Analog Digital.Lib(模拟数字式集成块元件库)AD系列DAC系列HD系列MC系列Protel Dos Schematic Comparator.Lib(比较放大器元件库)Protel Dos Shcematic Intel.Lib(INTEL公司生产的80系列CPU集成块元件库)Protel Dos Schematic Linear.lib(线性元件库)Protel Dos Schemattic Memory Devices.Lib(内存存储器元件库)Protel Dos Schematic SYnertek.Lib(SY系列集成块元件库)Protes Dos Schematic Motorlla.Lib(摩托罗拉公司生产的元件库)Protes Dos Schematic NEC.lib(NEC公司生产的集成块元件库)Protes Dos Schematic Operationel Amplifers.lib(运算放大器元件库)Protes Dos Schematic TTL.Lib(晶体管集成块元件库74系列)Protel Dos Schematic Voltage Regulator.lib(电压调整集成块元件库)Protes Dos Schematic Zilog.Lib(齐格格公司生产的Z80系列CPU集成块元件库)元件属性对话框中英文对照Lib ref 元件名称Footprint 器件封装Designator 元件称号Part 器件类别或标示值Schematic Tools 主工具栏Writing Tools 连线工具栏Drawing Tools 绘图工具栏部分分立元件库元件名称及中英对照Power Objects 电源工具栏Digital Objects 数字器件工具栏Simulation Sources 模拟信号源工具栏PLD Toolbars 映象工具栏2.DXP2004 DRC 规则中英文对照在DXP2004中的DRC规则检查项目,对于一些初学的朋友是一个大难题,特对其进行整理一下,英文水平有限,仅供参考:DXP2004 DRC 规则英文对照Ⅰ:Error Reporting 错误报告A:Violations Associated with Buses 有关总线电气错误的各类型(共12项)◆bus indices out of range 总线分支索引超出范围◆Bus range syntax errors 总线范围的语法错误◆Illegal bus range values 非法的总线范围值◆Illegal bus definitions 定义的总线非法◆Mismatched bus label ordering 总线分支网络标号错误排序◆Mismatched bus/wire object on wire/bus 总线/导线错误的连接导线/总线◆Mismatched bus widths 总线宽度错误◆Mismatched bus section index ordering 总线范围值表达错误◆Mismatched electrical types on bus 总线上错误的电气类型◆Mismatched generics on bus (first index) 总线范围值的首位错误◆Mismatched generics on bus (second index) 总线范围值末位错误◆Mixed generics and numeric bus labeling 总线命名规则错误B:Violations Associated Components 有关元件符号电气错误(共20项)◆Component Implementations with duplicate pins usage 元件管脚在原理图中重复被使用◆Component Implementations with invalid pin mappings 元件管脚在应用中和PCB封装中的焊盘不符◆Component Implementations with missing pins in sequence 元件管脚的序号出现序号丢失◆Component contaning duplicate sub-parts 元件中出现了重复的子部分◆Component with duplicate Implementations 元件被重复使用◆Component with duplicate pins 元件中有重复的管脚◆Duplicate component models 一个元件被定义多种重复模型◆Duplicate part designators 元件中出现标示号重复的部分◆Errors in component model parameters 元件模型中出现错误的的参数◆Extra pin found in component display mode 多余的管脚在元件上显示◆Mismatched hidden pin component 元件隐藏管脚的连接不匹配◆Mismatched pin visibility 管脚的可视性不匹配◆Missing component model parameters 元件模型参数丢失◆Missing component models 元件模型丢失◆Missing component models in model files 元件模型不能在模型文件中找到◆Missing pin found in component display mode 不见的管脚在元件上显示◆Models found in different model locations 元件模型在未知的路径中找到◆Sheet symbol with duplicate entries 方框电路图中出现重复的端口◆Un-designated parts requiring annotation 未标记的部分需要自动标号◆Unused sub-part in component 元件中某个部分未使用C:violations associated with document 相关的文档电气错误(共10项)1、conflicting constraints 约束不一致的2、dupl icate sheet symbol name 层次原理图中使用了重复的方框电路图3、duplicate sheet numbers 重复的原理图图纸序号4、missing child sheet for sheet symbol 方框图没有对应的子电路图5、missing configuration target 缺少配置对象6、missing sub-project sheet for component 元件丢失子项目7、multiple configuration targets 无效的配置对象8、multiple top-level document 无效的顶层文件9、port not linked to parent sheet symbol 子原理图中的端口没有对应到总原理图上的端口10、sheet enter not linked to child sheet 方框电路图上的端口在对应子原理图中没有对应端口D:violations associated with nets 有关网络电气错误(共19项)1、adding hidden net to sheet 原理图中出现隐藏网络2、adding items from hidden net to net 在隐藏网络中添加对象到已有网络中3、auto-assigned ports to device pins 自动分配端口到设备引脚4、duplicate nets 原理图中出现重名的网络5、floating net labels 原理图中有悬空的网络标签6、global power-objects scope changes 全局的电源符号错误7、net parameters with no name 网络属性中缺少名称8、net parameters with no value 网络属性中缺少赋值9、nets containing floating input pins 网络包括悬空的输入引脚10、nets with multiple names 同一个网络被附加多个网络名11、nets with no driving source 网络中没有驱动12、nets with only one pin 网络只连接一个引脚13、nets with possible connection problems 网络可能有连接上的错误14、signals with multiple drivers 重复的驱动信号15、sheets containing duplicate ports 原理图中包含重复的端口16、signals with load 信号无负载17、signals with drivers 信号无驱动18、unconnected objects in net 网络中的元件出现未连接对象19、unconnected wires 原理图中有没连接的导线E:Violations associated with others有关原理图的各种类型的错误(3项)1、No Error 无错误2、Object not completely within sheet boundaries 原理图中的对象超出了图纸边框3、Off-grid object原理图中的对象不在格点位置F:Violations associated with parameters 有关参数错误的各种类型1、same parameter containing different types 相同的参数出现在不同的模型中2、same parameter containing different values 相同的参数出现了不同的取值Ⅱ、Comparator 规则比较A:Differences associated with components 原理图和PCB上有关的不同(共16项)◆Changed channel class name 通道类名称变化◆Changed component class name 元件类名称变化◆Changed net class name 网络类名称变化◆Changed room definitions 区域定义的变化◆Changed Rule 设计规则的变化◆Channel classes w ith extra members 通道类出现了多余的成员◆Component classes with extra members 元件类出现了多余的成员◆Difference component 元件出现不同的描述◆Different designators 元件标示的改变◆Different library references 出现不同的元件参考库◆Different types 出现不同的标准◆Different footprints 元件封装的改变◆Extra channel classes 多余的通道类◆Extra component classes 多余的元件类◆Extra component 多余的元件◆Extra room definitions 多余的区域定义B:Differences associated with nets 原理图和PCB上有关网络不同(共6项)◆Changed net name 网络名称出现改变◆Extra net classes 出现多余的网络类◆Extra nets 出现多余的网络◆Extra pins in nets 网络中出现多余的管脚◆Extra rules 网络中出现多余的设计规则◆Net class with Extra members 网络中出现多余的成员C:Differences associated with parameters 原理图和PCB上有关的参数不同(共3项)◆Changed parameter types 改变参数类型◆Changed parameter value 改变参数的取值◆Object with extra parameter 对象出现多余。