LKT4301 32位高性能多接口RSA防盗版加密芯片

LKT4201移动支付加密芯片

LKT4201 32位高端RSA加密芯片LKT4201 32位高性能超低功耗RSA加密IC是目前行业内最低功耗的高性能的RSA加密芯片,芯片采用32位CPU(获得全球最高安全等级EAL5+的智能卡芯片),18K RAM ,支持ISO7816及UART通信,通讯速率最高可达1.25Mbps;用户数据存储区容量最低64K字节。

在超高安全等级加密的同时,速度大大超越一般8位或16位RSA加密芯片。

RSA加接密功耗只相当于市面上普通8位16位RSA加密芯片的十分之一。

产品特点:高性能、低功率32位CPU内核64K以上字节用户数据存储区;内嵌真随机数发生器,符合FIPS140-2标准;外部时钟频率范围1~10M Hz;支持UART接口最高支持1.25Mbps通讯速率;通讯速率远远超过普通8位16位智能卡芯片为基础的RSA加密芯片;芯片安全性能,采用通过国际智能卡安全检测标准EAL5+,高于8位16位的智能卡加密芯片。

安全特性:电压检测模块对抗高低电压攻击;频率检测模块对抗高低频率攻击;多种检测传感器:高压和低压传感器,频率传感器、滤波器、脉冲传感器、温度传感器,具有传感器寿命测试功能,一旦芯片检测到非法探测,将启动内部的自毁功能;芯片防篡改设计,唯一序列号;总线加密,具有金属屏蔽防护层,探测到外部攻击后内部数据自毁;硬件RSA、3DES算法协处理器;32位可编程算法协处理器;MMU存储器管理单元,可灵活设置SYS\APP模式及授予相应权限;程序和数据均加密存储;安全认证目标:EAL5+。

产品功能:支持产生存储多条公私钥RSA密钥支持1024-1984位、2048位可定制公钥指数可以设定多种模式公私钥文件安全权限可以自定义支持SHA1、SHA256摘要算法支持DES、3DES算法支持DES 3DES过程密钥支持AES算法支持标准二进制、记录等文件系统技术参数:工作电压范围:1.8v—5.5v;工作温度:-20℃~+85℃;ESD保护:大于4KV;封装形式:SSOP20(可定制封装)。

LKT4201_RSA芯片

LKT4201 32位高端RSA移动支付加密芯片1.产品图片2.加密芯片说明LKT4201 32位高端RSA移动支付加密芯片说明LKT4201 32位高性能超低功耗RSA加密IC是目前行业内最低功耗的高性能的RSA加密芯片,芯片采用32位CPU(获得全球最高安全等级EAL5+的智能卡芯片),18K RAM ,支持ISO7816及UART通信,通讯速率最高可达1.25Mbps;用户数据存储区容量最低64K字节。

在超高安全等级加密的同时,速度大大超越一般8位或16位RSA加密芯片。

RSA加接密功耗只相当于市面上普通8位16位RSA加密芯片的十分之一。

2.1.产品特点高性能、低功率32位CPU内核64K以上字节用户数据存储区;内嵌真随机数发生器,符合FIPS140-2标准;外部时钟频率范围1~10M Hz;支持UART接口最高支持1.25Mbps通讯速率;通讯速率远远超过普通8位16位智能卡芯片为基础的RSA加密芯片;芯片安全性能,采用通过国际智能卡安全检测标准EAL5+,高于8位16位的智能卡加密芯片。

2.2.安全特性电压检测模块对抗高低电压攻击;频率检测模块对抗高低频率攻击;多种检测传感器:高压和低压传感器,频率传感器、滤波器、脉冲传感器、温度传感器,具有传感器寿命测试功能,一旦芯片检测到非法探测,将启动内部的自毁功能;芯片防篡改设计,唯一序列号;总线加密,具有金属屏蔽防护层,探测到外部攻击后内部数据自毁;硬件RSA、3DES算法协处理器;32位可编程算法协处理器;MMU存储器管理单元,可灵活设置SYS\APP模式及授予相应权限;程序和数据均加密存储;安全认证目标:EAL5+。

2.3.产品功能支持产生存储多条公私钥RSA密钥支持1024-1984位、2048位可定制公钥指数可以设定多种模式公私钥文件安全权限可以自定义支持SHA1、SHA256摘要算法支持DES、3DES算法支持DES 3DES过程密钥支持AES算法支持标准二进制、记录等文件系统2.4.技术参数工作电压范围:1.8v—5.5v;工作温度:-20℃~+85℃;ESD保护:大于4KV;封装形式:SSOP20(可定制封装)。

FPGA可编程逻辑器件芯片EP4SGX230KF40I3中文规格书

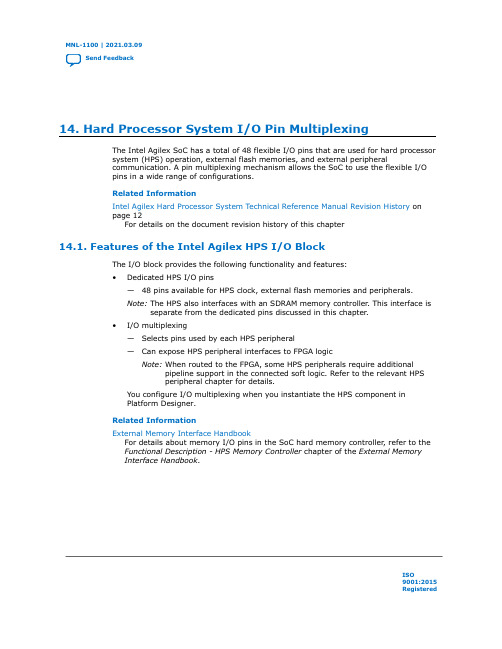

14.Hard Processor System I/O Pin MultiplexingThe Intel Agilex SoC has a total of 48 flexible I/O pins that are used for hard processor system (HPS) operation, external flash memories, and external peripheral communication. A pin multiplexing mechanism allows the SoC to use the flexible I/O pins in a wide range of configurations.Related InformationIntel Agilex Hard Processor System Technical Reference Manual Revision History on page 12For details on the document revision history of this chapter14.1. Features of the Intel Agilex HPS I/O BlockThe I/O block provides the following functionality and features:•Dedicated HPS I/O pins—48 pins available for HPS clock, external flash memories and peripherals.Note: The HPS also interfaces with an SDRAM memory controller . This interface is separate from the dedicated pins discussed in this chapter .•I/O multiplexing—Selects pins used by each HPS peripheral —Can expose HPS peripheral interfaces to FPGA logicNote: When routed to the FPGA, some HPS peripherals require additional pipeline support in the connected soft logic. Refer to the relevant HPS peripheral chapter for details.You configure I/O multiplexing when you instantiate the HPS component in Platform Designer.Related InformationExternal Memory Interface Handbook For details about memory I/O pins in the SoC hard memory controller , refer to the Functional Description - HPS Memory Controller chapter of the External Memory Interface Handbook .MNL-1100 | 2021.03.09Send FeedbackISO 9001:2015Registered14.2. Intel Agilex HPS I/O System IntegrationThe HPS I/O block consists of the following sub-blocks:•Dedicated pin multiplexers (MUXes) – MUXes for the dedicated I/O bank •FPGA access pin multiplexers – MUXes for HPS peripheral connections to the FPGA fabric •Register slave interface – Provides access to control registers, which allow the bootloader to initialize I/O pins and HPS peripheral interfaces at system startupRelated InformationIntel Agilex I/O Control Registers on page 18514.3. Functional Description of the HPS I/O14.3.1. I/O PinsThe HPS has 48 dedicated I/O pins. They are divided into four quadrants of 12 signals per quadrant. When you instantiate the HPS component in Platform Designer, you must assign one of the 48 pins as the HPS clock. You can then use the remaining dedicated I/O pins for other common peripherals.You can alternatively route most HPS peripherals (except USB) through the FPGA.Select this routing when you instantiate the HPS Component. For more information,refer to the Intel Agilex HPS Component Reference Manual .Note:When assigning an HPS peripheral to HPS dedicated pins, you must assign all peripheral I/O pins to the same quadrant, except for NANDx16, Trace, and GPIO.Note: Although the HPS dedicated I/O pins are configured through the control registers,software cannot reconfigure the pins after I/O configuration is complete. There is no support for dynamically changing the pin MUX selections for HPS dedicated I/O pins.Related Information•Booting and Configuration on page 512Details about the boot up process for the Intel Agilex HPS •FPGA Access on page 184Information about routing HPS peripheral interfaces to the FPGA •Configuring HPS I/O Multiplexing on page 188Information about configuring the HPS I/O MUXes14.3.2. FPGA AccessMost HPS peripheral interfaces can be connected into the FPGA fabric, instead of to the dedicated I/O pins.HPS peripherals connect to the FPGA fabric through the FPGA access pin MUX. When connected to the FPGA fabric, peripheral interfaces are exposed as ports of the HPS component.14.Hard Processor System I/O Pin MultiplexingMNL-1100 | 2021.03.09Send FeedbackNote: For warm resets, software can set the brgwarmmask registers to prevent theassertion of module reset signals to peripheral modules.When a module that has been held in reset is ready to start running, software can deassert the respective reset signal by writing to the following appropriate register .Modules Module Reset Signal RegisterFPGA fabrics2f_rst -s2f_cold_rst -s2f_watchdog_rst-Debug domain with CoreSight and Trace dbg_rst_ndbgmodrst.dbg_rst dbgmodrst.csdap_rst MPU corereset_n [3:0]mpumodrst.core[3:0]cpuporreset_n [3:0]coldmodrst.cpupor[3:0]l2reset_n coldmodrst.l2DMA dma_rst_n per0modrst.dmadma_ecc_rst_n per0modrst.dmaocpdma_periph_if_rst_n [7:0]per0modrst.dmaif[7:0]SPI Master and Slave spim_rst_n [1:0]per0modrst.spim[1:0]spis_rst_n [1:0]per0modrst.spis[1:0]Ethernet MAC emac_rst_n [2:0]per0modrst.emac[2:0]emac_ecc_rst_n [2:0]per0modrst.emac[2:0]ocpemac_ptp_rst_n per0modrst.emacptpUSB usb_rst_n [1:0]b[1:0]usb_ecc_rst_n [1:0]b[1:0]ocpNAND Flash nand_flash_rst_n per0modrst.nandnand_flash_ecc_rst_n per0modrst.nandocpSD/MMC sdmmc_rst_n per0modrst.sdmmcsdmmc_ecc_rst_n per0modrst.sdmmcocpWatchdog watchdog_rst_n [3:0]per1modrst.watchdog[3:0]Timer l4sys_timer_rst_n [1:0]per1modrst.l4systimer[1:0]sp_timer_rst_n [1:0]per1modrst.sptimer[1:0]I 2C i2c_rst_n [4:0]per1modrst.i2c[4:0]UART uart_rst_n [1:0]per1modrst.uart[1:0]GPIO gpio_rst_n [1:0]per1modrst.gpio[1:0]SoC-to-FPGA Bridge soc2fpga_bridge_rst_n brgmodrst.soc2fpgaFPGA-to-SoC Bridge fpga2soc_bridge_rst_n brgmodrst.fpga2socLightweight SoC-to-FPGA Bridge lwsoc2fpga_bridge_rst_n brgmodrst.lwsoc2fpgaMPFE mpfe_rst_nbrgmodrst.mpfe 13.Reset ManagerMNL-1100 | 2021.03.09Send Feedback。

用于高级音频和语音应用的低功耗32位DSP架构框架

用于高级音频和语音应用的低功耗32位DSP架构框架

佚名

【期刊名称】《今日电子》

【年(卷),期】2012(000)007

【摘要】CEVA-TL410和CEVA—TL411DSP分圳提供的单个32×32位乘法器和两个32×32像乘法器,针对语音、音频编解码器和hubs应用,CEVA—TL420和CEVA-TL421DSP增加了全cache的存储器予系统和AXI系统按口,目标市场是应用处理器和家庭音频Soc。

【总页数】1页(P63-63)

【正文语种】中文

【中图分类】TN76

【相关文献】

1.CEVA推出低功耗32位DSP架构CEVA—TeakLite-4 [J],

2.用于专用DSP处理器的高速低功耗的IEEE 32位浮点加法器 [J], 孙旭光;毛志刚;来逢昌

3.德州仪器借助新架构推进新兴的线缆语音技术基于DSP的低功耗平台为线缆制造商提供了功能强大的处理技术以及更高的设计灵活性 [J],

4.科大讯飞嵌入式语音识别软件可用于CEVA超低功耗音频/语音DSP [J],

5.CEVA推出低功耗32位DSP架构框架CEVA-TeakLite-4 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

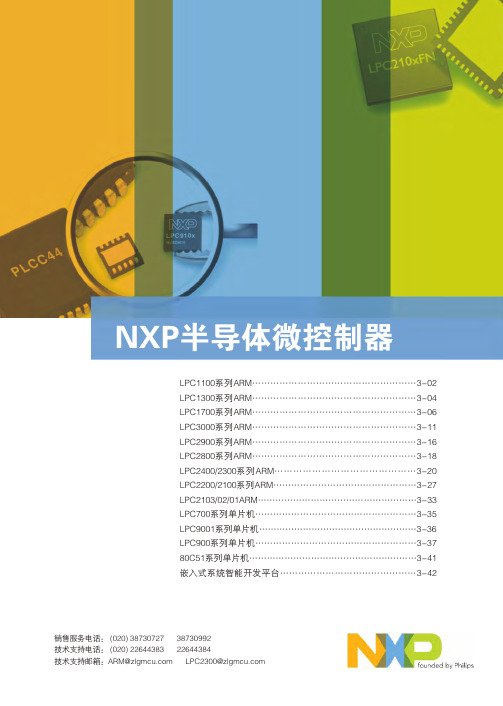

NXP mcu

TinyM0核心板电路为LPC111x芯片的最小系统,硬件支持2.54mm间距的 标准排针。用户可以将TinyM0核心板配套自行设计的底板进行产品开发。 ● 支持多款芯片

和16位竞争产品的2至4倍。

Cortex-M0内核

● 32位ARM RISC处理器,16位Thumb指令集; ● 功耗与面积高度优化,设计专用于低成本、低功耗场合; ● 24位SysTick定时器; ● 32位硬件乘法器; ● 中断现场自动保存,有处理决定性、固定延迟的中断能力; ● 系统接口支持小端或字节不变的大端数据访问; ● SWD串行线调试。

LPC1300选型表:

器件型号 LPC1343 LPC1342 LPC1313 LPC1311

Flash (KB) 32 16 32 8

SRAM(KB) 8 4 8 2

USB 2.0 Device Device

-

I2C(Fast+) 1 1 1 1

ADC 8ch/10bit 8ch/10bit 8ch/10bit 8ch/10bit

置的新型开漏工作模式

LPC1100

◎ 四个通用计数器/计数器 ◎ 可编程的看门狗定时器(WDT),带锁死功能 ◎ 系统计时器 ◎ 各外设自带时钟分频器,有利于降低功耗

芯片特色:

Cortex-M0处理器性能 ● Cortex-M0微控制器可以轻松超越高端8位和16位器件的

性能水平; ● 内核额定性能为0.9DMIPS/MHz,相当于与其最接近的8位

LKT4200加密芯片的安全性分析

LKT4200加密芯片的安全性分析

随着国内盗版破解方面的日益猖獗,严重影响了产品开发商的利益,从技术角度保护开发商产品的知识产权已经越来越重要了。

而市面上大批形形色色的加密芯片很多,到底哪些加密芯片才能起到加密保护作用呢?目前市面上主要流行几大类加密芯片:

第一种是逻辑加密芯片,这种芯片一般是由一个EEPROM加上外围逻辑电路,通过简单的ID号或者逻辑认证口令进行保护认证,这种芯片的特点就是便宜,开发也最简单,但破解难度最低,目前深圳华强北破解这种芯片基本可以做到立等可取,破解费用在150元到几百元不等,非常简单。

这种芯片一般用于对盗版没什么压力,只是为了加一个保护的样子,或者基本没什么利润的产品。

第二种是带有固定算法,采用比对认证模式的加密芯片,这种芯片相对于上面那种芯片复杂点,但由于采用的是比对模式,就算线路上传送的是随机数或者被加密的随机认证码,但并没有能起到多高的保护作用,因为被保护的CPU中的程序是完整的,跟加密芯片直接只是存在着若干孤立的比对点,而当盗版商去破解这个系统的时候,不会去破解加密芯片,而是直接破解CPU获得全部的代码,然后跳过所有比对点。

这样就完成了破解。

这种固定算法比对模式的加密芯片开发相对也不是太难,只要按照说明书上的认证流程开发,当然盗版商也很喜欢这样的芯片,因为他的加密流程盗版商也很熟悉。

目前市场前几年大卖的几款国内外加密芯片的破解成本已经非常低廉,破解方法都已经在破解圈被大家所熟悉。

第三种加密芯片是近几年兴起的采用高端(EAL5+)智能卡芯片内核,软硬件开发商可以把自己软件中一部分算法和代码下载到芯片中运行。

用户采用。

为什么DX81C04防抄板加密芯片这么好用

为什么DX81C04防抄板加密芯片这么好用众所周知,每年的硬件和软件的克隆都会导致数十亿美元的收益损失,从充斥市场的廉价仿冒品到被入侵的智能仪表和泄露的密钥卡系统,类似的事件层出不穷。

在现在大众创业,万众创新的时代中,无论设计的是打印机,智能手机,医疗设备,无人机,广告机,还是很酷的创新产品,或者是墨盒,一次性医疗用品,电池等耗材和配机,企业都将大量的时间,精力和金钱投资于公司的核心技术开发中。

但是,往往对有价值的技术不加以保护,很容易被黑客和仿冒者给窃取,给企业带来巨大的经济损失。

如何做到安全保护企业的核心固件呢?主要考虑这几个重要因素,第一,采用软硬件同时加密的方式,保证产品必须使用公司的核心固件才能够使用,第二,将公司的核心固件存放在加密存储器中,第三,在核心固件进行传输的过程中进行加密。

DX81C04防抄板加密芯片可以一站式的解决客户的这些担忧,它很容易与任何微处理器连接,而且非常小强,几乎可以适应任何设计。

那么,DX81C04是如何的工作的呢,客户只需要把密钥和核心数据存储在DX81C04防抄板加密芯片中,当主系统要求配件或者耗材证明其真伪时,系统的响应取决于根据密钥算出啦的加密结果,如何是错误的应答,则系统拒绝该配件和耗材。

那么市场是有这么多加密芯片,为什么要选择DX81C04呢?DX81C04防抄板加密芯片有几个非常显著的特点1. 每颗芯片通过芯片制造产生全球唯一SN序列号(芯片唯一性)2. 内置56bits的一次性写入用户UID号,可以用来规范自己产品编号,进行生产,出货,串货管理。

(管理产品的出货、串货、售后系统)3. 采用国际通用SHA1算法,128bits密钥长度进行Host认证(高强度的密钥保护系统)4. EEPROM物理访问地址乱序,EEPROM物理数据存储加密。

(客户的核心数据,核心程序的保护系统,即使破掉密钥也无法读出加密数据)5. 独特的密钥安全烧写系统,每颗芯片存放的都是真实密钥在加密过的密钥,破解单颗芯片的密钥只对这颗芯片对应的产品有效,对整个同类型的产品是无效的,依旧无法通过验证滴(超高的安全性,用软硬件结合的方式从根本上解决破解掉单个产品,整个同类型的产品全被破解掉的担忧。

北京时代民芯科技有限公司 CLGA封装芯片测试夹具说明书

(19)国家知识产权局(12)实用新型专利(10)授权公告号 (45)授权公告日 (21)申请号 202122081758.0(22)申请日 2021.08.31(73)专利权人 北京时代民芯科技有限公司地址 100076 北京市丰台区东高地四营门北路2号专利权人 北京微电子技术研究所(72)发明人 李明远 闫静 姜扬 刘利新 常国义 闫兰丰 黄玉凤 吕学明 (74)专利代理机构 中国航天科技专利中心11009专利代理师 范晓毅(51)Int.Cl.G01R 1/04(2006.01)G01R 31/28(2006.01)(54)实用新型名称一种针对CLGA封装芯片的测试夹具(57)摘要本实用新型提供一种针对CLGA封装芯片的测试夹具,将夹具中传统的单一尺寸导向框改进为包括最大外形导向框和可拆装导向块的导向框组件,最大外形导向框中设有大于等于待测芯片最大外形尺寸上限的内腔,可拆装导向块安装于最大外形导向框,调整内腔的尺寸与待测芯片最大外形尺寸相匹配,实现待测芯片在所述内腔中的定位,进而利用导向框组件,测试座,探针和手测盖之间的配合,实现对待测芯片的测试。

本实用新型解决了陶瓷平面网格阵列封装器件公差较大、器件在测试夹具内定位不精准的问题,可以快速组装不同定位腔尺寸的导向框,不需要通过新制或者返修原有导向框的方法来兼容陶瓷封装器件的最大外形公差,节约了重新制作导向框的成本。

权利要求书2页 说明书4页 附图3页CN 216525901 U 2022.05.13C N 216525901U1.一种针对CLGA封装芯片的测试夹具,包括测试座(1),探针(2)和手测盖(4),其特征在于,还包括导向框组件(3);导向框组件(3)包括最大外形导向框(31)和可拆装导向块(32);所述最大外形导向框(31)设有顶部开口的内腔(311),所述内腔(311)的尺寸大于等于待测芯片最大外形的尺寸上限;待测芯片置于所述内腔(311)中,可拆装导向块(32)固定安装于最大外形导向框(31)上,实现待测芯片在所述内腔(311)中的定位;导向框组件(3)固定安装于测试座(1)上,手测盖(4)设于导向框组件(3)上方,用于测试时向待测芯片施加压力;测试座(1)和导向框组件(3)上分别设有第一针孔和第二针孔,探针(2)通过第一针孔固定安装于测试座(1)上,待测芯片受到所述压力时,探针(2)穿过第二针孔与待测芯片焊盘接触,实现对待测芯片的测试。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LKT4301 32位高性能多接口RSA防盗版加密芯片

LKT4301 高性能多接口RSA防盗版加密芯片采用32位智能卡专用芯片,带有USB接口的32位智能卡微控制器。

内部工作时钟频率可达50M Hz,且可在内部和外部时钟之间动态切换。

芯片内嵌USB DEVICE控制器,支持USB low speed、full speed通信模式。

芯片支持USB、UART、GPIO以及SPI高速接口等通信模式。

芯片内部集成了移植算法程序功能以及标准智能卡文件密钥功能,支持RSA1024bit-2048bit、DES\3DES、AES128、AES192、AES256、SHA1、SHA256等算法,软硬件开发商还可以把自己软件中一部分算法和代码下载到芯片中运行。

,从根本上杜绝程序被破解的可能。

32位CPU内核,32位操作系统

支持DES/3DES算法

支持AES128、AES192、AES256算法

支持RSA1024bit-2048bit算法

支持ECC(可选)算法

高性能、低功率32位CPU内核,指令支持标准C

内嵌USB DEVICE控制器,支持USB low speed、full speed通信模式

64K字节算法程序存储区,16K字节NVM区、32K字节密钥文件区

全球唯一序列号

32位CPU内部硬件集成协处理器,支持RSA、DES、SHA1、AES、ECC等常用密码学计算

内嵌真随机数发生器,符合FIPS140-2标准

电压检测模块对抗高低电压攻击

频率检测模块对抗高低频率攻击

MMU存储器管理单元,可灵活设置SYS\APP模式及授予相应权限

程序和数据均加密存储

安全认证目标:EAL5+

参数类型:

4KV 静电保护

工作电压:4.4V-5.5V

环境温度:-25 ℃ ~ +85 ℃

数据空间:64K字节算法程序存储区,16K字节NVM区、32K字节密钥文件区最大电流:40mA

通讯方式:UART串行通讯接口,USB,SPI接口

通讯协议:ISO7816 T=0协议或者T=1协议(可定义),支持自定义A3协议

通讯速率:最高通讯速率支持12Mbps(USB接口)

产品封装:

封装形式:SSOP24

质量:

取得MSDS认证报告

获得EAL5+通用标准评估保证等级认证.

通过了欧盟RoHS环保认证标准

通过ISO9001:2008质量体系认证

设计支持:

开发工具:

Smart Cardreader智能卡读卡器

linkSAM烧录测试软件

SCKit智能卡操作软件

通讯调试板

芯片转接板

开发相关资料

LKT4301 data SHEET

LKT4301 开发手册

通讯调试板使用说明

LKT4301算法例程

SPI通讯例程

Demo电路

应用领域:

软件狗

PC上位机软件加密

嵌入式linux软件加密

控制器嵌入式软件加密汽车电子嵌入式软件加密平板电脑嵌入式软件加密机顶盒嵌入式软件加密路由器嵌入式软件加密交换机嵌入式软件加密仪器仪嵌入式软件加密国防嵌入式软件加密

工业嵌入式软件加密。