计算机组成原理第7章作业答案

计算机组成原理习题答案第七章

1.控制器有哪几种控制方式?各有何特点?解:控制器的控制方式可以分为3种:同步控制方式、异步控制方式和联合控制方式。

同步控制方式的各项操作都由统一的时序信号控制,在每个机器周期中产生统一数目的节拍电位和工作脉冲。

这种控制方式设计简单,容易实现;但是对于许多简单指令来说会有较多的空闲时间,造成较大数量的时间浪费,从而影响了指令的执行速度。

异步控制方式的各项操作不采用统一的时序信号控制,而根据指令或部件的具体情况决定,需要多少时间,就占用多少时间。

异步控制方式没有时间上的浪费,因而提高了机器的效率,但是控制比较复杂。

联合控制方式是同步控制和异步控制相结合的方式。

2.什么是三级时序系统?解:三级时序系统是指机器周期、节拍和工作脉冲。

计算机中每个指令周期划分为若干个机器周期,每个机器周期划分为若干个节拍,每个节拍中设置一个或几个工作脉冲。

3.控制器有哪些基本功能?它可分为哪几类?分类的依据是什么?解:控制器的基本功能有:(1)从主存中取出一条指令,并指出下一条指令在主存中的位置。

(2)对指令进行译码或测试,产生相应的操作控制信号,以便启动规定的动作。

(3)指挥并控制CPU 、主存和输入输出设备之间的数据流动。

控制器可分为组合逻辑型、存储逻辑型、组合逻辑与存储逻辑结合型3类,分类的依据在于控制器的核心———微操作信号发生器(控制单元CU)的实现方法不同。

4.中央处理器有哪些功能?它由哪些基本部件所组成?解:从程序运行的角度来看,CPU 的基本功能就是对指令流和数据流在时间与空间上实施正确的控制。

对于冯? 诺依曼结构的计算机而言,数据流是根据指令流的操作而形成的,也就是说数据流是由指令流来驱动的。

5.中央处理器中有哪几个主要寄存器?试说明它们的结构和功能。

解:CPU 中的寄存器是用来暂时保存运算和控制过程中的中间结果、最终结果及控制、状态信息的,它可分为通用寄存器和专用寄存器两大类。

通用寄存器可用来存放原始数据和运算结果,有的还可以作为变址寄存器、计数器、地址指针等。

第7章习题答案 计算机组成原理课后答案(清华大学出版社 袁春风主编)

• 159 •

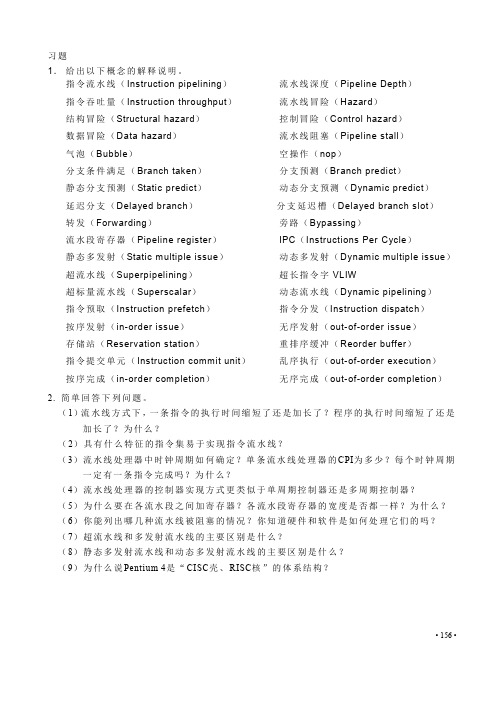

7. 假定以下 MIPS 指 令序列在图 7.18 所示 的流 水线数据通路中 执行:

addu $s3, $s1, $s0

subu $t2, $s0, $s3

流水线深度( Pipeline Depth) 流 水 线 冒 险 ( Hazar d) 控制冒险(Control hazard) 流水线阻塞( Pipeline stall) 空 操 作 ( nop) 分支预测(Branch predict) 动态分支预测(Dynamic predict) 分支 延迟槽(Delayed branch slot) 旁 路 ( Bypassing) IPC(Instructions Per Cycle) 动态多发射(Dynamic multiple issue) 超长指令字 VLIW 动态流水线(Dynamic pipelining) 指令分发(Instruction dispatch) 无序发射( out-of-order issue) 重排序缓冲(Reorder buffer) 乱序执行( out-of-order execution) 无序完成( out-of-order completion)

(1)插入 一个流水段寄 存器,得到 一个两级 流水线 (2)插 入两个流水段 寄存器,得 到一个三 级流水线 (3)插入 三个流水段寄 存器,得到 一个四级 流水线 (4)吞 吐量最大的流 水线 参考答案:

(1)两级流水线的平衡点在 C 和 D 之间,其前面一个流水段的组合逻辑延时为 80+30+60=170ps,后 面一 个流水 段的 组合逻 辑延时 为 50+70+10=130ps。这 样每个 流水段 都 以 最 长 延 时 调 整 为 170+20=190ps , 故 时 钟 周 期 为 190ps , 指 令 吞 吐 率 为 1/190ps=5.26GOPS,每条 指令的执行时 间为 2x190=380ps。

计算机组成与设计第三版第七章课后答案

13在所用主存储器芯片已确定的情况下,还要进行大幅度提高主存储器系统的读写 速度的办法是什么?

答:在所用主存储器芯片已确定的情况下,还要进行大幅度提高主存储器系统的读 写速度的办法是采用成组传送数据的方式,该方式是指用于提高在数据总线上的数 据输入/输出能力的一种技术。即通过地址总线传送一次地址后,能连续在数据总 线上传送多个(一组)数据,而不像正常总线工作方式那样,每传送一次数据,总 要用两段时间,即先送一次地址(地址时间),后送一次数据传送(数据时间)。 在成组传送方式,为传送N个数据,就可以用N+1个总线时钟周期,而不再是用 2N个总线时钟周期,使总线上的数据入/出尖峰提高一倍。

01

12存储器读写操作时,地址信号、片选信 号、读写命令、读出的数据或写入的数据, 在时间配合上要满足些什么关系?

02

答:存储器读写操作时,地址信号、片选信 号、读写命令、读出的数据或写入的数据, 它们之间在时序配合要满足以下这些条件: 有了稳定的地址与片选信号才可以读;有了 稳定的地址和写入的数据,再有了片选信号 才能再给出写命令,以便保证无误的写操作。 此外,这些信号应有一定的持续时间,以保 证读写操作得以正常完成。

202X

计算机组成原 理第七章习题

单击此处添加文本具体内容,简明扼要地 阐述你的观点

7.1.在计算机中,为什么要采用多级结构的存储器系统?它们的应用是建 立在程序的什么特性之上的?

答:在现代的计算机系统中,通常总是采用由三种运行原理不同,性能差异 很大的存储介质分别构建高速缓冲存储器、主存储器和虚拟存储器,再将它 们组成三级结构的统一管理、高度的一体化存储器系统。由高速缓冲存储器 缓解主存储器读写速度慢,不能满足CPU运行速度需要的矛盾;用虚拟存储 器更大的存储空间,解决主存储器容量小,存不下更大程序与更多数据的难 题。

计算机组成原理(第七章 输入输出系统

第七章输入输出系统第一节基本的输入输出方式一、外围设备的寻址1.统一编址:将输入输出设备中控制寄存器、数据寄存器、状态寄存器等与内存单元一样看待,将它们和内存单元联合在一起编排地址,用访问内存的指令来访问输入输出设备接口的某个寄存器,从而实现数据的输入输出。

2.单独编址:将输入输出设备中控制寄存器、数据寄存器、状态寄存器单独编排地址,用专门的控制信号进行输入输出操作。

3.CPU与外围设备进行通信有三种类型:(1)CPU向外围设备发出操作控制命令。

(2)外围设备向CPU提供状态信息。

(3)数据在CPU与外围设备之间的传递。

历年真题1.对外设统一编址是指给每个外设设置一个地址码。

(2002年)【分析】CPU与外设之间的信息传送是通过硬件接口来实现的,各种外设的硬件接口上又都包含有多个寄存器,如控制寄存器、数据寄存器、状态寄存器等。

统一编址是将外设接口上的各种寄存器等同于内存储器的存储单元,通过使用访问内存单元的指令来访问外设接口上的各个寄存器,这样就可以使用访存指令来访问外设,输入输出操作简单,程序设计比较简便。

由于外设接口上的寄存器种类和数量通常不止一个,所以一个外设至少对应一个以上的内存地址。

【答案】对外设统一编址是将外设接口上的寄存器等同内存单元,给每个外设设置至少一个地址码。

二、外围设备的定时1.外围设备的定时方式有异步传输方式和同步定时方式两种。

2.实现输入输出数据传输的方式主要有:程序控制方式、直接存储访问(DMA)方式、通道方式。

程序控制方式又可分为程序查询方式和中断方式两种。

历年真题1.对I/O数据传送的控制方式,可分为程序中断控制方式和独立编址传送控制方式两种。

(2001年)【分析】对1/O数据传送的控制方式,可分为程序直接控制方式、程序中断控制方式、DMA控制方式、通道控制方式等。

程序中断控制方式只是其中的一种方法,独立编址是指对1/O设备的控制寄存器、数据寄存器、状态寄存器等单独进行地址编排,使用专门的指令对其进行操作,可用在各种数据传送的控制方式中。

计算机组成原理第7章习题指导

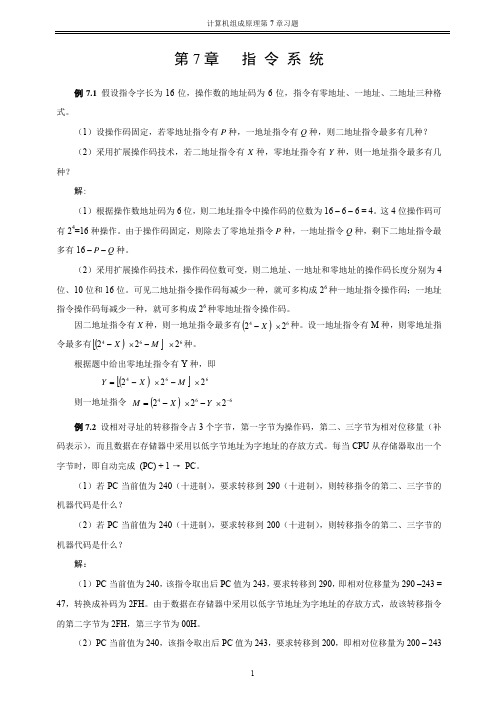

第7章 指 令 系 统例7.1 假设指令字长为16位,操作数的地址码为6位,指令有零地址、一地址、二地址三种格式。

(1)设操作码固定,若零地址指令有P 种,一地址指令有Q 种,则二地址指令最多有几种?(2)采用扩展操作码技术,若二地址指令有X 种,零地址指令有Y 种,则一地址指令最多有几种?解:(1)根据操作数地址码为6位,则二地址指令中操作码的位数为16 – 6 – 6 = 4。

这4位操作码可有24=16种操作。

由于操作码固定,则除去了零地址指令P 种,一地址指令Q 种,剩下二地址指令最多有16 – P – Q 种。

(2)采用扩展操作码技术,操作码位数可变,则二地址、一地址和零地址的操作码长度分别为4位、10位和16位。

可见二地址指令操作码每减少一种,就可多构成26种一地址指令操作码;一地址指令操作码每减少一种,就可多构成26种零地址指令操作码。

因二地址指令有X 种,则一地址指令最多有()6422×−X 种。

设一地址指令有M 种,则零地址指令最多有()[]664222×−×−M X 种。

根据题中给出零地址指令有Y 种,即()[]664222×−×−=M X Y则一地址指令 ()664222−×−×−=Y X M例7.2 设相对寻址的转移指令占3个字节,第一字节为操作码,第二、三字节为相对位移量(补码表示),而且数据在存储器中采用以低字节地址为字地址的存放方式。

每当CPU 从存储器取出一个字节时,即自动完成 (PC) + 1 → PC 。

(1)若PC 当前值为240(十进制),要求转移到290(十进制),则转移指令的第二、三字节的机器代码是什么?(2)若PC 当前值为240(十进制),要求转移到200(十进制),则转移指令的第二、三字节的机器代码是什么?解:(1)PC 当前值为240,该指令取出后PC 值为243,要求转移到290,即相对位移量为290 –243 = 47,转换成补码为2FH 。

计算机组成原理第四版课后题答案七,八章

第七章1. 计算机的外围设备是指()A.输入/ 输出设备 B. 外存储器C. 输入/输出设备及外存储器D. 除了CPU和内存以外的其他设备解:D2.打印机根据印字方式可以分为()和()两大类,在()类打印机中,只有()型打印机能打印汉字,请从下面答案中选择填空。

A.针型打印机B. 活字型打印机C. 击打式D. 非击打式解:C D C A7.试推导磁盘存贮器读写一块信息所需总时间的公式。

解:设读写一块信息所需总时间为Tb,平均找道时间为Ts,平均等待时间为TL,读写一块信息的传输时间为Tm,则:Tb=Ts+TL+Tm。

假设磁盘以每秒r 转速率旋转,每条磁道容量为N 个字,则数据传输率=rN 个字/ 秒。

又假设每块的字数为n,因而一旦读写头定位在该块始端,就能在Tm≈(n / rN )秒的时间中传输完毕。

TL是磁盘旋转半周的时间,TL=(1/2r )秒,由此可得:Tb=Ts+1/2r +n/rN 秒8.某磁盘存贮器转速为3000 转/ 分,共有4 个记录面,每毫米5 道,每道记录信息为12288 字节,最小磁道直径为230mm,共有275 道。

问:(1)磁盘存贮器的容量是多少?(2)最高位密度与最低位密度是多少?(3)磁盘数据传输率是多少?(4)平均等待时间是多少?(5)给出一个磁盘地址格式方案。

解:(1)每道记录信息容量= 12288 字节每个记录面信息容量= 275 × 12288 字节共有4 个记录面,所以磁盘存储器总容量为:4 ×275×12288字节= 13516800 字节(2)最高位密度D1按最小磁道半径R1计算(R1 = 115mm):D1 = 12288 字节/ 2 πR1 = 17 字节/ mm 最低位密度D2 按最大磁道半径R2计算:R2 = R1 + (275 ÷ 5)= 115 + 55 = 170mmD2 = 12288 字节/ 2 πR2 = 11.5 字节/ mm(3)磁盘传输率C = r · Nr = 3000 / 60 = 50 周/ 秒N = 12288 字节(信道信息容量)C = r · N = 50 × 12288 = 614400 字节/ 秒(4)平均等待时间= 1/2r = 1 / (2 ×50) = 10 毫秒(5)磁盘存贮器假定只有一台,所以可不考虑台号地址。

计算机组成原理第7章作业答案PPT培训课件

虚拟存储器

一种将内存和外存统一管理的技术,使得用 户无需关心物理内存和外存的界限,方便程 序的编写和运行。

04 指令系统

指令格式与寻址方式

指令格式

指令格式包括操作码和地址码两部分,操作 码表示指令的操作类型,地址码表示操作数 所在内存单元的地址。

寻址方式

寻址方式是指确定操作数所在内存单元地址 的方式,包括直接寻址、间接寻址、寄存器

要点二

指令优化

为了提高指令执行效率,可以采用多种优化技术,如流水 线技术、分支预测、动态调度等。其中流水线技术可以将 指令执行过程划分为多个阶段,并行处理多个指令;分支 预测可以预测分支指令的执行路径,减少分支带来的时间 开销;动态调度可以根据指令的特性动态调整指令执行顺 序,提高指令的并行度。

05 中央处理器

重点与难点回顾

重点回顾

该部分对本章的重点内容进行了回顾,包括计算机组成 原理的基本概念、计算机系统的层次结构、指令系统、 中央处理器、存储器等。

难点回顾

该部分对本章的难点内容进行了回顾,包括计算机组成 原理的实现细节、指令执行的时序控制、流水线技术等 。

学习建议与展望

学习建议

该部分给出了一些学习建议,包括如何加深对计算机 组成原理的理解、如何提高解题能力等。

寻址、基址寻址和变址寻址等。

指令集与指令的功能

指令集

指令集是计算机中所有指令的集合,包括算术运算、 逻辑运算、控制转移等指令。

指令的功能

指令的功能是指指令所能完成的操作类型,如加法、 减法、乘法、除法、逻辑运算、控制转移等。

指令执行流程与优化

要点一

指令执行流程

指令执行流程包括取指令、解码、执行、访存和写回等阶 段,其中取指令阶段是从内存中取出指令并存放到CPU的 指令寄存器中;解码阶段是将指令操作码转换成相应的控 制信号;执行阶段是完成指令所描述的操作;访存阶段是 访问内存以获取操作数;写回阶段是将结果写回到内存或 寄存器中。

计算机组成原理习题答案第七章

期平均包含4个时钟周期,该机的平均指令执行速度为0.8MIPS,试问:

(1)平均指令周期是多少μs?

(2)平均每个指令周期含有多少个机器周期?

(3)若改用时钟周期为0.4μs的CPU芯片,则计算机的平均指令执行速度又是多少MIPS?

10.CPU中指令寄存器是否可以不要?指令译码器是否能直接对存储器数据寄存器MDR中的信息译码?为什么?请以无条件转移指令JMP A为例说明。

解:指令寄存器不可以不要。指令译码器不能直接对MDR中的信息译码,因为在

取指周期MDR的内容是指令,而在取数周期MDR的内容是操作数。以JMP A指令为

例,假设指令占两个字,第一个字为操作码,第二个字为转移地址,它们从主存中取出时都

1.控制器有哪几种控制方式?各有何特点?

解:控制器的控制方式可以分为3种:同步控制方式、异步控制方式和联合控制方式。同步控制方式的各项操作都由统一的时序信号控制,在每个机器周期中产生统一数目的节拍电位和工作脉冲。这种控制方式设计简单,容易实现;但是对于许多简单指令来说会有较多的空闲时间,造成较大数量的时间浪费,从而影响了指令的执行速度。异步控制方式的各项操作不采用统一的时序信号控制,而根据指令或部件的具体情况决定,需要多少时间,就占用多少时间。异步控制方式没有时间上的浪费,因而提高了机器的效率,但是控制比较复杂。

MDR→MM

Acc+1→Acc;恢复Acc

(4)STORE(存数)指令:

取指令微操作略。

A→MAR;Acc中的数据写

入主存单元

Acc→MDR,WRITE

MDR→MM

12.某计算机的CPU内部结构如图6唱22所示。两

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4

4

4

4

OP

A1

A2

A3

解题思路:以三地址指令格式为

该指令系统的基本格式。以此格式为 基础,采用扩展操作码技术,设计出 题意所要求的地址码结构的指令。

指令操作码分配方案如下:

第 5 张幻灯片

指令操ቤተ መጻሕፍቲ ባይዱ码分配方案

4位OP 0000, ……, A1,A2,A3;8条三地址指令 01目11,录 1000,0000, …10上…00一,,页…11…11,, A2,A3;16条二地址指令 10下01一,页0000,0000, …退…,出……,……, A3;100条一地址指令 1001,0110,0011, 1001,0110,0100, ……,……,……, 冗余编码 1001,1111,1111, 可用来扩充一、零地址指令条数 1010, ……, 冗余编码 1111, 可用来扩充三、二、一、零地址指令条数

FFH ECH

第 14 张幻灯片

目录

上一页 下一页 退出

16. 某机主存容量为4M16位,且存 储字长等于指令字长,若该机指令系统 可完成108种操作,操作码位数固定, 且具有直接、间接、变址、基址、相对、 立即等六种寻址方式,试回答以下问题。

(1)画出一地址指令格式并指出 各字段的作用。

(2)该指令直接寻址的最大范围。 (3)一次间接寻址和多次间接寻 址的寻址范围。 (4)立即数的范围(十进制表 示)。

第 15 张幻灯片

目录

执行JMP后PC各为: EA1= 200AH EA2 = 1FF7H

请参考课件上的例子。

第 13 张幻灯片

目录

上一页 下一页 退出

15.解: +35-3 = 20H -17-3 = ECH

当取出JZ指令时,PC的内容变为 4003H。由于数据在存储器中采用以 高字节地址为字地址的存放方式故 此时转移指令第二、三字节内容各 为: 00H 20H

一地址格式的另一个操作数通常可采用隐含寻址。

举例参照P312.

第 3 张幻灯片

目5.解录:二地址指令操作数的物理地址用地址码给 出,可以是主存的地址,也可以是寄存器的地址, 上甚一至页 可以是I/O设备的地址。(P302)

下一页 退出

第 4 张幻灯片

目录

上一页 下一页 退出

6. 某指令系统字长为16位,地址 码取4位,试提出一种方案,使该指 令系统有8条三地址指令、16条二地 址指令、100条一地址指令。

A

(公操作)

第 11 张幻灯片

目录

上一页 下一页 退出

14. 设相对寻址的转移指令占两个 字节,第一个字节是操作码,第二个 字节是相对位移量,用补码表示。假 设当前转移指令第一字节所在的地址 为2000H,且CPU每取出一个字节便自 动完成(PC)+1PC的操作。试问当 执行“JMP *+8”和“JMP *-9”指令时, 转移指令第二字节的内容各为多少?

解:1)若采用定长操作码时,二 地址指令格式如下:

4

6

6

OP

A1

A2

此时,无论指令中有几个地址, 指令格式都不变。

第 8 张幻灯片

目录

上一页 下一页 退出

设二地址指令有K种,则: K=24-M-N 当M=1(最小值),N=1(最小值) 时,二地址指令最多有:

Kmax=16-1-1=14种 2)若采用变长操作码时,二地址指 令格式仍如1)所示,但操作码长度可随 地址码的个数而变。此时,

一地址指令条数 =3×26 =192条

第 7 张幻灯片

目录

上一页 下一页 退出

8. 某机指令字长16位,每个操作 数的地址码为6位,设操作码长度固定,

指令分为零地址、一地址和二地址三

种格式。若零地址指令有M种,一地 址指令有N种,则二地址指令最多有

几种?若操作码位数可变,则二地址

指令最多允许有几种?

解:据题意,相对寻址的转移指令 格式如下:

2000H 2001H 2002H

OP A

第 12 张幻灯片

目录

上一页 下一页 退出

当取出JMP指令时,PC的内容变 为2002H。此时转移指令第二字节内容 各为:

A1= 0000 0110 = 06H(6) A2= 1111 0101 = F5H(-11)

目解录:由于本题未指定数据通路结构,因此只能大

概地排一下信息流程图,并且流程图中突出寻址过程

的实上一现页。

下A一D页D *-5指令信息流程图如下:

退出

A

取指令(省)

EA MAR,读

寻址计算: EA=(PC)-5 =4000H+FFFBH =3FFBH

M(EA) MDR

(ACC)+(MDR) ACC

( M/26向上取整)。 零地址指令条数为: M = 216 - 212K - 26N; 当K最大时(K=15),一地址指令 最多有: Nmax=64 - 1=63种; 零地址指令最多有: Mmax=64种

注意:应首先根据题意画出指令 基本格式。

第 10 张幻灯片

13. 画出执行“ADD *-5”指令(*为相对寻址特征) 的信息流程图。设另一个操作数和结果存于ACC中, 并假设(PC)=4000H。

K= 24 -(N/26 + M/212 ); (N/26 + M/212 向上取整)

当(N/26 + M/212 ) 1时,K最大, 则二地址指令最多有:

Kmax=16-1=15种(只留一种编码作扩 展标志用。)

第 9 张幻灯片

目录

上一页 下一页 退出

讨论:此时,一地址指令条数为: N=(24 - K)×26 - M/26;

第 6 张幻灯片

目录

上一页 下一页 退出

7. 设指令字长为16位,采用扩展操 作码技术,每个操作数的地址为6位。 如果定义了13条二地址指令,试问还可 安排多少条一地址指令?

解:二地址指令格式如下:

4

6

6

OP

A1

A2

设二地址指令格式为该指令系统 的基本格式,4位操作码共有16种编码 ,其中13种用来定义二地址指令,还 剩3种可用作扩展标志。如不考虑零地 址指令,该指令系统最多还能安排:

指令系统

第七章

目作业录 题: 3,4,5,6,7,8,13,14,15,16,20,21

上一页 下一页 退出

第 2 张幻灯片

目3. 录

指令字长:7.1.2节(P304) 上机一器页 字长:1.3.1节(P17) 下存一储页 字长:P13

退出

4.解:

零地址指令的操作数的地址隐含在堆栈指针SP 中(P303)