Solutions - Loop Gain an... Analog Control Systems

高性能视频放大器AD8010使用手册说明书

REV.AInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication oraAD8010One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781/329-4700World Wide Web Site: 200 mA Output Current High Speed AmplifierCONNECTION DIAGRAMS8-Lead DIP and SOIC87651234NC = NO CONNECTNC –IN +IN NC +V S OUT NC–V S AD801016-Lead Wide Body SOIC161514131234NC = NO CONNECTNC –IN +IN NC +V S OUT NC –V S 12111095678NC NC NC NC NC NC NC NCAD8010V IN+5V–5V75⍀75⍀AD8010R TR GR FR SFigure 1.Video Distribution AmplifierPRODUCT DESCRIPTIONThe AD8010 is a low power, high current amplifier capable of delivering a minimum load drive of 175 mA. Signal performance such as 0.02% and 0.03° differential gain and phase error is maintained while driving eight 75 Ω back terminated video lines.The current feedback amplifier features gain flatness to 60 MHz and –3 dB (G = +1) signal bandwidth of 230 MHz and only requires a typical of 15.5 mA supply current from ±5 V supplies.These features make the AD8010 an ideal component for Video Distribution Amplifiers or as the drive amplifier within high data rate Digital Subscriber Line (VDSL and xDSL) systems.The AD8010 is an ideal component choice for any application that needs a driver that will maintain signal quality when driving low impedance loads.The AD8010 is offered in three package options: an 8-lead DIP,16-lead wide body SOIC and a low thermal resistance 8-lead SOIC, and operates over the industrial temperature range of –40°C to +85°C.FEATURES200 mA of Output Current 9 ⍀ LoadSFDR –54 dBc @ 1 MHzDifferential Gain Error 0.04%, f = 4.43 MHz Differential Phase Error 0.06؇, f = 4.43 MHzMaintains Video Specifications Driving Eight Parallel 75 ⍀ Loads0.02% Differential Gain 0.03؇ Differential Phase0.1 dB Gain Flatness to 60 MHz THD –72 dBc @ 1 MHz, R L = 18.75 ⍀IP3 42 dBm @ 5 MHz, R L = 18.75 ⍀1 dB Gain Compression 21 dBm @ 5 MHz, R L = 100 ⍀230 MHz –3 dB Bandwidth, G = +1, R L = 18.75 ⍀800 V/s Slew Rate, R L = 18.75 ⍀25 ns Settling Time to 0.1%Available in 8-Lead DIP, 16-Lead Wide Body SOIC and Thermally Enhanced 8-Lead SOIC APPLICATIONSVideo Distribution Amplifier VDSL, xDSL Line Driver Communications ATEInstrumentation查询AD8010供应商捷多邦,专业PCB打样工厂,24小时加急出货AD8010–SPECIFICATIONS(@ +25؇C, V S = ؎5 V, G = +2, R L = 18.75 ⍀, R S+ = 150 ⍀, R F = R G = 604 ⍀ (R-16), R F = R G = 562 ⍀ (N-8), R F = R G = 499 ⍀ (R-8). T MIN = –40؇C, T MAX = +85؇C unless otherwise noted)M odel Conditions Min Typ Max Units DYNAMIC PERFORMANCE–3 dB Bandwidth G = +1, V OUT = 0.2 V p-p180230MHzG = +2, V OUT = 0.2 V p-p130190MHz0.1 dB Bandwidth V OUT = 0.2 V p-p3060MHzLarge Signal Bandwidth V OUT = 4 V p-p90MHz Peaking V OUT = 0.2 V p-p, < 5 MHz0.02dB Slew V OUT = 2 V p-p800V/µs Rise and Fall Time V OUT = 2 V p-p 2.0ns Settling Time0.1%, V OUT = 2 V p-p25ns NOISE/HARMONIC PERFORMANCEDistortion V OUT = 2 V p-p2nd Harmonic 1 MHz–73dBc5 MHz–58dBc10 MHz–53dBc10 MHz, R L = 39 Ω–67dBc20 MHz–44dBc3rd Harmonic 1 MHz–77dBc5 MHz–63dBc10 MHz–57dBc10 MHz, R L = 39 Ω–63dBc20 MHz–50dBcIMD 5 MHz ∆f = 10 kHz–73dBc IP3 5 MHz42dBm1 dB Gain Compression 5 MHz21dBmInput Noise Voltage f = 10 kHz2nV√Hz Input Noise Current f = 10 kHz, +In3pA√Hzf = 20 kHz, –In20pA√HzDifferential Gain f = 4.43 MHz, R L = 150 Ω0.02%f = 4.43 MHz, R L = 18.75 Ω0.02%Differential Phase f = 4.43 MHz, R L = 150 Ω0.02Degreesf = 4.43 MHz, R L =18.75 Ω0.03Degrees DC PERFORMANCEInput Offset Voltage512mVT MIN–T MAX15mV Offset Drift10µV/°C Input Bias Current (–)10135µAT MIN–T MAX200µA Input Bias Current (+)612µAT MIN–T MAX20µA INPUT CHARACTERISTICSInput Resistance+Input125kΩ–Input12.5ΩInput Capacitance 2.75pF Common-Mode Rejection Ratio V CM = ±2.5 V5054dB Input Common-Mode Voltage Range±2.5V Open Loop Transresistance V OUT = ±2.5 V300500kΩT MIN–T MAX250kΩOUTPUT CHARACTERISTICSOutput Voltage SwingR L = 18.75 Ω±2.1±2.5V R L = 150 Ω±2.7±3.0V Output Current R L = 9 Ω175200mA Short-Circuit Current240mA Capacitive Load Drive40pF POWER SUPPLYOperating Range±4.5±6.0V Quiescent Current15.517mAT MIN to T MAX20mA Power Supply Rejection Ratio+V S = +4 V to +6 V, –V S = +5 V6066dB+V S = +5 V, –V S = –4 V to –6 V5056dBAD8010ABSOLUTE MAXIMUM RATINGS 1Supply␣Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12.6␣V Internal␣Power␣Dissipation 2Plastic␣Package (N) . . . . . . .Observe Power Derating Curves Small␣Outline␣Package (R) . .Observe Power Derating Curves Wide Body SOIC (R-16) . . . .Observe Power Derating Curves Input Voltage (Common-Mode) . . . . . . . . . . . . . . . . . . . .±V S Differential␣Input␣Voltage . . . . . . . . . . . . . . . . . . . . . .±1.2␣V Output Short Circuit Duration.␣. . . . . . . . . . . . . . . . . . . . . .Observe Power Derating Curves Storage Temperature Range N, R . . . . . . . .–65°C to +125°C Operating Temperature Range (A Grade) . . .–40°C to +85°C Lead Temperature Range (Soldering␣10␣sec) . . . . . . . .+300°CNOTES1Stresses above those listed under Absolute Maximum Ratings may cause perma-nent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.2Specification is for device in free air:8-Lead Plastic Package: θJA = 90°C/Watt 8-Lead SOIC Package: θJA = 122°C/Watt 16-Lead SOIC Package: θJA = 73°C/WattAMBIENT TEMPERATURE – ؇C–50M A X I M U M P O W E R D I S S I P A T I O N – W a t t s–40–30–20–100102030405060708090Figure 2.Plot of Maximum Power Dissipation vs. TemperatureCAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test equipment and can discharge without detection.Although the AD8010 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.ORDERING GUIDEModelTemperature Range Package Description Package Options AD8010AN –40°C to +85°C 8-Lead Plastic DIP N-8AD8010AR –40°C to +85°C 8-Lead Plastic SOICSO-8AD8010AR-16–40°C to +85°C16-Lead Wide Body SOIC R-16AD8010AR-REEL REEL SOIC 13" REEL AD8010AR-REEL7REEL SOIC 7" REEL AD8010AR-16-REEL REEL SOIC 13" REEL AD8010AR-16-REEL7REEL SOIC7" REELMAXIMUM POWER DISSIPATIONThe maximum power that can be safely dissipated by the AD8010 is limited by the associated rise in junction tempera-ture. The maximum safe junction temperature for plasticencapsulated devices is determined by the glass transition tem-perature of the plastic, approximately +150°C. Temporarily exceeding this limit may cause a shift in parametric perfor-mance due to a change in the stresses exerted on the die by the package. Exceeding a junction temperature of +175°C for an extended period can result in device failure.While the AD8010 is internally short circuit protected, this may not be sufficient to guarantee that the maximum junction temperature (+150°C) is not exceeded under all conditions. To ensure proper operation, it is necessary to observe the maximum power derating curves.AD8010dG (%)/d – Degrees60300.130.01P E R C E N T A G E O F U N I T S0.020.030.040.050.060.070.080.090.100.110.12504020100Figure 3.Distribution of Differential Gain (dG) andDifferential Phase (d φ); R L = 18.75 ΩFREQUENCY – MHzH A R M O N I C D I S T O R T I O N – d B cFigure 4.Harmonic Distortion vs. Frequency; G = +2Figure 5.Gain Flatness vs. Frequency Over Temperature (–40°C to +85°C)NUMBER OF VIDEO LOADS0.050.041624681012140.030.020.01D I F F E R E N T I A L G A I N – %10.100.080.060.040.02D I F FE R E N T I A LP H A S E – D e g r e e sFigure 6.Differential Gain and Phase vs. Number of Video Loads Over Temperature (–40°C to +85°C); f = 4.43 MHzFigure 7.Two-Tone, 3rd Order IMD Intercept vs.Frequency; G = +2, RL = 18.75 Ω6.56.46.36.26.16.05.95.85.75.65.5FREQUENCY – MHzG A I N F L A T N E S S – d BFigure 8.Gain Flatness vs. Frequency vs. Number of Video Loads–Typical Performance CharacteristicsAD8010FREQUENCY – MHzI N T E R M O D U L A T I O N D I S T O R T I O N – d B mFigure 9.Intermodulation DistortionP OUT – dBm–35–75–105–1012–8T O T A L H A R M O N I C D I S T O R T I O N – d B c–6–4–2246810–45–55–85–95–65Figure 10.Total Harmonic Distortion vs. P OUT ; G = +2FREQUENCY – MHz21–7N O R M A L I Z E D G A I N – d B0–1–6–2–3–4–5 Figure 11.Small Signal Closed-Loop Frequency Response; R L = 18.75ΩFREQUENCY – MHz10123456789–10–90P M E A S U R E – d B m–50–60–70–80–30–40–20Figure 12. Multitone Distortion; R L = 100 ΩLOAD – ⍀–55–60–65–70–75–80–85–9015100200300400500H A R M O N I C D I S T O R T I O N – d B cFigure 13.Harmonic Distortion vs. LoadFigure 14.Closed-Loop Frequency Response vs. Number of Video LoadsAD8010FREQUENCY – MHz–10–200.035000.1P S R R – d B110100–30–40–80–50–60–70Figure 15.PSRR vs. FrequencyFREQUENCY – MHz0.15001C L O S ED -L O O P O U T P U T RE S I S T A N C E – ⍀1010031010031103.110.310.1Figure 16.Closed-Loop Output Resistance vs. FrequencyFREQUENCY – MHz21N O R M A L I Z E D G A I N – d B–1–2–7–3–4–5–60Figure rge Signal Frequency Response; V O = 2 V p-pFREQUENCY – MHz0.15001C M R R – d B101000–10–100–20–30–40–50–60–70–80–90Figure 18.CMRR vs. FrequencyFREQUENCY – Hz3160.31610k1G100kT R A N S R E S I S T A N C E – k ⍀1M 10M 100M10031.6103.16190P H A S E – D e g r e e s451000Figure 19.Transresistance and Phase vs. Frequency;R L = 18.75 ΩFREQUENCY – MHz0.1N O R M A L I Z E D G A I N – d B1003.02.0–7.01.00.0–1.0–2.0–3.0–4.0–5.0–6.0Figure rge Signal Frequency Response; V O = 4 V p-pAD8010Figure 21.Small-Signal Pulse Response; G = +1Figure 22.Small-Signal Pulse Response; G = +2, –110010FREQUENCY – Hz 1k 1010010k 100k 1M 1I N P U T V O L T A G EN O I S E – n V / H z10MFigure 23.Input Voltage Noise vs. FrequencyV O L T SFigure rge-Signal Pulse Response; G = +1Figure 25.Large-Signal Pulse Response; G = +2, –1100101FREQUENCY – HzI N P U T C U R R E N T N O I S E – P A H z1000Figure 26.Input Current Noise vs. FrequencyAD8010V O L T SFigure 27.Overdrive Recovery; G = +6OVERDRIVE RECOVERYOverdrive of an amplifier occurs when the output and/or input range are exceeded. The amplifier must recover from this over-drive condition. As shown in Figure 27, the AD8010 recovers within 35 ns from negative overdrive and within 75 ns from positive overdrive.THEORY OF OPERATIONThe AD8010 is a current feedback amplifier optimized for high current output while maintaining excellent performance with respect to flatness, distortion and differential gain/phase. As a video distribution amplifier, the AD8010 will drive up to 12parallel video loads (12.5 Ω) from a single output with 0.04%differential gain and 0.04° differential phase errors. This means that, unlike designs with one driver per output, any output is a true reflection of the signal on all other outputs.The high output current capability of the AD8010 also make it useful in xDSL applications. The AD8010 can drive a 12.5 Ωsingle-ended or 25 Ω differential load with low harmonic distor-tion. This makes it useful in designs that utilize a step-up trans-former to drive a twisted-pair transmission line.To achieve these levels of performance special precautions with respect to supply bypassing are recommended (Figure 29). This configuration minimizes the contribution from high frequency supply rejection to differential gain and phase errors as well as reducing distortion due to harmonic energy in the power supplies.R S – ⍀205C A P A C I T I V E L O AD – p F1015Figure 28.Capacitive Load Drive vs. Series Resistor for Various GainsDriving Capacitance LoadsThe AD8010 was designed primarily to drive nonreactive loads.If driving loads with a capacitive component is desired, best frequency response is obtained by the addition of a small series resistance as shown in Figure 28. The inset figure shows the optimum value for R SERIES vs. capacitive load. It is worth noting that the frequency response of the circuit when driving large capacitive loads will be dominated by the passive roll-off of R SERIES and C L.LAYOUT CONSIDERATIONSThe specified high speed performance of the AD8010 requires careful attention to board layout and component selection.Proper R F design techniques and low-pass parasitic component selection are necessary.The PCB should have a ground plane covering all unused por-tions of the component side of the board to provide low imped-ance path. The ground plane should be removed from the area near the input pins to reduce the parasitic capacitance.Figure 29.Standard Noninverting Closed-Loop Configura-tion with Recommended Bypassing TechniqueThe standard noninverting closed-loop configuration with the recommended power supply bypassing technique is shown in Figure 29. Ferrite beads (Amidon Associates, Torrance CA,Part Number 43101) are used to suppress high frequency power supply energy on the DUT supply lines at the DUT. C1 and C2each represent the parallel combination of a 47 µF (16 V) tanta-lum electrolytic capacitor, a 10 µF (10 V) tantalum electrolytic capacitor and a 0.1 µF ceramic chip capacitor. Connect C1from the +V S pin to the –V S pin. Connect C2 from the –V S pin to signal ground.The feedback resistor should be located close to the inverting input pin in order to keep the parasitic capacitance at this node to a minimum. Parasitic capacitances of less than 1 pF at the inverting input can significantly affect high speed performance.Stripline design techniques should be used for long traces (greater than about 3 cm). These should be designed with a characteristic impedance (Z O ) of 50 Ω or 75 Ω and be properly terminated at each end.AD8010APPLICATIONSVideo Distribution AmplifierThe AD8010 is optimized for the specific function of providing excellent video performance when driving multiple video loads in parallel. Significant power is saved and heat sinking is greatly simplified because of the ability of the AD8010 to obtain this performance when running on a ±5 V supply. However, due to the high currents that flow when driving many parallel video loads, special layout and bypassing techniques are required to assure optimal performance.When designing a video distribution amplifier with the AD8010, it is very important to keep in mind where the high (ac) currents will flow. These paths include the power supply pins of the chip along with the bypass capacitors and the return path for these capacitors, the output circuits and the return path of the output current from the loads.In general, any loops that are formed by any of the above paths should be made as small as possible. Large loops are both gen-erators and receivers of magnetic fields and can cause undesired coupling of signals that lowers the performance of the amplifier.Effects that have not been seen before in other op amp circuits might arise because of the high currents. Most op amp circuits output, at most, tens of milliamps and do not require extremely tight video specifications, while a video distribution amplifier can output hundreds of milliamps and require extremely low differential gain and phase errors.The bypassing scheme that is used for the AD8010 requires special attention. It was found that the conventional technique of bypassing each power pin individually to ground can have an adverse effect on the differential phase error of the circuit. The cause of this is attributed to the fact that there is an internal compensation capacitor in the AD8010 that is referenced to the negative supply.The recommended technique is to connect parallel bypass capacitors from the positive supply to the negative supply and then to bypass the negative supply to ground. For high fre-quency bypassing, 0.1 µF ceramic capacitors are recommended.These should be placed within a few millimeters of the power pins and should preferably be chip type capacitors.The high currents that can potentially flow through the power supply pins require large bypassing capacitors. These should be low inductance tantalum types and at least 47 µF. The ground side of the capacitor that bypasses the negative supply should be brought to a single point ground that is the common for the returns of the outputs.Figure 30 shows a circuit for making an N-channel video distri-bution amplifier. As a practical matter, the AD8010 can readily drive eight standard 150 Ω video loads. When driving up to 12video loads, there is minimal degradation in video performance.Another important consideration when driving multiple cables is the high frequency isolation between the outputs of the cables. Due to its low output impedance, the AD8010 achieves better than 46 dB of output-to-output isolation at 5 MHz driv-ing back terminated 75 Ω cables.Figure 30.An N-Channel Video Distribution Amplifier Using An AD8010.NOTE: Please see Figure 29 for Recommended Bypassing Technique.V L1L2LNAD8010Differential Line DriverTwisted pair transmission lines are more often being used for high frequency analog and digital signals. Over long distances,however, the attenuation characteristics of these lines can degrade the performance of the transmission system. To com-pensate for this, larger signals are transmitted, which after the attenuation, will still have useful signal strength.The high output current of two AD8010s can be used along with a transformer to create a high power differential line driver.The differential configuration effectively doubles the output swing, while the step-up transformer further increases the out-put voltage.In the circuit in Figure 31 the A device is configured as a gain-of-two follower, while the B device is a gain-of-two inverter.These will produce a differential output signal whose maximum value is twice the peak-to-peak value of the maximum output of one device. For this circuit a 12 V peak-to-peak output can be obtained.The op amps drive a 1:2 step-up transformer that drives a 100 Ω transmission line. Since the impedance reflected back to the primary varies as the square of the turns ratio, it will appear as 25 Ω at the primary. This source terminating resistor is split as a 12.4 Ω resistor at the output of each device.The circuit shown is capable of delivering 12 V p-p to the line and operates with a –3 dB bandwidth of 40 MHz. The peak current output of either op amp is 100 mA.Figure 31.High Output Differential Line Driver Using Two AD8010s.NOTE: Please see Figure 29 for Recommended Bypassing Technique.V ⍀AD8010 Closed-Loop Gain and BandwidthThe AD8010 is a current feedback amplifier optimized for usein high performance video and data acquisition applications.Since it uses a current feedback architecture, its closed-loop–3 dB bandwidth is dependent on the magnitude of the feed-back resistor. The desired closed-loop bandwidth and gain areobtained by varying the feedback resistor (R F) to set the band-width, and varying the gain resistor (R G) to set the desired gain.The characteristic curves and specifications for this data sheetreflect the performance of the AD8010 using the values of R Fnoted at the top of the specifications table. If a greater –3dB band-width and/or slew rate is required (at the expense of video per-formance), Table I provides the recommended resistor values.Figure 32 shows the test circuit and conditions used to produceTable I.Effect of Feedback Resistor Tolerance on Gain FlatnessBecause of the relationship between the 3 dB bandwidth and thefeedback resistor, the fine scale gain flatness will, to some ex-tent, vary with feedback resistor tolerance. It is therefore recom-mended that resistors with a 1% tolerance be used if it is desiredto maintain flatness over a wide range of production lots. Inaddition, resistors of different construction have different associ-ated parasitic capacitance and inductance. Metal-film resistorswere used for the bulk of the characterization for this data sheet.It is possible that values other than those indicated will be opti-mal for other resistor types.Quality of Coaxial CableOptimum flatness when driving a coax cable is possible onlywhen the driven cable is terminated at each end with a resistormatching its characteristic impedance. If the coax was ideal, then the resulting flatness would not be affected by the length of the cable. While outstanding results can be achieved using inex-pensive cables, it should be noted that some variation in flatness due to varying cable lengths may be experienced.OUTVFigure 32.Test Circuit for Table INOTES1VO= 0.2 V p-p for –3 dB Bandwidth.2VO= 2 V p-p for Slew Rate.3Bypassing per Figure 29.Table I.–3 dB Bandwidth and Slew Rate vs. Closed-Loop Gain and Resistor ValuesPackage: N-8Closed-Loop–3 dB BW Slew Rate Gain R F (⍀)R G (⍀)(MHz) (V/s) +1453∞285900+2374374255900+534886.6200800+1056261.9120550 Package: R-16Closed-Loop–3 dB BW Slew Rate Gain R F (⍀)R G (⍀)(MHz) (V/s) +1412∞245900+2392392220900+539297.6160800+1060466.595550 Package: SO-8Closed-Loop–3 dB BW Slew Rate Gain R F (⍀)R G (⍀)(MHz) (V/s) +1392∞345950+23743743051000+534886.62201000+1049954.9135650OUTLINE DIMENSIONSDimensions shown in inches and (mm).C 3208a –0–10/98P R I N T E D I N U .S .A .AD80108-Lead Plastic Mini-DIP(N-8)PLANE0.014 (0.356)0.045 (1.15)(2.54)BSC0.325 (8.25)0.300 (7.62)0.008 (0.204)8-Lead SOIC (SO-8)PLANE BSC ؇16-Lead Wide Body SOIC(R-16)PLANE0.0138 (0.35)(1.27)BSC0.0091 (0.23)。

GE Grid Solutions 8系列高级馈线控制器产品手册说明书

GEGrid Solutionsimagination at workInnovative Technology& Design• Advanced feeder One Box Solution for protection, control monitoring anddiagnostics of single/dual feeder applications Feeder and Bay Controller Solutions for Industrial and Utility ApplicationsThe Multilin™ 850 relay is a member of the Multilin 8 Series protective relay platform and has been designed for the management, protection and control of feeder applications. The Multilin 850 is used to provide primary (main) or backup protection for underground and overhead single or dual feeders for utility and industrial power networks.With 11 Switchgear control elements, fully configurable Single Line Diagram on a large color graphical display, 36 alarm integrated annunciator panel and 20 push buttons makes the 850 the ideal choice for bay control and protection as a “One Box Solution”.Designed with advanced communications options and detailed asset monitoring capabilities, the Multilin 850 provides advanced functionality, including high-performance protection, extensive programmable logic and flexible configuration capabilities. With support for industry leading communications protocols and technologies, the 850 provides easy integration into new or existing SCADA or DCS for enhanced situational awareness.Key Benefits• One Box Solution with advanced logic and configuration flexibility, providing primary or backup protection for up to 2 feeders or feeders with 2 sets of voltage inputs • User configurable Single Line Diagram on color display for local control, system status, and metering • Advanced breaker diagnostics with comprehensive fault and disturbance recording• Integrated arc flash detection using light sensors supervised by overcurrent to reduce incident energy and equipment damage • Advanced cyber security features including AAA, Radius, RBAC, and Syslog enabling NERC ® CIP requirements • Draw-out design simplifies testing, commissioning and maintenance, increasing process uptime • Patented environmental monitoring, providing visibility to changes in environmental conditions that can affect relay lifeApplications• Single/dual feeder applications for utility, oil & gas, mining & metals, process industry, commercial, and waste water segments • Fast protection pass enabling load shedding schemes • Reliable automatic bus transfer & autoreclose schemes • Bay controller for wide range of switchgear applications • High speed fault detection for arc flash mitigationMultilin 850WARRANTYYEAR850Multilin 850 OverviewThe Multilin 850 is an advanced feeder protection device designed for high performance, protection, control and monitoring of incoming and outgoing feeders.With up to 57 digital inputs and 22 digital outputs in a compact box, the 850 provides a versatile and cost effective control, protection, measurement & monitoring solution. Flexelements and Flexlogic enable users to customize schemes to meet a variety of applications.From dual main to main-standby configurations, the Multilin 850D delivers a more economical and reliable solution, enabling customers to reduce hardware requirements and simplify device integration, including safe and secure Wi-Fi communications for system configuration and diagnostics. Bay Controller/One Box SolutionThe 850 offers comprehensive switchgear control aided by a configurable Single Line Diagram & breaker control. A total of 10 switchgear elements can be displayed and 8 elements controlled. The integrated solution for protection, control, monitoring and diagnostics eliminates the need for other external devices thus offering an integrated solution for switchgear systems. The device supports 6 user programmable pages. The Multilin 850 is an integrated solution that performs protection, control & monitoring of assets, and ease of retrieval of fault & event records. Coordinating remotely with SCADA over multiple communication protocols gives the Multilin 850 an added advantage for fast and efficient management of fault isolation and service restoration.The Multilin 850 is a cost-effective retrofit solutions where individual components of protection, metering, control switches, annunciator & panel mimic can be replaced by only one relay. Switchgear Control and Configurable SLDThe Multilin 850 provides a configurable dynamic SLD up to six (6) pages for comprehensive switchgear control of up to 2 breakers and 9 disconnect switches; including interlocks. Up to 15 digital and metering status elements can be configured per SLD page. These can be configured to show breakers, switches, metering, and status items.Individual SLD pages can be selected for the default home screen pages. Automatic cycling through these pages can also be achieved through default screen settings.The provision of such powerful control and display capability within the relay (“One Box” concept) eliminates the need for external controls, switches and annunciation on the panel reducing equipment and engineering cost. Annunciator Panel and Virtual Push ButtonsThe Multilin 850 offers a configurable annunciator panel that can be constructed to show up to 36 alarms in either self-reset mode or latched mode per ISA 18.1 standard similar to a physical annunciator panel; eliminating the need for a physical one. This removes the need for additional programmable LEDs. The alarms can be displayed on the front panel in a configurable grid layout of 2x2 or 3x3.The Multilin 850 extends the local control functionalities with 20 virtual pushbuttons that can be assigned for various functions. Each programmable pushbutton has its own programmable LED which can be used to acknowledge the action taken by the tab pushbutton.With a fast protection pass, running every 2 msec, the 850 relay provides fast response to current, voltage, power, and frequency protection elements; helping reduce stress on assets. The Multilin 850 supports the latest communication protocols, including DNP, ModBus, IEC 60870-5-103, IEC 62439/PRP and IEC 61850; facilitating easy integration into new or existing SCADA/DCS networks.Functional Block Diagram850 Distribution FeederWith support for up to 8 CT inputs & 2 sets of 4 traditional VT inputs, the 850 can be used for 2 feeders or feeders with 2 sets of voltage inputs, simplifying system architectures and operational costs.The 850 offers redundancy with the same number of devices, enabling:Architecture Simplification - Reduced Number of Devices• Less capital cost • Less O&M costMean Time to Repair - Less than 15 minutes• Field swappable PSU • Draw out construction• Ready to consume service reportsExtended Asset and Relay Life• Built-in Environmental monitoring • Advanced breaker monitoring• TGFD and Cable incipient fault detection/locationSimplified Management - Platform Based Solution• Reduced training needs• Standardized part number across systems • Harmonized look and feel, operational experienceProtection & ControlAs part of the 8 Series family, the Multilin 850 provides superior protection and control. The 850 offers comprehensive protection and control solutions for incoming, outgoing bus-tie/bus-coupler feeders. It contains a full range of selectively enabled, self-contained protection and control elements.The voltage and frequency protection functions detect abnormal system conditions, potentially hazardous to the system. Some of these conditions may consist of over and undervoltage, over and underfrequency, and phase reversal.Fast UnderfrequencyThe 850 has an 8 stage Fast Underfrequency element that measures frequency by detecting the consecutive voltage zero crossings and measuring the time between them. The measured frequency has a range between 20 to 70 Hz. This is useful for performing fast load-shedding when frequency variations from unbalance conditions arise due to:• Inadequate load forecast or deficient generation capacity programming.• Busbars, generator group or interconnection feeders trip.• System splits into islands.FlexCurves™For applications that require greater flexibility, FlexCurves can be used to define custom curve shapes. These curves can be used to coordinate with other feeders to achieve fault selectivity.RTD ProtectionThe Multilin 850 supports up to 13 programmable RTD inputs that can be configured for an Alarm or Trip.The RTDs can be assigned to a group for monitoring ambient temperatures or any other desired temperature. The RTD voting option gives additional reliability to ignore and alarm for any RTD failures.Integrated Arc Flash ProtectionThe Multilin 8 Series supports an integrated arc flash module providing constant monitoring for an arc flash condition within the switchgear, motor control centers, or panelboards. With a 2ms protection pass, the 8 Series is able to detect light and overcurrent using 4 arc sensors connected to the relay. In situations where an arc flash/fault does occur, the relay is able to quickly identify the fault and issue a trip command to the associated breaker thereby reducing the total incident energy and minimizing resulting equipment damage.Self-monitoring and diagnostics of the sensors ensures the health of the sensors as well as the full length fiber cables. LEDs on the front panel display of the 850 can be configured to indicate the health of the sensorsand its connections to the relay.Dual feederRedundant feeder850WANT TO LEARN MORE?EXPLORE IN 3DMV SwitchgearMultilin 8 SeriesFast, reliable arc flash protection with integrated light based arc flash sensors. This delivers detection in as fast as 2 msec, reducing the costs associated with equipment damage and unplanned downtime.Inputs and OutputsThe 850 provides a max of 57 Digital inputs and 22 Digital outputs with an option for 7 Analog Outputs (dc mA), 4 Analog Inputs (dc mA), and 1 RTD input. The configurable analog inputs can be used to measure quantities fed to the relay from standard transducers. Each input can be individually set to measure 4-20 mA, 0-20 mA or 0-1 mA transducer signals.Advanced AutomationThe Multilin 850 incorporates advanced automation capabilities which exceed those found in most feeder protection relays. This reduces the need for additional programmable controllers or discrete control relays including programmable logic, communication, and SCADA devices. Advanced automation also enables seamless integration of the 850 into other protection or process systems (SCADA or DCS).FlexElements™FlexElement is a universal comparator, that can be used to monitor any (analog) actual value measured or calculated by the relay, or a net difference of any two analog (actual) values of the same type.The element can be programmed to respond either to a signal level or to a rate-of-change (delta) over a pre-defined period of time.This can be used to generate special protection or monitoring functions which allow the user to flag a user-defined abnormality to give better visibility to a certain condition.FlexLogic™FlexLogic is the powerful programming logic engine that provides the ability to create customized protection and control schemes, minimizing the need for and associated costs of auxiliary components and wiring. Using FlexLogic, the 850 can be programmed to provide the required tripping logic along with custom scheme logic for feeder control interlocking schemes with adjacent protection (for example, preventing sympathetic tripping of healthy feeders), and dynamic setting group changes.Breaker Health MonitoringThe breaker is monitored by the relay not only for detection of breaker failure, but also for the overall “breaker health” which includes:• Breaker close and breaker open times • Trip circuit monitoring • Spring charging time • Per-phase arcing current • Trip countersAll algorithms provide the user with the flexibility to set up initial breaker trip counter conditions and define the criteria for breaker wear throughouta number of set points.Breaker Health Reporting assists Condition-Based Maintenance and savings in Operational CostsMonitoring & DiagnosticsThe Multilin 850 includes high accuracy metering and recording for all AC signals. Voltage, current, and power metering are built into the relay as a standard feature. Current and voltage parameters are available as total RMS magnitude, and as fundamental frequency magnitude and angle.Environmental MonitoringThe 850 has an Environmental Awareness Module (EAM) to record environmental data over the life of the product. The patented module measures temperature, humidity, surge pulses and accumulates the events every hour in pre-determined threshold buckets over a period of 15 years. This data can be retrieved using the EnerVista Setup Software. This report helps identify the operating condition of the installed fleet so that remedial action can be taken.850Environmental health report is available via Multilin PC SoftwareMeteringThe Multilin 850 offers high accuracy power quality monitoring for fault and system disturbance analysis. It delivers unmatched power system analytics through the following advanced features and monitoring and recording tools:• Harmonics measurement up to 25th harmonic for both currents and voltages including THD.• The length of the transient recorder record ranges from 31 to 1549 cycles (typically half a second to half a minute).• 32 digital points and 16 analog values.• Comprehensive data logger provides the recording of 16 analog values.• Detailed Fault Report. The 850 stores fault reports for the last 16 events. 1024 Event Recorder.CommunicationsThe Multilin 8 Series provides advanced communications technologies for remote data and engineering access, making it easy and flexible to use and integrate into new and existing infrastructures. Direct support for fiber optic Ethernet provides high-bandwidth communications, allowing for low-latency controls and high-speed file transfers of relay fault and event record information. The 850 also supports two independent IP addresses, providing high flexibility for the most challenging of communication networks. Providing several Ethernet and serial port options and supporting a wide range of industry standard protocols, the 8 Series enables easy, direct integration into DCS and SCADA systems. The 8 Series supports the following protocols:• IEC 61850 (8 Clients, 4 Logical Devices, Tx & Rx expansion, Analog GOOSE), IEC 62439 / PRP• DNP 3.0 serial, DNP 3.0 TCP/IP, IEC 60870-5-103, IEC 60870-5-104• Modbus RTU, Modbus TCP/IPThe 850 has two interfaces, a USB front port and Wi-Fi for ease of access to the relay.Wi-Fi Connectivity:• Simplify set-up and configuration• Simplify diagnostic retrieval• Allows personnel to be a safer distance from the front of the switchgear • WPA-2 securityCyber SecurityThe 8 Series delivers a host of cyber security features that help operators to comply with NERC CIP guidelines and regulations.• AAA Server Support (Radius/LDAP)• Role Based Access Control (RBAC)• Event Recorder (Syslog for SEM)Role, User, PasswordEncrypted (SSH)Security ServerCyber Security with Radius AuthenticationPLC / Gateway850869845MM200MM300ControllersReason S20Ethernet SwitchLV Network850 Menu path display indicating location within menu structureSoft menu navigation keysLED status indicatorsGraphic ControlPanel (GCP)Navigation keysFront USB portCaptive screw prevents inadvertent or unauthorized draw-outContext-sensitive menu for fast navigation Front View - Advanced Membrane Front PanelDimensions & MountingStandard serial and RJ45 Ethernet moduleAdvanced communica-tions module (Fiber Optic or Copper ports)CT, VT inputsGrounding screwPower supplyRTDsDigital I/O, DCmA, Arc Flash sensorsRear ViewEXPLORE IN 3D8.42”9.90”1.55”7.55”Optional IP20 cover available10 User-ProgrammablePush Buttons850 850D Wiring DiagramACCESS POINT850 850E Wiring DiagramPHASE CTsDIRECTION OF POWER FLOW FOR POSITIVE WATTS POSITIVE DIRECTION OF LAGGING VARSD9C O MN NINSTRUCTION MANUALSEE VT WIRING INCONNECTIONWYE VT INSTRUCTION MANUALINPUT WIRING INSEE GROUND 52b52a850-E Industrial Feeder Protection SystemJ9 J10 J11 J12 J13 J14OPEN DELTA VT CONNECTIONN N A I G I sg I C I N B I CANRESRVD 10D8D D745CV B V A V XV X V C V B V A V COMPUTERPERSONAL COMMUNICATIONSD1D2D3D D D6S L O T ASLOTS J & KDA O L CIRCUITCLOSECIRCUITTRIP POWERCONTROL RS485COMMUNICATIONS IRIG-B SLOT F: I/O_AVOLTAGE INPUTSCURRENT INPUTSETHERNETCOMPUTERPERSONAL USBPWR SUPPLY STUDGND BUSGROUND BUS MANUALIN INSTRUCTION MONITORING CLOSE COIL SEE TRIP AND CONTROL POWERSHOWN WITH NO OUTPUT CONTACTS 52F2F1O U T P U T R E L A Y SD I G I T A L I N P U T SVVF24F23F22F12F11F10F9F8F7F6F5F4J16F3RELAYFAILURE CRITICAL AUXILIARY 3CLOSETRIPDN U O R G LA R T U E N EN I L A1A2A3J14J13J12J11J10J9J1 J2 J3 J4 J5 J6 J7 J8 K7 K8G/H2G/H1O U T P U T R E L A Y SG/H24G/H23G/H22G/H12G/H11G/H10G/H9G/H8G/H7G/H6G/H5G/H4G/H3SLOT G OR H: I/O_A* (OPTIONAL)ACCESS POINTJ15AUX VTAUXILIARY 4AUXILIARY 9AUXILIARY 10AUXILIARY 11AUXILIARY 12AUXILIARY 16DCmA I/OANALOG OUTPUTANALOG INPUTRTD12345671234ANY MEASURED OR METEREDANALOG PARAMETER OUTPUTSAMBIENTTEMPERATURE+++++++++++SLOT G: I/O_L (OPTIONAL)A R C F L A S HSLOT H: I/O_F (OPTIONAL)SLOT B OR C: I/O_R OR I/O_S* (OPTIONAL)* SUPPORTS 10 OHM COPPER RTD AS WELL* SLOT H I/O_A IS AVAILABLE WHEN SLOT G IS WITH I/O_LANY MEASURED ORMETERED ANALOG PARAMETER INPUTSCABLE SHIELD TO BE GROUNDED AT PLC/COMPUTER END ONLYRTD RTDFront PanelSLOT D**SLOT ERear PanelC O M850OrderingCONFIGURE ONLINE850* **NN *****A ************N DescriptionAAdvanced - CyberSentry Level 1Note: Harsh Environment Coating is provided as standard on all 8 series units.* HV I/O, Option A - Max 2 across slots F through HArc Flash Detection (Option F): Includes 4 x Arc Flash sensors, each 18 feet (5.5 meters) longIEC is a registered trademark of Commission Electrotechnique Internationale. IEEE is a registeredtrademark of the Institute of Electrical Electronics Engineers, Inc. Modbus is a registered trademark ofSchneider Automation. NERC is a registered trademark of North American Electric Reliability Council. NISTis a registered trademark of the National Institute of Standards and Technology.GE, the GE monogram, Multilin, FlexLogic, EnerVista and CyberSentry are trademarks of General ElectricCompany.GE reserves the right to make changes to specifications of products described at any time without notice andwithout obligation to notify any person of such changes.imagination at work GEA-32050(E)Copyright 2018, General Electric Company. All Rights Reserved.。

Loop Gain Crossover Frequency

P ower supplies are one of the last holdouts of trueanalog feedback in electronics. For various rea-sons,including cost,noise,protection,and speed,they have remained this way in the face of thedigital control revolution. And it is likely they will stay this way for decades to come. It is still the easiest and most effective control method for PWM converters.In power supplies,we still measure and characterize the con-trol system in traditional ways– injecting a swept sinusoidal test signal into the components of the system,and measuring the analog response. Unfortunately,most engineers receive little training or guidance in optimizing their systems. Suppose you have a choice of two power supplies for your system– power supplies A and B. Power supply A has a crossover frequency of its control loop of 1 kHz. Power supply B has a crossover frequency of 20 kHz. Which is a better design? The answer is that there is not enough information from which to choose. If power supply A and power supply B meet all other criteria,such as cost,size,efficiency,regula-tion and dynamic loading,the crossover frequency of the control loop is irrelevant.Loop gain crossover has no intrinsic value. It is only useful as a tool to design a power supply that is stable and provides the needed voltage source at its output. If all other criteria were equal,power supply A with the lower loop crossover is the better choice. A more conserva-tive loop crossover frequency is less prone to noise,compo-nent variations,and power supply operating point.So how should loop gain crossover frequency be selected? The answer is complex,depending on several factors:● Power supply topology● Power supply switching frequency● Control method – voltage-mode or current-mode control ● Output capacitor type and characteristics● Power stage componentsWe will lay down the basic boundaries for crossover selec-tion in this article. In the next issue of Switching Power Magazine,we’ll look at other system issues such as reac-tive loading,to see how this affects the design of the loop. This is a very important topic with the proliferation of DC-DC converter modules,many of which expect the user to add substantial output capacitance,but do not give access to the control loop.The Purpose of Loop GainLoop gain is not an end in itself– it is a means to achieve other critical performance measures of a power supply. For most power supplies,the objective is to provide a voltagegain,however,due to the complex frequency characteristics of typical power converters. In this rest of this article,the limits of crossover frequency for practical converters will be defined.Topology EquivalenceThe equations in this article are defined for the classic buck,boost,and flyback converters. They are also applicable with the other converters in the same family. The buck family includes (but is not limited to) the forward,two-switch for-ward,half-bridge,full-bridge and push-pull converters.The boost converter is not usually isolated,but if it is,the equations still apply as long as the inductor value is reflected to the secondary side of the isolation transformer. The fly-back and buck-boost converters also have the same character-istics. With the flyback,the inductor value is the magnetizing inductance of the transformer reflected to the secondary side.Resonant Frequency Lower Crossover LimitIf you are using voltage-mode control and operating in con-tinuous conduction mode (CCM),an LC resonant filter is being driven by the controlled switching action. That filter will naturally ring,and the control must eliminate this. For voltage-mode control,there is only one loop. This loop must have significant gain at the power filter resonant frequency.So,the lower bound must be,for the different converters:C o n t r o l L o o p s● Avoid expensive product Instability● Control loops change with line, load, and temperature ● Optimize control loops to reduce cost and sizeC a p a c i t o r s● Measure essential data not provided by manufacturers ● Select optimum cost, size, shape, and performanceF i l t e r s● Characterize power systems filter building blocks ● Optimize performance at line and control frequencies ● 15 MHz range shows filter effectiveness for EMI performanceM a g n e t i c s● Design and specify more reliable magnetics ● Measure critical parasitic components ● Detect winding and material changes● Characterize component resonances up to 15 MHzP o w e r L i n e H a r m o n i c s● Check IEC compliance for AC input systems ● Measure line harmonics to 10 kHz● Avoid expensive redesign, and minimize test facility time770 640 9024885 Woodstock Rd.USB port compatibility.Designed specifically for switching power supplies, the AP200 makes swept frequency response measurements that give magnitude and phase data plotted versus frequency.1c . This is overdesign,and a penalty will be paid in terms of peak switch current.The RHP zero also constrains crossover for the boost converter.the flyback converter– allow a reasonable amount of ripple current in the inductor to produce a controllable converter.You need to carefully trade off the control loop crossover fre-quency which can be achieved versus the input filter require-ments for filtering the ripple current.Switching Frequency Crossover LimitSwitching power supplies are sampled-data systems. The Nyquist frequency (which is half the switching frequency) isthe absolute limit of information transfer,but you cannot cross over a loop as high as this. A reasonable limit on the crossover frequency is:with noise will arise. As converter switching frequencies have risen in past years from 50 kHz to above 500 kHz,very few power supply designers ever push this upper limit due to the noise complications. Recent developments in fast-response supplies for VRMs (voltage regulator modules for CPU supplies) are starting to push the crossover frequencies closer to this limit.Capacitor ESR Crossover LimitIn many power supplies,the output capacitor determines how effective raising the crossover frequency will be. If your main performance objective is driven by step load require-ments,there is no benefit in raising the crossover frequency above the output capacitor ESR frequency.Figure 1c. Inductor current of flyback converter 100 kHz,DCM,L=8 uHFigure 3a shows the loop gains for a converter,withcrossovers ranging from 500 Hz to 10 kHz. As the crossover frequency is raised from 500 Hz to 5 kHz,the corresponding output overshoot drops significantly from 0.93 V to 0.17 V as shown in Figure 3b . Increasing the loop crossover beyond 5kHz has no effect on the peak overshoot. At this point,the overshoot is simply determined by the output step current value multiplied by the capacitor ESR value.Right Half Plane (RHP) ZerosRHP zeros are a property of a special class of active cir-cuits which have a tendency to respond initially in the wrong direction when given a changed input. Eventually,the output will move in the direction commanded by the input. How fast it starts moving in the right direction is determined by the frequency location of the RHP zero.Boost and flyback converters are very popular circuits in use in the industry today,and both have RHP zero charac-teristics when operating in continuous conduction mode.The cause of the RHP zero for these converters is the same and intuitive. The output capacitor of the converter is charged by the inductor current,but ONLY when the power switch is turned off. An initial increase in duty cycle of the power switch increases the current in the inductor within one cycle,but the net charge to the output capacitor (product of the inductor current and off-time) is initially less. Hence,an increase in command to the system results in a temporary droop in the output voltage.This can be confusing for a controller that is monitoring the output voltage to make control decisions. There is noalternative but to wait and see where the long-term trend is before adjusting the duty cycle.There is no other solution to RHP zeros. Constant on-time,or constant off-time controllers have no effect on their location,and do not improve the controllability of these converters. Other converters can fare even worse results– the Sepic and Cuk converters have a pair of complex RHP zeros which can be extremely difficult to compensate. While these converters may sometimes have their niche applications,be prepared for a longer development time and potential increased cost to solvethese issues.Figure 2. Inductor current and output voltage of boost convert-er with step duty cycle. Duty cycle step from 0.5 to 0.95into converters operating at high switching frequencies. The Array highest loop gain crossover achieved was at 180 kHz,for a 7 MHz zero-voltage-switched quasi-resonant converter. Noise issues,and error amplifier limits prevented higher crossover frequencies.The converter power stage schematic is shown in Figure 7. Operation of the power stage is given in [1]. The control loop used a modified current-mode control scheme to avoid some of the noise problems of current mode control described in the last issue of Switching Power Magazine,and further details of the control circuit are given in [2]. Even using high performance parts,the theoretical phase margin was not achieved with this converter when trying to cross over the loop at 180 kHz. The phase curves should have remained constant for both loop gains,but limits in the feedback com-ponents caused additional phase rolloff as shown.In SummaryLoop gain design is still of great importance to switching power supply designers. Much can be done with the control loop to optimize performance,and reduce costs in the power stage components. Looking at the loop early in the design and checking the potential performance of your power stage with some of the guidelines in this article can help avoid subse-quent costly redesign.There are other issues impacting loop design which are not covered in this paper. The most significant of these are input and output circuitry attached to the converter,usually in the form of input filters and active or reactive loads. These can sub-stantially change the stability of a converter design,and future articles will address these topics.References[1] “Zero-Voltage Switched Buck and Flyback Converters – Experimental Results at 10 MHz”, W.A.Tabisz, P. Gradzki and F.C. Lee, IEEE Transactions on Power Electronics, Vol. 4, No. 2, April 1989.[2] “Multi-Loop Control for Quasi-Resonant Converters”, R.B.Ridley, W.A. Tabisz, F.C. Lee and V. Vorperian, IEEE Transactionson Power Electronics, Vol. 6 No. 1, January 1991.Only Need One Topology?Buy a module at a time ...Buck Converter $295Boost Converter $295Buck-Boost Converter $295Flyback Converter$595Isolated Forward,Half Bridge,$595Full-Bridge,Push-PullModulesA B C D EBundlesPOWER 4-5-6 Features● Power-Stage Designer● Magnetics Designer with core library ● Control Loop Designer● Current-Mode and Voltage-Mode Designer and analysis with most advanced & accurate models ● Nine power topologies for all power ranges ● True transient response for step loads● CCM and DCM operation simulated exactly● Stress and loss analysis for all power components ● Fifth-order input filter analysis of stability interaction ● Proprietary high-speed simulation outperforms any other approach● Second-stage LC Filter Designer ● Snubber Designer● Magnetics Proximity Loss Designer● Semiconductor Switching Loss Designer ● Micrometals Toroid Designer● Design Process Interface accelerated and enhancedBundle A-B-C$595All Modules A-B-C-D-E $1295Roswell, GA 30075 USA。

思科SPA112 2端口电话适配器数据表说明书

Data SheetCisco SPA112 2 Port Phone AdapterAffordable and Feature-Rich Voice over IP (VoIP)HighlightsEliminate compromise on voice quality or features for phone and fax capabilities associated with Internet voice over IP (VoIP) service. Cisco® VoIP solutions provide the quality, peace of mind, and investment protection at an affordable price.Product OverviewThe Cisco SPA112 2 Port Adapter enables high-quality VoIP service with a comprehensive feature set through a broadband Internet connection. Easy to install and use, it works over an IP network to connect analog phones and fax machines to a VoIP service provider and provides support for additional LAN connections.The Cisco SPA112 includes two standard telephone ports to connect existing analog phones or fax machines to a VoIP service provider. Each phone line can be configured independently. With the Cisco SPA112, users can protect and extend their investment in their existing analog telephones, conference speakerphones, and fax machines as well as control their migration to IP voice with an extremely affordable, reliable solution.Compact in design and compatible with international voice and data standards, the Cisco SPA112 can be used with residential, home-office, and small business VoIP service offerings, including full-featured hosted or open source IP PBX environments. This easy-to-use solution delivers advanced features to better connect employees and serve customers, all on a highly secure Cisco network.The Cisco SPA112 2 Port Adapter (Figures 1 and 2):●Enables high-quality VoIP service with a comprehensive feature set through a broadband Internetconnection●Provides high-quality, clear-sounding voice, using advanced voice quality-of-service (QoS) capabilities andthe industry-leading voice Session Initiation Protocol (SIP) stack●Supports reliable faxing with simultaneous voice and data use●Includes two standard telephone ports, each with an independent phone number, for use with fax machinesor analog phone devices●Is compatible with all industry voice and data standards and common telephone features such as caller ID,call waiting, and voicemail●Includes a simple-to-use web-based configuration utility for easy deploymentFigure 1. Cisco SPA112 2 Port AdapterFigure 2. Ports on Cisco SPA112 ATA 2 Port AdapterFeatures and BenefitsThe Cisco SPA112 provides an easy-to-use VoIP solution that offers:●Toll-quality voice and carrier-class feature support: The Cisco SPA112 delivers clear, high-quality voicecommunication under a variety of network conditions. Excellent voice quality in challenging, changeable IP network environments is made possible through the advanced implementation of standard voice codingalgorithms. The Cisco SPA112 is interoperable with common telephony equipment such as fax, voicemail, private branch exchanges (PBXs) and key telephone systems (KTSs), and interactive voice responsesystems.●Large-scale deployment and management: The Cisco SPA112 enables service providers to providecustomized services to their subscribers. It can be remotely provisioned and supports dynamic, in-service software upgrades. A highly secure profile upload saves providers the time and expense of managing and preconfiguring or reconfiguring customer premises equipment (CPE) for deployment.●Outstanding security: The Cisco SPA112 supports highly secure, encryption-based methods forcommunication, provisioning, and servicing.●Compact size: Designed for small spaces, the Cisco SPA112 can be installed as a desktop unit ormounted on a wall.●Comprehensive feature set: The standards-based Cisco SPA112 is compatible with Internet VoIPprovider features such as caller ID, call waiting, voicemail, call forwarding, distinctive ring, and much more to provide a complete, affordable, and highly reliable solution for high-quality VoIP.●Easy installation and changes: The web-based configuration utility enables quick deployment andeasy changes.●Investment protection: Businesses that are growing rapidly can use the solution with other Cisco UnifiedCommunications solutions, providing industry-leading investment protection.●Peace of mind: Cisco solutions deliver the solid reliability you expect from Cisco. All solution componentshave been rigorously tested to help ensure easy setup, interoperability, and performance.Table 1 lists the specifications for the Cisco SPA112 2 Port Adapter.Table 1. Product Specifications*Note: Many specifications are programmable within a defined range or list of options. Please see the Cisco SPA100 Series Administration Guide for details. The configuration profile is uploaded to the Cisco SPA112 at the time of provisioning.Data networking MAC address (IEEE 802.3)IPv4 (RFC 791) upgradeable to IPv6 (RFC 1883)Address Resolution Protocol (ARP)Domain Name System (DNS) A record (RFC 1706) and SRV record (RFC 2782)Dynamic Host Configuration Protocol (DHCP) client (RFC 2131)Point-to-Point Protocol over Ethernet (PPoE) client (RFC 2516)Internet Control Message Protocol (ICMP) (RFC 792)TCP (RFC 793)User Datagram Protocol (UDP) (RFC 768)Real Time Protocol (RTP) (RFC 1889) (RFC 1890)Real Time Control Protocol (RTCP) (RFC 1889)VLAN tagging (IEEE 802.1p)Simple Network Time Protocol (SNTP) (RFC 2030)SIP channels support for both UDP and TCP transportVoice gateway SIPv2 (RFC 3261, 3262, 3263, and 3264)SIP proxy redundancy: Dynamic through use of DNS SRV A recordsReregistration with primary SIP proxy serverSIP support in network address translation (NAT) networks (including Serial Tunnel [STUN])Highly secure (encrypted) calling using Secure RTP (SRTP)Codec name assignmentG.711 (A-law and μ-law)G.726 (32 kbps)G.729 ADynamic payloadAdjustable audio frames per packetDual-tone multifrequency (DTMF): In-band and out-of-band (RFC 2833) (SIP information)Voice features Independent configurable dial plans with interdigit timers and IP dialing (1 per port)Call progress tone generationJitter buffer: AdaptiveFrame loss concealmentFull-duplex audioEcho cancellation (G.165 and G.168)Voice activity detection (VAD)Silence suppressionComfort noise generation (CNG)Attenuation and gain adjustmentsFlash hook timerMessage waiting indicator (MWI) tonesVisual messaging waiting indicator (VMWI) using frequency shift keying (FSK)Polarity controlHook flash event signalingCaller ID generation (name and number): Bellcore, DTMF, and European Telecommunications StandardsInstitute (ETSI)Streaming audio server: Up to 4 sessionsMusic on holdCall waiting, call waiting and caller IDCaller ID with name and numberCaller ID blockingSelective and anonymous call rejectionCall forwarding: No answer, busy, and allDo not disturbCall transfer, call return, and call back on busyThree-way conference calling with local mixingPer-call authentication and associated routingCall blocking with toll restrictionDistinctive ringing: Calling and called numberOff-hook warning toneAdvanced inbound and outbound call routingHotline and warmline callingLong silence (configurable time setting) silence thresholdDisconnect tone (for example, reorder tone)Configurable ring frequencyRing validation time settingTip and ring voltage adjustment settingRing indication delay settingFax capability Fax tone detection pass-throughFax pass-through using G.711Real-time fax over IP using T.38 fax relay (T.38 support is dependent on fax machine and network and transportresilience)Security Password-protected system reset to factory defaultPassword-protected administrator and user access authorityProvisioning, configuration, and authenticationHTTPS with factory-installed client certificateHTTP digest: Encrypted authentication using MD5 (RFC 1321)Up to 256-bit Advanced Encryption Standard (AES) encryptionSIP Transport Layer Security (TLS)Provisioning, administration, and maintenance Web browser administration and configuration using integral web serverTelephone keypad configuration with interactive voice promptsAutomated provisioning and upgrade using HTTPS, HTTP, and Trivial File Transfer Protocol (TFTP) TR-069Asynchronous notification of upgrade availability using NotifyNonintrusive, in-service upgradesReport generation and event loggingStatistics in Bye messageDebug server records and syslog: Per-line configurable web browserPing and traceroute diagnosticsConfiguration management: Backup and restoreSupport for BonjourPhysical interfaces 1 WAN 100BASE-T RJ-45 Ethernet Port (IEEE 802.3)2 RJ-11 FXS phone ports for analog circuit telephone device (tip and ring)Reset buttonSubscriber line interface circuit (SLIC) Ring voltage: 40–90 Vpk configurableRing frequency: 20–25 HzRing waveform: trapezoidalMaximum ringer load: 5 ringer equivalence numbers (RENs)On-hook voltage (tip and ring): –46 to –56VOff-hook current: 18–25 mATerminating impedance: 600 ohm resistive or 270 ohm + 750 ohm 150 nF complex impedanceFrequency response: 300–3400 HzReturn loss (600 ohm, 300–3400 Hz): up to 20 dBInsertion loss (1 Vrms at 1 kHz): 3–4 dBTotal harmonic distortion (THD) (350 mV peak at 300 Hz): up to 3% Idle channel noise: 72 dB (typical)Longitudinal balance: 55 dB (typical)Cisco Small Business Support Service for the Cisco SPA112 2 Port AdapterThe Cisco Small Business Support Service provides “peace of mind” coverage at an affordable price and helps you get the most value from your Cisco Small Business solution. This device-level, subscription-based service includes software upgrades and updates, extended access to the Cisco Small Business Support Center, and next-business-day hardware replacement as necessary. It also provides community-based support to enable small businesses to share knowledge and collaborate using online forums and wikis to help boost business efficiency, identify and reduce risks, and serve customers better.For More InformationFor more information about Cisco Small Business solutions, visit /go/smallbusiness. For more information about the Cisco SPA 100 Series, visit /go/gateways or contact your local Cisco account representative.Cisco CapitalFinancing to Help You Achieve Your ObjectivesCisco Capital can help you acquire the technology you need to achieve your objectives and stay competitive. We can help you reduce CapEx. Accelerate your growth. Optimize your investment dollars and ROI. Cisco Capital financing gives you flexibility in acquiring hardware, software, services, and complementary third-party equipment. And there’s just one predictable payment. Cisco Capital is available in more than 100 countries.Learn more.。

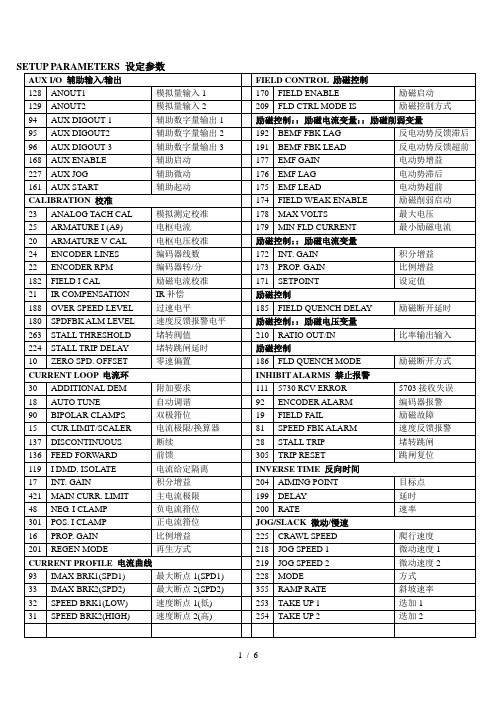

欧陆直流驱动器中英文参数对照表new

励磁控制

10

ZERO SPD. OFFSET

零速偏置

186

FLD QUENCH MODE

励磁断开方式

CURRENT LOOP电流环

INHIBIT ALARMS禁止报警30Βιβλιοθήκη ADDITIONAL DEM

附加要求

111

5730 RCV ERROR

5703接收失误

18

AUTO TUNE

自动调谐

92

程序停机时间

217

STOP LIMIT

停机极限

27

STOP TIME

停机时间

29

STOP ZERO SPEED

停机零速

SYSTEM系统

配置输入输出::模拟输入::ANIN 1(A2)

294

SPT SUM 1 DEST

设定值合计1目的

230

CALIBRATION

校准

442

TAPER

锥度

246

DESTINATION TAG

目的标记

CONFIGURE 5703配置输入输出::配置5703

231

MAX VALUE

最大值

135

DESTINATION TAG

目的标记

232

MIN VALUE

最小值

134

SOURCE TAG

源标记

配置输入输出::模拟输入::ANIN 2(A3)

CONFIGURE I/O配置输入输出

233

CALIBRATION

110

VALUE FOR FALSE

“虚”的值

241

MIN VALUE

最小值

109

Analog and Digital(模拟电子和数字电子)电子信息专业英语文章