电子万年历课程设计报告

多功能电子万年历实训报告

一、引言随着科技的发展,电子产品在我们的日常生活中扮演着越来越重要的角色。

作为电子信息专业的一名学生,我深知理论与实践相结合的重要性。

为了提高自己的动手能力和解决实际问题的能力,我参加了本次多功能电子万年历的实训项目。

通过本次实训,我不仅掌握了单片机的基本原理和编程方法,还学会了如何将理论知识应用于实际项目中。

二、实训目的1. 熟悉单片机的硬件结构和编程方法。

2. 掌握电子万年历的设计原理和实现方法。

3. 提高动手能力和解决实际问题的能力。

4. 培养团队协作和沟通能力。

三、实训内容本次实训主要围绕多功能电子万年历的设计与实现展开,主要包括以下几个方面:1. 硬件设计:选择合适的单片机作为核心控制单元,设计电路图,并焊接电路板。

2. 软件设计:编写程序,实现万年历的基本功能,如显示日期、时间、星期、闰年判断、闹钟等。

3. 温度采集:使用DS18B20温度传感器采集环境温度,并在LCD1602显示屏上显示。

4. 按键控制:设计按键电路,实现时间校准、闹钟设置、温度显示等功能。

四、实训过程1. 硬件设计:- 选择AT89C52单片机作为核心控制单元,因为它具有低功耗、高性能的特点。

- 设计电路图,包括晶振电路、复位电路、时钟电路、按键电路、LCD1602显示电路、温度传感器电路等。

- 焊接电路板,确保电路连接正确。

2. 软件设计:- 使用Keil软件编写程序,实现万年历的基本功能。

- 编写时间显示、闹钟、温度显示等模块的程序。

- 编写按键扫描程序,实现时间校准、闹钟设置、温度显示等功能。

3. 温度采集:- 使用DS18B20温度传感器采集环境温度。

- 将温度数据转换为数字信号,并在LCD1602显示屏上显示。

4. 按键控制:- 设计按键电路,实现时间校准、闹钟设置、温度显示等功能。

- 编写按键扫描程序,检测按键状态,并执行相应的操作。

五、实训结果经过努力,我成功完成了多功能电子万年历的设计与实现。

该万年历具有以下功能:1. 显示年、月、日、星期、时、分、秒。

电子万年历课程设计

电子万年历课程设计一、课程目标知识目标:1. 学生能够理解电子万年历的基本原理和组成部分。

2. 学生掌握电子万年历的日期、时间设置及调整方法。

3. 学生了解电子万年历在不同场合的应用和功能。

技能目标:1. 学生能够独立完成电子万年历的组装和调试。

2. 学生通过实际操作,学会使用编程软件编写简单的程序,实现电子万年历的基本功能。

3. 学生具备分析电子万年历故障并进行排除的能力。

情感态度价值观目标:1. 学生培养对电子万年历的兴趣,激发学习电子技术和编程的热情。

2. 学生在合作学习中,培养团队协作能力和沟通表达能力。

3. 学生认识到电子万年历在现代生活中的重要作用,增强对科技创新的认识。

课程性质:本课程为实践性较强的信息技术课程,结合电子技术和编程知识,培养学生的动手能力和创新能力。

学生特点:五年级学生具备一定的电子技术基础和编程兴趣,好奇心强,喜欢动手操作。

教学要求:教师应关注学生的个体差异,采用分层教学,引导学生主动探索、实践,提高学生的综合素养。

在教学过程中,注重目标分解,确保学生能够达到预期学习成果。

二、教学内容1. 电子万年历的原理与结构- 介绍电子万年历的组成及工作原理- 分析电子万年历的核心元件及其功能2. 电子万年历的组装与调试- 指导学生进行电子万年历的组装- 教授调试方法,确保电子万年历正常运行3. 编程软件的使用- 介绍编程软件的基本操作和功能- 演示如何编写程序,实现电子万年历的基本功能4. 电子万年历的应用与拓展- 讲解电子万年历在不同场合的应用- 探讨电子万年历的拓展功能及其实现方法5. 故障分析与排除- 分析电子万年历可能出现的故障- 教授排除故障的方法和技巧教学内容安排与进度:第一课时:电子万年历原理与结构介绍第二课时:电子万年历组装与调试第三课时:编程软件使用及基本程序编写第四课时:电子万年历应用与拓展第五课时:故障分析与排除教材章节关联:本教学内容与课本第四章“电子时钟与万年历”相关,涉及电子万年历的原理、组装、编程及应用等方面的知识。

电子万历年课程设计

电子万历年课程设计一、课程目标知识目标:1. 学生能理解电子万年历的基本原理,掌握年月日、星期等时间单位的换算关系。

2. 学生能运用所学知识,分析电子万年历的电路结构和编程逻辑。

3. 学生了解电子万年历在生活中的应用,认识到科技与日常生活的紧密联系。

技能目标:1. 学生通过动手实践,掌握电子万年历的制作方法,提高动手操作能力。

2. 学生学会运用编程软件进行简单程序的编写,培养逻辑思维和问题解决能力。

3. 学生能够运用所学知识,对电子万年历进行创新设计和优化。

情感态度价值观目标:1. 学生在课程学习中,培养对电子科学的兴趣,激发探索精神和创新意识。

2. 学生通过合作学习,培养团队协作精神,增强沟通与交流能力。

3. 学生了解我国在电子万年历领域的发展,增强国家认同感和自豪感。

本课程针对初中年级学生,结合电子科学的学科特点,以实用性为导向,注重培养学生的动手实践能力和逻辑思维能力。

课程目标明确,可衡量,旨在帮助学生掌握电子万年历相关知识,提高学生的综合素养。

二、教学内容1. 电子万年历基础知识:年月日、星期等时间单位的换算关系,闰年的判定方法。

2. 电子万年历电路结构:介绍集成电路、晶体振荡器、显示器件等组件的工作原理及电路连接方式。

3. 编程逻辑:学习C语言基础,掌握简单的顺序结构、分支结构和循环结构,运用编程软件进行程序编写。

4. 电子万年历的制作与调试:动手实践,学会焊接电路板,编写程序,调试电子万年历。

5. 创新设计与优化:在掌握基本原理和制作方法的基础上,对电子万年历进行改进和创新设计。

教学内容安排和进度:第一课时:电子万年历基础知识学习,介绍时间单位换算关系,讲解闰年判定方法。

第二课时:学习电子万年历电路结构,分析各组件工作原理及电路连接方式。

第三课时:C语言基础学习,理解顺序结构、分支结构和循环结构。

第四课时:动手实践,制作电子万年历,学习焊接电路板,编写程序。

第五课时:调试电子万年历,进行创新设计与优化,展示与交流。

单片机课程设计报告电子万年历

单片机课程设计报告电子万年历单片机课程设计报告:电子万年历一、设计简介在本次单片机课程设计中,我们选择了电子万年历作为设计主题。

电子万年历是一种结合了数字电路、单片机技术和实时时钟(RTC)技术的电子产品,它具有显示年份、月份、星期、日、时、分、秒的功能,还可以根据用户的需求进行定时、闹钟、报时等功能。

二、硬件设计我们采用了基于8051内核的单片机作为主控芯片。

该单片机具有丰富的I/O 端口,适于实现各种复杂的输入输出操作。

此外,它还内置了定时器和中断控制器,可以很方便地实现实时时钟功能。

1.显示模块:为了方便用户查看时间信息,我们选用了LCD显示屏作为显示设备。

LCD屏具有功耗低、体积小、显示内容丰富等优点。

2.实时时钟(RTC)模块:我们采用了常用的DS1302芯片作为实时时钟模块。

该芯片可以提供秒、分、时、日、星期、月、年的信息,而且还有可编程的报警功能。

3.按键模块:为了实现人机交互,我们设计了一组按键。

用户可以通过按键来调整时间、设置闹钟等。

4.电源模块:为了保证系统的稳定工作,我们采用了稳定的5V直流电源。

三、软件设计我们采用了C语言编写程序。

程序主要由以下几个部分组成:1.主程序:主程序主要负责读取RTC模块的时间信息,并控制LCD显示屏显示时间。

同时,主程序还要检测按键输入,根据用户的需求进行相应的操作。

2.RTC驱动程序:为了正确地读取和设置DS1302芯片的时间信息,我们编写了相应的驱动程序。

驱动程序包括初始化和读写寄存器两部分。

3.按键处理程序:按键处理程序用于检测按键输入,并根据按键值执行相应的操作。

比如,用户可以通过按键来增加或减少时间,设置闹钟等。

4.LCD显示程序:LCD显示程序用于控制LCD显示屏的显示内容。

在本设计中,我们使用了点阵字符库,将时间信息以字符的形式显示在LCD屏上。

四、测试与验证为了确保我们的电子万年历设计正确无误,我们进行了以下的测试和验证:1.硬件测试:首先,我们对硬件电路进行了测试,确保每个模块都能正常工作。

万年历设计报告

万年历设计1、设计目的:1、学会对单片机外围电路的使用。

2、熟悉使用proteus电路仿真软件。

3、熟悉使用KILE C语言编程软件。

4、了解数字万年历的工作原理及其组成。

2、设计任务:1、显示年月日时分秒及星期信息2、具有可调整日期和时间功能3、增加闰年计算功能3、方案比较:用单片机设计电子时钟通常有两种方法:一是通过单片机内部的定时器或者计数器。

这种方法硬件线路简单,采用软件编程实现时钟计数,一般称为软时钟。

系统的功能一般与软件设计有关,通常用在对时间精度要求不高的场合;二是采用时钟芯片,它的功能强大,功能部件集成在芯片内部,自动产生时钟等相关功能。

硬件成本相对较高,软件编程简单。

通常使用在对时钟精度要求较高的场合。

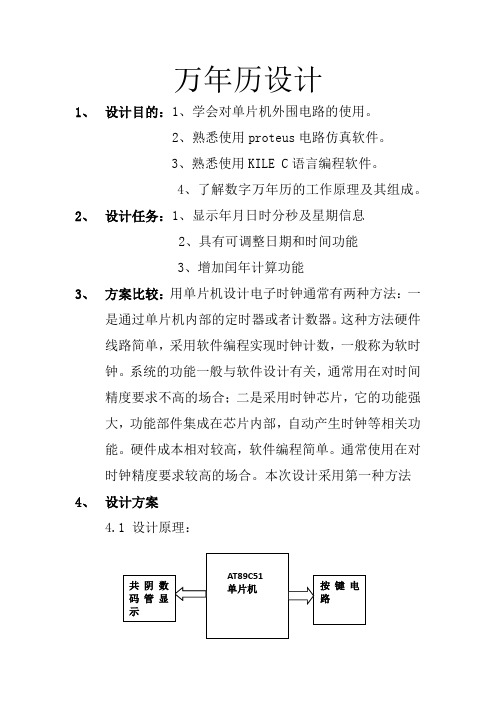

本次设计采用第一种方法4、设计方案4.1 设计原理:本方案有的时间脉冲由单片机内部的定时器/计数器产生,所以硬件电路相对简单,由单片机产生时钟信号,通过程序分别产生年月日时分秒,同时可以区分闰年闰月,加送数码管显示,同时加上按键电路,可以对年月日时分秒进行调整,还有清零。

4.2硬件设计:图1如图1该电路由51单片机为核心,使用数码管显示,按键电路进行调整,考虑到单片机P0口的驱动能力不足的情况,使用上拉电阻提升驱动能力。

4.3软件设计:仿真开始,先初始化系统时间加送数码管显示,然后判断按键是否按下,如果按下,就表明要对时间进行调整,接下来则显示调整完的时间,如果没有按下,则显示初始时间。

5、设计结果图2如图2所示,数码管阵列第一列显示年月日,第二列显示时分秒,按键电路从上到下分别为复位,秒分时日月年的调整按键。

每当秒到60则分进位,同理,分满时进位,时满日进位,日满月进位,月满年进位,还可以区分闰年闰月。

6、总结和个人体验通过该课程设计很好的掌握了KILE,proteus两个和专业相关的软件,极大的拓宽了自己的知识宽度,期间产生的问题都与老师一起讨论得到了很好的解决,这对自己的问题阐述能力以及解决问题的能力都有很大的提升。

电子万年历实验报告

实验报告电子万年历:一、需求分析:电子万年历系统主要实现以下单个查询功能:1、查询某一年的日历。

要求从键盘输入年份,输出该年12个月份的日历2、查询某一天某一个月的日历。

要求从键盘输入年份和月份,输出该月的日历。

3、查询某一天是星期几。

要求从键盘输入年、月、日,输出这一天是星期几。

二、总体设计:1、功能模块图计算模块:用于计算天数,判断闰年输出模块:用于菜单输出和日历输出查询模块:实现查询某一年的日历。

查询某一天某一个月的日历。

查询某一天是星期几。

三、详细设计:1、计算模块:计算模块主要包含3个函数:LeapYear()、CountYearDays()、CountMonthDays函数CountYearDays()功能是计算从公元元年1月1日到某年12月31日一共有多少天。

CountYearDays()功能是几双当年1月1日到输入日期的前一个月的天数2、输出模块包含2个函数:Menu()和ListMonth()函数。

Menu()函数用来输出系统提供的功能选项。

ListMonth()函数用来按规定格式输出一个月的日历。

3、查询模块针对系统要实现三个查询功能定义了3个函数:Search1()、 Search2()和 Search3()函数。

函数Search1()用来显示一年12个月的日历,输入年份后,计算该年1月1日是星期几,然后从1月份开始一次输出每个月的日历,其中调用了函数LeapYear()、CountYearDays()和CountMonthDays()。

函数Search2()用来显示某年某月的日历,输入年份和月份后,计算出该年该月1日是星期几,然后输出这个月的日历,其中调用了函数LeapYear()和CountYearDays()、CountMonthDays()和ListMonth()。

函数Search3()用来显示某天是星期几,通过调用函数LeapYear()、CountYearDays()和CountMonthDays()计算出从公元元年1月1日到这一天总共过去了多少天,用这个总天数除以7得到的余数即为答案。

电子万年历设计报告书

题目:带温度显示的万年历的设计姓名:学院:组别:万年历的设计与实现摘要随着科技的快速发展,时间的流逝,至从观太阳、摆钟到现在电子钟,人类不断研究,不断创新纪录。

美国DALLAS公司推出的具有涓细电流充电能的低功耗实时时钟电路DS1302。

它可以对年、月、日、周日、时、分、秒进行计时,还具有闰年补偿等多种功能,而且DS1302的使用寿命长,误差小。

对于数字电子万年历采用直观的数字显示,可以同时显示年、月、日、周日、时、分、秒和温度等信息,还具有时间校准等功能。

该电路采用AT89S52单片机作为核心,能够显示从2000至2099年的年、月、日、星期、时、分、秒。

同时还可以对当前环境温度进行实时测量。

系统具有读取方便、显示直观、功能多样、电路简洁、成本低廉等诸多优点,符合电子仪器仪表的发展趋势,具有广阔的市场前景。

关键词:单片机,时钟芯片,多功能万年历,数码管,温度传感器ABSTRACTWith the rapid development of science and technology, the passage of time, tofrom the view of the sun, pendulum clock to the present clock, humans continue to study, and continuously record. DALLAS United States that have launched small trickle charge current to a low-power real time clock circuitry of the DS1302. It can be year, month, day, Sunday, hours, minutes, seconds for time, but also has a leap year compensation to a variety of functions, and the DS1302's long life, small error. For the digital electronic calendar using an intuitive digital display can simultaneously display year, month, day, Sunday, hours, minutes, seconds, and temperature and other information, but also a time-calibration and other functions.The circuit uses AT89S52 microcontroller as the core,, can demonstrate from 2000 to 2099 year, month, Japan, week, divides, the second and carries on the integral point to report time.. The system has the read to be convenient, the demonstration is direct-viewing, the function is diverse, the electric circuit is succinct, cost inexpensive and so on many merits, conforms to the electronic instrumentation measuring appliance's trend of development, has the broad market prospect.KEY WORDS: monolithic integrated circuit;real time clock;multi-purpose ten thousand calendars;LED;temperature sensor.一、设计要求与方案论证1.1 设计要求:①系统具有年、月、日、星期、时、分等功能;②系统具有温度计功能;③系统具备年、月、日、星期、时、分校准功能;1.2 系统基本方案选择和论证1.2.1单片机芯片的选择方案和论证:方案一:采用89C51芯片作为硬件核心,采用Flash ROM,内部具有4KB ROM 存储空间,能于3V的超低压工作,而且与MCS-51系列单片机完全兼容,但是运用于电路设计中时由于不具备ISP在线编程技术, 当在对电路进行调试时,由于程序的错误修改或对程序的新增功能需要烧入程序时,对芯片的多次拔插会对芯片造成一定的损坏。

制作电子万年历实训报告

一、引言随着科技的飞速发展,电子产品的普及和应用越来越广泛。

电子万年历作为一种常见的电子设备,不仅可以显示年、月、日、星期、时、分等信息,还可以实现闹钟、定时显示等功能。

为了提高我们的实践能力和创新能力,本次实训我们选择制作一款基于单片机的电子万年历。

二、实训目的1. 掌握电子万年历的基本原理和设计方法。

2. 熟悉单片机的编程和应用。

3. 培养团队协作能力和动手实践能力。

三、实训内容1. 硬件设计本实训所使用的硬件主要包括以下部分:- 单片机:AT89C52- 时钟模块:DS1302- 显示模块:LCD1602- 遥控模块:1838V- 按键模块:S1(设置键)、S2(上调键)、S3(下调键)、S4(复位键)硬件电路图如下:2. 软件设计本实训所使用的软件主要包括以下部分:- 单片机编程:C语言- 显示程序:LCD1602驱动程序- 遥控程序:1838V遥控接收程序软件流程图如下:3. 功能实现本实训所实现的电子万年历具有以下功能:- 显示年、月、日、星期、时、分等信息。

- 遥控操作:设置时间、星期、日期等。

- 定时显示:定时显示当前时间。

- 停电自动计时:采用DS1302时钟模块,停电后可继续计时。

四、实训过程1. 硬件搭建首先,我们根据电路图搭建了电子万年历的硬件电路。

在搭建过程中,我们注意了以下几点:- 确保电路连接正确,避免短路或开路。

- 选择合适的元器件,确保电路性能稳定。

- 对电路进行测试,确保电路正常工作。

2. 软件编程接下来,我们使用C语言对单片机进行编程。

在编程过程中,我们遵循以下步骤:- 分析功能需求,确定程序结构。

- 编写程序代码,实现各项功能。

- 调试程序,确保程序运行正常。

3. 测试与优化在完成软件编程后,我们对电子万年历进行测试。

在测试过程中,我们发现以下问题:- 遥控操作不稳定。

电子万年历设计报告

电子万年历设计报告The document was prepared on January 2, 2021电子万年历设计报告专业电气工程及其自动化班级电气2班姓名马志欣学号小组第22组指导教师王松林电子万年历概述电子万年历是一种应用非常广泛的日常计时工具,数字显示的日历钟已经越来越流行,特别是适合在家庭居室、办公室、大厅、议室、车站和广场等使用,壁挂式LED数码管显示的日历钟逐渐受到人们的欢迎.LED数字显示的日历钟显示清晰直观、走时准确、可以进行夜视,二十一世纪的今天,最具代表性的计时产品就是电子万年历,它是近代世界钟表业界的第三次革命.第一次是摆和摆轮游丝的发明,相对稳定的机械振荡频率源使钟表的走时差从分级缩小到秒级,代表性的产品就是带有摆或摆轮游丝的机械钟或表.第二次革命是石英晶体振荡器的应用,发明了走时精度更高的石英电子钟表,使钟表的走时月差从分级缩小到秒级.第三次革命就是单片机数码计时技术的应用电子万年历,使计时产品的走时日差从分级缩小到1/600万秒,从原有传统指针计时的方式发展为人们日常更为熟悉的夜光数字显示方式,直观明了,并增加了全自动日期、星期、温度以及其他日常附属信息的显示功能,它更符合消费者的生活需求因此,电子万年历的出现带来了钟表计时业界跨跃性的进步.随着科学技术的快速发展,不断研究创新,对于电子万年历采用直观的数字显示,可以同时显示年,月,日,时,分,温度等信息,还具有时间校准等功能,该电路采用AT89C51单片机作为核心,电压可选用3-5V电压供电.一、内容摘要本设计利用数量较少的芯片制作了一个运用简单的电子万年历.以单片机作为本设计的核心,实现时钟日历的显示:用八段LED数码管分别显示年、月、日、星期、时、分、秒,用DS1302作为该设计的实时时钟芯片,用74LS164寄存器来驱动数码管的各段码,用三极管来驱动数码管的各位码.并且通过AT89C51单片机读取数字温度芯片的内部数据,进行处理后送到数码管显示其温度功能,通过按键实现调试功能.二、设计要求1设计电子万年历,实现时钟日历的显示,或显示年、月、日或时、分、秒,用DS1302作为设计的实时时钟芯片.2温度记录仪电路设计:功能:1、记录温度并保存,每10分钟记录一次温度数据.2、可显示时间、温度数据3、可查询温度数据4、可由上位机电脑读取温度数据.三、设计方案1、显示时钟功能1单片机芯片的选择采用AT89C51芯片作为硬件核心,并且与MCS-51系列单片机完全兼容.2显示模块的选择采用LED数码管,更注重于显示多位数字.3时钟芯片的选择采用DS1302时钟芯片实现时钟,且精度高,可自动对时、分、秒进行计数,工作电压在范围内.2、温度显示功能1单片机芯片的选择AT89C51芯片2显示模块的选择采用LED数码管来显示温度3温度传感器的选择采用温度传感器DS18B20,传感器DS1302四、系统硬件框图1单片机模块引脚功能:AT89C51单片机有40个引脚.Vcc:电源电压+5VGND:接地P0口:P0口是一组8位漏极开路型双向I/O口,也即地址/数据总线复用口.作为输出口用时,每位能驱动8个TTL逻辑门电路,对端口写“1”可作为高阻抗输入端用.P1口:P1口是一个带内部上拉电阻的8位双向I/O,P1的输出缓冲级可驱动吸收或输出电流4个TTL逻辑门电路.对端口写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口.作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流.P2口:P2口是一个带内部上拉电阻的8位双向I/O,P2的输出缓冲级可驱动吸收或输出电流4个TTL逻辑门电路.对端口写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口.作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流.P3口:P3口是一组带内部上拉电阻的8位双向I/O,P3的输出缓冲级可驱动吸收或输出电流4个TTL逻辑门电路.对P3口写入“1”时,它们被内部的上拉电阻拉高并可作为输入端口.作输入端时,被外部拉低的P3口将用上拉电阻输出电流.P3口除了作为一般的I/O口线外,更重要的用途是它的第二功能,见表3-1所示:RST:复位输入.ALE/PROG:当访问外部程序存储器或数据存储器时,ALE地址锁存器允许输出脉冲用于锁存地址的低8位字节XTAL1:振荡器反相放大器及内部时钟发生器的输入端.XTAL2:振荡器反相放大器的输出端.定时/计数器:AT89C51单片机内含有2个16位的定时器/计数器.中断系统:AT89C51单片机有6个中断源,中断系统主要由中断允许寄存器IE、中断优先级寄存器IP、优先级结构和一些逻辑门组成.2按键电路3数码管显示4热敏电阻5DS1302系统精确时钟DS1302的控制字节的最高有效位位7必须是逻辑1,如果它为0,则不能把数据写入DS1302中,位6如果为0,则表示存取日历时钟数据,为1表示存取RAM数据;位5至位1指示操作单元的地址;最低有效位位0如为0表示要进行写操作,为1表示进行读操作,控制字节总是从最低位开始输出.DS1302 引脚图6蜂鸣器7拨动开关五、万年历软件系统的流程当接通电源开始工作后,单片机中的程序开始运行,将对DS18B20进行初始化,以便和单片机芯片达成通信协议.完成初始化后,由于本系统只有一个测温元件,单片机会向其发出跳过RAM 指令,接下来便可向其发送操作指令,启动测温程序,测温过程完成后,发出温度转换指令,从而便可将温度转化成数字模式进行显示读取;同时DS1302将读取时分秒及年月日寄存器后通过LED数码管显示时间日期,键盘电路中按键可对实时时钟进行调整.六、各单元元器件内容介绍1、温度信息采集通过DS18B20单线总线的所有执行处理都从一哥舒适化序列开始,初始化序列包括一个由总线控制器发出复位脉冲和随后由从机发出的存在脉冲.1复位2存在脉冲3控制器发送ROM指令4控制器发送存储器操作指令5执行或数据读写2、时钟的读取1DS1302控制字节2DS1302数据的输入和输出在控制指令字输入后的下一个SCLK时钟的上升沿时数据被写入DS1302,数据输入从低位即位0开始.在紧跟8位的控制指令字后的下一个SCLK脉冲的下降沿读出DS1302的数据,读出数据时从低位0位至高位7.3温度的显示控制先对LED数码管进行初始化,当所测温度从DS18B20输送到单片机上之后,在LED数码管上显示出来.4按键模块使用按键可调整LED数码管上显示的数值.七、相关的电路图和实物图电子万年历实物图电子万年历封装图八、调试与软件仿真1、软件的仿真与调试1打开KEIL,输入所编写的源程序进行编译,在软件的帮助下检查其中的错误并进行修改,直到编译正确后运行.2绘制单片机电子万年历运行电路图.3检查所画电路运行图,确保没错误后,在PROTEUS下对原理图进行加载KEIL下的源程序.4加载完成后,进行仿真,观察LED数码管情况,程序调试完成后2、硬件调试与连接1检测AT89C51运行是否正常2LED数码管显示是否正常3各元件是否正常4将程序下载完调试完后用仿真软件主机与从机连接主机与从机连接后的电路板情况九、问题分析与总结出现的问题:1、在焊接电路板时,有些元件出现假焊,致使LED数码管不能正常显示.2、在接芯片时引脚弄错,致使与电路图不能相互符合.3、在调试完成后,LED数码管不能正常显示或出现乱码,检查后发现是接触不良造成的.总结在制作过程中一直不断出现很多常见的错误,导致结果都不理想,之后通过与老师与同学之间的交流后每个问题都得到了解决,这让我们更加加深印象.虽然出现很多问题但也学到了许多常识性的知识,这使我们的能力也得到锻炼和提高,也使对设计的整体流程有了更清楚的认识,小组成员们也一直在不断的努力,在经过老师与同学的帮助后最终有了成果使我们信心上得到了很大的支持.。

廖东东 电子万年历设计报告书

图书分类号:密级:毕业设计(论文)基于AT89S52单片机的电子万年历BASED ON AT89S52 MONOLITHIC INTEGRATED CIRCUIT ELECTRONIC TEN THOUSAND CALENDARS学生姓名廖东东学院名称信电工程学院专业名称电子信息工程技术指导教师潘晓博年月日摘要现在是一个知识爆炸的新时代,新产品、新技术层出不穷,电子技术的发展更是日新月异。

可以毫不夸张的说,电子技术的应用无处不在,电子技术正在不断地改变我们的生活,改变着我们的世界。

在这快速发展的年代,时间对人们来说是越来越宝贵,在快节奏的生活时,人们往往忘记了时间,一旦遇到重要的事情而忘记了时间,这将会带来很大的损失。

因此我们需要一个定时系统来提醒这些忙碌的人,而数字化的钟表给人们带来了极大的方便。

由于单片机具有灵活性强、成本低、功耗低、保密性好等特点,所以电子日历时钟一般都以单片机为核心,外加一些外围设备来实现。

近些年,随着科技的发展和社会的进步,人们对数字钟的要求也越来越高,传统的时钟已不能满足人们的需求。

多功能数字钟不管在性能还是在样式上都发生了质的变化,有电子闹钟、数字闹钟等等。

单片机在多功能数字钟中的应用已是非常普遍的,人们对数字钟的功能及工作顺序都非常熟悉。

但是却很少知道它的内部结构以及工作原理。

由单片机作为数字钟的核心控制器,可以通过它的时钟信号进行计时实现计时功能,将其时间数据经单片机输出,利用显示器显示出来,通过按键可以进行定时、校时功能。

输出设备显示器可以用液晶显示技术和数码管显示技术。

随着科技的快速发展,时间的流逝,至从观太阳、摆钟到现在电子钟,人类不断研究,不断创新纪录。

美国DALLAS公司推出的具有涓细电流充电能的低功耗实时时钟电路DS1302。

它可以对年、月、日、周日、时、分、秒进行计时,还具有闰年补偿等多种功能,而且DS1302的使用寿命长,误差小。

对于数字电子万年历采用直观的数字显示,可以同时显示年、月、日、周日、时、分、秒和温度等信息,还具有时间校准等功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程:创新与综合课程设计电子与电气工程系实践教学环节说明书题目名称电子万年历院(系)电子与电气工程学院专业电子信息工程班级119411学号1109635010学生姓名11指导教师q1起止日期13周周一~14周周五电子万年历一.设计目的设计一个具有报时功能、停电正常运行(来电无需校时)、带有年月日、时分秒及星期显示的电子日历。

二.方案设计硬件控制电路主要用了AT89S52芯片处理器、LCD1602显示器等。

根据各自芯片的功能互相连接成电子万年历的控制电路。

软件控制程序主要有主控程序、电子万年历的时间控制程序、时间显示及星期显示程序等组成。

主控程序中对整个程序进行控制,进行了初始化程序及计数器、还有键盘功能程序、以及显示程序等工作,时间控制程序是电子万年历中比较重要的部分。

时间控制程序体现了年、月、日、时、分、秒及星期的计算方法。

时间控制程序主要是定时器0计时中断程序每隔10ms中断一次当作一个计数,每中断一次则计数加1,当计数100次时,则表示1秒到了,秒变量加1,同理再判断是否1分钟到了,再判断是否1小时到了,再判断是否1天到了,再判断是否1月到了,再判断是否1年到了,若计数到了则相关变量清除0。

先给出一般年份的每月天数。

如果是闰年,第二个月天数不为28天,而是29天。

再用公式s=v-1 +〔(y-1/4〕-〔(y-1/100〕+〔(y-1/400〕+ d计算当前显示日期是星期几,当调节日期时,星期自动的调整过来。

闰年的判断规则为,如果该年份是4或100的整数倍或者是400的整数倍,则为闰年;否则为非闰年。

在我们的这个设计中由于只涉及100年范围内,所以判断是否闰年就只需要用该年份除4来判断就行了。

三.系统的设计框图本系统以AT89S52单片机为核心,结合时钟芯片DS1302,LCD1602,键盘等外围器件,实现电子万年历的一系列功能,并通过液晶屏和按键控制完成人机交互的功能。

系统总体设计框图如图(1)所示四.系统硬件设计1.单片机主控制模块AT89S52单片机为40引脚双列直插芯片,有四个I/O口P0,P1,P2,P3, MCS-51单片机共有4个8位的I/O口(P0、P1、P2、P3),每一条I/O线都能独立地作输出或输入。

如图(2)所示。

(1)内部结构按功能分为8部分:CUP,程序存储器,数据存储器,时钟电路,串行口,并行I/O口,中断系统,定时/计数器。

(2)引脚定义及功能1).电源及时钟引脚Vcc:接+5V 电源Vss:接地XTAL1和XTAL2:时钟引脚,外接晶体引线端。

当使用芯片内部时钟时,此两引脚端用于外接石英晶体和微调电容;当使用外部时钟时,用于接外部时钟脉冲信号。

2).控制引脚RST/Vpq:RST是复位信号输入端,Vpd是备用电源输入端。

当RST输入端保持2个机器周期以上高电平时,单片机完成复位初始化操作。

当主电源Vcc发生故障而突然下降到一定低电压或断电时,第2功能Vpd 将为片内RAM提供电源以保护片内RAM中的信息不丢失。

ALE/PROG:地址锁存允许信号输入端。

在存取外存储器时,用于锁存低8位地址信号。

当单片机正常工作后,ALE端就周期性地以时钟振荡频率的1/6固定频率向外输出正脉冲信号。

此引脚的第2功能PROG是对片内带有4K字节EPROM 的8751固外程序时,作为编程脉冲输入端。

PSEN:程序存储器允许输出端。

当片外程序存储器的读选通信号,低电平有效。

CPU从外部程序存储器取指令时,PSEN信号会自动产生负脉冲,作为外部程序存储器的选通信号。

EA/Vpp:程序存储器地址允许输入端。

当EA为高电平时,CPU执行片内程序存储器指令,但当PC中的值超过0FFFH时,将自动转向执行片外程序存储器指令;当EA为低电平时,CPU只执行片外程序存储器指令。

3).I/O口引脚P0.0~P0.7:P0口8位双向I/O口;P1.0~P1.7:P1口8位准双向I/O口;P2.0~P2.7:P2口8位准双向I/O口;P3.0~P3.7:P3口8位准双向I/O口。

(3)片外总线结构分为三部分:数据总线 Data Bus(DB),地址总线 Address Bus (AB),控制总线 Control Bus(CB).2.时钟电路模块(1) DS1302的结构及工作原理DS1302 是美国DALLAS公司推出的一种高性能、低功耗、带RAM的实时时钟电路,它可以对年、月、日、周日、时、分、秒进行计时,具有闰年补偿功能,工作电压为2.5V~5.5V。

采用三线接口与CPU进行同步通信,并可采用突发方式一次传送多个字节的时钟信号或RAM数据。

DS1302内部有一个31×8的用于临时性存放数据的RAM寄存器。

DS1302是DS1202的升级产品,与DS1202兼容,但增加了主电源/后背电源双电源引脚,同时提供了对后背电源进行涓细电流充电的能力。

(2) 引脚功能及结构图3所示出DS1302 的引脚排列,其中Vcc1 为后备电源,VCC2 为主电源。

在主电源关闭的情况下,也能保持时钟的连续运行。

DS1302 由Vcc1 或Vcc2 两者中的较大者供电。

当Vcc2 大于Vcc1+0.2V 时,Vcc2 给DS1302供电。

当Vcc2 小于Vcc1 时,DS1302 由Vcc1 供电。

X1 和X2 是振荡源,外接32.768kHz 晶振。

RST 是复位/片选线,通过把RST 输入驱动置高电平来启动所有的数据传送。

RST 输入有两种功能:首先,RST 接通控制逻辑,允许地址/命令序列送入移位寄存器;其次,RST 提供终止单字节或多字节数据的传送手段。

当RST 为高电平时,所有的数据传送被初始化,允许对DS1302 进行操作。

如果在传送过程中RST 置为低电平,则会终止此次数据传送,I/O 引脚变为高阻态。

上电运行时,在Vcc≥2.5V 之前,RST 必须保持低电平。

只有在SCLK 为低电平时,才能将RST 置为高电平。

I/O 为串行数据输入输出端(双向),后面有详细说明。

SCLK 始终是输入端。

图3 ds1302(3) 数据输入输出(I/O)在控制指令字输入后的下一个SCLK 时钟的上升沿时,数据被写入DS1302,数据输入从低位即位0 开始。

同样,在紧跟8 位的控制指令字后的下一个SCLK 脉冲的下降沿读出DS1302 的数据,读出数据时从低位0 位到高位7。

3. 显示部分1602液晶也叫1602字符型液晶它是一种专门用来显示字母、数字、符号等的点阵型液晶模块它有若干个5X7或者5X11等点阵字符位组成,每个点阵字符位都可以显示一个字符。

显示电路采用LCD1602液晶显示,如图4所示,图中只画出了其相应的接口,3脚用于调节LCD1602的背光,4、5、6为LCD1602的控制口,用于控制其写入或是读出指令,7至14脚为LCD1602的数据口,将数传送到LCD1602中。

图4 LCD1602显示电路4.复位电路设计复位电路由电阻和极性电容组成,如图5所示,通过高电平使单片机复位,在时钟电路开始工作后,当高电平的时间超过大约2us时,即可实现复位。

此复位电路为上电复位,较为简单。

若改进可以添加手动复位的功能,上电复位发生在开机加电时,由系统自动完成,手动复位通过一个按键来实现,在程序运行时,若遇到死机,死循环或程序“跑飞”等情况,通过手动复位就可以实现重新启动的操作。

手动按钮复位需要人为在复位输入端RST上加入高电平。

一般采用的办法是在RST端和正电源Vcc之间接一个按钮和一个电阻。

图5复位电路图6时钟振荡电路图5.时钟振荡电路时钟振荡电路图6所示,时钟振荡电路用于产生单片机正常工作时所需要的时钟信号,电路由两个30pF的瓷片电容和一个12MHz的晶振组成,并接入到单片机的XTAL1和XTAL2引脚处,使单片机工作于内部振荡模式。

此电路在加电后延迟大约10ms振荡器起振,在XTAL2引脚产生幅度为3V左右的正弦波时钟信号,其振荡频率主要由石英晶振的频率决定。

电路中两个电容C1、C2的作用使电路快速起振,提高电路的运行速度。

6.按键调整系统电路设计按键电路由四个轻触开关组成,如图7所示。

按键用来调整时间,其一端直接接到单片机的端口,另一端接地,当按下按键时,相应的端口变为低电平,通过一个与门只要这四个按键有一个按下就会在P3.2检测到一低电平就触发外部中断0进入按键调节程序中,通过与个各键相连的端口P3.4_P3.7可以判断是哪个键按下,从而作相应的操作。

图7按键电路与单片机的链接五.系统软件总体设计本系统选用适时性强与透明度高的C语言作为编程语言,系统软件的开发全部采用Keil uVision4进行。

软件控制程序主要有主控程序、电子万年历的时间控制程序组成。

主控程序中对整个程序进行控制,进行了初始化程序及计数器、还有键盘功能程序、以及显示程序和时间控制程序是电子万年历中比较重要的部分。

时间控制程序体现了年、月、日、时、分、秒及星期的计算方法。

时间控制程序主要是定时器0计时中断程序每隔10ms中断一次当作一个计数,每中断一次则计数加1,当计数100次时,则表示1秒到了,秒变量加1,同理再判断是否1分钟到了,再判断是否1小时到了,再判断是否1天到了,再判断是否1月到了,再判断是否1年到了,若计数到了则相关变量清除0。

先给出一般年份的每月天数。

如果是闰年,第二个月天数不为28天,而是29天。

闰年的判断规则为,如果该年份是4或100的整数倍或者是400的整数倍,则为闰年;否则为非闰年。

公历与星期的换算方法在现行公历中,历年的长度365天(平年)或者366天(闰年)都不是七的整数倍,所以日期与星期之间没有明显的对应关系。

一般情况下,不看日历牌就无法知道某月某日是星期几。

不过,它们之间还是有一定规律可循的,只要经过简单计算,或者查找表格,就可以知道与任何日期相对应的星期数。

主程序首先初始化定时器、LCD1602及DS1302,然后就开始查询按键,有键按下则开始调整时间和日期,若没有按下,则执行下面的时间、日期的显示,最后依次循环这些相同的操作,相应流程图如图8所示:图8主程序流程图六.系统测试与分析按键的检测是通过中断的办法来实现,利用按键进行间调整。

K1按下则开始设置时间及日期,同时在第一行最右端显示被选择的对象,第一次按下K1时,设置年份,若按下K3,则是减1操作,按下K2是加1操作,设置好年后,第二次按下K1时,则是设置月份,按K3减,按K2则加1,依次循环下去,则可以将时间和日期设置完毕,K4是确定键,设置好按下即可保存。

通过此电子万年历设计,本系统能完成以下功能:(1)显示公历日期功能(年、月、日、时、分、秒以及星期),(2)可通过按键切换年、月、日及时、分、秒的显示状态,(3)可随时调校年、月、日或时、分、秒,星期,(4)可每次增减一进行时间调节,(5)停电可以正常运行。