SERDES FPGA设计手册要点

基于FPGA的serdes电路之comma和PRBS检测电路设计说明书

基于FPGA的Serdes接口电路设计Comma和PRBS检测方案(仅供内部使用)拟制:谭宇日期:2013/09/13审核:姚亚峰日期:内部资料请勿外传修订记录日期修订版本描述作者2012/09/13 1.00初稿完成谭宇目录1.Serdes接口电路整体结构图 (3)2.概述 (5)2.1.文档版本 (5)2.2.相关标准 (5)2.3.开发环境 (5)3.Serdes接口电路选型 (5)3.1.Serdes芯片架构选型 (5)3.2.Serdes主要性能指标 (7)ma检测电路原理和实现 (7)ma检测电路原理 (7)ma的设计思路 (8)5.PRBS电路原理和实现 (9)5.1.PRBS电路原理 (9)5.2.PRBS电路实现过程 (10)6.说明 (10)Comma和PRBS检测电路设计说明书关键词:Serdes接口电路设计摘要:随着电子行业技术的发展,特别是在传输接口的发展上,原本用于光纤通信的Serdes 技术成为了为高速串行接口的主流。

它是一种时分多路复用(TDM)、点对点(P2P)的串行通信技术。

即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。

这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,从而大大降低通信成本。

安华高,博通,飞兆等国外半导体公司均已推出基于独立的Serdes 芯片,而国内目前还基本处于预研阶段。

本文就以基于FPGA的Serdes芯片IP core中Comma和PRBS检测电路部分做详细的介绍和说明。

缩略语清单:Serdes Serializer/Deserializer串行器/解串器PRBS Pseudo-Random Binary Sequence伪随机二进制序列1.Serdes接口电路整体结构图图1.Serdes接口电路整体结构图Serdes接口电路为一个全双工电路,同时又具有点对点的高效传输。

(完整版)SERDESFPGA设计手册

编号:版本:V0.2页数:共页密级:SERDES FPGA设计手册更改记录注:作者兜福邮箱:zouxingyu705@,多多交流,共同进步。

目录SERDES FPGA设计手册 (1)目录 (2)1目的 (5)2范围 (5)3术语 (5)4SERDES基础知识 (5)5SERDES应用指南 (5)5.1ISERDES (5)5.1.1ISERDES基元 (5)5.1.2ISERDES基元的时钟解决方案 (9)5.2OSERDES (10)5.2.1OSERDES组成功能模块 (10)5.2.2OSERDES基元 (12)5.2.3OSERDES基元的时钟解决方案 (13)6SERDES应用指南 (14)6.1ISERDES设计 (14)6.1.1单个ISERDES单元设计(SDR) (14)6.1.1.1ISERDES配置参数 (14)6.1.1.2设计思想 (17)6.1.1.3仿真结果 (17)6.1.1.4ISERDES数据时序 (18)6.1.1.4.1ISERDES输入数据时序 (18)6.1.1.4.1ISERDES输出数据时序 (19)6.1.2单个ISERDES单元设计(DDR) (20)6.1.2.1ISERDES配置参数 (20)6.1.2.2设计思想 (20)6.1.2.3仿真结果 (20)6.1.3ISERDES宽度扩展 (20)6.1.3.1设计实例 (21)6.1.3.2仿真结果 (24)6.2OSERDES设计 (24)6.2.1单个OSERDES单元设计(SDR) (24)6.2.1.1OSERDES配置参数 (24)6.2.1.2设计思想 (26)6.2.1.3仿真结果 (27)6.2.1.1OSERDES基元SDR模式时序 (27)6.2.2单个OSERDES单元设计(DDR) (27)6.2.2.1OSERDES配置参数 (28)6.2.2.2设计思想 (28)6.2.2.3仿真结果 (28)6.2.2.1OSERDES基元SDR模式时序 (29)6.2.3OSERDES宽度扩展 (29)6.2.3.1设计实例 (29)6.2.3.1仿真结果 (31)1目的为了学习xilinx serdes原语的使用,以及交流学习经验,在工程项目中方便的应用SERDES进行设计,故编写此文档。

SERDES FPGA设计手册

编号:版本:页数:共页密级:SERDES FPGA设计手册更改记录注:作者兜福邮箱:,多多交流,共同进步。

目录SERDES FPGA设计手册错误!未定义书签。

目录错误!未定义书签。

1目的错误!未定义书签。

2范围错误!未定义书签。

3术语错误!未定义书签。

4SERDES基础知识错误!未定义书签。

5SERDES应用指南错误!未定义书签。

ISERDES 错误!未定义书签。

ISERDES基元错误!未定义书签。

ISERDES基元的时钟解决方案错误!未定义书签。

OSERDES 错误!未定义书签。

OSERDES组成功能模块错误!未定义书签。

OSERDES基元错误!未定义书签。

OSERDES基元的时钟解决方案错误!未定义书签。

6SERDES应用指南错误!未定义书签。

ISERDES设计错误!未定义书签。

单个ISERDES单元设计(SDR) 错误!未定义书签。

配置参数错误!未定义书签。

设计思想错误!未定义书签。

仿真结果错误!未定义书签。

数据时序错误!未定义书签。

输入数据时序错误!未定义书签。

输出数据时序错误!未定义书签。

单个ISERDES单元设计(DDR) 错误!未定义书签。

配置参数错误!未定义书签。

设计思想错误!未定义书签。

仿真结果错误!未定义书签。

ISERDES宽度扩展错误!未定义书签。

设计实例错误!未定义书签。

仿真结果错误!未定义书签。

OSERDES设计错误!未定义书签。

单个OSERDES单元设计(SDR) 错误!未定义书签。

配置参数错误!未定义书签。

设计思想错误!未定义书签。

仿真结果错误!未定义书签。

基元SDR模式时序错误!未定义书签。

单个OSERDES单元设计(DDR) 错误!未定义书签。

配置参数错误!未定义书签。

设计思想错误!未定义书签。

仿真结果错误!未定义书签。

基元SDR模式时序错误!未定义书签。

OSERDES宽度扩展错误!未定义书签。

设计实例错误!未定义书签。

仿真结果错误!未定义书签。

目的为了学习xilinx serdes原语的使用,以及交流学习经验,在工程项目中方便的应用SERDES进行设计,故编写此文档。

SerDes知识详解

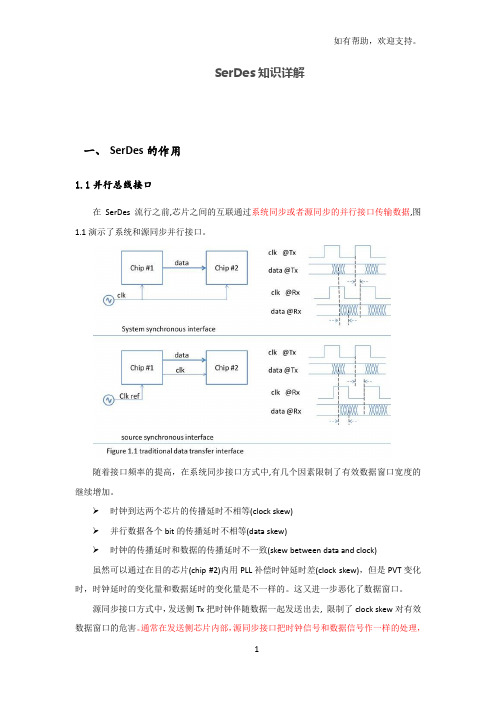

SerDes知识详解一、SerDes的作用1.1并行总线接口在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。

随着接口频率的提高,在系统同步接口方式中,有几个因素限制了有效数据窗口宽度的继续增加。

时钟到达两个芯片的传播延时不相等(clock skew)并行数据各个bit的传播延时不相等(data skew)时钟的传播延时和数据的传播延时不一致(skew between data and clock)虽然可以通过在目的芯片(chip #2)内用PLL补偿时钟延时差(clock skew),但是PVT变化时,时钟延时的变化量和数据延时的变化量是不一样的。

这又进一步恶化了数据窗口。

源同步接口方式中,发送侧Tx把时钟伴随数据一起发送出去, 限制了clock skew对有效数据窗口的危害。

通常在发送侧芯片内部,源同步接口把时钟信号和数据信号作一样的处理,也就是让它和数据信号经过相同的路径,保持相同的延时。

这样PVT变化时,时钟和数据会朝着同一个方向增大或者减小相同的量,对skew最有利。

我们来做一些合理的典型假设,假设一个32bit数据的并行总线,a)发送端的数据skew = 50 ps ---很高的要求b)pcb走线引入的skew = 50ps ---很高的要求c)时钟的周期抖动jitter = +/-50 ps ---很高的要求d)接收端触发器采样窗口= 250 ps ---Xilinx V7高端器件的IO触发器可以大致估计出并行接口的最高时钟= 1/(50+50+100+250) = 2.2GHz (DDR)或者1.1GHz (SDR)。

利用源同步接口,数据的有效窗口可以提高很多。

通常频率都在1GHz以下。

在实际应用中可以见到如SPI4.2接口的时钟可以高达DDR 700MHz x 16bits位宽。

DDR Memory接口也算一种源同步接口,如DDR3在FPGA中可以做到大约800MHz的时钟。

fpga 设计手册

fpga 设计手册

FPGA设计手册是一本关于FPGA(现场可编程门阵列)设计

的指南和参考手册。

它包含了FPGA设计的基本原理、设计

方法、工具使用以及各种电路和应用的实例。

FPGA设计手册通常涵盖以下内容:

1. FPGA基础知识:介绍FPGA的基本原理、架构和工作原理,让读者对FPGA有全面的了解。

2. 设计流程:详细解释FPGA设计的各个阶段,包括需求分析、设计规格、设计验证和实现等。

3. 设计工具:介绍使用FPGA设计所需的工具,如EDA(电

子设计自动化)工具、仿真工具和编程语言。

4. 设计技巧和优化:提供一些常用的FPGA设计技巧和优化

方法,帮助设计者提高设计效率和性能。

5. 电路实例:给出一些常见的FPGA电路实例,如逻辑门、

计数器、寄存器和状态机等,以帮助读者理解和应用FPGA

设计。

6. 应用案例:介绍一些实际应用中的FPGA设计案例,如图

像处理、通信系统和数字信号处理等,以展示FPGA在各个

领域的应用。

FPGA设计手册通常是由FPGA厂商、学术机构或工程师编写,旨在为初学者和有经验的FPGA设计者提供指导和参考。

读

者可以根据自己的需求选择适合的FPGA设计手册,并结合

实际项目进行学习和实践。

基于FPGA芯片的SERDES接口电路设计

基于FPGA芯片的SERDES接口电路设计串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。

随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。

起初,SERDES 是独立的ASSP 或ASIC 器件。

在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。

本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES 收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data Recovery,时钟数据恢复),完成100~200Mhz的板间SERDES单通道通信,该SERDES接口方案具有成本低、灵活性高、研发周期短等特点。

1 硬件接口:硬件的接口如上图所示,主要包括发送与接收模块。

发送模块包括8b/10b编码器,并串转换器,锁相环(PLL)频率合成器和发送器,接收模块包括8b/10b解码器,Comma 检测器,串并转换器,时钟数据恢复器(CDR)和接收器。

8b/10b编码器用于将从上层协议芯片发送过来的字节信号映射成直流平衡的10 位8b/10b 编码,并串转换用于将10 位编码结果串行化,并串转换所需的高速、低抖动时钟由锁相环提供,发送器用于将CMOS电平的高速串行码流转换成抗噪声能力较强的差分信号,经背板连接或光纤信道发送到接收机。

在接收端,接收器将接收到的低摆幅差分信号还原为CMOS 电平的串行信号,CDR 从串行信号中抽取时钟信息,完成对串行数据的最佳采样,串并转换利用CDR 恢复的时钟,将串行信号转换成10 位的并行数据,Comma 检测器检测特殊的Comma 字符,调整字边界,字边界正确的并行数据经过8b/10b 解码,还原为字节信号,传送到上层协议芯片,完成整个信息传输过程。

实际的设计中,CDR部分是由纯逻辑电路完成的,为设计的核心的部分,下面将介绍数字CDR在HR03的实现方案。

SerDes知识详解

SerDes知识详解SerDes技术是一种用于高速数据传输的技术,其主要作用是将并行数据流转换为串行数据流,以便在高速传输中减少时钟抖动和数据抖动等问题。

在SerDes技术流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据。

然而,随着接口频率的提高,这种方式存在一些限制,如时钟到达两个芯片的传播延时不相等、并行数据各个bit的传播延时不相等以及时钟的传播延时和数据的传播延时不一致等问题,这些问题都会影响数据的传输效率和可靠性。

为了解决这些问题,SerDes技术应运而生。

通过将并行数据流转换为串行数据流,SerDes技术可以减少时钟抖动和数据抖动等问题,从而提高数据的传输效率和可靠性。

同时,SerDes技术还可以提高数据的有效窗口,使得数据的传输速率可以更高。

在实际应用中,SerDes技术已经得到了广泛的应用,如SPI4.2接口的时钟可以高达DDR 700MHz x 16bits位宽,DDR Memory接口也可以做到大约800MHz的时钟。

需要注意的是,SerDes技术虽然可以提高数据的传输效率和可靠性,但是它也存在一些问题。

例如,SerDes技术需要消耗更多的功率,因此在功耗方面需要做出一定的权衡。

此外,SerDes技术还需要更多的硬件资源,因此在设计时需要考虑到硬件资源的使用情况。

总之,SerDes技术是一种非常重要的技术,它在高速数据传输方面有着广泛的应用前景。

Feedback Equalizer)进行均衡,再经过反串行器(Deserializer)进行串->并转换,最后通过8B/10B解码器(8B/10B decoder)或反扰码器(descambler)来还原原始数据。

接收端还会有时钟恢复模块(Clock Recovery)来提取时钟信号,以保证数据的同步性。

SerDes的核心是PMA层,它负责将数字信号转换成模拟信号,并进行调制、解调、均衡等操作。

PMA层的设计对SerDes的性能有着至关重要的影响。

serdes项目实例

serdes项目实例SerDes(Serializer/Deserializer)是一种高速串行接口技术,用于将数据从并行格式转换为串行格式,或者将数据从串行格式转换为并行格式。

SerDes广泛应用于高速通信、数据中心、云计算等领域。

下面是一个简单的SerDes项目实例,使用FPGA实现一个4Gbps的SerDes接口。

1. 项目目标本项目旨在设计并实现一个基于FPGA的4Gbps SerDes接口,用于高速数据传输和通信。

SerDes接口需要能够将FPGA内部的并行数据转换为高速串行数据,并能够在远距离传输后恢复原始数据。

2. 项目设计本项目采用Xilinx Virtex-7系列FPGA,使用其内建的SERDES模块实现SerDes接口。

具体设计如下:并行数据输入:SerDes接口接收FPGA内部的32位并行数据,数据速率为1000MHz。

串行数据输出:SerDes接口将接收到的并行数据转换为高速串行数据,数据速率为4Gbps,通过一对差分线传输。

线路编码:采用8B/10B编码方案,以提高信号的眼图质量和降低误码率。

均衡与去加重:在发送端,使用预加重和去加重技术,以提高信号的传输质量和降低误码率。

时钟管理:SerDes接口内部采用时钟管理单元(CMT),以确保时钟的准确性和稳定性。

3. 项目实现在FPGA上实现SerDes接口需要编写相应的硬件描述语言(HDL)代码,如VHDL或Verilog。

具体实现步骤如下:设计并行数据接收模块,将FPGA内部的并行数据接收并缓存到FIFO中。

设计串行数据发送模块,将FIFO中的数据转换为高速串行数据并发送出去。

设计时钟管理模块,为SerDes接口提供稳定的时钟信号。

设计均衡与去加重模块,在发送端对数据进行预加重和去加重处理,在接收端进行均衡处理。

综合和布局布线:使用Xilinx Vivado工具对设计进行综合和布局布线,生成可下载到FPGA的bit文件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

编号:版本:V0.2页数:共页密级:SERDES FPGA设计手册更改记录版本拟制/更改审核批准生效日期更改内容V0.1 兜福2013.7.19 创建文档V0.2 兜福2013.9.11 添加补充了OSERDES部分,未完待续;注:作者兜福邮箱:zouxingyu705@,多多交流,共同进步。

目录SERDES FPGA设计手册 (1)目录 (2)1目的 (5)2范围 (5)3术语 (5)4SERDES基础知识 (5)5SERDES应用指南 (5)5.1ISERDES (5)5.1.1ISERDES基元 (5)5.1.2ISERDES基元的时钟解决方案 (9)5.2OSERDES (10)5.2.1OSERDES组成功能模块 (10)5.2.2OSERDES基元 (12)5.2.3OSERDES基元的时钟解决方案 (13)6SERDES应用指南 (14)6.1ISERDES设计 (14)6.1.1单个ISERDES单元设计(SDR) (14)6.1.1.1ISERDES配置参数 (14)6.1.1.2设计思想 (17)6.1.1.3仿真结果 (17)6.1.1.4ISERDES数据时序 (18)6.1.1.4.1ISERDES输入数据时序 (18)6.1.1.4.1ISERDES输出数据时序 (19)6.1.2单个ISERDES单元设计(DDR) (20)6.1.2.1ISERDES配置参数 (20)6.1.2.2设计思想 (20)6.1.2.3仿真结果 (20)6.1.3ISERDES宽度扩展 (20)6.1.3.1设计实例 (21)6.1.3.2仿真结果 (24)6.2OSERDES设计 (24)6.2.1单个OSERDES单元设计(SDR) (24)6.2.1.1OSERDES配置参数 (24)6.2.1.2设计思想 (26)6.2.1.3仿真结果 (27)6.2.1.1OSERDES基元SDR模式时序 (27)6.2.2单个OSERDES单元设计(DDR) (27)6.2.2.1OSERDES配置参数 (28)6.2.2.2设计思想 (28)6.2.2.3仿真结果 (28)6.2.2.1OSERDES基元SDR模式时序 (29)6.2.3OSERDES宽度扩展 (29)6.2.3.1设计实例 (29)6.2.3.1仿真结果 (31)1目的为了学习xilinx serdes原语的使用,以及交流学习经验,在工程项目中方便的应用SERDES进行设计,故编写此文档。

2范围本文档所介绍的SERDES原语内容,适用于Xilinx V5系列器件。

3术语ISERDES:串并转换器。

OSERDES:并串转换器。

4SERDES基础知识待补充。

5SERDES应用指南5.1ISERDES5.1.1I SERDES基元图 1 ISERDES基元图 2 ISERDES内部组成单元结构框图图 3 当使用Memory模型是ISERDES内部的连接情况表 1 ISERDES端口列表Port Name Type Width DescriptionQ1-Q6 Output 1(each) 寄存器输出SHIFTOUT1 Output 1 进位输出,用于数据宽度的扩展。

连接到从IOB的SHIFIN1。

SHIFTOUT2 Output 1 进位输出,用于数据宽度的扩展。

连接到从IOB的SHIFIN2。

BITSLIP Input 1 启动bitslip操作CE1Input 1(each) 时钟使能输入CE2CLK Input 1 高速时钟输入,对串行输入数据流进行时钟控制。

CLKB Input 1 高速时钟第二输入,对串行输入的数据流进行时钟控制。

总是连接~CLK。

CLKDIV Input 1 时钟CLK的分频时钟,取决于解串的数据宽度。

控制着延迟单元、解串数据、Bitslip子模块和CE单元进行时钟控制。

D Input 1 来自IOB的串行输入数据。

OCLK Input 1 用于存储器应用的高速时钟输入,该信号只有在INTERFACE_TYPE属性配置为("MEMORY")时,才可用;配置为”NETWORKING”时,直接赋0值即可。

SHIFTIN1 Input 1 用于数据扩展的进位输入,连接到主IOB的SHIFTOUT1。

SHIFTIN2 Input 1 用于数据扩展的进位输入,连接到主IOB的SHIFTOUT2。

RST Input 1 异步复位输入,高有效。

表 2 ISERDES属性列表Atrribute Name Eescription Value Default ValueBITSLIP_ENABL E 允许用户使用或者忽略bitslip子模块。

该属性在INTERFACE_TYPE属性配置为MEMORY时必须配置为FALSE,在配置为NETWORKING时必须配置为TURE。

字符串:TURE或FALSEFALSEDATA_RATE 允许将输入的数据流作为”DDR”或者”SDR”来进行处理。

字符串:DDR或SDRDDRDATA_WIDTH 定义串并转换的宽度,合法的值取决于DATA_RATE的配置(SDR或者DDR)。

如果DATA_RATE = DDR,则此值限制为4、6、8 或10。

如果DATA_RATE = SDR,则此值限制为2、3、4、5、6、7 或8。

4INTERFACE_TYP E 选择ISERDES的使用说明字符串:MEMORY或NETWORKINGMEMORYNUM_CE 定义时钟使能数整数:1或2 2SERDES_MODE 当使用宽度扩展时定义SERDES是主模块,还是从模块。

字符串:MASTER或SLA VE。

MASTER表 3 推荐的数据宽度配置5.1.2I SERDES基元的时钟解决方案CLK和CLKDIV的相位关系,在串并转换的过程中是非常重要的。

CLK和CLKDIV的相位关系应该是理想对齐的。

FPGA中存在这样的时钟模块单元来设计满足CLK和CLKDIV的相位关系。

在networking模式下,解决时钟相位关系的唯一办法是:•CLK driven by BUFIO, CLKDIV driven by BUFR•CLK driven by DCM, CLKDIV driven by the CLKDV output of the same DCM•CLK driven by PLL, CLKDIV driven by CLKOUT[0:5] of same PLL在Memory Interface模式下,解决时钟相位关系的唯一办法是:•CLK driven by BUFIO or BUFG•OCLK driven by DCM and CLKDIV driven by CLKDV output of same DCM •OCLK driven by PLL and CLKDIV driven by CLKOUT[0:5] of same PLL图 4 控制CLK和CLKDIV相位对齐的时钟解决方案//补充文档内容从以下区域进行添加5.2OSERDESOSERDES:输出并串转换器逻辑资源,具有专门用来帮助实现源同步接口的待定时钟控制和逻辑资源。

每个OSERDES模块包含一个用户数据和三态控制的专用串行器。

数据和专用串行器都可以配置成SDR和DDR模式。

数据串行化可大6:1,如果使用“OSERDES宽度扩展,则是10:1”。

三态串行化可达4:1。

5.2.1O SERDES组成功能模块图OSERDES功能框图在OSERDES并串转换过程中,并行数据串行化是从数据引入引脚的最低位到最高位的顺序进行的(即D1输入引脚上的数据传输到OQ引脚的首位)。

OSERDES使用CLK和CLKDIV两个时钟进行数据速率转换。

CLK是高速串行时钟;CLKDIV是分频并行时钟。

假定CLK和CLKDIV相位对齐,表**所示为各种模式下CLK与CLKDIV之间的关系。

表** 并串转换器的clk/clkdiv关系SDR模式下的输入数据宽度输出DDR模式下的输入数据宽度输出CLK CLKDIV2 4 2X X3 6 3X X4 8 4X X5 10 5X X6 —6X X7 —7X X8 —8X XOSERDES延迟Oserdes模块的输入到输出延迟取决于DATA_RATE和DATA_WIDTH属性。

延迟的定义是,并行数据样本输入OSERDES所需的慢时钟(CLKDIV)周期数,后加OSERDES在并行数据采样之后将第一个串行数据送入OQ输出所需的快时钟(CLK)周期数。

表××概述了各种OSERDES延迟值。

5.2.2O SERDES基元图oserdes基元端口名称类型宽度描述OQ 输出output 1 数据通路输出,并转串后的串行输出。

SHIFTOUT1 输出 1 数据宽度扩展的进位输出,连接到主OSERDES的SHIFTIN1。

SHIFTOUT2 输出 1 数据宽度扩展的进位输出,连接到主OSERDES的SHIFTIN2。

TQ 输出 1 三态控制输出CLK 输入 1 高速时钟输入,驱动并串转换器的串行侧。

CLKDIV 输入 1 分频时钟输入。

对延迟单元,解串数据,Bitslip自模块和CE单元进行时钟控制。

为CLK端口所连接时钟的分频版本,分频大小根据数据转换宽度而定。

CLKDIV驱动驱动并串转换器的并行侧。

D1-D6 输入1/port 并行数据输入。

D1将最先出现在串行输出口OQ上。

所有并行数据全通过D1-D6进入OSERDES模块。

OCE 输入 1 输出数据时钟使能,高有效。

该信号可以作为输入OSERDES基元内的并行数据的同步有效标志,并可以同时输出到接收转换后的串行数据的一方,作为一个有效数据的起始位置的判断标志。

REV 输入 1 反转SR引脚。

OSERDES模块中没有此端口。

SHIFTIN1 输入 1 数据宽度扩展的进位输入,连接到从OSERDES的SHIFTOUT1。

SHIFTIN2 输入 1 数据宽度扩展的进位输入,连接到从OSERDES的SHIFTOUT2。

SR 输入 1 设置/复位。

在OSERDES模块中,此引脚只作为异步复位。

T1-T4 输入1/port 并行三态输入。

所有并行三态信号,都通过端口T1到T4进入OSERDES模块。

此端口连接到FPGA内部资源,可以配置成一位或者四位。

TCE 输入 1 三态控制通路时钟使能,高有效。

5.2.3O SERDES基元的时钟解决方案6SERDES应用指南6.1ISERDES设计6.1.1单个ISERDES单元设计(SDR)6.1.1.1ISERDES配置参数Iserdes仿真设计的练习中将iserdes的参数配置为图XX中的参数,具体参数释义如表XX所示。