北航电子电路设计数字部分实验报告

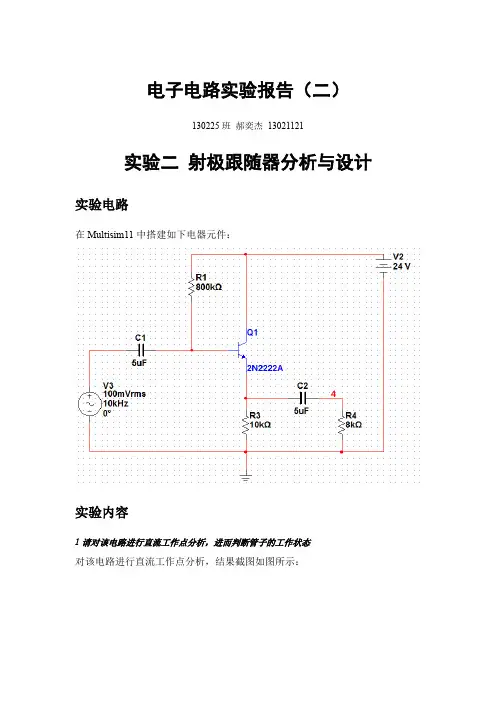

北航电子电路实验报告二

测试方法同第二步

测得:Ii=202.33nA,Ui=99.996mV,进而可求的Ri=494.22kΩ

(3)输出电阻

测试方法同第三步

测得:Io=2.913mA,Uo=99.996mV,进而可求的Ro=34.32Ω

(4)利用软件提供的各种测量仪表测出该电路的幅频、相频特性曲线:

将xbp表如图所示连接在电路中,观察xbp表即可得其幅频、相频特性曲线

100mV

对于电路一用上面公式计算放大倍数,可以看到随着RL的增加,放大倍数增加,逐渐接近输入电压100mV。

而对于理想放大器来说,跟随器的作用就是使得输出电压等于输入电压,所以输出电压恒为100mV

3测量输出电阻

将输入电压源短路,同时在输出端串接电压源,同时连接万用表如下图所示

测得:Io=2.929mA,Uo=99.996mV,进而可求的Ro=34.140Ω

4利用软件提供的测量仪表测出电路的幅频、相频特性曲线

将xbp表如图所示连接在电路中,观察xbp表即可得其幅频、相频特性曲线

5利用交流分析功能测出电路的幅频、相频特性曲线

电路一

10欧

100欧

1000欧

10千欧

100千欧

1兆欧

100兆欧

22.088mV

81.811mV

98.302mV

99.665mV

99.803mV

99.816mV

99.818mV

运算放大器

10欧

100欧

1000欧

10千欧

100千欧

1兆欧

100兆欧

100mV

100mV

100mV

100mV

100mV

100mV

电子电路

北航电力电子实验报告

电力电子实验报告学号12031006王天然实验一功率场效应晶体管(MOSFET)特性与驱动电路研究一.实验目的:1.熟悉MOSFET主要参数的测量方法2.掌握MOSEET对驱动电路的要求3.掌握一个实用驱动电路的工作原理与调试方法二.实验设备和仪器1.NMCL-07电力电子实验箱中的MOSFET与PWM波形发生器部分2.双踪示波器3.安培表(实验箱自带)4.电压表(使用万用表的直流电压档) 三.实验方法1.MOSFET 主要参数测试 (1)开启阀值电压V GS(th)测试开启阀值电压简称开启电压,是指器件流过一定量的漏极电流时(通常取漏极电流I D =1mA)的最小栅源极电压。

在主回路的“1”端与MOS 管的“25”端之间串入毫安表(箱上自带的数字安培表表头),测量漏极电流I D ,将主回路的“3”与“4”端分别与MOS 管的“24”与“23”相连,再在“24”与“23”端间接入电压表, 测量MOS 管的栅源电压Vgs ,并将主回路电位器RP 左旋到底,使Vgs=0。

图2-2 MOSFET实验电路将电位器RP逐渐向右旋转,边旋转边监视毫安表的读数,当漏极电流I D=1mA时的栅源电压值即为开启阀值电压V GS(th)。

读取6—7组I D、Vgs,其中I D=1mA必测,填入下表中。

I D0.2 0.5 1 5 100 200 500 (mA)Vgs2.64 2.72 2.863.04 3.50 3.63 3.89 (V)(2)跨导g FS测试双极型晶体管(GTR)通常用h FE(β)表示其增益,功率MOSFET器件以跨导g FS表示其增益。

跨导的定义为漏极电流的小变化与相应的栅源电压小变化量之比,即g FS=△I D/△V GS。

★注意典型的跨导额定值是在1/2额定漏极电流和V DS=15V下测得,受条件限制,实验中只能测到1/5额定漏极电流值,因此重点是掌握跨导的测量及计算方法。

根据上一步得到的测量数值,计算gFS=0.0038ΩI D(mA)0.2 0.5 1 5 10 100 200 500Vgs(V) 2.64 2.72 2.86 3.04 3.13 3.5 3.63 3.89g FS0.0038 0.0036 0.0222 0.0556 0.2432 0.7692 1.1538DS导通电阻定义为R DS=V DS/I D将电压表接至MOS 管的“25”与“23”两端,测量U DS,其余接线同上。

(完整版)北航微机原理实验报告

微计算机原理及运用实验报告目录实验一:I/O地址译码实验 (4)一、实验目的 (4)二、实验原理和内容 (4)三、实验程序 (4)四.实验总结 (5)实验二:8255并行接口实验 (6)一、实验目的 (6)二、实验原理和内容 (6)三、程序框图 (7)四.实验程序 (7)五.实验总结 (8)实验三:键盘显示控制实验 (9)一、实验目的 (9)二、实验内容及原理 (9)三、流程图 (10)四.程序 (10)五.实验总结 (13)实验四:8254定时器/计数器实验 (14)一、实验目的 (14)二、实验原理和内容 (14)三、实验程序 (14)四.实验总结 (15)实验五:继电器控制实验 (16)一、实验目的 (16)二、实验原理和内容 (16)三、实验中使用的程序 (16)四.实验总结 (18)实验六:DMA传送 (18)一、实验目的 (18)二、实验原理和内容 (18)三、程序 (19)四.实验总结 (20)实验七:8259 中断控制实验 (20)一、实验目的 (20)二、实验原理和内容 (21)三、流程图 (21)四.程序 (21)五.实验总结 (25)实验八:8255中断实验 (25)一、实验目的 (25)二、实验原理和内容 (25)三.实验程序 (26)四.实验总结 (27)实验一:I/O地址译码实验一、实验目的掌握I/O地址译码电路的工作原理。

二、实验原理和内容实验电路如附图1所示,其中74LS74为D触发器,可直接使用实验台上数字电路实验区的D触发器,74LS138为地址译码器。

译码输出端Y0~Y7在实验台上“I/O地址“输出端引出,每个输出端包含8个地址,Y0:280H~287H,Y1:288H~28FH,……当CPU执行I/O指令且地址在280H~2BFH范围内,译码器选中,必有一根译码线输出负脉冲。

附图1 I/O地址译码电路利用这个负脉冲控制L7闪烁发光(亮、灭、亮、灭、……),时间间隔通过软件延时实现。

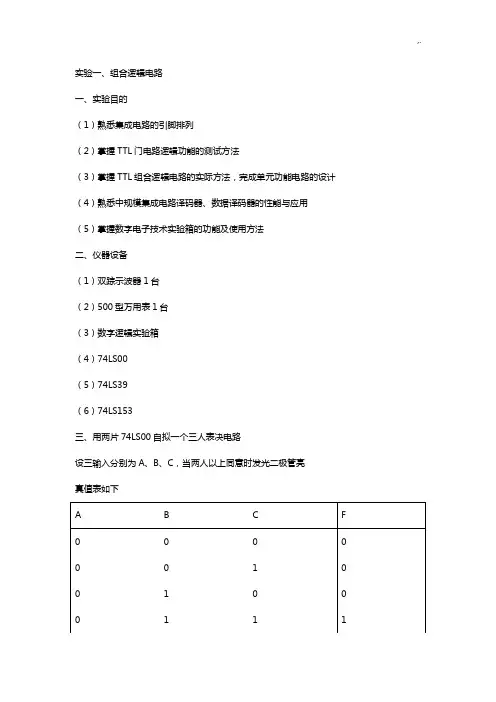

北航电路实验报告

实验一、组合逻辑电路一、实验目的(1)熟悉集成电路的引脚排列(2)掌握TTL门电路逻辑功能的测试方法(3)掌握TTL组合逻辑电路的实际方法,完成单元功能电路的设计(4)熟悉中规模集成电路译码器、数据译码器的性能与应用(5)掌握数字电子技术实验箱的功能及使用方法二、仪器设备(1)双踪示波器1台(2)500型万用表1台(3)数字逻辑实验箱(4)74LS00(5)74LS39(6)74LS153三、用两片74LS00自拟一个三人表决电路设三输入分别为A、B、C,当两人以上同意时发光二极管亮真值表如下1 0 0 0 1 0 1 1 1 1 0 1 1 1 1 1电路图如下:运行结果如下所示。

一人按下:二人按下:三人按下:2、设计一个三输入三输出的逻辑电路真值表如下用两个数据选择器74LS153设计电路,电路图如下:红绿灯亮:黄红灯亮:绿黄灯亮:实验二、时序逻辑电路一、实验目的(1)掌握D触发器和JK触发器逻辑功能的测试方法(2)掌握74LS161功能和引脚图,设计和实现具有一定功能的时序逻辑电路,体会不同控制端在电路设计中的作用(3)了解所用总规模集成器件的性能和应用二、仪器设备(1)双踪示波器1台(2)500型万用表1台(3)数字逻辑实验箱(4)74LS74(5)74LS20(6)74LS00(7)74LS161三、实验原理与内容1、利用2片74LS74、1片74LS20和2片74LS00设计一个4人抢答器。

电路图如下:主持人未按下抢答无效:A完成抢答其他选手按下无效:抢答完成后选手松开按钮灯保持不灭:2、利用中规模计数器74LS161实现任意进制计数器(1)用预置数置0实现七进制计数器电路图如下:计数为3的图片:计数为6的图片:,.。

北邮数字电路双色点阵实验报告(精)

数字电路与逻辑设计实验报告学院:电子工程学院班级:2011211203学号:2011210971班内序号:22姓名:郭一鸣指导老师:陈凌霄目录一、课题名称 (4二、摘要 (4三、设计任务要求 (4四、设计思路,总体结构框图 (41、基本框架 (42、在点阵上显示一个字或图案 (53、控制亮度 (53.1脉冲宽度调制(PWM (53.2 亮度 (64、控制颜色 (65、实现三种模式的滚动 (75.1状态 (75.2如何存储需要译码的字符 (75.3如何进行译码 (76、总体框图 (8五、控制器部分的状态转移图和流程图 (81、状态转移图 (92、流程图 (9六、总体电路和分块电路的设计 (111、总体电路 (112、分块电路 (11(1pwm调制器 (11(2数据选择器(mux (13(3译码器(translate (14(4其他模块 (20七、所实现的功能说明 (211、已完成的基本功能 (212、已完成的扩展功能 (213、器件资源占用情况 (214、关键波形仿真图 (21(1pwm调制器 (21(2数据选择器 (22(3译码器 (22八、故障及问题分析 (28九、总结 (29十、所用元器件及测试仪表清单 (29 十一、完整源程序 (291、总体原理图设计 (292、防抖模块 (293、一级分频器(pwm调制器 (304、二级分频器 (325、三级分频器 (326、模2计数器 (337、模4计数器 (348、模8计数器 (349、滚动状态计数器(模4模32计数器组合 (3510、数据选择器 (3611、译码器 (36十二、参考文献 (43欢迎学弟学妹下载!一、课题名称双色点阵显示控制器二、摘要本实验使用在QuartusII9.1的软件基础上,使用VHDL设计输入和原理图设计输入混合编程,设计了一个8×8双色点阵显示器,实现了控制固定图形的亮度和颜色以及多个字母不同模式的滚动且同时手动、自动变色的功能。

北京航空航天大学电子电路i-eda实验

4

晶体管的输出特性曲线

Q2 5V dc

Q2 N 69 6 ib

1m Adc

Vc e 自变量:vce,0~10v,0.1v。 参变量:Ib, 0~200ua,20ua。 负载:1.5k

直 流扫 描

0 8.0mA

直 流负 载 线

4.0mA

2020/6/20

0A 0V

2V

4V

6V

8V

10V

IC(Q2) (10v-v_vce)/1.5k

2020/6/20

2

二.直流传输特性

计算工作点 在工作点处对电路的元件做线性化处理。 计算线性化电路的小信号增益、输入输出电阻,

结果保存在输出文件。 参数设置:设置输入信号源及输出电压。

**** SMALL-SIGNAL CHARACTERISTICS V(OUT)/V_V2 = 0.000E+00 INPUT RESISTANCE AT V_V2 = 1.000E+20 OUTPUT RESISTANCE AT V(OUT) = 3.300E+04

100mV

50mV

0V 1.0Hz

V(OUT)

100Hz

10KHz Frequency

1.0MHz

9

100MHz

300mV

参数扫描 200mV

100mV

0V 1.0Hz

100Hz V(OUT)

10KHz Frequency

1.0MHz

100MHz

线性 对数 列表

2020/6/20

10

仿真分析

电路系统计算机辅助设计

2020/6/20

1

一.直流工作点分析

C1 in

北航_电子实习_数字部分实验报告

报告名称:电子电路设计训练数字部分学院:仪器科学与光电工程学院目录实验报告概述: (3)一、选做实验总结: (3)(1)补充练习2:楼梯灯设计 (3)(2)练习题6:用两种不同的设计方法设计一个功能相同的模块,完成4个数据的冒泡排序 (5)(3)练习题3:利用10MB的时钟,设计一个单周期形状的周期波形 (6)(4)练习题4:运用always块设计一个8路数据选择器 (6)(5)练习题5:设计一个带控制端的逻辑运算电路 (7)二、必做实验总结: (7)(1)练习一:简单组合逻辑设计 (7)(2)练习三:利用条件语句实现计数分频失序电路 (7)(3)练习四:阻塞赋值与非阻塞赋值得区别 (8)(4)练习五:用always块实现较复杂的组合逻辑电路 (8)(5)练习六:在verilog HDL中使用函数 (9)(6)练习七:在verilog HDL中使用任务 (9)(7)练习八:利用有限状态机进行时许逻辑设计 (10)三、实验总结及体会: (10)四、选作程序源代码 (11)(1)练习题3:利用10MB的时钟,设计一个单周期形状的周期波形 (11)(2)练习题4:运用always块设计一个8路数据选择器 (12)(3)练习题5:设计一个带控制端的逻辑运算电路 (13)(4)练习题6:用两种不同的设计方法设计一个功能相同的模块,完成4个数据的冒泡排序 (14)(5)补充练习2:楼梯灯设计 (16)图表目录Figure 1 楼梯灯任务4 (5)Figure 2 组合逻辑 (5)Figure 3 时序逻辑 (6)Figure 4 周期波形 (6)Figure 5 8路数据选择器 (6)Figure 6 逻辑运算电路 (7)Figure 7 组合逻辑设计 (7)Figure 8 计数分频时序电路 (8)Figure 9 阻塞赋值与非阻塞赋值得区别 (8)Figure 10 always块组合逻辑电路 (9)Figure 11 使用函数 (9)Figure 12 使用任务 (10)Figure 13 有限状态机 (10)电子电路设计训练(数字部分)实验报告实验报告概述:本实验报告为对四次电子电路设计训练(数字部分)实验的总结,主要包括以下四部分:第一部分为选做实验总结,主要包括每个选择实验的设计思路、运行结果、注意事项、心得体会;第二部分为必做实验总结,包括运行结果、总结、心得体会;第三部分为课程总结和体会,是对全部实验及课程的总结;第四部分为选做实验部分源代码;一、选做实验总结:(1)补充练习2:楼梯灯设计设计思路:本题给出楼梯的运行规则,并分别给与四个相应任务进行编程设计,考虑到程序的通用性及FPGA高速并行处理的优点,主要思路如下:根据运行规则(8s内和大于8s等),对每个灯的相应状态进行编程,设计时序逻辑及有限状态机;由于在总体上看,每个灯的状态变化相对独立(只有一个人上楼除外),故对每个灯编程所得到的程序代码可通用于其它灯(只需要改变相应寄存器定义即可),此即为灯控制模块,对4个不同的任务,只需设计其它部分判断逻辑,即可完成任务要求;如此设计,可大大提高程序设计效率、易用性,同时如果面对更多的灯控制需要,也可快速进行修改部署。

北航电子电路设计训练模拟部分实验报告

北航电子电路设计训练模拟部分实验报告电子电路设计训练模拟部分实验实验报告实验一:共射放大器分析与设计1.目的:(1)进一步了解Multisim的各项功能,熟练掌握其使用方法,为后续课程打好基础。

(2)通过使用Multisim来仿真电路,测试如图1所示的单管共射放大电路的静态工作点、电压放大倍数、输入电阻和输出电阻,并观察静态工作点的变化对输出波形的影响。

(3 )加深对放大电路工作原理的理解和参数变化对输出波形的影响。

(4)观察失真现象,了解其产生的原因。

■ ■ ■…- n - - ■- r f - - "一Lr-t-g-.I. .1 4l.4h.l- ■JLJIi.lb _...... vcc图1实验一电路图2.步骤:(1)请对该电路进行直流工作点分析,进而判断管子的工作状态。

(2)请利用软件提供的各种测量仪表测出该电路的输入电阻。

(3)请利用软件提供的各种测量仪表测出该电路的输出电阻。

(4)请利用软件提供的各种测量仪表测出该电路的幅频、相频特性曲线。

(5)请利用交流分析功能给出该电路的幅频、相频特性曲线。

(6)请分别在30Hz、1KHz lOOKHz 4MHz和100MHz这5个频点利用示波器测出输入和输出的关系,并仔细观察放大倍数和相位差。

(提示:在上述实验步骤中,建议使用普通的2N2222A三极管,并请注意信号源幅度和频率的选取,否则将得不到正确的结果。

)3.实验结果及分析:(1)根据直流工作点分析的结果,说明该电路的工作状态。

由simulate->analyses->DC operating point, 可测得该电路的静态工作点为:.Ls>lOtnVrffls1000 Hz0s..............R4j.4kQ::由V(5)>V(4)>V(2),可知,晶体管发射结导通,且发射结正偏,集 电结反偏,晶体管工作在放大状态。

(2)详细说明测量输入电阻的方法(操作步骤),并给出其值图3输入电阻测量使用交流模式的电流表接在电路的输入端测量输入电压和输入电 流,如图所示,可得输入电阻:R +需料3碎。

北航电力电子实验报告

电力电子实验报告学号姓名王天然实验一功率场效应晶体管(MOSFET)特性与驱动电路研究一.实验目的:1.熟悉MOSFET主要参数的测量方法2.掌握MOSEET对驱动电路的要求3.掌握一个实用驱动电路的工作原理与调试方法二.实验设备和仪器1.NMCL-07电力电子实验箱中的MOSFET与PWM波形发生器部分2.双踪示波器3.安培表(实验箱自带)4.电压表(使用万用表的直流电压档) 三.实验方法1.MOSFET 主要参数测试 (1)开启阀值电压V GS(th)测试开启阀值电压简称开启电压,是指器件流过一定量的漏极电流时(通常取漏极电流I D =1mA)的最小栅源极电压。

在主回路的“1”端与MOS 管的“25”端之间串入毫安表(箱上自带的数字安培表表头),测量漏极电流I D ,将主回路的“3”与“4”端分别与MOS 管的“24”与“23”相连,再在“24”与“23”端间接入电压表, 测量MOS 管的栅源电压Vgs ,并将主回路电位器RP 左旋到底,使Vgs=0。

图2-2 MOSFET实验电路将电位器RP逐渐向右旋转,边旋转边监视毫安表的读数,当漏极电流I D=1mA时的栅源电压值即为开启阀值电压V GS(th)。

读取6—7组I D、Vgs,其中I D=1mA必测,填入下表中。

I D0.2 0.5 1 5 100 200 500 (mA)Vgs2.64 2.72 2.863.04 3.50 3.63 3.89 (V)(2)跨导g FS测试双极型晶体管(GTR)通常用h FE(β)表示其增益,功率MOSFET器件以跨导g FS表示其增益。

跨导的定义为漏极电流的小变化与相应的栅源电压小变化量之比,即g FS=△I D/△V GS。

★注意典型的跨导额定值是在1/2额定漏极电流和V DS=15V下测得,受条件限制,实验中只能测到1/5额定漏极电流值,因此重点是掌握跨导的测量及计算方法。

根据上一步得到的测量数值,计算gFS=0.0038ΩI D(mA)0.2 0.5 1 5 10 100 200 500Vgs(V) 2.64 2.72 2.86 3.04 3.13 3.5 3.63 3.89g FS0.0038 0.0036 0.0222 0.0556 0.2432 0.7692 1.1538DS导通电阻定义为R DS=V DS/I D将电压表接至MOS 管的“25”与“23”两端,测量U DS,其余接线同上。

电子电路实验报告 北邮

指数运算电路的设计与实现摘要:指数放大电路由对数放大器和反对数放大器及温度补偿电路构成。

首先进行主要单元电路的设计,在实际应用中,基于二极管PN节的指数伏安特性实现对数反对数运算,用三极管替代PN节以增加集电极电流动态运用范围。

同时引入运算放大器,利用其方向端的“虚地特性”把PN节上的电压电流关系转化为电路的输入输出电压关系。

由于晶体管的相关参数T U,ES I是温度函数,其运算精度受温度影响较大,故加上温度补偿电路。

关键词:对数放大电路,反对数放大电路,温度补偿电路,指数放大电路,调试一、设计任务要求:设计实现一个指数运算电路,要求电路的输入输出满足指数运算关系uu k i。

o1、基本要求(1)本实验要求K=2或K=3(2)电路的输入阻抗R≥100KΩ。

i(3)输入信号幅度为0~2V(4)设计该电路的电源电路(不要求实际搭建)2、提高要求(1)可以手动的选取不同的K 值,并用数码管显示K 值。

(2)在指数运算电路的基础上进一步实现乘法,除法,乘方,开方等电路(3)其他设计、解决与功能扩展方案。

二、设计思路及总体结构框图 1、设计思路:利用二极管的PN 结的指数型伏安特性,实现对数运算。

通过电阻与晶体管位置的互换实现反对数运算电路。

加入温度补偿电路,消除温度对三极管参数的影响。

同时由电路特性确定电路中的电阻值,使之满足i R ≥100k Ω 2、系统组成框图如图所示,指数运算电路由对数放大器,放对数放大器及温度补偿电路三部分构成。

基本数学推导: i o u k u ln '=i ou k u o Be Be u ln '==Bu e o uk i=ln两边取对数: Bu u k o i ln ln =k oi u Bu =调整相关参数使B=1 即k i o u u = 3、主要单元电路设计 (1)基本对数放大器由图可知,晶体管集电极电流为e I i U uTES c =又因为 i c =i R ,u U o -=所以 Rui=-e I U uT ES从而得出RI u U ES i T o U ln-=注意:在该电路中,i u >0且输出电压不能超过0.7V 以使晶体管处于放大导通状态;此外,I ES ,T U 都是温度的函数,其运算结果受温度影响很大,所以需用对管消除I ES 的影响;用温度补偿电路消除T U 的温度影响。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子电路设计数字部分实验报告学院:姓名:实验一简单组合逻辑设计实验内容描述一个可综合的数据比较器,比较数据a 、b的大小,若相同,则给出结果1,否则给出结果0。

实验仿真结果实验代码主程序module compare(equal,a,b);input[7:0] a,b;output equal;assign equal=(a>b)1:0;endmodule测试程序module t;reg[7:0] a,b;reg clock,k;wire equal;initialbegina=0;b=0;clock=0;k=0;endalways #50 clock = ~clock; always @ (posedge clock) begina[0]={$random}%2;a[1]={$random}%2;a[2]={$random}%2;a[3]={$random}%2;a[4]={$random}%2;a[5]={$random}%2;a[6]={$random}%2;a[7]={$random}%2;b[0]={$random}%2;b[1]={$random}%2;b[2]={$random}%2;b[3]={$random}%2;b[4]={$random}%2;b[5]={$random}%2;b[6]={$random}%2;b[7]={$random}%2;endinitialbegin #100000 $stop;endcompare m(.equal(equal),.a(a),.b(b));endmodule实验二简单分频时序逻辑电路的设计实验内容用always块和@(posedge clk)或@(negedge clk)的结构表述一个1/2分频器的可综合模型,观察时序仿真结果。

实验仿真结果实验代码主程序module half_clk(reset,clk_in,clk_out); input clk_in,reset;output clk_out;reg clk_out;always@(negedge clk_in)beginif(!reset)clk_out=0;elseclk_out=~clk_out;endendmodule测试程序`timescale 1ns/100ps`define clk_cycle 50module top;reg clk,reset;wire clk_out;always #`clk_cycle clk=~clk;initialbeginclk=0;reset=1;#10 reset=0;#110 reset=1;#100000 $stop;endhalf_clk m0(.reset(reset),.clk_in(clk),.clk_out(clk_out));endmodule实验三利用条件语句实现计数分频时序电路实验内容利用10MHz的时钟,设计一个单周期形状的周期波形。

实验仿真结果实验代码主程序module fdivision(RESET,F10M,out); input F10M,RESET;output out;reg out;reg[7:0] i;always @(posedge F10M)if(!RESET)beginout<=0;i<=0;endelse if(i==2||i==3)beginout=~out;i<=i+1;endelse if(i==5)i<=1;elsei<=i+1;endmodule测试程序`timescale 1ns/100psmodule division_top;reg F10M,RESET;wire out;always #50 F10M=~F10M;initialbeginRESET=1;F10M=0;#90 RESET=0;#100 RESET=1;#10000 $stop;endfdivision fdivision(.RESET(RESET),.F10M(F10M),.out(out));endmodule实验四阻塞赋值与非阻塞赋值的区别实验内容比较四种不同的写法,观察阻塞与非阻塞赋值的区别。

Blocking:always @(posedge clk)beginb=a;c=b;endBlocking1:always @(posedge clk)beginc=b;b=a;endBlocking2:always @(posedge clk) b=a; always @(posedge clk) c=b; non_Blocking:always@(posedge clk)beginb<=a;c<=b;End实验仿真结果实验代码主程序module blocking(clk,a,b,c);output[3:0] b,c;input[3:0] a;input clk;reg[3:0] b,c;always @(posedge clk)beginb=a;c=b;endendmodule测试部分`timescale 1 ns/100 ps`include "./"`include "./"`include "./"`include "./"module compareTop;wire[3:0]b11,c11,b12,c12,b13,c13,b2,c2; reg[3:0]a;reg clk;initialbeginclk=0;forever#50 clk=~clk;endinitialbegina=4'h3;$display("%d",a);#100 a=4'h7;$display("%d",a);#100 a=4'hf;$display("%d",a);#100 a=4'ha;$display("%d",a);#100 a=4'h2;$display("%d",a);#100 $stop;endblocking blocking(clk,a,b11,c11);blocking1 blocking1(clk,a,b12,c12);blocking2 blocking2(clk,a,b13,c13);non_blocking non_blocking(clk,a,b2,c2); endmodule实验五用always块实现较复杂的组合逻辑实验目的运用always块设计一个8路数据选择器。

要求:每路输入数据与输出数据均为4位2进制数,当选择开关(至少3位)或输入数据发生变化时,输出数据也相应地变化。

实验仿真结果实验代码主程序module alu(out,opcode,a1,a2,a3,a4,a5,a6,a7,a8);output[3:0] out;reg[3:0] out;input[3:0] a0,a1,a2,a3,a4,a5,a6,a7;input[2:0] opcode;always@(opcode or a1 or a2 or a3 or a4 or a5 or a6 or a7 or a0) begincase(opcode)3'd0: out=a0;3'd1: out=a1;3'd2: out=a2;3'd3: out=a3;3'd4: out=a4;3'd5: out=a5;3'd6: out=a6;3'd7: out=a7;default:out=4'b0000;endcaseendendmodule测试程序`timescale 1ns/1ns`include "./"module alutext;wire[3:0] out;reg[3:0] a1,a2,a3,a4,a5,a6,a7,a8;reg[2:0] opcode;initialbegina1={$random}%16;a2={$random}%16;a3={$random}%16;a4={$random}%16;a5={$random}%16;a6={$random}%16;a7={$random}%16;a8={$random}%16;repeat(100)begin#100 opcode={$random}%8;a1={$random}%16;a2={$random}%16;a3={$random}%16;a4={$random}%16;a5={$random}%16;a6={$random}%16;a7={$random}%16;a8={$random}%16;end#100 $stop;endalu alu(out,opcode,a1,a2,a3,a4,a5,a6,a7,a8); endmodule实验六在 Verilog HDL中使用函数实验目的设计一个带控制端的逻辑运算电路,分别完成正整数的平方、立方和最大数为5的阶乘运算。

实验仿真结果实验代码主程序module tryfunct(clk,n,result1,result2,result3,reset);output[31:0]result1,result2,result3;input[3:0]n;input reset,clk;reg[31:0]result1,result2,result3;always@(posedge clk)beginif(!reset)beginresult1<=0;result2<=0;result3<=0;endelsebeginresult1<=fun1(n); result2<=fun2(n); result3<=fun3(n); endendfunction[31:0]fun1;input[3:0]operand;fun1=operand*operand; endfunctionfunction[31:0]fun2;input[3:0]operand;beginfun2=operand*operand; fun2=operand*fun2;endendfunctionfunction[31:0]fun3;input[3:0]operand;reg[3:0]index;beginfun3=1;if(operand<11)for(index=2;index<=operand;index=index+1) fun3=index*fun3;elsefor(index=2;index<=10;index=index+1)fun3=index*fun3;endendfunctionendmodule测试程序`include"./"`timescale 1ns/100psmodule tryfunctTop;reg[3:0] n,i;reg reset,clk;wire[31:0]result1,result2,result3;initialbeginclk=0;n=0;reset=1;#100 reset=0;#100 reset=1;for(i=0;i<=15;i=i+1)begin#200 n=i;end#100 $stop;endalways#50 clk=~clk;tryfunctm(.clk(clk),.n(n),.result1(result1),.result2(result2),.result3(result3),.reset( reset));endmodule实验七在Verilog HDL中使用任务(task)实验目的用两种不同方法设计一个功能相同的模块,该模块能完成四个8位2进制输入数据的冒泡排序。