数字电路1-2

数字电路与逻辑设计(第二版)章图文 (2)

第2章 组合逻辑电路

2.1 集成门电路 2.2 组合逻辑电路的分析和设计 2.3 组合逻辑电路中的竞争-冒险

第2章 组合逻辑电路

2.1 集成门电路

2.1.1 TTL门电路 TTL门电路由双极型三极管构成,它的特点是速度

快、抗静电能力强、集成度低、功耗大,目前广泛应用 于中、小规模集成电路中。TTL门电路有74(商用) 和54(军用)两大系列,每个系列中又有若干子系列,例 如,74系列包含如下基本子系列:

4)传输延时tP 传输延时tP指输入变化引起输出变化所需的时间,它 是衡量逻辑电路工作速度的重要指标。传输延时越短, 工作速度越快,工作频率越高。tPHL指输出由高电平变 为低电平时,输入脉冲的指定参考点(一般为中点)到 输出脉冲的相应指定参考点的时间。tPLH指输出由低电 平变为高电平时,输入脉冲的指定参考点到输出脉冲的 相应指定参考点的时间。标准TTL系列门电路典型的 传输延时为11ns;高速TTL系列门电路典型的传输延时 为3.3ns。HCT系列CMOS门电路的传输延时为7ns;AC 系列CMOS门电路的传输延时为5ns;ALVC系列CMOS 门电路的传输延时为3ns。

第2章 组合逻辑电路

图2―2和图2―3分别给出了TTL电路和CMOS电 路的输入/输出逻辑电平。

当输入电平在UIL(max)和UIH(min)之间时,逻辑电路可 能把它当作0,也可能把它当作1,而当逻辑电路因所接 负载过多等原因不能正常工作时,高电平输出可能低于 UOH(min),低电平输出可能高于UOL(max)。

第2章 组合逻辑电路

74AC和74ACT:先进CMOS(Advanced CMOS)。 74AHC和74AHCT:先进高速CMOS(Advanced High speed

数字电路_2数制和编码

? 区位码——GB 2312的所有字符分布在一个94行×94列的二维平面内,行号称为区号,列号称 为位号。区号和位号的组合就可以作为汉字字符的编码,称为汉字的区位码。

加法

减法

十六进制

? 由于二进制数在使用时位数太长,不容易记忆,所以又推出了十六进制数。 ? 十六进制数有两个基本特点:

? 它由十六个字符 0~9以及A,B,C,D,E,F组成(它们分别表示十进制数 10~15);

? 十六进制数运算规律是逢十六进一,即基 R=16=2 4,通常在表示时用尾部标志 H或下标 16以示区别。 例如:十六进制数 4AC8可写成( 4AC8 )16,或写成 4AC8H 。

B表示。 例如:二进制数 10110011 可以写成( 10110011 )2,或写成 10110011B ? 对于十进制数可以不加注基数;

十进制

(D) 0 1 2 3 4

56

7

8

9 10

二进制 (B) 0 1 10 11 100 101 110 111 1000 1001 1010

计算机采用二进制数

(101.11)B= 1×22 +0×21+1×20+1×2-1+1×2-2 =(5.75)D

各数位的权是2的幂

十进制数 →二进制数 将整数部分和小数部分分别进行转换。

整数部分 ---除2取余,逆序排列 ; 合并

小数部分 ---乘2取整,顺序排列。

? 十进制数 44.375 转换成二进制等于多少?

(44.375)D=(?)B

十六进制数 →二进制数

? 十六进制数转换为二进制数时正好与上面所述相反,只要将每位的十六进制数对应的 4 位二进制写出来就行了。

(数字电子技术基础)第2章. 门电路

• 小规模集成电路(SSI-Small Scale 小规模集成电路(SSI(SSI Integration), 每片组件内包含10~100 10~100个元件 Integration), 每片组件内包含10~100个元件 10~20个等效门 个等效门) (或10~20个等效门)。 • 中规模集成电路(MSI-Medium Scale 中规模集成电路(MSI (MSIIntegration),每片组件内含100~1000 100~1000个元件 Integration),每片组件内含100~1000个元件 20~100个等效门 个等效门) (或20~100个等效门)。 • 大规模集成电路(LSI-Large Scale 大规模集成电路(LSI (LSIIntegration), 每片组件内含1000~100 000个 Integration), 每片组件内含1000~100 000个 元件( 100~1000个等效门 个等效门) 元件(或100~1000个等效门)。 • 超大规模集成电路(VLSI-Very Large Scale 超大规模集成电路(VLSI (VLSIIntegration), 每片组件内含100 000个元件 Integration), 每片组件内含100 000个元件 1000个以上等效门 个以上等效门) (或1000个以上等效门)。

•

+5V

R1

T1

T5 R3

•

(2-30)

前级

后级

灌电流的计算

饱和

I OL

5 − T5压降 − T1的be结压降 = R1

5 − 0.3 − 0.7 ≈ 1.4mA = 3

(2-31)

关于电流的技术参数

名称及符号 输入低电平电流 IiL 输入高电平电流 IiH IOL 及其极限 IOL(max) IOH 及其极限 IOH (max) 含义 输入为低电平时流入输 入端的电流-1 入端的电流 .4mA。 。 输入为高电平时流入输 入端的电流几十 几十μ 。 入端的电流几十μA。 当 IOL> IOL(max)时,输出 不再是低电平。 不再是低电平。 当 IOH >IOH(max)时, 输出 不再是高电平。 不再是高电平。

数字电路基础知识部分(第二章)

练习一、一、填空题1、 模拟信号是在时间上和数值上都是 变化 的信号。

2、 脉冲信号则是指极短时间内的 电信号。

3、 广义地凡是 规律变化的,带有突变特点的电信号均称脉冲。

4、 数字信号是指在时间和数值上都是 的信号,是脉冲信号的一种。

5、 常见的脉冲波形有,矩形波、 、三角波、 、阶梯波。

6、 一个脉冲的参数主要有 、tr 、 、T P 、T 等。

7、 数字电路研究的对象是电路的 之间的逻辑关系。

8、 电容器两端的电压不能突变,即外加电压突变瞬间,电容器相当于 。

9、 电容充放电结束时,流过电容的电流为0,电容相当于 。

10、 通常规定,RC 充放电,当t = 时,即认为充放电过程结束。

11、 RC 充放电过程的快慢取决于电路本身的 ,与其它因素无关。

12、 RC 充放电过程中,电压,电流均按 规律变化。

13、 理想二极管正向导通时,其端电压为0,相当于开关的 。

14、 在脉冲与数字电路中,三极管主要工作在 和 。

15、 三极管输出响应输入的变化需要一定的时间,时间越短,开关特性 。

16、 选择题1 若逻辑表达式F A B =+,则下列表达式中与F 相同的是( ) A 、F A B = B 、F AB = C 、F A B =+2 若一个逻辑函数由三个变量组成,则最小项共有( )个。

A 、3 B 、4 C 、83 图9-1所示是三个变量的卡诺图,则最简的“与或式”表达式为( ) A 、A B A C B C ++B 、A B BC AC ++ C 、AB BC AC ++4 下列各式中哪个是三变量A 、B 、C 的最小项( ) A 、A B C ++ B 、A B C + C 、ABC 5、模拟电路与脉冲电路的不同在于( )。

A 、模拟电路的晶体管多工作在开关状态,脉冲电路的晶体管多工作在放大状态。

B 、模拟电路的晶体管多工作在放大状态,脉冲电路的晶体管多工作在开关状态。

C 、模拟电路的晶体管多工作在截止状态,脉冲电路的晶体管多工作在饱和状态。

1.数字电路又称二值数字逻辑,对数字信号进行传递、变换、

2.数字电路的分类

① 按电路类型分类: 组合逻辑电路 时序逻辑电路

②按集成度分类(见下表)

③按半导体的导电类型分类 •双极型电路(MOS场效应管) •单极型电路(晶体管)

3. 数字系统

数字系统是由实现各种功能的逻辑电路互相连 接构成的整体,它能交互式的处理用离散形式表示 的信息。

从概念上讲,凡是用数字技术来处理和传输信 息的系统都可以称为数字系统。本课程所指的数字 系统,是指由数字逻辑电路构成的纯硬件数字系统。

4. 数字系统中的两种运算类型

算术运算和逻辑运算。

5.数字逻辑电路研究的主要问题

数字逻辑电路主要研究电路输出信号状态与输入信 号状态之间的逻辑关系。它包含逻辑电路分析和逻辑电 路设计两个方面的内容。理论基础是逻辑代数。

逻辑电路分析:是要了解一个给定电路所实现的逻 辑功能;

逻辑电路设计:是根据实际问题提出的功能要求, 构造出实现该功能的电路。

1.数字电路

又称二值数字逻辑,对数字信号进行传递、变

换、运算、存储以及显示等处理的电路。它们可以 用电子器件的开关特性来实现。产生离散信号电压 或数字电压。

离散信号电压或数字电压通常用逻辑电平来表示。 例如,逻辑电平与电压值的关系可用下表来描述:

电压(V) +5 0

二值逻辑 1 0

电平

H(高电平) L(低电平)

2、可靠性高 •数字电路的抗干扰能力强,固而可靠。现在,越 来越多的模拟产品被数字产品所替代,从手表到电 视机、手机等等。

•在信号的传送过程中,数字传送比模拟传送也要 可靠的多。

3、集成度高

8、数字电路的分析方法与测试技术

1 分析方法

•数字电路的研究对象是电路的输入与输出之间的 逻辑关系; •三极管工作在开关状态,所以,分析方法不能再 是模拟电路中的图解法、小信号模型分析法,而是 采用布尔代数、真值表、卡诺图、逻辑表达式、逻 辑图、时序图等。

数字电路第2章 门电路

2)输入负载特性 (ui R )

R1 3k b1 A B C T1 R2 750 R4 100

+5V

c1

T3

T2

3k

T4

R5 T5

F

ui

V

R

R3

360

R较小时 设:T2、T5 截止

A B C

R1 3k b1

+5V

R4

R2

c1

T1

T2

R5

T3

T4 F T5

R

ui

R3

R (5 U ) 4.3R ui be1 R1 R 3 R

I BS vcc vCES 5 0.3 mA 0.094mA βRc 50 1

V CC = +5V Rc iC 1kΩ vo c R b 10kΩ b β = 40 iB e

②vi=0.3V时,iB=0,三极管 工作在截止状态,ic=0。因 为ic=0,所以输出电压: vo=VCC=5V

IB 0

IC 0

VCE VCC

7

三极管的开关特性

+UCC 3V 0V RB RC uO T

+UCC

RC 3V

饱和时, VCE ≈ 0,C、 E极间电阻 很小 0V 截止时, IC ≈ 0,C、 E极间电阻 很大

C E

uO 0

相当于 开关闭合

ui

饱和 截止

+UCC RC

C E

uO UCC

避免!

0V 0

VL(max)

低电平

分立元件门电路和集成门电路:

分立元件门电路:用分立的元件和导线连 接起来构成的门电路。简单、经济、功耗低, 负载差。 集成门电路:把构成门电路的元器件和连 线都制作在一块半导体芯片上,再封装起来, 便构成了集成门电路。现在使用最多的是CMOS 和TTL集成门电路。

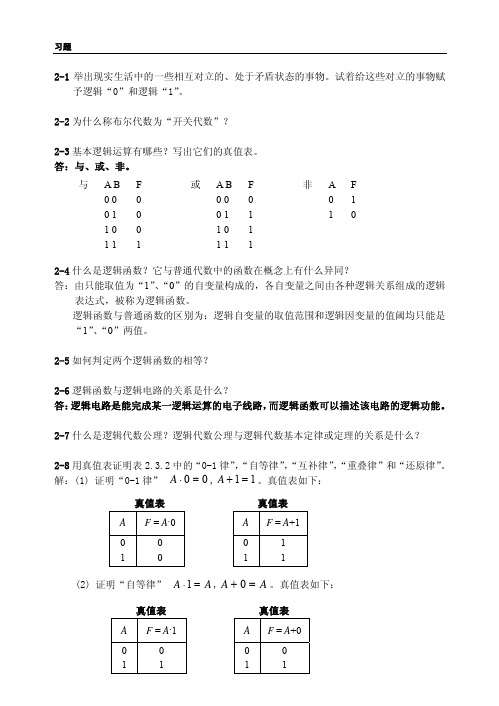

《数字电路-分析与设计》第二章习题及解答 北京理工大学出版社

5. A ⊕ B = A ⊕ B = A ⊕ B ⊕1

证明: 左边=AB+AB 中间= AB+AB=(A+B)(A+B)=AB+AB=左边 右边= (AB+AB)1+(AB+AB)1= AB+AB=中间 或者:根据 1⊕A=A,右边=中间

F1=(A+B)(B+C)(C+A)=ABC+ABC F2=(A+B)(B+C)(C+A)=ABC+ABC=F1 所以 F1=F2

习题

2. F1 = ABC + A B C , F2 = AB + BC + CA

由 1.知:F1=F2

3. F1 = C D + A B + BC , F2 = ABC + AB D + BC D

= AB + AC + BC

F = ( A + B) ⋅ ( A + C) ⋅ (B + C) = ( A + AB + AC + BC) ⋅ (B + C) = AB + ABC + BC + AC + ABC + AC + BC = AB + AC + BC

2-12 证明下列等式。

1. A ⊕ 0 = A

9. A( A + B ) = A

证明:左边=A+AB=A=右边,得证。 用真值表法略。 2-10 用逻辑代数演算证明下列等式。

数字电路 第2章习题解答

2-21 图2-53中所示门电路均为CMOS电路, 写出各电路输出的表达式。 a、b两图常用于扩展输入 端。 能否用于扩展TTL电路? 为什么?

F2 A B C D E

2-21 图2-53中所示门电路均为CMOS电路, 写出各电路输出的表达式。

不能用于扩展TTL电路。 在a图中,当C、D、E中 有低电平输入时,分立元 件与门输入到TTL电路的 电平已大于其VILmax,在逻 辑上可能相当于1,这样 分立元件与门已实现不了 “与”功能了。

2-21 图2-53中所示门电路均为CMOS电路, 写出各电路输出的表达式。

不能用于扩展TTL电路。 在b图中,当C、D、E均 为低电平时,三个二极管 均截止,100kΩ电阻会使 TTL或非门输入相当于逻 辑1,因而,分立元件或 非门实现不了“或”运算 。

2-21 图2-53中所示门电路均为CMOS电路, 写出各电路输出的表达式。

错误。 ⒉A=0,无论B、C取何值,AB=AC=0 ,故运算

错误。 ⒊1+B=1,A=B=1时,AB=1,故运算正确。

填空

采用5V电压供电的 CMOS门的抗干扰噪 声容限比5V电压供电的TTL门的抗干扰 噪声容限要( 宽 )。

TTL门带同类门的负载能力比CMOS门带 同类门的负载能力要( 弱 )。

F(A,B,C,D) =∑m(3,5,6,7,10) 约束条件:∑d(0,1,2,4,8)= 0。

用公式法化简函数 F ABCD ABD ACD

回答下列各题

•门电路组成的电路如图所示,请写出F1、 F2的逻辑表达式,当输入如图所示信号波 形时,画出F1、F2端的波形。

A

&

1

C

EN

TTL

&

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

• 由真值表 最小项表达式 使函数值 为 1 的最小项相“+”

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

(1) 两变量卡诺图: (2) 三变量卡诺图:

B A

0

1 AB AB

A BC00 0 4

A

二变量卡诺图

B

0 0 2 11 3 7

1 1 3 10 2 6

0 AB 1 AB

0 1

01 1 5

0 1

三变量卡诺图

(3) 四变量卡诺图:

CD 00 AB 0 00 01 11 10 4 12 8 01 1 5 13 9 11 3 7 15 11 10 2 6 14 10

AB

00 01 11 A 10

F=(A,B,C,D)= (0,1,3,4,7,12,13,15) AB CD 00 1 1 1 1 01 1 11 1 1 1 10

00 01 11 10

最 简 结 果 可 不 唯 一

F A C D A B D BCD AB C

CD AB 00 01 11 10 00 1 01 1 1 1 1 11 10 1 1 1 AB

A B A B A B A B

A B NAND

AB

A B Negative-OR

A+B

A B NOR

A+B

A B Negative-AND

AB

(3)常用公式

A B A B A 还原律: ( A B ) ( A B ) A

A A B A 吸收率: A ( A B) A

当前无法显示此图像。

01 1 1

11 X X X X

10

1 1

X X

10

在卡诺图化简中,利用无关项可取1,尽量将圈画大。

F(A,B,C,D)=(m4, m6, m10, m13 , m15 )+d(m0, m1, m2, m5, m7, m8,) AB CD

F AB BD B D

00 X 1 0 X 01 X X 1 0 11 0 X 1 0 10 X 1 0 1

1. 并项法 并项法

2. 吸收法 3. 消项法 消项法 4. 消因子法 消因子法A AA B A BA AB B AA 0; AA ; A 5. 配项法 A 1 A 1 配项法 A A

AB A AB B A BA A A A AAB AB A AB A C BC AB A C AB A C BC AB A C

C 0 1 0 1 0 1 0 1

编号 m0 m1 m2 m3 m4 m5 m6 m7

相邻项?

两个最小项只有一个变量互为相反变量,其余变量均相同

2. 逻辑函数的标准表达式--最小项表达式: 逻辑函数可表示为唯一的最小项表达式(最小项之和的 形式)。Standard SOP Form (Sum of Minterms Form)

A(B+C)=AB+AC(乘 法 分 配 律 )

其对偶等式:

A+BC=(A+B) (A+C)

注意

函数式中有“”和“⊙”运算符,求反函数及对 偶函数时,要将运算符“”换成“⊙”, “⊙” 换成“”。

3. 用布尔代数化简逻辑函数: 任何F都可以写成“与-或” (SOP: Sum-of-product ) 表达式的形式。 目的:乘积项最少;每个乘积项中因子最少。 方法:公式化简、卡诺图化简。 利用基本公式和常用公式来化简逻辑函数。

最小项的特点:

• 每个最小项只有n个变量因子; • 每个变量只能出现一次(原变 量或反变量); • n个变量共有2n个最小项。

ABC 最小项函数式 编号 m0 000 ABC m1 001 ABC m2 010 ABC m3 011 ABC m4 100 ABC m5 101 ABC m6 110 ABC m7 111 ABC

A BC 00 01 11 1 1 1 1 10

0 1

2) 已知非标准表达式 • 与或式 在“与项”所 覆盖 面积里的方格上填 1。

F(A,B,C)=A+BC

A BC 00 1 01 1 11 1 1 10 1

0 1

•或与式

F( A,B ,C ) ( A B C )( A B C )( A B C )

3) 写出划过圈的卡诺图所对应的表达式 (将每个圈对应的乘积项或在一起) AB AB 00 CD 00 1 1 1 1 1 1 1 1 1 01 11 10

01

ACD BD

11 10

BC

F ABCD AC D AB BC BD

F=(A,B,C,D)= (0,2,3,4,6,7,8,10,11,12,14) CD

6. 卡诺图化简逻辑函数

用卡诺图化简的步骤 :

AB CD 00 1 1 1 1 1 1 1 1 1 01 11

F A BC D A BCD ABC ABC AB D BCD

10

00 01 11 10

1) 将逻辑函 数F用卡诺 图表示;

2) 对卡诺图中为1的最小项划圈; AB CD 00 00 01 11 10 1 1 1 1 1 1 1 1 1 01 11 10

Y ( A.B.C ) m (0.2.7) d (1.4.5)

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

F 1 × 1 0 × × 0 1

例 F(A,B,C,D)=(m1, m5, m8, m12)+d(m3, m7, m10, m11, m14, m15,) CD 00 AB 00 01 11

F D BC AC

00 1 1 1 1 1 01 11 1 1

BC 10 1 1 1 1 AC

AB

00 01 D 11 10

F=(A,B,C,D)= (0,2,3,5,7,8,9,10,11,12,13,14,15) CD

F A B D BD CD

00 1 1 1 1 1 1 BD 01 11 1 1 1 1 1 1 10 1 CD B D

冗余律:AB

A ( A B) A B A A B A B

A C BC AB A C

2. 逻辑代数的三条规则: 1) 代入规则: 将等式中的某一变量都代以一个逻辑函数F,则此等式仍 成立: 规则应用:公式扩展。

A+B A B

A (D C) A (D C) A D C

2) 反演规则: 规则应用:求逻辑函数F的反函数。

例:Y

A( B C ) CD

求

Y

Y ( A B C )(C D )

例:求F A B C D E的反函数 F

F A B C D 则的应用:证明等式成立 若两个逻辑函数相等,则它们的对偶式也相等

( A B) C A ( B C ) 结合律: ( A B) C A ( B C )

A (B C ) A B A C 分配律: A B C ( A B) ( A C )

A B A B 反演律(狄摩根定律): A B A B

例:F2 A A BC (B AC D) BC

A BC ( A BC )( B AC D)

A BC

例: F ABC AD CD BD

ABC ( A C) D BD

ABC ACD BD ABC ACD

F 0 1 1 1 0 1 0 0

• 一般与或表达式 最小项表达式

( A A)

F(A,B,C)=AB+AC

F ( A, B, C ) AB(C C ) A ( B B )C

=m6+ m7+ m1+ m3

4. 卡诺图画法: 1) 卡诺图的构成与特点: 用小方格表示最小项,且按一定的规律排列。 卡诺图规律:凡几何位置相邻,其对应的最小项均是逻 辑相邻项。 任一行或一列两端的最小项也具有逻辑相邻性。

卡诺图的缺点:函数的变量个数不宜超过 5 个。

5.

用卡诺图表示逻辑函数:

ABC 000 001 010 011 100 101 110 111 F 0 0 0 1 0 1 1 1

1)已知逻辑函数的标准表达式(或真值表) 直接填入 与最小项相应的方格填1,其余填0。 F(A,B,C)=m3+ m5+ m6+ m7

F ABC ABC ABC

写出反函数的“与-或”式,按反函数填入。

A 0 1 BC 00 1 0 01 1 0 11 1 1 10 1 0

4. 最小项合并规律

利用最小项之间的相邻性合并最小项,即利用A+A=1 ,AB+AB=B 进行化简。 1) 两个相邻项 F=ABCD+ABCD=ACD

CD 00 00 01 11 10 1 01 1 1 1 1 11 10 1 1 1

F BC ABC ABD AC D

CD AB 00 01 11 10 1 00 01 1 1 1 1 1 1 1 11 10 AB 00 01 11 10

F BC ABD ACD

CD 00 01 1 1 1 1 1 1 1 1 11 10

例:

F A B BC BC AB

A B(C C) BC BC (A A ) AB