LVPECL详细讲解

存储基础(VG、LV、LP、PV、PP)资料讲解

存储基础(V G、L V、L P、P V、P P)传统UNIX磁盘存储存在的问题● 分区大小固定● 不能随意扩展分区● 文件系统和文件的大小受限制● 分区时需要大量的时间去计划传统UNIX的一个磁盘分区需要连续的磁盘空间,这样一个分区一但划定后如果发现其太小也不能在扩充了.如图如果发现分区1的空间不够尽管硬盘还有剩余空间但由于两部分不连续,这样分区1的大小不能该变了.由于分区需要占有连续的磁盘空间那么分区的空间大小受到系统硬盘空间的大小的限制,分区不能跨越硬盘存在.这样系统中的文件系统大小和文件大小除了受本身算法限制还要受硬盘大小的限制.在安装操作系统时系统管理员应该首先对系统硬盘进行分区,但分区划定后就不能改变其大小了这样需要系统管理员花时间和精力去很好的规划每个分区的大小.LVM(Logical Volume Manager)是由一组系统命令,系统调用和其它工具组成,用户使用它可以建立和控制系统的逻辑存储. 它通过逻辑视图存储空间数据和真实的物理硬盘的数据之间的对应关系管理磁盘资源.LVM在传统的磁盘驱动程序上加了一层逻辑卷设备驱动程序用于映射逻辑视图与物理硬盘间的数据.LVM由两部分组成:LVDD(Logical Volume Device Driver)和操作命令集.LVDD 负责管理和执行所有的I/O.它将逻辑地址转换成物理地址并将请求发送给相应的磁盘驱动程序.操作命令集包括一组系统调用和高级命令用于操纵LVM.这些高级命令一般以shell script形式出现,如lsvg表示列出系统的卷组.在这些script文件中包含许多LVM的基本命令,这些基本命令对应这一些系统调用.这些调用的API存放在liblvm.a中Physical partition(PP):硬盘存储的最小分配单位.当硬盘加入卷组中时系统安装卷组定义的PP大小对硬盘进行划分.PP的大小在创建VG时定义,以后就不能改变了.它的取值范围是1-1024M,以2的整数次幂变化.一个硬盘缺省时最多可以被划分成1016个PP.Physical Volume(PV):系统的物理硬盘,如果一个硬盘如果参与系统的存储分配,则需要将该硬盘加入的系统的卷组(VG)中或自己创建一个卷组.一个硬盘同时只能属于一个VG.图中的hdisk1,hdisk2,hdisk3为PV.Logical partition(LP):LP与PP相对应.一个LP一般对应一个PP,LP的大小与PP的大小相同.Logical Volume(LV):由同在一个卷组的一个或多个LP组成,它不需要占用连续的PV空间,它可以跨越硬盘存在可以动态的扩充容量.应用程序访问磁盘一般访问到LV这一层.LV中可以包括日志文件系统,Paging Space,日志log,BLV系统启动逻辑卷等.一般情况一个LV最大为64G,一个VG中最多包含256个LV.Volume Group(VG):AIX存储分配的最大单位,它包括一个或多个PV.一般情况下最多包括32个PV,一个系统最多有255个VG.VG从逻辑的角度来看还包含多个LV.在系统安装时系统会自动创建一个卷组rootvg.● 灵活的LV由于LV是由一个或多个LP组成,LP与PP相对应,这种对应关系被LVDD管理.LV可以不占用连续的物理硬盘空间这样LV在一个VG中可以跨硬盘存在,它的大小可以被动态增加,可以很容易的加镜像,可以很容易的被删除.● 高可靠性LVM通过镜像来提高数据的可靠性,被镜像的LV在系统中可以有2到3份拷贝.当一份数据被毁坏后系统可以用该数据的镜像.● 高性能LVM通过strping来提高系统访问数据的速度.strping技术将LV的数据分布到不同PV上访问这些数据时可以进行并行的读写.我们在创建LV时可以指定LV 在PV上的分布位置,我们将经常被访问的LV放在PV的热点位置可以提高访问速度.● 写校验LVM可以通过写校验对每次的磁盘写操作都被校验,提供数据的稳定性.● 动态管理我们可以在系统正常运行期间对系统的LV进行各种操作,操作后不需要重新启动机器.这些操作大部分对用户是透明的.● 容易使用我们课通过使用高级命令来管理系统存储也可以通过smit来管理系统存储.AIX的物理存储包括一些几个部分● VGAIX存储分配的最大单位,它包括一个或多个PV.一般情况下最多包括32个PV,一个系统最多有255个VG.VG从逻辑的角度来看还包含多个LV.在系统安装时系统会自动创建一个卷组rootvg.在一个VG中分配空间时是以PP为单位分配,VG中的所有PV作为一个整体进行使用.一个VG的PP大小在创建VG时定义,这个值以后不能在被改变.一个VG可以直接的从一个系统迁移到另一个系统中.● PV系统的物理硬盘,如果一个硬盘如果参与系统的存储分配,则需要将该硬盘加入的系统的卷组(VG)中或自己创建一个卷组.一个硬盘同时只能属于一个VG.当一个PV被加入到系统中在系统的/dev目录下创建hdiskn的设备文件与其对应.● PP硬盘存储的最小分配单位.当硬盘加入卷组中时系统安装卷组定义的PP大小对硬盘进行划分.PP的大小在创建VG时定义,以后就不能改变了.它的取值范围是1-1024M,以2的整数次幂变化.一个硬盘缺省时最多可以被划分成1016个PP.用户可以给rootvg(在安装系统是自动创建)中加硬盘,也可以创建新的卷组我们为什么创建新的卷组● 将用户数据与系统数据分开我们在系统升级后重新安装操作系统时只对系统的rootvg进行操作,如果用户数据集中在rootvg上那么在重新安装系统时有可能毁坏用户数据(安装方式决定是否会毁坏用户数据).系统的崩溃一般也发生在rootvg上.这样我们将用户数据放在其他VG中可以提供用户数据的稳定性.● 灾难恢复系统提供的备份方式中有一种是卷组备份,如果我们对系统的每个卷组都进行了这样的备份,当发生故障时可以很快的恢复系统和用户数据.● 数据维护当我们希望用户数据不被用户访问而系统还需要正常运行,如果这些数据被放在一个独立的卷组中我们可以使用varyoffvg的命令时这个卷组暂时不被激活.● 数据移动我们在系统间移动数据时,不能以硬盘为单位移动只能以vg为单位移动.●VGDAVGDA(Volume Group Descriptor Area)是包含在卷组中硬盘上的一个区域.卷组中的每一个硬盘至少有一个VGDA区,同一个卷组中所有硬盘的VGDA内容是一样的.VGDA中存放的是关于卷组的管理信息如卷组的ID号,包含的硬盘ID,逻辑卷ID还存放PP与LP的对应关系.●Quroum当VG被激活时系统会对该卷组中的VGDA进行表决以决定是否可以激活该卷组.VGAD的表决数用于确保卷组的管理数据的完整性,这个数是该卷组的VGDA 数量的51%或51%以上.如图包含两块硬盘的VG有3个VGDA,其表决数为2.如果只包含一个VGDA的硬盘坏了该卷组还可以被激活,反之则不能被激活.由于卷组中的每个硬盘都包含至少一个VGDA,如果硬盘过多VGDA的管理不太容易所有一般来讲每个卷组最好只包含3到4块硬盘即可.LVM菜单被用于管理许多的系统存储●Volume Group 用于管理VG●Logical Volume 用于管理LV.由于LV包括paging space,文件系统,他们都有相应的管理菜单,这里只提供一些地层的管理菜单.●Physical Volume 用于管理PV●Paging Space 用于管理系统页面交换空间.我们使用smit vg的命令可以得到卷组管理菜单镜像卷组可以将卷组中的所有逻辑卷进行镜像使用的命令是mirrorvg.●列出所有的卷组lsvg命令列出系统中所有已经定义的卷组(无论是否被激活)lsvg -o 列出现在处于激活状态的卷组●列出一个卷组的内容我们使用lsvg vgname的命令可以得到该卷组的状态和该卷组的内容.PP SIZE 表示卷组中PP的大小.State表示卷组的状态.LVs表示该卷组中逻辑卷的个数,TOTAL PPs表示卷组中PP的个数,FREE PPs表示当前卷组中未分配的PP个数,QUORUM表示卷组的表决数.VG DESCRIPTORS表示卷组的VGDA数量.●列出卷组中硬盘lsvg -p 卷组名可以列出该卷组所包含的硬盘名称,状态,每个硬盘的中PP个数,未分配PP的个数,未分配的PP在拼音的位置.●列出卷组中逻辑卷用lsvg -l 卷组名可以列出该卷组中所有定义的逻辑卷的名称,类型,LV包含的LP的个数和PP的个数,LV跨越硬盘的个数,LV的状态,如果LV是被用于文件系统的列出它的mount点.LV的类型用paging,日志log,启动LV和日志文件系统.LV的状态表示该卷组是否可以被访问,open表示可以被使用,closed表示是不能被访问(如果LV的类型是文件系统closed表示该文件系统没有被mount).syncd表示LV的内容是同步的(LV做镜像时有用,如果不同步则表示为staled状态).●增加卷组在这个smit对话框中我们必须选择的是新卷组包含的硬盘名称,该硬盘已经不能属于其他卷组.我们可以根据硬盘的大小指定卷组的PP大小缺省为4M,卷组名称如果没有声明则以vgnn命名nn表示为数字,卷组主设备号,是否创建为并行卷组,在并在模式下自动被激活这三个选项用于HACMP中.创建卷组的命令是mkvg.●删除卷组当卷组中最后一块硬盘被删除该卷组会被自动删除.●给卷组中增加一个硬盘我们用 extendvg -f Volumegroup hdiskn 的命令可以个卷组中增加一块硬盘,当一块yp被加入到某个卷组时系统会安装该卷组的PP大小对硬盘进行划分该硬盘中所有内容将会被清除.-f选项表示自动确认将将硬盘加入到卷组当中.●从卷组中删除一个硬盘用reducevg [-d] Volumegroup hdiskn可以从卷组中删除一块硬盘,删除前需要先将该硬盘的内容清除或移动到别的硬盘上.-d选择表示可以不做清除或移动工作而将性删除.一个卷组创建后我们可以修改卷组的部分属性如卷组在下一次系统启动时是否自动被激活,卷组被激活后是否还需要vgda表决数如果需要则卷组中硬盘的失效影响导致好的VGDA数量不足表决数则卷组自动变成不可使用状态.我们创建逻辑卷时可以指定该逻辑卷在硬盘的位置,如果创建时指定位置已经被使用则系统会自动分配其他位置给该逻辑卷.系统使用一段时间后管理员发现指定位置已经被释放我们可以利用reorgvg的命令来重新安装lv的位置定义调整卷组中lv的位置.reorgvg volumegroup [lvname].如#reorgvg vg3 lv04 lv07 可以调整lv04和lv07在vg3上的位置.安装lv名字在命令中出现的次序依次调整.这种调整对用户是透明的.●激活一个卷组varyonvg [-s] Volumegroup如果系统启动时我们发现一些卷组没有被自动激活我们可以使用#varyonvg datavg的命令将datavg激活.-s选项可以将vg激活到维护模式,这时只能对其使用管理命令,其他操作不允许.●使一个卷组处于非激活状态varyoffvg [-s] Volunegroup可以将一个处于激活状态的卷组变为非激活状态.使用该命令时卷组中的所有lv必须处于closed状态.-s表示将该卷组变为维护模式.我们有时需要将一个卷组从一个系统A移动到另一个系统B并希望保留该卷组上的所有数据,这时我们可以在A系统上使用exportvg的命令将卷组从A系统中删除,在B系统安装识别好该卷组中的硬盘后使用importvg的命令将该卷组引入到B系统上.使用exportvg时需要该卷组处于非激活状态.这些命令常用在HACMP中和系统升级后导入以前的非rootvg卷组的内容.Logical partition(LP):LP与PP相对应.一个LP一般对应一个PP,LP的大小与PP的大小相同.Logical Volume(LV):由同在一个卷组的一个或多个LP组成,它不需要占用连续的PV空间,它可以跨越硬盘存在可以动态的扩充容量.应用程序访问磁盘一般访问到LV这一层.LV中可以包括日志文件系统,Paging Space,日志log,BLV系统启动逻辑卷等.一般情况一个LV最大为64G,一个VG中最多包含256个LV.●镜像是一个LP在同一个卷组中对应1块以上的PP.即该LP的内容在系统中用1份以上的拷贝.当我们创建逻辑卷时我们可以声明对该lv中的lv做镜像,我们也称为该lv做镜像.通常lv的每一份拷贝都应该放在不同的不同的物理硬盘上.我们可以给lv加镜像也可以删除其镜像.● 镜像的读写策略● 并行策略并行的写是指系统在对该lv进行写操作时,几块拷贝同时写当最后一份拷贝写完后将控制权交给用户.读策略表示系统读取lv内容时哪一个拷贝近就读那一块.● 串行策略串行写表示系统在对该lv进行写操作时先写第一份拷贝,写完后在写第二份.当最后一份写完后将控制权交给用户.读策略表示系统读取lv内容时先读第一份拷贝如果读不出则在读第二份拷贝.● 正常lv的数据块分布正常的率数据块时连续分布到不同的硬盘上,这样在读写数据时总是不能达到并行读写.● stripe lv的数据块分布strping技术将LV的数据分布到不同PV上访问这些数据时可以进行并行的读写.如图在读写数据时1,2,3块数据由于分布在不同的硬盘上可以同时进行操作.一个striped的lv不能做镜像,而且使用stripe时至少需要两块硬盘而且每一块硬盘必须有其独立的读写器.striped lv的数据块单位不使用lp而使用stripe的块单位.● intra-pv 分布策略当我们创建逻辑卷时或修改逻辑卷时我们可以指定lv在硬盘的分布方式,intra 分布方式指的是lv在硬盘上的位置,系统如图将硬盘分为5个部分边缘,中部,中心,内中部,内边缘.其中中心部分访问速度最快,中部其次,边缘最慢.我们可以将经常使用的逻辑卷放在硬盘的中心部分.● inter-pv 分布策略inter分布方式指的是lv跨越硬盘的个数,其有两个选项minimum分布到最少数量的硬盘,maximum分布到最多数量的硬盘.我们可以使用smit lv的得到的smit菜单管理逻辑卷●列出系统中所有的lv●显示lv的属性COPIES表示lv是否有镜像,如果该值为1表示没有镜像.LPs表示LV包含的LP 的个数.Mirror Write Consistency表示如果镜像是否做镜像写校验,SCHED POLICY表示如果有镜像镜像的策略是什么.●列出lv在硬盘上的映射列出该lv在硬盘上的分布情况,COPIES表示该lv的不同拷贝在硬盘上的PP数量.以:为分隔符第一个域为第一拷贝,第二个域为第二拷贝,第三个域为第三拷贝.IN BAND表示满足分布策略的PP的百分比.●列出lv的lp在硬盘上的分布显示该逻辑卷上的LP给个拷贝与硬盘上的PP的映射关系.我们使用mklv可以创建一个新的逻辑卷.在smit对话框中我们必须填写的是卷组名,lv的lp个数.我们也可以指定lv所有的硬盘,指定lv的分布策略,也可以修改Munber of COPIES of each logical Partition的值来创建带有镜像的lv.如果没有指定lv的名称系统自动分配名称为lvnn,nn表示数字.我们可以用rmlv命令删除定义好的逻辑卷,删除前该逻辑卷需要处于closed状态.不要用rmlv命令删除日志文件系统和paging space.我们可以使用chlv命令修改lv的部分属性如分布策略,镜像策略和读写权限.使用chlv -n的命令可以修改lv的名称使用extendlv命令来扩充lv的大小,lv的大小不能被动态的减小.我们用mklvcopy可以增加一个逻辑卷的拷贝数,一个逻辑卷最多有3个拷贝.拷贝增加后需要对所有拷贝做同步,我们可以在使用mklvcopy命令时加-k选项即可.也可以在加完拷贝后用syncvg的命令进行同步.我们用rmlvcopy删除lv的拷贝.在使用smit方式增加lv拷贝时我们需要注意我们填写的拷贝数是新的总拷贝数.● 列出系统中的所有物理卷可以得到物理卷的名称,物理卷的ID号,物理卷所属的卷组● 列出物理卷的属性VG DESCRIPTORS表示该物理卷中包含的VGDA数量,分配的PP的分布情况,未分配的PP的分布情况● 列出物理卷中的逻辑卷可以显示该物理卷上所有逻辑卷的分布情况● 显示物理卷的PP使用情况●增加一个硬盘增加一个硬盘可以通过smit来增加或通过cfgmgr的命令来配置.●移动一个物理卷的内容我们用migratepv [-l lvname] sourcePV targetPV将一个硬盘上的所有内容或几个逻辑卷的内容迁移到另一个硬盘上.目标盘和源盘必须在同一个卷组之内.我们一般在替换硬盘时使用这个命令.例如#migratepv -l lv02 hdisk0 hdisk6将hdisk0上的lv02的内容迁移到hdisk6上.。

Labview技巧集锦

Labview 技巧集锦1.不知您是否注意到,在LV80的比较模板上新增加了一个称作“空数组?”的函数,您可以连接任意数据类型和任意维数,返回一个布尔值表明您连接的数组是否为空。

这比我们过去用的方法更为智能,过去我们是通过检查数组的长度来实现的,对于多维,我们不得不把所有的长度乘在一起来判断是否为0。

2.比较模板上另一个函数是“Empty String/Path”,但是您知道吗,除了string/path之外,它实际支持五种类型为空的检测,string,path,variant,picture,DSC tag.3.当前VI同一目录下VI路径的技巧。

方法一:方法二:方法三:4.您使用过“Merge Error vi?”吗?如果您用PROFILE检查您应用程序的性能的话,您会很惊讶该函数会耗费很大的运行时间。

主要是因为必须重复检查每个ERROR中是ERROR 还是warning,如果您不关心W ARNING的话,可以用Select 函数来实现。

5.对于FRONT PANNEL中Array,判断数组长度的最佳办法是:鼠标右击ARRAY,选择Advanced>Show Last Element,数组索引自动切换到最后一个元素,LV8后数组增加了SCROLL BAR,鼠标右击数组选择Visable Itmes>Vertical (or Horizontal) Scroll Bar.,更为灵活。

6.在Case structure or Event Structure 中,Ctrl+Mouse Wheel 浏览不同的Frame.7.快速建立Control Reference:从Refnum 模板中,建立一个Control Reference,直接拖动FRONT PANEL中Control 到Reference Control中。

8.Icon:为vi生成新图标时,如何从一个空白框开始呢,双击ICON EDITOR中Select Rectangle(虚框),按DEL删除。

LVPECL详细讲解

LVPECL详细讲解LVPECL即Low Voltage Positiv e Emitter-CoupleLogic,也就是低压正发射极耦合逻辑,使用3.3V或2.5V电源,LVPECL是由PECL演变而来的,PECL即 Positiv e Emitter-CoupleLogic,也就是正发射极耦合逻辑的意思,使用 5.0V电源,而PECL是由E CL演变而来的,ECL即Emi tter-CoupleLogic,也就是发射极耦合逻辑,ECL有两个供电电压VCC和VEE。

当VEE接地时,VCC接正电压时,这时的逻辑称为P ECL;当当VCC接地时,VEE接负电压时,这时的逻辑成为N EC L,VEE一般接-5.2V电源;一般狭义的EC L就是指NE CL。

ECL分类:ECL/PECL/LVPECL逻辑的优点:1. 输出阻抗低(6~8ohm),输出阻抗高(可以看作无穷大),所以驱动能力特别强,它可以驱动50~130ohm特征阻抗的传输线而交流特性并没有明显的改变。

由于驱动能力强,所以支持更远距离的传输,所以背板走线或长线缆传输基本上都使用E C L逻辑。

2. ECL器件对电压和温度的变化不如TTL和CMOS器件敏感,ECL时钟驱动器产生的各路时钟的并发性更好,skew更小。

3. 相对于同为差分信号的LVDS,ECL支持的速率更高,受工艺的限制,L VDS的逻辑很少有高于1.5GHz的应用,而ECL可以应用高于10G H z的场合,可以说,高于5GHz的场合,基本上是ECL和CML的天下。

在所有的数字电路中,ECL的工作速度最高,其延时小于1n s,在中小规模集成电路,高速,超高速数字系统和设备中应用。

4. 对传输线阻抗的适应范围更宽。

L VDS属于电流型驱动,其终端的100ohm匹配电阻兼有产生电压的功能。

Labview的使用技巧

0Labview的使用技巧对于LabVIEW中用于定时的两个最常用的vi就是Wait (ms).vi 以及 Wait Until Next ms Mul tiple,本文将用实际例子来讲述这两个vi的区别。

不想看后面的详细讨论的可以只看下面几个结论即可:1.如果想实现定周期While循环时,需要用Wait(ms).vi而不是Wait Until Next ms Multiple.vi2.Wait(ms).vi在与代码并行时可以保证整个运行时间为设定值,这个功能一般都会以为是Wait Until Next ms Multiple.vi的特性3.Wait Until Next ms Multiple.vi 并非想象中那么好用,它会造成不少的问题,至少第一次的运行时间无法保证为设定值。

4.在代码执行时间没超过设定值时,两者可以通过编程实现大致相同的功能,但是当代码执行时间很大时,两者的处理方法是截然不同的。

一.Wait (ms)对于Wait (ms) 这个vi来说需要分两部分来讨论,即它是被顺序地放入代码中还是并行地放入代码中,这两种方式的不同将导致它起的作用完全不同。

(1)顺序模式看一下附带程序中的Wait Sequence Demo 1.vi ,在一个While循环中,首先用Time Dela y.vi延时0.05s,然后顺序地使用Wait (ms).vi,设为20ms。

最后运行后的结果如下图,循环的周期在70ms左右。

从结果中可以得知,在顺序模式中,Wait (ms).vi是实打实地延时了所设定的时间,如果其他顺序中的代码耗了时间后,那整个循环的时间就是代码时间+延时的时间。

即使在此例中将Ti me Delay换成一些其他消耗一定时间的code后结果也是一样。

(2)并行模式当在并行模式时,在不是跑Real-Time时,Wait (ms)这个vi竟然是能保证整个循环周期是所设定的值,我们看下面的例子(Wait Parallel Demo 1.vi),程序如下:循环中有n多Wait(ms).vi,运行后的结果是循环周期是20ms,因此可以初步得出结论,对于Wait(ms).vi与其他代码并行时,它会保证整个部分的运行时间是所设定的值(millisecond es to wait)。

LVPECL端接技术

应用笔记:HFAN-1.0Rev. 1; 4/08LVDS、PECL和CML介绍[本应用笔记中的一些器件最初发布于2000年7月3日1120期的Electronic Engineering Times]Maxim Integrated Products1引言 (1)2PECL接口 (1)2.1PECL输出结构 (1)2.2PECL输入结构 (2)3CML接口 (3)3.1CML输出结构 (3)3.2CML输入结构 (3)4LVDS接口 (4)4.1LVDS输出结构 (4)4.2LVDS输入结构 (4)5接口互连 (6)5.1CML到CML的连接 (6)5.2PECL到PECL的连接 (6)5.2.1直流耦合:驱动50Ω至(V CC-2V)的戴维宁等效电路 (6)5.2.2交流耦合 (7)5.3LVDS与LVDS的连接 (8)6LVDS、PECL、CML间的互连 (8)6.1LVPECL到CML的连接 (8)6.1.1交流耦合 (8)6.1.2直流耦合 (9)6.2CML到LVPECL的连接 (11)6.3LVPECL到LVDS的连接 (11)6.3.1直流耦合 (11)6.3.2交流耦合 (11)6.4LVDS到LVPECL的连接 (11)6.4.1直流耦合 (11)6.4.2交流耦合 (13)6.5CML和LVDS间互连 (14)图 1. PECL输出结构 (1)图 2. PECL输入结构 (2)图 3.CML输出结构 (3)图 4. 直流耦合与交流耦合情况下,CML输出波形 (3)图 5. CML输入电路配置 (3)图6. LVDS输出结构 (4)图7. LVDS输入结构 (4)图 8. CML到CML的连接 (6)图 9. 戴维宁等效变换 (6)图 10. PECL与PECL之间的直流耦合 (7)图 11.PECL与PECL之间的交流耦合 (7)图 12. LVDS与LVDS的连接 (8)图 13. LVPECL与CML之间的交流耦合 (8)图 14. LVPECL与CML之间的电阻网络(MAX3875) (9)图 15. LVPECL与CML之间的直流耦合(MAX3875) (9)图 16. CML与LVPECL之间的交流耦合 (10)图 17. LVPECL与LVDS之间的直流耦合 (10)图 18. LVPECL与LVDS之间的交流耦合 (11)图 19. LVDS与LVPECL之间的直流耦合 (12)图 20. LVDS与LVPECL之间的交流耦合 (13)图 21. CML与LVDS之间的交流耦合 (14)图 22. LVDS与CML之间的交流耦合 (14)LVDS、PECL和CML I/O结构1引言随着高速数据传输业务需求的增加,如何高质量地解决高速IC芯片间的互连变得越来越重要。

lvpecl 的共模电压

lvpecl 的共模电压

LVPECL是一种常见的差分信号标准,它具有许多优点,如高速、低抖动和低

功耗等特性。

在LVPECL电路中,共模电压是一个重要的参数,它对电路的性能

和稳定性有着重要影响。

共模电压是LVPECL电路中的一个重要参数,它是指差分信号的两个端口的共同参考电压。

在LVPECL电路中,共模电压通常被设置为一定的值,以确保差分

信号的稳定性和正确性。

共模电压的准确设置可以确保LVPECL电路的正常工作,避免信号失真和干扰。

在LVPECL电路中,共模电压的设置通常需要考虑以下几个因素:

1. 差分信号的幅度:共模电压的设置需要考虑差分信号的幅度范围,以确保差

分信号在电路中的正常工作范围内。

2. 输入电平:共模电压的设置还需要考虑输入信号的电平范围,以确保电路对

输入信号的适应性和稳定性。

3. 电源电压:共模电压的设置还需要考虑电源电压的稳定性和范围,以确保电

路的正常工作和可靠性。

在实际的LVPECL电路设计中,共模电压的设置通常需要通过仿真和实验来确定。

设计者需要根据电路的具体要求和性能指标,选择合适的共模电压设置方案,并进行验证和调整,以确保电路的性能和稳定性。

总的来说,共模电压是LVPECL电路中的一个重要参数,它对电路的性能和稳定性有着重要的影响。

设计者在设计LVPECL电路时,需要合理设置共模电压,

以确保电路的正常工作和性能优化。

通过仿真和实验,设计者可以确定最佳的共模电压设置方案,从而提高电路的性能和可靠性。

vcs ucil语法

vcs ucil语法

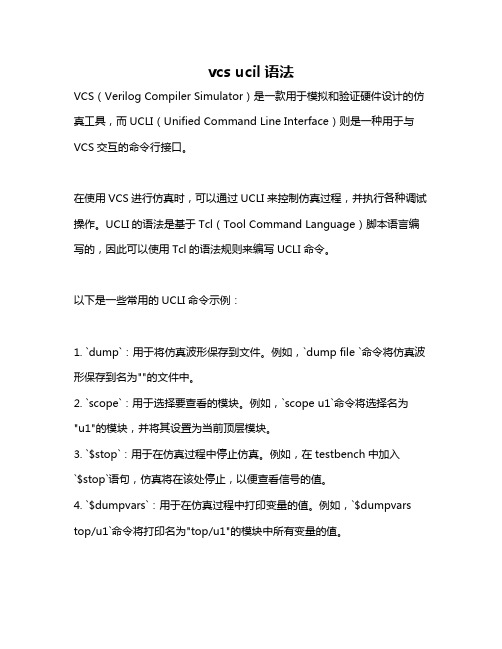

VCS(Verilog Compiler Simulator)是一款用于模拟和验证硬件设计的仿真工具,而UCLI(Unified Command Line Interface)则是一种用于与VCS交互的命令行接口。

在使用VCS进行仿真时,可以通过UCLI来控制仿真过程,并执行各种调试操作。

UCLI的语法是基于Tcl(Tool Command Language)脚本语言编写的,因此可以使用Tcl的语法规则来编写UCLI命令。

以下是一些常用的UCLI命令示例:

1. `dump`:用于将仿真波形保存到文件。

例如,`dump file `命令将仿真波形保存到名为""的文件中。

2. `scope`:用于选择要查看的模块。

例如,`scope u1`命令将选择名为"u1"的模块,并将其设置为当前顶层模块。

3. `$stop`:用于在仿真过程中停止仿真。

例如,在testbench中加入

`$stop`语句,仿真将在该处停止,以便查看信号的值。

4. `$dumpvars`:用于在仿真过程中打印变量的值。

例如,`$dumpvars top/u1`命令将打印名为"top/u1"的模块中所有变量的值。

5. `$set`:用于设置仿真参数。

例如,`$set debug_level 3`命令将设置调试级别为3。

6. `$run`:用于开始仿真。

例如,`$run 100ms`命令将运行仿真100毫秒。

以上是一些常用的UCLI命令示例,但UCLI还提供了许多其他命令和功能,可以根据需要进行学习和使用。

labview之术语索引

波形显示控件

按照处理测量数据的方式和显示过程的不同,LabVIEW 波形显示控件主要分为两类: 事后记录图(Graph):基本数据结构是数组,一次显示完成 实时趋势图(Chart):基本数据结构是数据标量或数组,连续不断显示

移位寄存器

Label

标签

运行 VI

1/5

1.运行 VI(Run) 2.连续运行 VI(Run Continuously) 3.停止运行 VI(Abort Execution) 4.暂停运行 VI(Pause) 调试 VI 1. 单步执行

单步(入),单步(跳),单步(出) 2.设置端点 3.设置探针 4.显示数据流动画 数据类型: 基本数据类型:数字型(Numeric),布尔型(Boolean),字符串型(String) 构造数据类型:数组(Array),簇(Cluster) 其它数据类型:枚举(RefNum),空类型

簇(Cluster): 类似于 Pascal 语言的 record 和 C 语言的 struct

2/5

组成:不同的数据类型 创建:控制面板—>Array & Cluster 子面板;向框架添加所需的元素;根据需要更改簇和簇 中元素的名称 使用: 1.Unbundle 解包。获得簇中元素的值 2.Bundle 打包。将相互关联的不同数据类型的数据组成一个簇,或给簇中的某个元素赋值 3.Unbundle By Name 按名称解包。获得由元素名称指定簇中相应元素的值 4.Bundle By Name 按名称打包。将相互关联的不同数据类型的数据组成一个簇,或给簇中 的某个元素赋值 5.Build Cluster Array 建立簇的数组 6.Index & Bundle Cluster Array 将输入数组的元素按照索引组成簇,然后将这些簇组成一个 数组 7.Cluster To Array 将簇转化为数组 8.Array To Cluster 将数组转化为簇

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LVPECL详细讲解

LVPECL即Low Voltage Positive Emitter-Couple Logic,也就是低压正发射极耦合逻辑,使用3.3V或2.5V电源,LVPECL是由PECL演变而来的,PECL即 Positive Emitter-Couple Logic,也就是正发射极耦合逻辑的意思,使用5.0V电源,而PECL是由ECL演变而来的,ECL即Emitter-Couple Logic,也就是发射极耦合逻辑,ECL有两个供电电压VCC和VEE。

当VEE接地时,VCC接正电压时,这时的逻辑称为PECL;当当VCC接地时,VEE接负电压时,这时的逻辑成为NEC L,VEE一般接-5.2V电源;一般狭义的ECL就是指NECL。

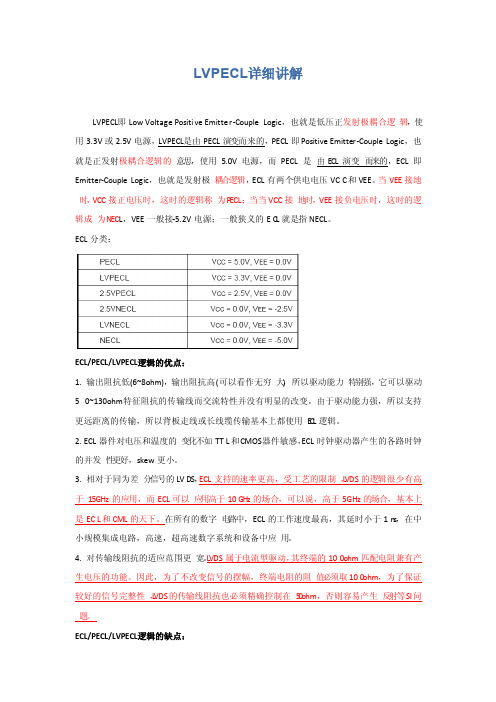

ECL分类:

ECL/PECL/LVPECL逻辑的优点:

1. 输出阻抗低(6~8ohm),输出阻抗高(可以看作无穷大),所以驱动能力特别强,它可以驱动50~130ohm特征阻抗的传输线而交流特性并没有明显的改变。

由于驱动能力强,所以支持更远距离的传输,所以背板走线或长线缆传输基本上都使用ECL逻辑。

2. ECL器件对电压和温度的变化不如TTL和CMOS器件敏感,ECL时钟驱动器产生的各路时钟的并发性更好,skew更小。

3. 相对于同为差分信号的LVDS,ECL支持的速率更高,受工艺的限制,LVDS的逻辑很少有高于1.5GHz的应用,而ECL可以应用高于10GHz的场合,可以说,高于5GHz的场合,基本上是ECL和CML的天下。

在所有的数字电路中,ECL的工作速度最高,其延时小于1ns,在中小规模集成电路,高速,超高速数字系统和设备中应用。

4. 对传输线阻抗的适应范围更宽。

LVDS属于电流型驱动,其终端的100ohm匹配电阻兼有产生电压的功能。

因此,为了不改变信号的摆幅,终端电阻的阻值必须取100ohm,为了保证较好的信号完整性,LVDS的传输线阻抗也必须精确控制在50ohm,否则容易产生反射等SI问题。

ECL/PECL/LVPECL逻辑的缺点:

跟它的优点一样,ECL的缺点也很明显,那就是功耗大,噪声容限小,抗干扰能力弱。

ECL电路的逻辑摆幅只有0.8V,直流噪声容限只有200mV。

可以说,ECL的高速性能是用高功耗、低噪声容限为代价换来的。

PECL的标准输出负载是50ohm至VCC-2V的电平上,在这种负载条件下,OUT+与OUT-的静态电平典型值为VCC-1.3V,OUT+与OUT-的输出电流为14mA。

PECL的输出电路结构:

PECL的输入是一个具有高输入阻抗的差分对,该差分对的共模电压需要偏置到VCC-1.3V,这样允许的输入信号电平动态最大。

有的芯片在内部已经集成了偏置电路,使用时直接连接即可,有的芯片没有加,使用时需要在芯片外部加直流偏置。

PECL的输入电路结构:

PECL的逻辑电平指标:

(注:专业文档是经验性极强的领域,无法思考和涵盖全面,素材和资料部分来自网络,供参考。

可复制、编制,期待你的好评与关注)。