DSPc55x锁相环初始化程序的理解

第5章 TMS320C55x的片内集成外设开发及测试

2014年3月5日

TMS320C55x DSP原理及应用

1

第5章 TMS320C55x的片内集成外设开发及 测试(1) 5.1 C55x片内外设与芯片支持库简介 5.2 时钟发生器 5.3 通用定时器与DSP中断 实验2.1 指示灯实验 实验2.2 拨码开关实验 实验2.3 DSP定时器

2014年3月5日 TMS320C55x DSP原理及应用 2

3.失锁

锁相环对输入时钟跟踪锁定之后,由于其他原因使其 输出时钟发生偏移,即失锁。出现失锁现象后,PLL的动 作由时钟模式寄存器中的IOB确定。

2014年3月5日

TMS320C55x DSP原理及应用

15

第5章 TMS320C55x的片内集成外设开发及测试

五、

使用方法及实例

调用时钟发生器库函数首先要在头文件中包含csl_pll.h文件。 首先要声明PLL配置结构,具体声明如下: PLL_Config Config_PLL = { 1, /*iai 休眠后重新锁相 */ 1, /*iob 失锁后进入旁路模式并重新锁相 */ 6, /*倍频系数PLLMULT=6*/ 0 /*1分频, CLKOUT= DSP主时钟/(div+1) */ }; 之后运行配置函数: PLL_config(&Config_PLL); 也可以通过函数设置PLL频率: PLL_setFreq(6, 1); 通过PLL_setFreq函数可以复位PLL锁相环,并改变倍频和分频数 从而得到所需的频率。

一、时钟模式寄存器(CLKMD) 功能:控制时钟发生器的工作状态。

表5-1 时钟模式寄存器CLKMD

位 15 字 段 数 值 保留 说 明 Rsvd

14

IAI

0

DSP入门必须掌握知识点

1.DSP选型:主要考虑处理速度、功耗、程序存储器和数据存储器的容量、片内的资源,如定时器的数量、I/O 口数量、中断数量、DMA通道数等。

DSP的主要供应商有TI,ADI,Motorola,Lucent和Zilog等,其中TI占有最大的市场份额。

选择DSP可以根据以下几方面决定:1)速度:DSP速度一般用MIPS或FLOPS表示,即百万次/秒钟。

根据您对处理速度的要求选择适合的器件。

一般选择处理速度不要过高,速度高的DSP,系统实现也较困难。

2)精度:DSP芯片分为定点、浮点处理器,对于运算精度要求很高的处理,可选择浮点处理器。

定点处理器也可完成浮点运算,但精度和速度会有影响。

3)寻址空间:不同系列DSP程序、数据、I/O 空间大小不一,与普通MCU不同,DSP在一个指令周期内能完成多个操作,所以DSP的指令效率很高,程序空间一般不会有问题,关键是数据空间是否满足。

数据空间的大小可以通过DMA的帮助,借助程序空间扩大。

4)成本:一般定点DSP的成本会比浮点DSP的要低,速度也较快。

要获得低成本的DSP系统,尽量用定点算法,用定点DSP。

5)实现方便:浮点DSP的结构实现DSP系统较容易,不用考虑寻址空间的问题,指令对C语言支持的效率也较高。

6)内部部件:根据应用要求,选择具有特殊部件的DSP。

如:C2000适合于电机控制;OMAP适合于多媒体等。

1)C5000系列(定点、低功耗):C54X,C54XX,C55X相比其它系列的主要特点是低功耗,所以最适合个人与便携式上网以及无线通信应用,如手机、PDA、GPS等应用。

处理速度在80MIPS--400MIPS之间。

C54XX和C55XX一般只具有McBSP同步串口、HPI并行接口、定时器、DMA等外设。

值得注意的是C55XX提供了EMIF外部存储器扩展接口,可以直接使用SDRAM,而C54XX则不能直接使用。

两个系列的数字IO 都只有两条。

2)C2000系列(定点、控制器):C20X,F20X,F24X,F24XX ,C28x该系芯片具有大量外设资源,如:A/D、定时器、各种串口(同步和异步),WATCHDOG、CAN总线/PWM 发生器、数字IO 脚等。

第3章 TMS320C55x的指令系统

2016年3月2日

TMS320C55x DSP原理及应用

13

第3章

TMS320C55x的指令系统 AR间接寻址DSP模式

序 1

号

操作数

在生成地址之后,ARn 加上 在生成地址之后增加: 在生成地址之前增加: T0或ARn 中16位带符号的常数:如果 16位操作,ARn =ARn C54CM + 1= 0,ARn =ARn + T0 在生成地址之后,ARn 减去 在生成地址之后减少: 在生成地址之前减少: T0或ARn 中16位带符号的常数:如果 16位操作,ARn =ARn C54CM 1 = 0,ARn =ARnT0

地址修改 ARn未修改 在生成地址之后增加:16位操作,ARn =ARn + 1

*ARn

2

3

*ARn +

*ARn

32位操作,ARn =ARn + 2

在生成地址之后减少:16位操作,ARn =ARn1 32位操作,ARn =Arn2 在生成地址之前增加:16位操作,ARn =ARn + 1 32位操作,ARn =ARn + 2 在生成地址之前减少:16位操作,ARn =ARn1 32位操作,ARn =ARn2 在生成地址之后,ARn 加上T0 中16位带符号的数: ARn =ARn + T0

(1)DP寄存器:DP确定在主数据页内长度为128字节的局部数据页的 起始地址,该起始地址可以是主数据页内的任何地址。 (2)由汇编器计算出的7位偏移量(Doffset):偏移量的计算与访问的 是数据空间还是存储映射寄存器(限定词是mmap())有关。

由DPH和DP构成扩展数据页寄存器XDP,可以将 DPH和DP分别载入,也可以用一条指令载入XDP。

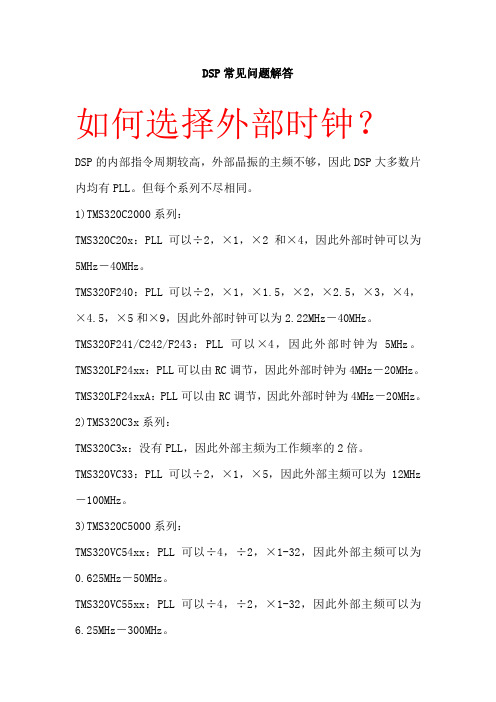

DSP常见问题解答

DSP常见问题解答如何选择外部时钟?DSP的内部指令周期较高,外部晶振的主频不够,因此DSP大多数片内均有PLL。

但每个系列不尽相同。

1)TMS320C2000系列:TMS320C20x:PLL可以÷2,×1,×2和×4,因此外部时钟可以为5MHz-40MHz。

TMS320F240:PLL可以÷2,×1,×1.5,×2,×2.5,×3,×4,×4.5,×5和×9,因此外部时钟可以为2.22MHz-40MHz。

TMS320F241/C242/F243:PLL可以×4,因此外部时钟为5MHz。

TMS320LF24xx:PLL可以由RC调节,因此外部时钟为4MHz-20MHz。

TMS320LF24xxA:PLL可以由RC调节,因此外部时钟为4MHz-20MHz。

2)TMS320C3x系列:TMS320C3x:没有PLL,因此外部主频为工作频率的2倍。

TMS320VC33:PLL可以÷2,×1,×5,因此外部主频可以为12MHz -100MHz。

3)TMS320C5000系列:TMS320VC54xx:PLL可以÷4,÷2,×1-32,因此外部主频可以为0.625MHz-50MHz。

TMS320VC55xx:PLL可以÷4,÷2,×1-32,因此外部主频可以为6.25MHz-300MHz。

4)TMS320C6000系列:TMS320C62xx:PLL可以×1,×4,×6,×7,×8,×9,×10和×11,因此外部主频可以为11.8MHz-300MHz。

TMS320C67xx:PLL可以×1和×4,因此外部主频可以为12.5MHz-230MHz。

第3章__TMS320C55x的指令系统

12

第3章 TMS320C55x的指令系统

DP直接寻址模式

XDP

DPH

000 0000 ~

000 0000

000 0001 ~

000 0001

000 0010 ~

000 0010

~

111 1111 ~

111 1111

2021/7/22

(DP+Doffset)

0000 0000 0000 0000 ~XDP

~

~

0000 0000 0000 0000 ~

1111 1111 1111 1111

第127主数据页:02 0000h~02 FFFFh

2021/7/22

TMS320C55x DSP原理及应用

16

例3-4,*SP(offset)用于数据存储器寻址。设 SPH=0,SP = FF00h。

MOV *SP(5),T2 ;SPH:(SP+offset)=00 FF05h, ;CPU从00 FF05h 处读取数据装入T2 MOV dbl(*SP(5)), pair(T2) ;SPH:(SP+offset)=00 FF05h,SPH:(SP+offset–1)=00 FF04h ;CPU从00 FF05h和00 FF04h处读取数据装入T2和T3

2021/7/22

TMS320C55x DSP原理及应用

4

第3章 TMS320C55x的指令系统

DPH

000 0000 ~

000 0000

.

000 0001 ~

000 0001

000 0010 ~

000 0010

~

111 1111 ~

111 1111

DSP常见问题

在CCS下,OUT文件加载时提示“Data verification failed...”的原因?Link的CMD文件分配的地址同GEL或设置的有效地址空间不符。

中断向量定位处或其它代码、数据段定位处,没有RAM,无法加载OUT文件。

解决方法:1)调整Link的CMD 文件,使得定位段处有RAM。

2)调整存储器设置,使得RAM区有效如何选择外部时钟?DSP的内部指令周期较高,外部晶振的主频不够,因此DSP大多数片内均有PLL。

但每个系列不尽相同。

1)TMS320C2000系列:TMS320C20x:PLL可以÷2,×1,×2和×4,因此外部时钟可以为5MHz-40MHz。

TMS320F240:PLL可以÷2,×1,×1.5,×2,×2.5,×3,×4,×4.5,×5和×9,因此外部时钟可以为2.22MHz-40MHz。

TMS320F241/C242/F243:PLL可以×4,因此外部时钟为5MHz。

TMS320LF24xx:PLL可以由RC调节,因此外部时钟为4MHz-20MHz。

TMS320LF24xxA:PLL可以由RC调节,因此外部时钟为4MHz-20MHz。

2)TMS320C3x系列:TMS320C3x:没有PLL,因此外部主频为工作频率的2倍。

TMS320VC33:PLL可以÷2,×1,×5,因此外部主频可以为12MHz-100MHz。

3)TMS320C5000系列:TMS320VC54xx:PLL可以÷4,÷2,×1-32,因此外部主频可以为0.625MHz-50MHz。

TMS320VC55xx:PLL可以÷4,÷2,×1-32,因此外部主频可以为6.25MHz-300MHz。

TMS320C55xDSP教材习题答案

第一章1.简述典型实时数字信号处理系统组成部分。

答:包括:抗混叠滤波器(Anti-aliasing filter)、模数转换器ADC(Analog-to-Digital Converter)、数字信号处理、数模转换器DAC(Digital-to-Analog Converter)和抗镜像滤波器(Anti-image filter) 。

2.简述X86处理器完成实时数字信号处理的优缺点。

答:利用X86处理器完成实时数字信号处理。

特点是处理器选择范围宽,主板及外设资源丰富,有多种操作系统可供选择,开发、调试较为方便;缺点是数字信号处理能力不强,硬件组成较为复杂,系统体积、重量较大,功耗较高,抗环境影响能力较弱。

3.简述数字信号处理器的主要特点。

答:(1)存储器采用哈佛或者改进的哈佛结构;(2)内部采用了多级流水;(3)具有硬件乘法累加单元;(4)可以实现零开销循环;(5)采用了特殊的寻址方式;(6)高效的特殊指令;(7)具有丰富的片内外设。

4.给出存储器的两种主要结构,并分析其区别。

答:存储器结构分为两大类:冯·诺依曼结构和哈佛结构。

冯·诺依曼结构的特点是只有一个存储器空间、一套地址总线和一套数据总线;指令、数据都存放在这个存储器空间中,统一分配地址,所以处理器必须分时访问程序和数据空间。

哈佛结构程序存储器空间和数据存储器空间分开,具有多套地址、数据总线,哈佛结构是并行体系结构,程序和数据存于不同的存储器空间,每个存储器空间独立编址、独立访问。

5.简述选择数字信号处理器所需要考虑的因素。

答:应考虑运算速度、算法格式和数据宽度、存储器类型、功耗和开发工具。

6.给出数字信号处理器的运算速度指标,并给出其具体含义。

答:常见的运算速度指标有如下几种:(1)指令周期:执行一条指令所需的最短时间,数值等于主频的倒数;指令周期通常以ns(纳秒)为单位。

例如,运行在200MHz的TMS320VC5510的指令周期为5ns。

第5章 TMS320C55x的片内集成外设开发及测试20141029lite

第5章 TMS320C55x的片内集成外设开发及测试

5.2

时钟发生器

5.2.1时钟模式寄存器

C55x片内的时钟发生器可以从CLKIN引脚接收输入的时钟,将其变 换为CPU及其外设所需要的工作时钟,工作时钟经过分频也能够通过引脚 CLKOUT输出,供其他器件使用,如下图5-1所示。

2014年10月31日

TMS320C55x DSP原理及应用

14

第5章 TMS320C55x的片内集成外设开发及测试

5.2.4 使用方法

通过对时钟模式寄存器的操作,可以根据需要设定时 钟发生器的工作模式和输出频率,在设置过程中除了工作 模式、分频值和倍频值以外,还要注意其他因素对PLL的 影响。 1.省电(IDLE) 为了节省功耗,可以使时钟发生器处于省电状态, 当时钟发生器退出省电状态时,PLL自动切换到旁路模 式,进行跟踪锁定,锁定后返回到锁定模式,时钟模式 寄存器中与省电有关的位是IAI。

2014年10月31日 TMS320C55x DSP原理及应用 6

第5章 TMS320C55x的片内集成外设开发及测试 为了方便地实现C55x外设的控制,德州仪器公司为用户 提供了片上外设支持库,片上外设支持库为用户提供了控制片 上外设的函数、宏等工具,用户可以通过程序或DSP/BIOS完 成这些函数和宏的调用。 片上外设支持库具有如下特点: (1)采用标准协议对外设进行编程 片上外设支持库采用标准协议实现片上外设的编程,这 些协议包括数据类型、定义外设配置的宏定义,以及实现各种 外设操作的函数等。 (2)基本资源管理 可以通过程序实现多通道外设的资源管理。 (3)设备的符号描述 片上外设支持库通过对外设寄存器和寄存器域的符号定 义,使程序在不同DSP之间的移植变得容易,而当DSP的版本 发生升级时,可以最大程度地减少程序的修改。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

锁相环初始化程序的理解

1、 ioport关键字用于对I/O空间进行寻址

2、 dsp_lk=12

3、 phase locked的意思是相位同步的意思;锁相技术:对于接收到的信号,仿制一个时钟信

号,使得这两个信号从某种角度来看是同步的(或者说,相干的)。

4、 PLL init()函数的理解

#include "5509.h"

#include "util.h"

DSPCLK dspclk;

void PLL_Init(int freq)

{

int i;

DSPCLK dspclk; //这是一个结构体类型,在#include "util.h"文件中有

DSPCLK的定义

ioport unsigned int *clkmd;

ioport unsigned int *sysr;

clkmd=(unsigned int *)0x1c00; //时钟产生寄存器CLKMD的地址是0x1C00

sysr=(unsigned int *)0x07fd; //这个寄存器用于控制某些特定设备的功能,它的

地址为0x7fd

// Calculate PLL multiplier values (only integral multiples now)

dspclk.clkin = DSP_CLKIN; //dspclk_clkin=12

dspclk.pllmult = (freq *2)/ dspclk.clkin; //pllmult=freq*2/12关于这个问题

//因此freq=pllmult*12/2,此时我们可以对

照发现PLL DIV 默认值为1,而input frequency在util.h文件中给出 值为12,但为什么一

开始PLL DIV=1呢?下面这张图是spru317g的关于Reset Values of CLKMD Bits and The

Effects,我们看到PLL DIV初始值是00,难道是和sysr寄存器中的CLK DIV有关?可sprs205

文档中并未说明CLK DIV究竟复位后值为几。

但看下面的代码可知,PLL DIV是被置1的。刚刚所看的文件是DSP被复位后的初始值,

而PLL DIV=1是此函数PLL_Init(int freq)的设置值,所以PLL DIV被认为是1

if(dspclk.pllmult>= 32)dspclk.pllmult=31;

//如果倍频值超过最大的31,则将其视为31倍频

// Turn the PLL off使PLL处于旁路模式

*clkmd &= ~0x10; //pll enable = 0;旁路模式,就是PLL通过BYPASS DIV对

输入信号进行分频

for(i=*clkmd&1; i!= 0 ;i=*clkmd&1); //查询clkmd的LOCK位,如果为1,PLL

工作于锁定模式,则继续等待,直到LOCK=0,PLL被旁路,

// 初始化锁相环的一些标识位

*clkmd &= ~0x4000; // iai=0;确定锁相环是否重新锁相当时钟发生器退出闲置模

式时,此设置使用上一次的参数设置

*clkmd |= 0x2000; // iob=1;自动切换到旁路模式,重新开始跟踪锁定后,又自动切

换到锁定模式

// 设置乘法器/除法器

// WriteMask(pCMOD -> clkmd,

// CLKMD_PLLDIV_1 | CLKMD_BYPASSDIV_1,

// CLKMD_PLLDIV_MASK | CLKMD_BYPASSDIV_MASK);

*clkmd &= ~0xc; //使得2、3位BYPASS DIV=00,1分频

*clkmd |= 4; //使得2位置1 , BYPASS DIV=01

*clkmd &= ~0x60; //使得5、6位置0

*clkmd |= 0x20; //第5位置1,PLL DIV=01

//WriteField(pCMOD -> clkmd, dspclk.pllmult, CLKMD_PLLMULT_MASK);

*clkmd &= ~0x0f80; //第7~11位置0,PLL MULT=0

*clkmd |= dspclk.pllmult<<7; //因为PLL MULT是7~11位,dspclk.pllmult所以

左移7位

// 打开锁相环

*clkmd|=0x10; //PLL ENABLE=1

for(i=0;i<10;i++); //等待锁定模式,在相位锁定的过程中,时钟发生器仍处于

旁路模式

for(i=*clkmd&1; i!= 1 ;i=*clkmd&1); //查询clkmd的LOCK位,如果为0,

PLL被旁路,则继续等待,直到LOCK=1,PLL处于锁定模式

*sysr=2; // CLKOUT等于CPU时钟除以4

}

PLL锁相环就是将时钟发生器的信号进行分频倍频的处理以供CPU工作,PLL模式与

旁路模式是两种分倍频的工作模式,通过各自的标志位进行相应的分频倍频计算。并且,由

于pll的锁相需要同步,因此是需要一定的等待时间,此时便仍处于BYPASS模式。

另外SYSR寄存器只是对CLKOUT这个引脚的输出信号进行设定,将CPU时钟信号通

过sysr的低三位决定CLKDIV进行分频最终输出,而CPU时钟信号并未改变,因此并不影

响pll的编程