FPGA笔记

最新FPGA状态机学习笔记(verilog)资料

FPGA之有限状态机学习笔记有限状态机(FSM)是由寄存器组合组合逻辑构成的硬件时序电路。

FSM 的状态只可能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态。

Mealy型FSM的下一个状态不仅取决于当前所在状态,还取决于各个输入值。

Moore型FSM的下一个状态只取决于当前状态。

Verilog HDL可以用很多方法描述FSM,最常用的是用always语句和case 语句。

FSM常用模型有Gray和独热码两种,对于用FPGA实现的FSM建议采用独热码。

因为采用独热码可省下许多组合电路的使用,提高电路的速度和可靠性,且总的单元数并无显著增加。

用Verilog语言描述FSM,可以充分发挥硬件描述语言的抽象建模能力。

有限状态机设计的一般步骤:(1)、逻辑抽象,得出状态转换图(2)、状态化简(3)、状态分配(4)、选定触发器的类型并求出状态方程、驱动方程和输出方程(5)、按照方程得出逻辑图以下就是分别用独热码和Gray码实现上述状态的源程序:采用独热码源程序:module fsm(Clock,Reset,A,B,C,D,E,Multi,Contig,Single);input Clock;input Reset;input A,B,C,D,E;output Multi,Contig,Single;reg Multi;reg Contig;reg Single;parameter [6:0]S1=7'b0000001,S2=7'b0000010,S3=7'b0000100,S4=7'b0001000,S5=7'b0010000,S6=7'b0100000,S7=7'b1000000;parameter U_DL Y=1;reg [6:0] curr_st;reg [6:0] next_st;always @(posedge Clock or posedge Reset) beginif(!Reset)curr_st=S1;elsecurr_st= #U_DL Y next_st;endalways @(curr_st or A or B or C or D or E) begincase(curr_st)S1:beginMulti =1'b0;Contig =1'b0;Single =1'b0;if(A&~B&C)next_st =S2;else if(A&B&~C)next_st =S4;elsenext_st =S1;endS2:beginMulti =1'b1;Contig =1'b0;Single =1'b0;if(!D)next_st =S3;elsenext_st =S4;endS3:beginMulti =1'b0;Contig =1'b1;Single =1'b0;if(A|D)next_st =S4;elsenext_st =S3;endS4:beginMulti =1'b1;Contig =1'b1;Single =1'b0;if(A&B&~C)next_st =S5;elsenext_st =S4;endS5:beginMulti =1'b1;Contig =1'b0;Single =1'b0;next_st =S6;endS6:beginMulti =1'b0;Contig =1'b1;Single =1'b1;if(!E)next_st =S7;elsenext_st =S6;endS7:beginMulti =1'b0;Contig =1'b1;Single =1'b0;if(E)next_st =S1;elsenext_st =S7;enddefault:next_st =S1;endcaseendendmoduleModelsim仿真激励文件程序如下:`timescale 1 ns/ 1 psmodule fsm_vlg_tst();// constants// general purpose registersreg eachvec;// test vector input registersreg A;reg B;reg C;reg Clock;reg D;reg E;reg Reset;// wireswire Contig;wire Multi;wire Single;// assign statements (if any)fsm i1 (// port map - connection between master ports and signals/registers .A(A),.B(B),.C(C),.Clock(Clock),.Contig(Contig),.D(D),.E(E),.Multi(Multi),.Reset(Reset),.Single(Single));initialbeginClock=0;forever #10Clock=~Clock;endinitialbeginReset=0;#100Reset=1;endinitialbegin//{A,B,C,D,E}=5'b10101;//# 10// {A,B,C,D,E}=5'b11000;{A,B,C,D,E}=5'b10111;//A=1;//B=0;//C=1;#100//{A,B,C,D,E}=5'b10101;D=0;#50//{A,B,C,D,E}=5'b10111;A=1;D=1;#50//{A,B,C,D,E}=5'b11011;A=1;B=1;C=0;#100//{A,B,C,D,E}=5'b11010;E=0;#50//{A,B,C,D,E}=5'b11011;E=1;endendmodule注:initial块中语句是顺序执行的,因此在需要延时的时候,按相对时间延时。

FPGA设计笔记:QSPI Flash与DDR3L SDRAM采用同一I-O分区

FPGA 设计笔记:QSPI Flash 与DDR3L SDRAM 采用同一I/O 分区众所周知FPGA 的硬件资源被划分为若干个不同的bank,Xilinx 一些高端的FPGA 器件由22 个甚至更多个bank 组成,这样设计主要是为了提高灵活性。

FPGA 的I/O 支持1.8V、2.5V 和3.3V 等多种电平输入输出,为了获得这些I/O电平,就需要在对应bank 的供电引脚输入对应的电源电压,这样就节省了很多总线转换器。

Flash 是一种具有电可擦除的可编程ROM 存储器,掉电内容不会丢失,按接口可以分为两大类:并行Flash 和串行Flash,并行Flash 存储量大,速度快;而串行Flash 存储量相对较小,但体积小,连线简单,可减小电路面积,节约成本。

SPI Flash 是内嵌SPI 总线接口的串行Flash,它比起传统的并行总线接口Flash,节省了很多的I/O 口资源。

SDRAM(Synchronous Dynamic Random Access Memory,同步动态随机存储器)也是FPGA 设计中经常采用的内存器件,掉电后不能保存数据,功耗也比较大。

因此Flash 用于保存FPGA 系统启动所需的配置文件,SDRAM 则用于系统的数据的缓存,所有程序的运行都在内存中进行,速度快。

Xilinx Spartan-7 FPGA 器件适用于那些成本敏感型应用。

它采用小型封装却拥有高比例的I/O 数量,单位功耗性价比相较前代产品提升多达四倍,可提供灵活的连接能力、接口桥接和辅助芯片等功能。

图1:Xilinx 推出的成本敏感型的Spartan-7 系列FPGA 器件最小型的Spartan-7 FPGA 只集成了100 个I/O 管脚,划分为两个bank,如果能够实现将QSPI Flash 和DDR SDRAM 都集成到同一bank 那么就会充分利用有限的I/O 资源。

QSPI Flash 的工作电压是1.8V,而DDR3L SDRAM 的工作电。

FPGA学习笔记(2)

笔记(一)1.关于源代码的组织方式:(1)面积与速度折中(Area&speed tradeoff):是一个相互制约的矛盾关系,一般选择速度优先;(2)硬件可实现(feasibility):软件管理学上的名词,对人和资源、项目的评价是指相同水平的工程技术人员再次实现的难易程度;(3)层次化设计(Hierarchical Design):自上而下(可读性强,易重用);(4)同步设计(Synchronization):同步信号稳定,可以避免冒险竞争,适用于高速设计。

笔记(二)1.有限状态机FSM(Finite State Machine)用于描述各种复杂的时序行为,是使用HDL进行数字逻辑设计的最重要方法之一。

它的基础为有限自动机FA(Finite Automata),由它延伸出的理论模型有:序列机SM(Sequential Machine),线性序列机LSM(Linear Sequential Machine),以及算法机(Algorithmic Sequential Machine)。

实际工程中,FSM,LSM,和ASM,及ASMD(Algorithmic State Machine and Datapath)或单独或组合应用。

因为LSM 和ASM都是从FSM演变过来,所以有时广义地将上述所有状态机统称为FSM。

用于FSM 的规划工具以及状态转移图STG(State Transition Graphs)和算法流程图ASMc(Algorithmic Sequential Machine charts)应用较多,在LSM情况下,也可以用SMF表规划(Sequential Machine Flow)。

2.开节点(Pipling Nodes):只有组合逻辑,没有寄存器;always块内只有组合逻辑。

闭节点(Closed Node):既有组合逻辑又有时序逻辑,有寄存器;always块由沿触发,在最后一级输出时会生成一个寄存器。

FPGA学习笔记23:模块实例化

FPGA学习笔记23:模块实例化

模块定义中是不允许嵌套定义模块的,模块之间的相互调⽤只能通过实例化来实现。

通过多次实例化相同的模块,实际上在电路中设计了4个相同的1位加法器,只是它们在电路中的名字和连接关系各不相同。

对已定义好的模块进⾏实例化引⽤的语法格式如下:模块名实例名 (端⼝连接关系列表); 在实例化时,可以⽤两种⽅式书写端⼝连接关系列表。

第⼀种⽅式是命名端⼝连接⽅式,其语法格式为模块名实例名 (.端⼝名(连接线1), .端⼝名2(连接线2),...);

若需要某个端⼝不连接,则在连接列表中不列出该端⼝即可

但这种在端⼝连接列表中忽略某个端⼝连接关系的写法通常会在仿真⼯具编译时报警,因此,⼀种更好的⽅式是这样书写:fadder_1 u_fadder_1_1 ( .i_B(i_B[0]), .i_Cin(i_Cin), .o_S(), // 端⼝o_S悬空 .o_Cout(Cout_1), .i_A(i_A[0]) ); 即在端⼝连接关系列表中写出o_S端⼝,但是不指定它所连接的信号,⽽是打⼀个空括号。

在实际使⽤Verilog HDL进⾏设计时,应坚持使⽤这样的⽅式来指定不进⾏连接的端⼝。

注意:信号连接类型

模块端⼝和与之连接的信号的数据类型必须遵循如下规定:

1.输⼊端⼝在模块内部必须为wire型数据,在模块外部可以连接wire或reg型数据。

2.输出端⼝在模块内部可以为wire或

reg型数据,在模块外部必须连接到wire型数据。

3.连接的两个端⼝位宽可以不同,但其仿真结果可能因Verilog HDL仿真器⽽异,通常会有警告。

FPGA笔记之verilog语言(基础语法篇)

FPGA笔记之verilog语言(基础语法篇)笔记之verilog语言(基础语法篇)写在前面:verilogHDL语言是面对硬件的语言,换句话说,就是用语言的形式来描述硬件线路。

因此与等软件语言不同,假如想要在实际的中实现,那么在举行verilog语言编写时,就需要提前有个硬件电路的构思和主意,同时,在编写verilog语言时,应当采纳可综合的语句和结构。

1. verilog 的基础结构1.1 verilog设计的基本单元——module在数字电路中,我们经常把一些复杂的电路或者具有特定功能的电路封装起来作为一个模块用法。

以后在运用这种模块化的封装时,我们只需要知道:1.模块的输入是什么;2.模块的输出是什么;3.什么样的输入对应什么样的输出。

而中间输入是经过什么样的电路转化为输出就不是我们在用法时需要特殊重视的问题。

当无数个这样的模块互相组合,就能构成一个系统,解决一些复杂的问题。

verilog语言的基础结构就是基于这种思想。

verilog中最基本的模块是module,就可以看做是一个封装好的模块,我们用verilog来写无数个基本模块,然后再用verilog描述多个模块之间的接线方式等,将多个模块组合得到一个系统。

那么一个module应当具有哪些要素呢?首先对于一个module,我们应当设计好其各个I/O,以及每个I/O的性质,用于与模块外部的信号相联系,让用法者知道如何连线。

第二,作为开发者,我们需要自己设计模块内部的线路来实现所需要的功能。

因此需要对模块内部浮现的变量举行声明,同时通过语句、代码块等实现模块的功能。

综上所述,我们把一个module分成以下五个部分:模块名端口定义I/O解释第1页共9页。

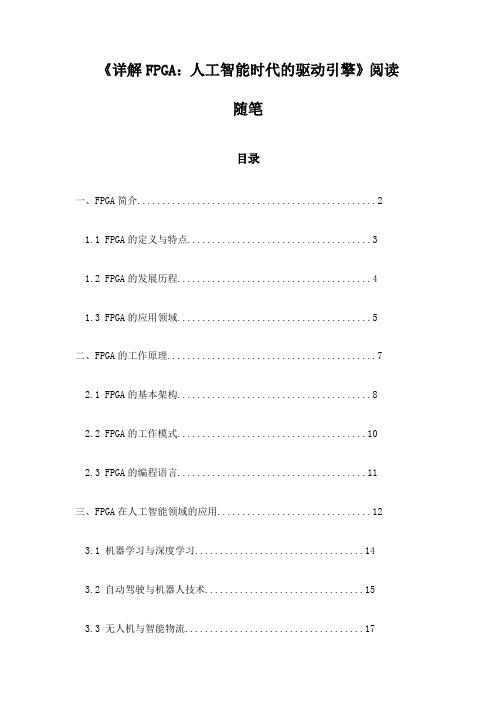

《详解FPGA:人工智能时代的驱动引擎》札记

《详解FPGA:人工智能时代的驱动引擎》阅读随笔目录一、FPGA简介 (2)1.1 FPGA的定义与特点 (3)1.2 FPGA的发展历程 (4)1.3 FPGA的应用领域 (5)二、FPGA的工作原理 (7)2.1 FPGA的基本架构 (8)2.2 FPGA的工作模式 (10)2.3 FPGA的编程语言 (11)三、FPGA在人工智能领域的应用 (12)3.1 机器学习与深度学习 (14)3.2 自动驾驶与机器人技术 (15)3.3 无人机与智能物流 (17)3.4 医疗诊断与生物信息学 (18)3.5 其他领域的FPGA应用 (20)四、FPGA的设计与优化 (22)4.1 FPGA设计流程 (23)4.2 硬件描述语言 (25)4.3 设计优化策略 (26)4.4 性能评估与测试 (28)五、FPGA的未来发展趋势 (29)5.1 技术创新与突破 (30)5.2 行业合作与生态系统建设 (32)5.3 应对挑战与机遇 (33)六、结论 (35)6.1 FPGA在人工智能时代的重要性 (36)6.2 未来展望与期许 (37)一、FPGA简介FPGA(现场可编程门阵列)是一种集成电路芯片,它允许设计师在硬件层面上实现可编程的解决方案。

与传统的专用硬件电路相比,FPGA具有更高的灵活性和可扩展性,因此在人工智能、数据中心、通信等领域得到了广泛应用。

FPGA的核心特点是可编程性。

它可以根据需要动态地重新配置内部逻辑单元,从而实现各种功能。

这种可编程性使得FPGA在应对不断变化的应用需求时具有很高的效率。

FPGA还具备低功耗、高性能、高可靠性等优点。

FPGA的发展历程可以追溯到20世纪80年代,当时Xilinx公司推出了世界上第一款商用FPGA产品。

随着技术的不断发展,FPGA的性能不断提高,功能也越来越丰富。

FPGA已经发展到了第四代,即UltraScale系列,其最大容量可达140亿个逻辑单元,支持多种编程语言和开发工具,为人工智能时代的应用提供了强大的支持。

《数字信号处理的FPGA实现》读书笔记

<数字信号处理的FPGA实现>Verilog写状态机大概有这样几点要求:1、组合逻辑完成状态转移的条件判断,时序逻辑完成状态机的状态转移。

2、组合逻辑和时序逻辑分别在两个不同的always块中完成,根据状态机状态通过译码逻辑产生的与状态机无关的逻辑部分不要放在专用的状态机always块中。

3、状态编码预先定义为parameter,状态较少的状态机推荐使用one-hot方式编码,以减小译码逻辑的复杂度,提高性能。

4、建议单独使用一个模块来描述状态机。

5、状态机应有一个default状态,在上电复位的时候作为初始状态。

6、注意状态机组合逻辑中的if...else语句,不要出现latch。

7、对于复杂状态机,最好采用状态机嵌套方式完成。

其实上面很多都是按照Synopsys LEDA的coding style的要求的,状态机的写法相对固定,因此很多Design entry的工具可以自动生成状态机代码,Xilinx也有工具支持直接由状态转移图输入完成状态机的编码。

所以关键还是画好状态转移图,其他就相对简单了。

visual hdl+ISE+synplify Pro+modelsim!1.设计输入1)设计的行为或结构描述。

2)典型文本输入工具有UltraEdit-32和Editplus.exe.。

3)典型图形化输入工具-Mentor的Renoir。

4)我认为UltraEdit-32最佳。

2.代码调试1)对设计输入的文件做代码调试,语法检查。

2)典型工具为Debussy。

3.前仿真1)功能仿真2)验证逻辑模型(没有使用时间延迟)。

3)典型工具有Mentor公司的ModelSim、Synopsys公司的VCS和VSS、Aldec公司的Active、Cadense公司的NC。

4)我认为做功能仿真Synopsys公司的VCS和VSS速度最快,并且调试器最好用,Mentor 公司的ModelSim对于读写文件速度最快,波形窗口比较好用。

FPGA串口UART学习笔记1串口通信

FPGA串⼝UART学习笔记1串⼝通信串⼝通信1、串⼝简介串⾏接⼝,COM接⼝,只需要两根线就能实现两台设备之间的通信。

UART指的是异步的串⾏接⼝,通⽤异步收发。

标准常⽤的是RS-232标准接⼝现在电脑上没有串⼝了,所以使⽤的是USB转串⼝芯⽚,CH340芯⽚。

换句话说,只需要两根数据线UART_RXD和UART_TXD,就能完成两台设备之间的通信。

2、串⼝时序两根数据线各⾃独⽴互不影响,⼆者的时序是相同的。

不同之处是UART_RXD是主机MASTER发送给从机SLAVE,UART_TXD是SLAVE 发送给MASTER。

由于两根线的时序完全相同且独⽴,下⾯以UART_TXD为例。

空闲状态时,UART_TXD⼀直拉⾼,当要传输数据之前,拉低⼀个数据位,此后开始传输数据。

数据之后有⼀个校验位,校验位之后是停⽌位,停⽌位之后进⼊下⼀个传输周期。

⾄此,完成了⼀个数据包的传输。

注意:(1)、传输的数据是从低⽐特位开始传,⽐如101010,接受端的接受顺序是010101。

(2)、传输数据的位数是MASTER与SLAVE约定好的,可以是4、5、6、7、8位,时序图中是以⼋位为例。

(3)、校验位⼀般是奇偶检验。

当然,也可以选择没有检验位,前提是MASTER与SLAVE约定好,在SLAVE解析接收到的数据的时候,不安排校验位的解析。

(4)、停⽌位,停⽌位是保证两段传输之间⼀定要有间隔。

两段传输之间可以没有空闲时间,但是,停⽌位⼀定要有。

3、时间的问题从时序图上可以看出,串⼝的发送和接受是没有时钟的,换句话说,这是⼀个异步时序。

那么如何确定每个位所需要的时间就尤为重要。

这个问题的要点是波特率,每秒发送/接受单位的个数。

我们使⽤的串⼝是以⽐特为单位,所以这⾥波特率与我们的⽐特率相同。

常见的波特率的数值有9600,19200,38400,57600,115200等。

以9600为例,表⽰⼀秒钟发送/接受9600个⽐特。