第8章_VHDL结构与要素

vhdl程序的基本结构vhdl程序一般由5个部分组成

块语句

块标号:BLOCK[保护表达式] [类属子句;] [端口子句;] [块说明部分;] BEGIN

<块语句部分;>

; END BLOCK 块标号

类属子句用于参数的定义;端口子句用于信号的定义; 块说明部分对该块要用到的信号、常数、元件和子程序 等进行说明;块语句部分对该块的功能进行描述,块语 句部分的语句是并行执行的,和书写顺序无关。

缺省说明: library std; use std.standard.all;

常用库及其程序包

IEEE: IEEE认可的标准库 std_logic_1164:定义了 std_logic, std_logic_vector, std_ulogic, std_ulogic_vector 等数据类型

VHDL 程序的基本结构

设计实体

实体说明

构造体

设计实体的组成

实体说明

Entity <实体名> is

[类属说明;] [端口说明;]

[实体说明部分;] [实体语句部分;] End [entity]<实体名>;

最简单的例: entity nothing is end nothing;

实体说明--类属说明

类属为设计实体和外部环境通讯的静态通信提供通道。可以定

实体说明--实体语句部分

是设计实体接口的共同部分。只能由并行断 言语句、并行过程调用语句、被动进程语 句组成,且不能在语句中给信号赋值。

设计实体

实体说明

构造体

设计实体的组成

构造体

architecture <构造体名> of <实体名> is

[构造体说明语句;]

Begin

<功能描述语句;>

VHDL语言的基本要素(大全)

VHDL语言的基本要素一、数据对象VHDL语言的主要数据对象有信号,变量,常量。

信号—信号是电路中的物理量,对应于电路的连线、节点;信号说明全局量,用于描述中的构造体(Architecture), 实体(Intity),程序包(package)。

变量—变量是程序运算中的中间量,并不对应电路中的物理量。

变量说明局部量,用于进程语句(process), 函数(Function), 过程(procedure)。

常量—常数也不对应电路中的物理量,当常量说明全局量,在构造体(Architecture), 实体(Intity),程序包(package),进程语句(process), 函数(Function), 过程(procedure)中均可使用。

数据对象的定义格式:signal 信号名:数据类型,约束条件,表达式Variable 变量名:数据类型,约束条件:=表达式Constant 常量名:数据类型,约束条件:=表达式例如:Variable count:INTEGER RANGE 0 TO 255:=10Constant Daly:Time:=100ns信号代入和变量赋值的区别:两者形式不同,操作过程也不相同。

变量赋值符“:=”,信号的代入符“<=”。

在变量的赋值语句中,该语句一当执行,其值立即将赋予变量;而信号的代入,其语句执行后不会立即使信号发生代入,在下条语句执行时,仍使用原来的信号值,如进程语句中的敏感表的信号代入就是如此。

二、数据类型VHDL语言中的数据类型,一般而言可分为:标量类型和组合类型。

在实际使用中,也可分成予定义类型和用户定义类型。

VHDL语言是强类型的语言,主要可按如下分类和变换处理。

①标准数据类型⑴整数⑵实数(浮点数)-1.0E+38~+1.0E38 ⑶位bit(0,1)⑷位矢量⑸布尔量,“假”,“真”⑹字符(ASCⅡ)字符⑺时间⑻错误等级⑼自然数(大于等于0的整数)⑽字符串(字符矢量)②用户定义的数据类型TYPE 数据类型名{数据类型名} 数据类型定义⑴枚举类型⑵整数类型⑶实数类型⑷数组类型⑸存取类型⑹文件类型⑺记录类型⑻时间类型③用户定义子类型SUBTUPE 子类型名IS 数据类型名[范围]例:SUBTYPE digit is INTEGER RANGE 0 TO 9④数据类型转换数据类型的变换函数通常由“STD_LOGIC_1164”,“STD_LOGIC_ARITH”,“STD_LOGIC_UNSIGNED”的程序包提供例如,在STD_LOGIC_1164程序包中,TO_STD LOGIC VECTOR(A) 由BIT_VECTOR转换为STD_LOGIC_VECTORTO_BITVECTOR(A) 由STO_LOGIC_VECTOR转为BIT_VECTORTO_STDLOGIC(A) 由BIT转换为STD_LOGICTO_BIT(A) 由STD_LOGIC转换成BIT signal a: BIT_VECTOR(11 DOWNTO 0)signal b: STD_LOGIC_VECTOR(11 DOWNTO 0)a<=X”A8” 十六进制值可赋予位矢量b<=X”A8” 语法错,十六进制不能赋予.STD 矢量b<=TO_STDLOGICVECTOR(X“AF7”)b<=TO_STDLOGICVECTOR(O“5177”)八进制变换b<=TO_STDLOGICVECTCR(B“1010_1111_0111”)下表中也给出一些典型的类型变换函数三、运算符运算符的优先级如下表所示:运算符的优先级例如,并置运算符的使用:tmp_b<=b AND (en&en&en&en) y <= a & tmp_b第一个语句表示b 的4位位矢量由en 进行选择 得到一个4位位矢量输出第二个语句表示4位位矢量a 和4位位矢量b 再 次连接(并置)构成8位的位矢量y 输出 右图所示为并置运算符操作的电路示意。

《VHDL程序基本结构》课件

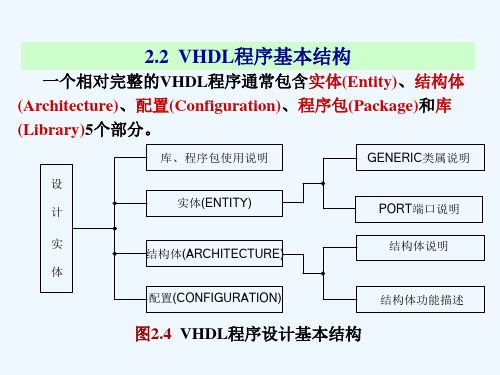

VHDL程序基本结构示意图

VHDL程序基本结构

这是一张示意图,展示了VHDL程序的基本结构和各个部分之间的关系。

VHDL程序编写实例

这里将展示一个简单的VHDL程序编写实例,以帮助理解VHDL程序的应用和编 写方法。

总结

通过本课程,我们了解了VHDL程序的基本结构和编写方法,以及各个部分的功能和关系。希望这些知识对你 的学习和工作有所帮助。

VHDL程序的基本组成

VHDL程序由实体说明部分、 架构说明部分、信号声明与 处理部分和过程描述部分组 成。

VHDL程序的编写流程

编写VHDL程序的流程包括定 义实体、编写架构、声明信 号和编写过程。

实体说明部分

ห้องสมุดไป่ตู้

1 实体声明

实体声明定义了模块的输入输出接口,包括 输入输出端口和内部信号。

2 输入端口声明

输入端口声明用于定义模块的输入信号和其 属性,如信号类型和位宽。

3 输出端口声明

输出端口声明用于定义模块的输出信号和其 属性,如信号类型和位宽。

4 端口映射

端口映射将模块的输入输出端口与上层设计 连接起来,以实现功能。

架构说明部分

1

架构声明

架构声明定义了模块的行为逻辑和组成元素,包括信号和过程。

2

参考文献

1. VHDL程序设计教程 2. VHDL语言基础与应用 3. VHDL编程入门

信号赋值语句

信号赋值语句用于给信号赋予特 定的值,以实现逻辑功能。

信号处理语句

信号处理语句用于处理信号的逻 辑运算和状态转换,以实现电路 功能。

过程描述部分

过程声明

过程声明用于定义过程的名称 和输入输出参数。

过程体

VHDL语言的基本结构

4

一、VHDL语言设计的基本单元及其构成

3)端口说明 PORT(端口名{,端口名}:方向 数据类型; 是对设计实体与外部接口 的描述,即对元件引脚、 ┇ 数据类型和I/O方向的描述 端口名{,端口名}:方向 数据类型); 1端口名

设计实体

进程 或其它并行结构 结构体 n (ARCHITECTURE 进程 或其它并行结构

配置(CONFIGURATION)

VHDL程序设计实体的一般结构

2

VHDL语言的基本结构

主要内容

一、 VHDL语言设计的基本单元及其构成 二、 VHDL语言构造体的子结构描述 三、 包集合、库及配置

3

一、VHDL语言设计的基本单元及其构成

VHDL语言

15

二、VHDL语言构造体的子结构描述

【例】4位二进制加法计数器构造体逻辑描述。

SIGNAL cnt4:INTEGER RANGE O TO 15; ... PROCESS(clk,clear,Stop) BEGIN IF clear='0' THEN cnt4<=0; ELSIF clk'EVENT AND clk='1' THEN IF stop='0' THEN cnt4<=cnt4+1; END IF; END IF; END PROCESS; --注意cnt4的数据类型

存盘文件 为 bpac.vhd

第8章 VHDL结构

图8-1

例8-1的逻辑电路图 的逻辑电路图

【例8-2】结构体中定义函数的应用实例 】 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL ; ENTITY func IS PORT ( a : IN STD_LOGIC_VECTOR (0 to 2 ) ; m : OUT STD_LOGIC_VECTOR (0 to 2 ) ); END ENTITY func ; ARCHITECTURE demo OF func IS FUNCTION sam(x ,y ,z : STD_LOGIC) RETURN STD_LOGIC IS BEGIN RETURN ( x AND y ) OR z ; 结构体中定义函数不必定义函数首! 结构体中定义函数不必定义函数首! END FUNCTION sam ; BEGIN PROCESS ( a ) BEGIN m(0) <= sam( a(0), a(1), a(2) ) ; --顺序函数调用语句 顺序函数调用语句 m(1) <= sam( a(2), a(0), a(1) ) ; m(2) <= sam( a(1), a(2), a(0) ) ; END PROCESS ; END ARCHITECTURE demo ;

接上页

LIBRARY IEEE; -- 函数应用实例 USE IEEE.STD_LOGIC_1164.ALL; USE WORK.packexp.ALL ; --调用前面定义的程序包 调用前面定义的程序包 ENTITY axamp IS PORT(dat1,dat2 : IN STD_LOGIC_VECTOR(3 DOWNTO 0); dat3,dat4 : IN STD_LOGIC_VECTOR(3 DOWNTO 0); out1,out2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END; ARCHITECTURE bhv OF axamp IS BEGIN out1 <= max(dat1,dat2); --用在赋值语句中的并行函数调用语句 用在赋值语句中的并行函数调用语句 用在赋值语句中的 PROCESS(dat3,dat4) BEGIN out2 <= max(dat3,dat4); --顺序函数调用语句 顺序函数调用语句 END PROCESS; END;

第八章VHDL结构与要素

FUNCTION max (a,b : IN STD-LOGIC-VECTOR )函数首 RETURN STD-LOGIC-VECTOR ; FUNCTION max (a,b : IN BIT-VECTOR ) RETURN BIT-VECTOR; FUNCTION max (a,b : IN INTEGER ) RETURN INTEGER; END; 函数首 函数首

(3) 例 ENTITY MCU1 IS GENERIC(addrwidth:INTEGER:=16); PORT(add_bus:OUT STD_LOGIC_VECTOR( addrwidth-1 DOWNTO 0); …

(4) 特点 A、 与常数不同,类属的值可以由设计体 外部提供,常数只能从实体内部得到 赋值 B、 在一个实体中定义的、来自外部赋入 类属的值可以在实体内部或与之相应 的结构体中读到 C、 数据类型通常取INTEGER或TIME等类 型,但是VHDL综合器只支持数据类型 为整数的类属值

8-3 子程序

顺序语句定义和完成算法的程序模块; 定义和完成算法的程序模块 用顺序语句定义和完成算法的程序模块; 可以在三个不同的位置定义:程序包、结构体、进程; 可以在三个不同的位置定义:程序包、结构体、进程; 具有可重载性,每一次调用将在综合后的硬件中产生相应的模块; 具有可重载性,每一次调用将在综合后的硬件中产生相应的模块; 可重载性 有过程和函数两种类型 8-3-1 函数 自定义函数 预定义函数 函数的表达格式——由函数首和函数体组成 由函数首和函数体组成 函数的表达格式 FUNCTION 函数名 (参数表) RETURN 数据类型 参数表) 函数首 函数体

程序包(体) 定义函数体

结束FUNCTION语句 结束PACKAGE BODY语句

VHDL程序基本结构

1) BLOCK块语句

使用BLOCK语句描述的格式如下: [块标号:]BLOCK BEGIN END BLOCK [块标号];

【例2.6】 用块语句实现的二选一电路

结构体不能单独存在,它必须有一个界面说明,即一个 实体。

对于具有多个结构体的实体,必须用CONFIGURATION 配置语句指明用于综合的结构体和用于仿真的结构体,即 在综合后的可映射于硬件电路的设计实体中,一个实体只 对应一个结构体。

在电路中,如果实体代表一个器件符号,则结构体描述 了这个符号的内部行为。

类属说明的一般书写格式如下: GENERIC([常数名;数据类型[:设定值] {;常数名:数据类型[:设定值 ]});

【例2.2】2输入与门的实体描述

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY AND2 IS

GENERIC(RISEW:TIME:=1 ns; FALLW:TIME:=1 ns);

【例2.9】 PROCEDURE语句应用

PROCEDURE vector_to_int (q:IN INTEGER; x_flag :OUT BOOLEAN; z:IN STD_LOGIC_VECTOR) IS

BEGIN q:=0; x_flag:=FALSE;

FOR i IN z’RANGE LOOP q:=q*2;

PROCEDURE 过程名(参数1,参数2) IS [定义语句]; BEGIN [顺序处理语句];

END 过程名;

●函数语句 FUNCTION 函数名(参数1,参数2)RETURN数据类型名 IS

VHDL语言的结构

BEGIN

[功能描述语句]

END 结构体名;

2.1 结构体名 结构体名由设计者自行定义,OF后面的 实体名指明了该结构体所对应的是哪个实体。 有些设计实体有多个结构体,这些结构体的 结构体名不可相同,通常用dataflow(数据 流)、behavior(行为)、structural(结构)

命名。这3个名称体现了3种不同结构体的描

实体语句结构如下:

ENTITY 实体名 IS [GENERIC(类属表);] [PORT(端口表);]

END ENTITY 实体名;

例: ENTITY or2 IS

PORT(a,b:IN STD_LOGIC;

C: OUT STD_LOGIC);

END ENTITY or2;

注意:实体应以语句“ENTITY 实体名 IS”开始,语句“END ENTITY 实体名;” 结束。 在层次化系统设计中,实体说明是整个 模块或整个系统的输入输出(I/O)接口; 在一个器件级的设计中,实体说明是一个 芯片的输入输出(I/O)。

图中5种功能描述语句的基本组成和功能分别 是:

块语句是由一系列并行语句构成的组合体, 它的功能是将结构体中的并行语句组成一个 或多个子模块。

进程语句定义顺序语句模块,用以将从外部 获得的信号值或内部运算数据向其他的信号 进行赋值。

信号赋值语句将设计实体内的处理结果向定 义的信号或界面端口进行赋值。 子程序调用语句可以调用进程或参数,并将 获得的结果赋值于信号。 元件例化语句对其他的设计实体做元件调用 说明,并将此元件的端口与其他元件、信号 或高层实体的界面端口进行连接。 各语句后面将介绍

PROCESS语句的结构

[进程标号] PROCESS [(敏感信号表)] [IS] [进程说明语句] BEGIN 顺序描述语句

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3-17 PACKAGE packexp IS --定义程序包 FUNCTOIN max( a, b IN STD_LOGIC_VECTOR)--定义函数首 RETURN STD_LOGIC_VECTOR; FUNCTION func1(a, b, c : REAL ) --定义函数首 RETURN REAL ;

KX

康芯科技

函数应用实例: ……… USE WOKE.PACKEXP.ALL ; PORT (…) ; END ; ARCHITECTURE bhv OF axamp IS BEGIN ……. out1 <= max( dat1, dat2 ) ; --并行函数调用语句 PROCESS (dat3 , dat4 ) BEGIN out2 <= max(dat3, dat4) ; --顺序函数调用语句 END PROCESS ; ………. END ;

子程序是一个非重入的程序,即子程序返回后才能再被 调用。在调用时子程序首先要进行初始化,执行结束后子程 序终止;再调用时要再进行初始化。因此,子程序内部的值 不能保持。 VHDL的子程序具有可重载性,即允许有许多重名的子程 序,但这些子程序的参数类型和返回数值类型是不同的。

3.5.1 函数(FUNCTION)

1. 结构体的一般语言格式

KX

康芯科技

8.2 结构体

2. 结构体说明语句

进程语句

信号赋值语句

3. 功能描述语句结构

子程序调用语句

元件例化语句

KX

康芯科技

8.3 子程序( SUBPROGRAM )

过程(PROCEDURE)

VHDL的子程序有两种类型:

子程序的特点:

函数(FUNCTION)

子程序可以在结构体或程序包和进程的任何位置被调用, 而且可以反复调用。

KX

康芯科技

8.2 结构体

结构体的组成部分是: • 对数据类型、常数、信号、子程序和元件等元素的说明 部分。 • 描述实体逻辑行为的、以各种不同的描述风格表达的功 能描述语句。 • 以元件例化语句为特征的外部元件(设计实体)端口间 的连接。

ARCHITECTURE 结构体名 OF 实体名 IS [说明语句] BEGIN [功能描述语句] END ARCHITECTURE 结构体名;

KX

康芯科技

ARCHITECTURE rtl OF dpeak IS SIGNAL peak : STD_LOGIC_VECTOR(5 downto 0); BEGIN dout<=peak; PROCESS (clk) BEGIN IF (clk'event and clk='1') THEN IF (set='1') THEN peak<=date; ELSE peak<=max(date,peak); END IF; END IF; END PROCESS; END rtl;

函数调用返回一个指定数据类型的值。

ห้องสมุดไป่ตู้X

例11 在结构体中调用求最大值的函数。

康芯科技

LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE ieee.newlib.ALL; ENTITY dpeak IS PORT(clk, set : IN STD_LOGIC; date : IN STD_LOGIC_VECTOR(5 downto 0); dout : OUT STD_LOGIC_VECTOR(5 downto 0)); END dpeak;

函数语句的调用格式: 函数名 (实际参数表);

函数名(实际参数表);

KX

例11 用FUNCTION语句描述求取最大值的函数。

康芯科技

FUNCTION max(a:std_logic_vector;b:std_logic_vector) RETURN std_logic_vector IS VARIABLE tmp:std_logic_vector(a'range); BEGIN IF (a>b) THEN tmp:=a; ELSE tmp:=b; END IF; RETURN tmp; END max; 函数的参数均为输入参数。

函数语句的结构:

FUNCTION 函数名 (参数表) RETURN 数据类型 [说明部分] BEGIN 顺序语句; END FUNCTION 函数名; FUNCTION 函数名(输入参数表)RETUEN

KX

康芯科技

--函数首

FUNCTION 函数名 (参数表) RETURN 数据类型 IS --函数体

【例8-3】

KX

康芯科技

LIBRARY IEEE; --待例化元件 USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_arith.ALL; USE IEEE.STD_LOGIC_unsigned.ALL; ENTITY addern IS PORT (a, b: IN STD_LOGIC_VECTOR; result: out STD_LOGIC_VECTOR); END addern; ARCHITECTURE behave OF addern IS BEGIN result <= a + b; END; LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_arith.ALL; USE IEEE.STD_LOGIC_unsigned.ALL; ENTITY adders IS GENERIC(msb_operand: INTEGER := 15; msb_sum: INTEGER :=15); PORT(b: IN STD_LOGIC_VECTOR (msb_operand DOWNTO 0); result: OUT STD_LOGIC_VECTOR (msb_sum DOWNTO 0)); END adders; 接下页

康芯科技 ARCHITECTURE behave OF adders IS KX COMPONENT addern 接上页 PORT ( a, b: IN STD_LOGIC_VECTOR; result: OUT STD_LOGIC_VECTOR); END COMPONENT; SIGNAL a: STD_LOGIC_VECTOR (msb_sum /2 DOWNTO 0); SIGNAL twoa: STD_LOGIC_VECTOR (msb_operand DOWNTO 0); BEGIN twoa <= a & a; U1: addern PORT MAP (a => twoa, b => b, result => result); U2: addern PORT MAP (a=>b(msb_operand downto msb_operand/2 +1), b=>b(msb_operand/2 downto 0), result => a); END behave;

KX

8.1.3 类属映射语句

康芯科技

类属映射语句可用于设计从外部端口改变元件内部 参数或结构规模的元件,或称类属元件,这些元件在 例化中特别方便,在改变电路结构或元件升级方面显 得尤为便捷。其语句格式是: GENERIC MAP(类属表)。

类属映射语句与端口映射语句PORT MAP()具有相似的功能和 使用方法,它描述相应元件类属参数间的衔接和传送方式,它 的类属参数衔接(连接)表达方式也相同。

KX

康芯科技

KX

【例8-2】

康芯科技

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY exn IS PORT(d1,d2,d3,d4,d5,d6,d7 : IN STD_LOGIC; q1,q2 : OUT STD_LOGIC); END; ARCHITECTURE exn_behav OF exn IS COMPONENT andn --元件调用声明 GENERIC ( n : INTEGER); PORT(a: IN STD_LOGIC_VECTOR(n-1 DOWNTO 0); c: OUT STD_LOGIC); END COMPONENT ; BEGIN -- 类属映射语句,定义类属变量,n赋值为2 u1: andn GENERIC MAP (n =>2) PORT MAP (a(0)=>d1,a(1)=>d2,c=>q1); u2: andn GENERIC MAP (n =>5) -- 定义类属变量,n赋值为5 PORT MAP (a(0)=>d3,a(1)=>d4,a(2)=>d5, a(3)=>d6,a(4)=>d7, c=>q2); END;

【例8-1】

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY andn IS GENERIC ( n : INTEGER ); --定义类属参量及其数据类型 PORT(a : IN STD_LOGIC_VECTOR(n-1 DOWNTO 0);--用类属参量 限制矢量长度 c : OUT STD_LOGIC); END; ARCHITECTURE behav OF andn IS BEGIN PROCESS (a) VARIABLE int : STD_LOGIC; BEGIN int := '1'; FOR I IN a'LENGTH - 1 DOWNTO 0 LOOP IF a(i)='0' THEN int := '0'; END IF; END LOOP; c <=int ; END PROCESS; END;