嵌入式高速数据采集处理模块的设计实现

基于Web和LPC2210的嵌入式数据采集系统的设计

作 者 简介 :陈 爱 平 ( 9 0)女 , 北 咸 宁人 , 1 8一 , 湖 助教 . 士 研 究 生 , 要 研究 方 向 : 械 电 子 工程 、 学 控 制 。 硕 主 机 数

维普资讯

・8・

机 械 工 程 与 自 动 化

LPC2 1 -Ad r NULL) 2 0 i p,

}武 科 大 机 械传 动 与 制 造 工 程 省重 点 实 验 室 开 发 基 金项 目 ( O3 2 2O AO ) 收 稿 日期 :2 0 —92 0 70 —6

和维 护系统 的各 种硬 件资源 。在 具体 设计 中 ,对微 控 制器 L C 2 0中 内置 A/ P 21 D转 换器 的操 作 、键 盘 的操 作 以及 L D 的操 作 由在 u l u C C i x下编 写 的设 备驱 动 n 程序 完成 ,这些 驱动 被编译 进 u l u C i x的 内核 。 n

基 于 We b和 L C2 P 1 2 O的嵌 入 式数 据采 集 系统 的设 计

陈 爱 平 刘 启 林 。 ,

305 . (. 武 汉 工 业 学 院 工 商 学院 机 械 工 程 系 ,湖 北 武 汉 4 0 6 ;2 武 汉 邮 电科 学研 究院 中光 通 信 公 司 ,湖 1

维普资讯 http://w 总 4

20 0 8年 2月

机 械 工 程 与 自 动 化 M ECHANI AL ENGI C NEERI NG & AU T0M AT1 0N

No .1

Fe b.

文章 编 号 : 6 2 6 1 ( 0 8 O — 0 70 1 7 — 4 3 2 O ) 10 0 — 2

20 0 8年 第 1 期

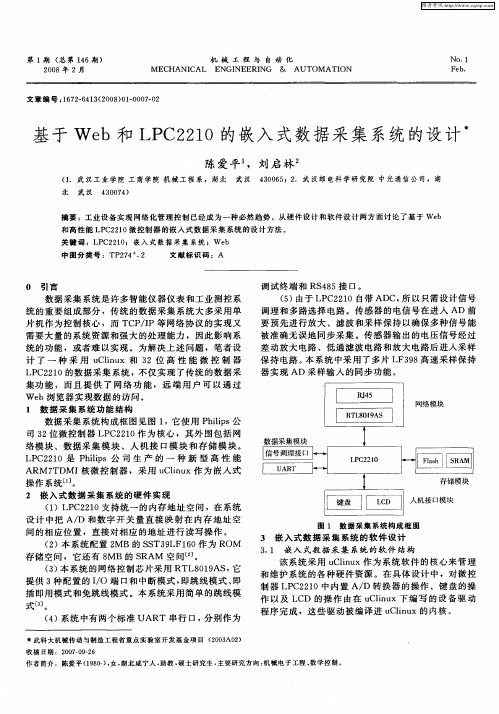

系统 任务 由两 个不 同的进 程实现 :本地 数据 采集 进 程和 网络服务 进 程 。本 地数据 采集进 程 又分 为数据 采 集模块 、数 据处理 模块 、L D模 块 、数据 保存模 块 C 和 键 盘模 块 。网 络 服 务进 程 由 嵌 入 式 We sr e b evr和 C 程序 两部 分构 成 。 GI

基于FPGA的数据采集系统设计与实现

了异步传输 中跨时钟域造成的亚稳态问题 [ 5 1 。在本 数据采集系统的设计中采用异步 FF IO的方式来解

图 2 数 据 采 集 系统 数 据 流 程

决跨时钟域 的数据传输 问题 。因为本数据采集系统 是针对 A C芯片的测试所用的, D 因此数据采集接 口 的数据率不是 固定 的 10 H x4i 而 D R 控制 5M z5b , D 2 t 器的用户接 口和 G E控制器接 口数据率是 固定的 , 分别为 10 H x 1b 和 15 z 2i 5 M zl2i t 2MH x b ,所 以选用 3 t 异步 FF IO可以使 系统更加灵活。

基于 F GA的数据采集系统设计与实现 P

张 泽 军 , 平 分 林

( 北京工业 大学 嵌入式 系统重点 实验 室, 北京, 1 4 102 ) 0

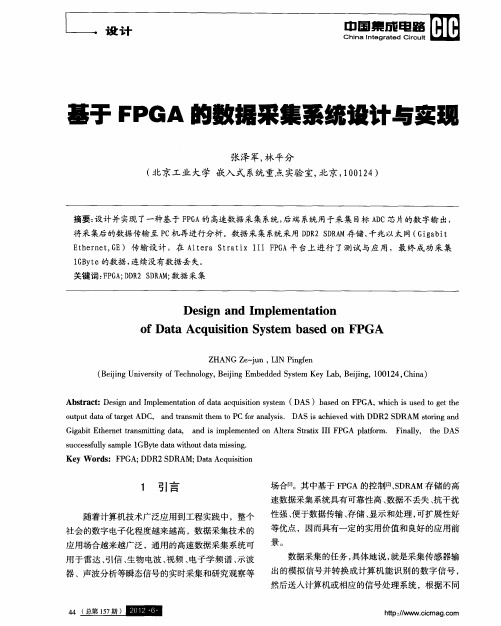

摘要 : 设计 并 实现 了一种基 于 FG P A的 高速 数据 采 集 系统 , 端 系统 用于采 集 目标 A C芯 片 的数 字输 出, 后 D 将 采集后 的数据传 输 至 P C机再 进行 分析 。数据 采 集 系统 采用 DR D A 储 、 兆 以太 网 ( ia i D 2SRM存 千 G gb t

数据传输及控制。同时 , 模块还负责 G I F E控制器、

图 1数 据 采 集 系统 框 图

D R D 2控制 器 的用户 总线及 外 部数 据采 集 接 口之间

h¨ n . h n nA 、 ,m a , , n / s A i, ;、 1 、

L一设 — 计

巾国集成电路

Chi na nt I eg r ed icu i at C r t

块 ,其 功 能 相 当 于 一 个 D MA ( i c M m r Dr t e oy e

基于嵌入式控制器的数据采集服务器的实现

展 , 用 这 一 接 口后 . 要 再 留 同 样 一 个 接 口 . 使 还 以免 影 响 其 他 系 统 对 这 一 接 口的 使 用 [ 1 】 由于 中心 控 制 屏 的 生 产 厂 家 的 不 同 . 以 格 式 的 数 据 给 下

期

v

MDR C T l O OE O U R懈_ N M E2 0 P

\

、

竺

定 的 扩 展 串 口能 力 I 4 1

个 数 据 段 写 满 10 0 0条 数 据 .程 序 就 使 用 另 一 个 数 据

收 稿 日期 :0 8 0 — 9 修 稿 日期 :0 8 0 — 0 20 — 4 0 2 0 — 4 1

总

第

九

三

实 现 这 个 功 能 , 位 机 必 须 具 有 数 据 保 存 功 能 。 当一 二 下

作 者 简介 : 立 坤 (9 1 。 , 苏 南 京 人 , 究 方 向 为 嵌 入 式 系 统 、 戴 17 一) 男 江 研 网络 技 术 、 算 机 技 术 应 用 计

到了一个很 高的集 成度 . 且系统 的投 资也得到 了有 并

效 的控 制

C M2 C M3 如果 有两个 屏 ) 中心屏 通信 . O 、O ( 和 每个 中

心 屏 连 接 1 2个 消 弧 线 圈 装 置 。 目 前 ,供 电 公 司 — 1O V 变 电 站 一 般 安 装 有 2 3台 消 弧 线 圈装 置 . 位 lk ~ 下 机 以 C M2口连 接 主 从 方 式 连 接 的 中 心 屏 . C M3 O 用 O 口连 接 直 接 连 接 消 弧 线 圈 的 中心 屏 如 果 没 有 第 三 台 消 弧 线 圈 .O C M3 口悬 空

嵌入式高速实时数据采集系统设备驱动程序的研究

CN4 — 2 8 TP 315 /

I S 1 0 — O S N 0 7 1 X 3

计算 机 工程与 科学

C OMPUTER ENGI NEE NG & S ENCE RI CI

20 0 6年第 2 8卷第 1 期 O

Vo . 8. . 0. 0 6 1 2 No 1 2 0

中 图分 类 号 : 2 4 TP 7

文献 标 识 码 : A

即将 高速数 字信号处 理芯 片 A P2 9 DS -1 1和三 星公 司高性

1 引 言

为适应在仪器故障诊 断和工业设备监控中进 行高速实 时数据采集和系统测试 的需 要 , 我们将 数字信 号处理芯 片 与嵌入式 中央处理器相结合的设计思想应用于高速实时数 据采集测试系统的设计过 程 中, 即将高 速实时 数据采集 测

文 章 编 号 :0 71 o 2 o ) 00 3 —4 10 —3x( o 6 1-1 10

嵌 入 式 高 速 实 时 数据 采 集 系统 设 备 驱 动 程 序 的研究

Re e r h o he De ie Drv r o s a c n t v c i e sf r Em b d e e dd H i h— e d Re lTi e Da a Ac uiii n Sy t m s g — Sp e a— m t q sto s e —

陆永忠 。 刘 峰

LU ngz n LI Fe g Yo -ho g。 U n

( 华中科技 大学软件 学院 。 湖北 武汉 4 0 7 ) 3 0 4

(c ol f ot aeHuzo gU i ri f i c n eh ooyW u a 3 0 4 C ia Sh o o f r 。 a hn nv s yo e ea dT c n l 。 h n4 0 7 , hn ) S w e t S n c g

嵌入式并行采集系统的优化设计

2 .北京 科技 大学 计 算机科 学与技 术 系,北 京 10 8 ) 003

摘 要 : 了及 时准确 地监 测 工 业设备 和 5 业环 境 中 的重要 参数 指 标 , 出了一种 基 于 F G 为 - 提 P A的嵌 入 式 高速 并行 数据 采 集 系统 的优 化设 计 方案 。对 _ 作原 理 进行 了分析 并提 出了总体 方案 , 此基础 上 , T - 在 着重 实现数 据采 集 系统的软 硬件 紧密结合 ,

关 键 词 : 场 可 编 程 门 阵 列 ; 监 测 系统 ; 嵌 入 式 系 统 ; 并 行 采 样 ; 高速 数 据 采 集 现

中图法 分类号 : P 3 T 35

文献标 识码 : A

文章编 号 :0 07 2 2 1) 512 —4 10 —04(0 1 0—620

Op i z d d sg f mb d e a all aaa q ii o y t m t mie e in o e e d dp r l t c u st n s se ed i

12 2 1, o. , o 计 算 机 工 程 与 设 计 C m u r n i en d ei 62 0 1 V 1 2 N . 3 5 o pt g er g n s n eE n i a D g

嵌入式并行采集系统的优化设计

王 浩森 王 沁 张 晓彤 郭 嵩 , , ,

W A osn, WA ቤተ መጻሕፍቲ ባይዱ, Z NG a — n GUO S n NGHa —e NG Qi HA Xiot g, o o g

(.Ifr t nT c n lg ne,A C S e y n r e gn sac n tue S e y n 1 0 5 1 no mai e h oo yCe tr VI h n a gAeo n ieRee rhIs tt, h n a g 10 1 ,Chn ; o i ia

基于嵌入式的多通道高速数据采集系统徐航

摘要:给出了一种多通道高速数据采集系统的设计方法,与传统的采用ISA 总线的采集卡相比,具有速度快、精度高和实时性好的特点。

本设计采用了比较常用的FPGA、高速AD9051、高速FIFO 等实现了高速采集系统,用DMA 控制技术将采集到的数据直接存储到高速FIFO 中,再由单片机将数据读出,并通过USB 端口传到上位机中,最后用LabVIEW 软件开发的界面进行数据的显示和分析。

实验表明该采集系统有通信速度快,可靠,增益可调,可连续采样等特点,更加适合应用于测试系统。

关键词:高速数据采集系统;FPGA;高速FIFO;LabVIEWAbstractAbstract:This paper presented a method of designing multi-channel high-speed data acquisition system ,which with faster speed,higher precision and better real-time compared to the traditional data acquisition card that use of the ISA bus .This design uses a relatively common FPGA,high-speed AD,high-speed FIFO and 51MCU to form a data acquisition system .The collect-ed data is stored directly into the high-speed FIFO by DMA control technology,then microcontroller read out data and transmit-ted to PC through the USB port ,PC display and process the data in the interface developed by LabVIEW .Experiments show that the acquisition system has fast communication speed,performance,adjustable gain,continuous sampling features and so on,it ’s more suitable for the test system.words Key words:High-Speed Data Acquisition system ;FPGA ;High Speed FIFO ;LabVIEW 中图分类号:TP73文献标识码:B文章编号:1001-9227(2013)-01-0148-03基于嵌入式的多通道高速数据采集系统徐航1,罗巍2(1四川大学电气信息学院四川成都,610065)(2浙江大学电气学院浙江杭州,310027)收稿日期:2012-10-25作者简介:徐航(1987-),男,硕士研究生,研究方向为电子技术应用。

基于嵌入式系统的同步数据采集设计及应用

( 庆 大 学输 配 电 装 备 及 系统 安 全 与 新技 术 国 家重 点 实验 室 重 庆 重 403 ) 0 0 0

摘

要 :为实现对发 电设 备电参量的实时测量 和监控 , 绍了基于 A 1 介 T9 RM9 0 2 0的外 部总线接 口( B ) E I与数 据采集

a q iiin c i M AX1 2 i r s n e f r c us t h p o 34 s p e e t d o me s rn a d a u i g n mo i rn ee t ia p r me e s f o r g n r tn n t i g lc rc l a a t r o p we - e e a i g o e u p n . e b s i t ra e d i e n li s i g o W o k r e i n d, n h a t a i me i f c lu a i g q ime t Th u n e f c , r r a d mu tt k n f Vx v a r s a e d sg e a d t e f s rt h t o ac ltn c t e e e t ia a a t ri e u e . e r s l s o h tt eme h d c n i p o e t em e s r me ta c r c n p e h lc rc lp r me e d d c d Th e u t h ws t a h t o a S m rv h a u e n c u a ya ds ed o o r g n r t g e u p n . e m e h d h s r f r n e v l e t h p l a i n o m b d e y t m n ee t i l fp we— e e a i q i me t Th t o a e e e c a u o t e a p i t f e e d d s s e i lc rc n c o a e g n e i g fed . n i e rn il s

基于STM32单片机的多路数据采集系统设计毕业设计

基于STM32单片机的多路数据采集系统设计毕业设计本文将设计一种基于STM32单片机的多路数据采集系统。

该系统可以实现多个输入信号的采集和处理,在电子仪器、自动化控制、工业检测等领域具有广泛的应用前景。

首先,我们需要选择合适的STM32单片机作为系统的核心处理器。

STM32系列单片机具有低功耗、高性能和丰富的外设资源等优点,非常适合用于嵌入式数据采集系统的设计。

在选取单片机时,要考虑到系统对于处理速度、存储容量和外设接口的需求,以及预算等因素。

其次,我们需要设计合适的外部电路来连接待采集的信号源。

常用的信号源包括温度传感器、光敏电阻、加速度传感器等。

我们可以使用适当的模拟电路将这些信号转换为STM32单片机能够接收的电平。

此外,还可以考虑使用模数转换芯片来实现对多路模拟信号的高速采集。

接下来,我们需要设计软件算法来对采集到的数据进行处理。

在数据采集系统中,常见的算法包括滤波、数据压缩、数据存储等。

通过滤波算法可以去除噪声,提高信号的质量;数据压缩可以减少数据存储和传输的空间;数据存储可以将采集到的数据保存在存储介质中以供后续分析。

最后,我们需要设计用户界面以便用户能够方便地操作系统。

可以使用LCD屏幕和按键等外设来实现用户界面的设计。

用户界面应该直观简洁,提供友好的操作和显示效果,方便用户进行数据采集和系统设置。

综上所述,基于STM32单片机的多路数据采集系统设计需要考虑到硬件电路和软件算法的设计,以及用户界面的设计。

通过合理的设计和实现,可以实现多路信号的高速采集、滤波处理和存储,为电子仪器、自动化控制和工业检测等领域提供可靠的数据支持。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

嵌入式高速数据采集处理模块的设计实现夏沈杰周晓霞倪明柴小丽(华东计算技术研究所,上海200233)

摘要:本文主要提出了DSP+FPGA的架构实现嵌入式高速数据采集的思想,以提高采集系统的整体性能。并且将抽取、内插、FFT和多种滤波处理按照特性在DsP与FPGA上进行了相应的优化设计及实现,从而大大提高了处理性能,而且H呵和滤波可并行处理,进一步提高了系统运行速度和效率。该系统还可以通过对FPGA内下栽不同的内容及改变DsP程序来实现在最小改动前提下对系统进行功能扩展、改变及升级,从这个方面讲,这个系统具有一定的灵活性、先进性和前瞻性。关键词:高速数据采集抽取内插DSPFPGAFIRFFI’

1引言数据采集技术是信息科学的一个重要分支,是以传感器、信号测量与处理、计算机等技术为基础而形成的一门综合应用技术,它具有很强的实用性,主要应用在仪器、通讯、雷达、遥感测量、地质、医药器械等各个领域。近年来,各种应用都在向数据采集技术提出更高的要求,如速度、分辨力、精度、功能、接口能力、软件设计以及抗恶劣环境能力,传统采用CPU+RAM+ADC方式的数据采集技术已经无法满足需要。随着DSP与FPGA性能的进一步发展以及开发手段的不断丰富,DSP+FPGA的方案正在逐渐被业界所重视。综上所述,本文提出使用DSP+FPGA架构来设计嵌入式高速数据采集处理系统,包括实时数据处理、信号处理、高速存储及快速校准,并用Simulink进行建模仿真,最终将其实现。

2高速数据采集处理模块的结构及功能高速数据采集系统的组成框图如下图所示:

图1高速数据采集系统组成框图作者简介:夏沈杰(1980一),男,硕士,研究方向为嵌入式计算枧和接口技术;周晓霞,工程师;倪明,研究员;柴小丽,高工。

118其中虚框内本文所要实现的数据采集处理模块。由于高速数据采集系统数据流速度快、运算量大、功能复杂及具有实时切换、调节能力,其可重构性要求使得它越来越倾向于灵活性强的DSP和FPGA。数据采集处理模块需要完成的功能有:1.是实时数据处理,包括抽取、峰值检测、根据校准结果进行数值调整等;2.是信号处理,包括内插、数值平滑、F盯、各种滤波等;3.是高速存储,根据用户要求将对应的高速数据流进行选择存储;4是快速校准,定时产生校准信号对模拟前端进行快速多点校准。3基于DSP+FPGA的高速数据采集处理模块设计根据DSP与FPGA的特性,就上述4种功能在DSP与FPGA中进行如下分配:高速数字采集处理模块的实时数据处理部分的特点是:整个数据流的速度非常高,很难直接用采样频率对数据流进行处理。解决方法有2种,1是采用能承受这么高处理速度的器件,2是先将高速’数据流进行降频处理,从而降低对处理器件的要求,但是处理位宽将成倍提高,而且实时处理算法也需要相应改变。第1种处理方法对器件要求非常高,实际上这样的器件很难找,而且价格相当贵,没有实用价值,所以本文采用第2种方法,即将ADC产生的高速数据流分频分相处理从而降低对后续操作的工作频率要求,由于位宽会随着分频倍数相应变的很高,所以分频数不能很大。这样的接入方案可以在FPGA中使用锁相环(PLL)加分相锁存电路来实现。数字接入后需要根据用户需要进行相应的实时数字处理,比如抽取、峰值检测、数值调整等。降频后的数据流速度依然很高,而且位宽是ADC输出位数的数倍,基本无法由FPGA以外的器件代替,所以这部分处理都需要在FPGA中实现。信号处理部分的主要任务是滤波、内插、数值平滑、FFYr等计算。传统的信号处理过程中使用DSP进行处理,如果面对多种大量重复操作的处理,DSP便暴露出其并行性不够,无法同时对数据进行多种处理的弱点。在现代高速数字采集处理系统中,有可能需要对同一批数据进行多次多种处理,所以需要给处理过程加速。具体方法就是使用FPGA来实现算法结构单一、数据量大的部分,如内插、数值平滑、肿,而需要能被灵活配置的多种滤波器只能由DSP来完成。实时的数据存储的速率要求与实时数字处理完后的数据速率有关,对很高速的数据流,存储速度要求很高,在连续采样的情况下可以考虑用高速RAM来满足存储要求,现在很多FPGA都带有内部RAM,在存储深度要求不是很高的情况下可以考虑使用FPGA内部RAM实现。对于在需要很大存储深度的工作状态下则需要使用外部容量较大的快速RAM如SBSRAM等来实现存储。由于实时数据存储的数据来源是在FPGA中实现的实时算法的输出,所以需要由FPGA设计与这些RAM的接口。而对于信号处理用的RAM,则需要根据产生数据的信号处理在DSP或者是FPGA中实现来确定,如果是DSP实现则直接挂在DSP外部存储总线上,否则就挂在FPGA的RAM控制器上。不过由于本文采用的DSP+FPGA架构是以DSP为主,所以直接由DSP协调控制使用DSP外接RAM、FPGA内部及外接RAM空间。而对用户设置的存储要求如数据同步帧等的检测由于其实时性高,由FPGA完成。快速校准需要每经过一段时间通过输出数据给DA产生一个已知标准信号,将其通过模拟前端经ADC数字化与标准的信号进行多点对比,然后产生一个校准曲线,最后交给实时数据处理部分进行数值调整,它是一个不断重复而且独立的模块,所以选择并行度高的FPGA将其实现。

4算法设计根据FPGA和DSP的特点不同,对各部分算法进行相应优化设计,下面介绍一下对FIR、数值平滑及FFT的优化设计。4.1FIR的优化设计拥有丰富DSP资源的FPGA使用DA算法可以加速FIR的速度,特别是当多通道都需要内插的时候,FPGA的优势就更明显,所耗费时间与单通道完全一样。下面使用DA算法对FIR进行优化。假设输入为X[n],输出为Y[n],滤波系数为C[n],阶数为N,则FIR可以用下式表示:N—lY[n]=<c,x>=∑c[o]・x[n]=

n‘’—ffi—0c[O]x[O]+C[I]X[1]+…+C[N—I]X[N—1]

假设系数c[n]是已知常数,X[n]是变量,在有符号DA系统中假设变量x[n]的表达119式如下:B-2x[n]=一2弘1・xB-l+∑xb[n]×26,其中

Xb[11]E[0,1]式中,】【b[n]表示x[n]的第b位,而X[n]也就是x的第n次采样。于是,内积Y可以表示为:N-1B一2Y=∑c[n]・[-28。1・xB_1+∑xb[n]×26]

重新分别求和(也就是分布式算法的由来),其结果如下:Y=c[0](一xB一1[0]2B一1+xB-2[0]2B一2+…+x0[0]20)+c[1](一xB一1[1]2B一1+xB一2[1]2B一2+…+如[1]20)+c[N一1](一xB一1[N一1]2B—l+xB一2[N—1]2B一2+…+如[N一1]20)=(c[0]xB一1[0]+c[1]xB一1[1]+…+c[N一1]xB一1[N一1])2B—l+(c[0]xB-2[0]+c[1]xB一2[1]

+…+e[N—1]xB一2[N一1])2B一2+…+(c[0]xO[0]+c[1]如[1]+…+c[N—1])D[N—1)20从上面的式子可以看出,DA是一种主要操作为乘加的算法。它与传统算法实现乘加运算的不同在于执行部分积运算的先后顺序不同。分布式算法在实现乘加功能时,是通过将各输人数据的每一对应位产生的部分积预先进行相加形成相应的部分积,然后再对各个部分积累加形成最终结果的,而传统算法是等到所有乘积已经产生之后再来相加完成乘加运算的。在需要FIR的模式下一般速度会比不需要进行FIR的模式下慢一些,再使用串行结构会更加降低速度,但根据本系统8路数据并行的特性使用8路串行处理,时间耗费一般还在ms以下,所以对于主机处理显示来说速度并没有因为使用串行结构而慢很多。与传统串行算法相比,分布式算法可极大地减少FPGA内部资源的消耗,提高电路的执行速度。它的实现框图如图2(虚线为流水线寄存器)所示。

图2DA实现框图

DSP中则只需根据用户需要从RAM中选取适当的滤波器系数,就可以通过调用TIC67xDSPLIB

中的DSPF_.sp_fir_gen函数直接实现各种阶数及幅频特性的FIR。

4.2数值平滑的优化设计数值平滑其实也是滤波的一种,它通过将前后多点平均来平滑信号。数值平滑包括8点、16点、32点、64点、128点、256点、512点、1024点平滑,一般由主机来计算产生,但是这样做的结果是大大降低了显示刷新的速度,特别是256点平均时刷新速度将非常慢。在本文中使用FPGA将其实现,充分利用FPGA内丰富的DSP资源以及大进位链的优势。数值平滑的公式如下式所示(以8点平均为例子)iwave『i1=(wavefi一71+wave[i一6]+wavefi一51+wavefi一41+wavefi一31+wavefi一21+waveri一11+wavefil)/8基本流程如下(假设高速数据采集部分将数据分为8路进行处理及存储),数据流分为8路并行进入处理模块,然后根据平均所需点数N,进行平均操作。从上面的式子可以看出,需要对各个通路进行分别处理,所以资源消耗是串行方式的8倍多,但速度也相应的提高了8倍,在对大批数据进行平均时效果尤为明显。由于FPGA内加法的进位链达70位,所以在3种波形平均方式下加法速度始终保持。并且8、16、32、64、128、256、512、1024都是2的整数次,也就是说,对这几个数做除法就相当于直接将对应的低几位去掉,根本不需要花时间。这样在FPGA中进行波形平均的处理在不同的点数要求下,速度都在同一个量级上,比主控CPU要快好几个量级。当然如果对大位宽的数据进行如256点及以上平滑的速度仍然不满意,就可以用CSD加法来改善速度,因为CSD本身的特性注定了它的加法可以做到无进位延迟,从而做到加法速度的提升,但代价是需要多耗费数倍的FP.GA资源。下图是数值平滑的框图。

图3数值平滑框图

4.3FFT的优化设计在本文中,使用了重叠卷积运算对肿进行

优化。重叠卷积运算是指把采样序列X(n)分成前后部分重叠的多个数据块(段),每个数据块是由前面的M个保留数据和(N—M)个新数据组成,以保证送至FFr进行卷积的数据块为N点。而将每段N长处理结果的前M个数据抛掉,保留后(N—M)长数据,各段结果依次相接构成总的处理结果。为保证处理结果的正确性,分段时应注意如下2点I第1,第1段的前M个数据补零;第2,重叠长度视具体应用要求而定,如做脉压时,应保证任何时刻回波都能被有效压缩,所以需要大于等于信号时宽,通常取为信号时宽。重叠增加了卷积运算次数,但提高了并行度,非常适合FPGA处理。但是由于FPGA中实现的FFr无法改变处理点数,所以需要DSP根据用户需要对数据进行相应分段然后控制FPGA内各个lH’模块进行处理。