【SPI】LPC1700系列Cortex-M3_ZLG1

【SPI】LPC1700系列Cortex-M3_ZLG

同步串行外设接口(SPI) LPC1700系列Cortex-M3微控制器SPI 简介与特性1SPI 基本操作2SPI 寄存器结构3SPI 操作流程与示例4SPI 使用注意事项5SPI 是一种同步串行外设接口,允许MCU 与外围设备以串行方式通信。

SPI 控制器使LPC1700系列Cortex-M3能与众多外设通信,从而大大增强了处理器的外设扩展能力。

MOSIMISO SCKSSEL LPC1700SCK :用于同步SPI 接口间数据传输的时钟信号MOSI :单向信号线,数据通过它由主机传输到从机SSEL :指示被选择参与数据传输的从机(低电平有效)MISO :单向信号线,数据通过它由从机传输到主机从机选择串行时钟主机输入从机输出主机输出从机输入SPI 总线可以连接一个主机和多个从机同一时刻只允许主机和一个从机进行通信SPI 总线通信是全双工的SPI 总线从机从机从机从机从机从机LPC1700(主机)SPI 简介与特性1SPI 基本操作2SPI 寄存器结构SPI 操作流程与示例SPI 使用注意事项SPI初始化●时钟极性控制位——CPOL该位决定了SPI总线空闲时,SCK时钟线的电平状态。

CPOL=0,当SPI总线空闲时,SCK时钟线为低电平;CPOL=1,当SPI总线空闲时,SCK时钟线为高电平。

●时钟相位控制位——CPHA该位决定了SPI总线上数据的采样位置。

CPHA=0,SPI总线在时钟线的第1个跳变沿采样数据;CPHA=1,SPI总线在时钟线的第2个跳变沿采样数据。

10SCKMOSI模式一:SCK 空闲时为低,SCK 前沿采样采样结果为:10101010b总线空闲时,SCK 为低电平CPOL=0CPHA=011SCKMOSI模式二:SCK 空闲时为低,SCK 后沿采样采样结果为:01010101b总线空闲时,SCK 为低电平CPOL=0CPHA=11010101SCKMOSI模式三:SCK 空闲时为高,SCK 前沿采样采样结果为:10101010b总线空闲时,SCK 为高电平从SCK 的前沿开始采样CPOL=1CPHA=001010101SCKMOSI模式四:SCK 空闲时为高,SCK 后沿采样采样结果为:01010101b从SCK 的前沿开始采样总线空闲时,SCK 为高电平CPOL=1CPHA=1帧长度:可以设置成8~16位帧格式:设置高位先发送还是低位先发送配置帧长度为8,低位先发送,情形如下所示:1 2 3 4 5 6 7 8帧长度帧格式帧长度为8低位在前P0.0SCKMOSISPI 主机MOSISCKSSELSPI 从机DATA需发送的数据数据编码后发送主机提供时钟DATA从机选择释放从机数据传输完成P0.0SCKMISOSPI 主机MISOSCKSSELSPI 从机需发送的数据DATA从机选择释放从机数据传输完成DATASPI简介与特性SPI基本操作3SPI寄存器结构SPI操作流程与示例SPI使用注意事项数据寄存器(S0SPDR)数据移位寄存器收发模块时钟计数寄存器(S0SPCCR)F PCLK控制寄存器(S0SPCR )中断标志寄存器(S0SPINT) 状态寄存器(S0SPSR)F PCLK 经分频后为收发模块提供时钟信号SPI 初始化配置反映收发模块的状态信息反映传输完成的中断信息SPI 控制器的核心SPI 传输完成发生模式错误Bit4:MODF Bit7:SPIF SPI 中断标志寄存器SPINT[0]置位SPI 控制寄存器SPI 状态寄存器SPI简介与特性SPI基本操作4SPI操作流程与示例SPI使用注意事项void SPIMasterInit (uint8 fdiv){S0SPCR = (1 << 5) |(0 << 7) |(0 << 2) |(0 << 6) |(1 << 4) |(0 << 3); if (fdiv < 8) {fdiv = 8;}S0SPCCR = fdiv & 0xfe; }void SPISlaveInit (void){S0SPCR = (0 << 5) | (0 << 7) |(0 << 2) |(0 << 6) |(1 << 4) |(0 << 3);}主机模式/从机模式不使用中断帧长度为8位先发送高位时钟极性为1时钟相位为0设置时钟频率uint8 MSendData (uint8 ucdata){IO0CLR |= SPI_CS;S0SPDR = ucdata;while ((S0SPSR & 0x80) == 0);IO0SET |= SPI_CS;return (S0SPDR);}void SSendData (uint8 ucdata){S0SPDR = ucdata ;while ((S0SPSR & 0x80) == 0);}选中从机发送数据等待数据发送完成释放从机返回接收到的数据发送数据等待数据发送完成SPI 简介与特性SPI 基本操作SPI 寄存器结构SPI 操作流程与示例4SPI 使用注意事项5⏹连接时,MOSI、MISO不能交叉连接;⏹使用时注意主机和从机的模式设置匹配;⏹SPI主机提供总线时钟;⏹作为主机使用时,SSEL引脚可以作为I/O口使用;指定作为SSEL功能后,则必须无效。

01-第一章Cortex-M3处理器简介 共25页

1.2 Cortex-M3 处理器基本结构

• 处理器核Cortex-M3 • NVIC • Bus Matrix • FPB(Flash Patch and Breakpoint) • DWT • ITM • MPU • ETM • TPIU • SW/SWJ-DP

Cortex-M3核的主要特点

1.3.3 STM32 系列MCU 的优点

• 性能出众而且功能创新的片上外设:STM32 处理 器片上外围的优势来源于双APB 总线结构,其中 有一个高速 APB(速度可达CPU 的运行频率), 连接到该总线上的外设能以更高的速度运行。针 对 MCU 应用中最常见的电机控制,STM32 对片 上外围设备进行一些功能创新。

• 6 个可独立配置的指令比较器,用于转换从 代码空间到系统空间的指令预取,或执行 硬件断点;

• 2 个常量比较器用于转换从代码空间到系统 空间的常量访问。

数据观测与跟踪单元(Data Watchpoint and Trace、DWT)

• DWT 有 4 个比较器可配置为硬件断点、 ETM 触发器、PC 采样事件触发器或数据 地址采样触发器;

• 高度的集成整合:STM32 处理器最大程度地实现 集成,尽可能地减少对外部器件的要求。

• 易于开发,可使产品快速进入市场。

1.3.4 STM32 处理器开发工具

谢谢!

• 硬件跟踪:DWT 产生信息包,由ITM 向外发送;

• 时间戳:ITM 可产生与所发送信息包相关的时间

戳包,并向外发送。

存储器保护单元(Memory Protection Unit,MPU)

• MPU 提供以下支持: • 存储保护;保护区域重叠; • 访问允许控制;向系统传递存储器属性。

zlg翻译的LPC1700中文手册

zlg翻译的LPC1700中文手册广州周立功单片机发展有限公司第1章第1章概述1.1 简介 LPC1700 系列Cortex-M3 微控制器用于处理要求高度集成和低功耗的嵌入式应用。

ARMCortex-M3 是下一代新生内核,它可提供系统增强型特性,例如现代化调试特性和支持更高级别的块集成。

LPC1700 系列 Cortex-M3 微控制器的操作频率可达 100MHz。

ARM Cortex-M3 CPU 具有 3级流水线和哈佛结构,带独立的本地指令和数据总线以及用于外设的稍微低性能的第三条总线。

ARM Cortex-M3 CPU 还包含一个支持随机跳转的内部预取指单元。

LPC1700 系列 Cortex-M3 微控制器的外设组件包含高达512KB 的 Flash 存储器、64KB 的数据存储器、以太网 MAC、 USB 主机/从机/OTG 接口、通道的通用 DMA 控制器、个 UART、 8 4 2 22 条 CAN 通道、2 个 SSP 控制器、SPI 接口、3 个 I C 接口、2-输入和 2-输出的 I S 接口、8 通道的 12 位 ADC、10 位 DAC、电机控制 PWM、正交编码器接口、4 个通用定时器、6-输出的通用 PWM、带独立电池供电的超低功耗 RTC 和多达 70 个的通用 I/O 管脚。

1.2 特性 ARM Cortex-M3 处理器,可在高至 100MHz 的频率存储器保护单元(MPU) ; ARM Cortex-M3 下运行,并包含一个支持 8 个区的内置了嵌套的向量中断控制器(NVIC) ; 具有在系统编程(ISP)和在应用编程(IAP)功能的 512KB 片上 Flash 程序存储器。

把增强型的 Flash 存储加速器和Flash 存储器在 CPU 本地代码/数据总线上的位置进行整合,则 Flash 可提供高性能的代码; 64KB 片内 SRAM 包括: –32KB SRAM 可供高性能 CPU 通过本2 个 16KB SRAM 模块,带独立访问路径,可进行更高地代码/数据总线访问; –吞量的操作。

第2章 LPC1700系列微控制器硬件体系结构

式中FPLLIN表示锁相环的输入时钟频率,FCCO表示电流 控制振荡器(CCO)的输出频率,N和M分别是分频和倍 频系数。

所有100个引脚可以分为5类: 3. 时钟引脚 时钟引脚主要有两类:一个是主振荡器的时钟引脚:XTA L1和XTAL2;另一个是RTC振荡器的时钟引脚:RTCX1和RTCX2。 还有一个引脚CLKOUT和P1.25复用,可以输出处理器内部的各 种时钟,方便用户调试使用。 4. 仿真引脚 仿真引脚也是分成了三类:一类是常用的JATG接口,使 用TDO、TDI、TMS、TRST、TCK和RTCK这几个引脚;一类是SWD 接口,使用SWO、SWDIO和SWDCLK这三个引脚;一类是跟踪接 口,使用TRACEDA[3]、TRACEDA[2]、TRACEDA[1]、TRACEDA[0] 和TRACECLK这几个引脚。

• CPU时钟配置寄存器(CCLKCFG)

功能: PLL0输出时钟必须要经过分频才能提供给CPU使 用,PLL0输出的分频由CCLKCFG寄存器进行控制。当 PLL0被旁路时,相当于1分频。当PLL0正在运行时, 输出必须经过分频以使CPU时钟频率(CCLK)工作在 限定的范围内。

• CPU时钟配置寄存器(CCLKCFG)

• 系统控制和状态寄存器(SCS)

• 内部RC振荡器

内部RC振荡器(IRC)可用作看门狗定时器的时钟 源,也可以用作驱动PLL0和CPU的时钟源。 如果使用USB功能或者CAN通信模块的通信波特率高 于100Kbit/s时,IRC的精度达不到要求,因使用外部晶 体振荡器作为系统时钟源。

典型MCU架构详解与主流MCU介绍

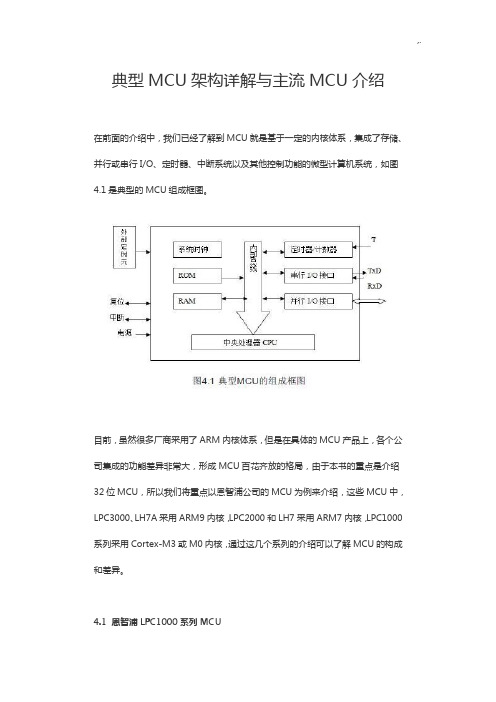

典型MCU架构详解与主流MCU介绍在前面的介绍中,我们已经了解到MCU就是基于一定的内核体系,集成了存储、并行或串行I/O、定时器、中断系统以及其他控制功能的微型计算机系统,如图4.1是典型的MCU组成框图。

目前,虽然很多厂商采用了ARM内核体系,但是在具体的MCU产品上,各个公司集成的功能差异非常大,形成MCU百花齐放的格局,由于本书的重点是介绍32位MCU,所以我们将重点以恩智浦公司的MCU为例来介绍,这些MCU中,LPC3000、LH7A采用ARM9内核,LPC2000和LH7采用ARM7内核,LPC1000系列采用Cortex-M3或M0内核,通过这几个系列的介绍可以了解MCU的构成和差异。

4.1 恩智浦LPC1000系列MCULPC1000系列MCU是以第二代Cortex-M3为内核的微控制器,用于处理要求高度集成和低功耗的嵌入式应用。

采用3级流水线和哈佛结构,其运行速度高达100MHz,带独立的本地指令和数据总线以及用于外设的第三条总线,使得代码执行速度高达1.25MIPS/MHz,并包含一个支持分支预测的内部预取指单元,特别适用于静电设计、照明设备、工业网络、报警系统、白色家电、电机控制等领域。

LPC1000系列MCU又分为LPC1700系列和LPC1300系列,下面我们分开介绍。

4.1.1 LPC1700系列MCU介绍LPC1700系列ARM是以第二代的Cortex-M3为内核,是为嵌入式系统应用而设计的高性能、低功耗的32位微处理器,适用于仪器仪表、工业通讯、电机控制、灯光控制、报警系统等领域。

其操作频率高达100MHz,采用3级流水线和哈佛结构,带独立的本地指令和数据总线以及用于外设的高性能的第三条总线,使得代码执行速度高达1.25MIPS/MHz,并包含一个支持分支预测的内部预取指单元。

LPC1700系列ARM Cortex-M3的外设组件:最高配置包括512KB片内Flash 程序存储器、64KB片内SRAM、8通道GPDMA控制器、4个32位通用定时器、一个8通道12位ADC、一个10位DAC、一路电机控制PWM输出、一个正交编码器接口、6路通用PWM输出、一个看门狗定时器以及一个独立供电的超低功耗RTC。

【GPIO】LPC1700系列

GPIO特性描述|通用输入输出

LPC1700系列Cortex-M3有5组GPIO,多达70个通用I/O 管脚(100管脚封装); 所有GPIO寄存器位于AHB总线上,可以进行高性能的 CPU快速访问,支持Cortex-M3位带操作; 可配置为上拉/下拉电阻、开漏和中继模式; GPIO允许进行DMA数据操作。

设置引脚连接模块

设置下降沿中断 使能GPIO中断 打开全局中断

void GPIO_ISR (void) { if((IO0IntStatF & 0x01) != 0) { 判断是否为P0.0下降沿中断 IO0IntClr = 0x01; 清除中断标志 ...... 用户其它代码 } }

GPIO特性描述|中断

LPC1700系列Cortex-M3的P0和P2还具有中断功能, P0和P2每个引脚都可配置为上升沿、下降沿或边沿中断。

P0.x

LPC1700

P2.x

GPIO中断还具 有掉电唤醒功能

下降沿中断

边沿中断

目

录

1

GPIO简介 GPIO特性描述

2

3 4

GPIO输入输出

GPIO中断

GPIO输入输出|I/O相关寄存器

2

设置下降沿中断使能

清除中断标志

IO0/2IntStatR IOIntStatus

IO0/2IntStatF

GPIO中断|中断操作流程

操作示例——设置P0.0下降沿中断

PINSEL0 &= 0xFFFFFFFC; PINMODE0 &= 0xFFFFFFFC; IO0IntEnF |= 0x01; ISER0 |= (1 << 21); zyIrqEnable();

典型MCU架构详解与主流MCU介绍

v1.0 可编辑可修改典型MCU架构详解与主流MCU介绍在前面的介绍中,我们已经了解到MCU就是基于一定的内核体系,集成了存储、并行或串行I/O、定时器、中断系统以及其他控制功能的微型计算机系统,如图是典型的MCU组成框图。

目前,虽然很多厂商采用了ARM内核体系,但是在具体的MCU产品上,各个公司集成的功能差异非常大,形成MCU百花齐放的格局,由于本书的重点是介绍32位MCU,所以我们将重点以恩智浦公司的MCU为例来介绍,这些MCU中,LPC3000、LH7A采用ARM9内核,LPC2000和LH7采用ARM7内核,LPC1000系列采用Cortex-M3或M0内核,通过这几个系列的介绍可以了解MCU的构成和差异。

恩智浦LPC1000系列MCULPC1000系列MCU是以第二代Cortex-M3为内核的微控制器,用于处理要求高度集成和低功耗的嵌入式应用。

采用3级流水线和哈佛结构,其运行速度高达100MHz,带独立的本地指令和数据总线以及用于外设的第三条总线,使得代码执行速度高达MHz,并包含一个支持分支预测的内部预取指单元,特别适用于静电设计、照明设备、工业网络、报警系统、白色家电、电机控制等领域。

LPC1000系列MCU又分为LPC1700系列和LPC1300系列,下面我们分开介绍。

LPC1700系列MCU介绍LPC1700系列ARM是以第二代的Cortex-M3为内核,是为嵌入式系统应用而设计的高性能、低功耗的32位微处理器,适用于仪器仪表、工业通讯、电机控制、灯光控制、报警系统等领域。

其操作频率高达100MHz,采用3级流水线和哈佛结构,带独立的本地指令和数据总线以及用于外设的高性能的第三条总线,使得代码执行速度高达MHz,并包含一个支持分支预测的内部预取指单元。

LPC1700系列ARM Cortex-M3的外设组件:最高配置包括512KB片内Flash程序存储器、64KB片内SRAM、8通道GPDMA控制器、4个32位通用定时器、一个8通道12位ADC、一个10位DAC、一路电机控制PWM输出、一个正交编码器接口、6路通用PWM输出、一个看门狗定时器以及一个独立供电的超低功耗RTC。

基于Cortex—m3为内核的开发板设计与制作

基于Cortex—m3为内核的开发板设计与制作作者:丁红王怀德来源:《现代电子技术》2012年第18期摘要:为了实现以CortexM3为内核制作一个实验开发板,用于教学、竞赛、工控开发,通过一系列的模拟仿真和研究分析,设计了开发板的电路原理图,分析了以太网的结构、原理、初始化过程,USBOTG的设计思路、电路原理图和初始化过程以及SD卡驱动电路的设计过程,并制作了可实际使用的电路板。

整个开发板主要能够为学生的课程设计、毕业设计、创新活动提供良好平台。

关键词:CortexM3;LPC1768;以太网驱动电路;USBOTG驱动电路;SD卡驱动电路中图分类号:TN91934文献标识码:A文章编号:1004373X(2012)18001903ARMCortexM3处理器是一款具有极高运算能力和中断响应能力的处理器内核,能够实现8位和16位处理器级数的代码存储密度。

该内核体积很小,从而使它的封装更为小型,成本更为低廉,应用更为广泛。

NXP(恩智浦半导体)公司的LPC1700系列ARM是基于CortexM3内核的微控制器,是为嵌入式系统应用而设计的高性能、低功耗的32位微处理器,适用于仪器仪表、工业通信、电机控制、灯光控制、报警系统等领域。

它的操作频率高达120MHz,采用3级流水线和哈佛结构,带独立的本地指令和数据总线,代码执行速度高达1.25MIPS/MHz,同时包含1个支持随机跳转的内部预取指单元[1]。

本文设计了以LPC1768为控制器核心的开发板,完成了以太网、USBOTG、SD卡驱动等控制电路设计及程序驱动设计。

1以太网驱动电路的设计以太网模块包含一个功能齐全的10Mb/s或100Mb/s以太网MAC(媒体访问控制),以太网MAC通过使用DMA硬件加速功能来优化其性能。

以太网模块具有大量的控制寄存器组,可以提供:半双工/全双工操作、流控制、控制帧、重发硬件加速、接收包过滤以及LAN上的唤醒等。

利用分散集中式(ScatterGather)DMA进行自动的帧发送和接收操作,减轻了CPU 的工作量[2]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SPI初始化 模式介绍 初始化| 初始化

CPOL=0 CPHA=0 模式一:SCK空闲时为低, SCK前沿采样 采样结果为:10101010b 从SCK的前沿 开始采样

总线空闲时, SCK为低电平

SCK

1 MOSI

0

1

0

1

0

1

0

SPI初始化 模式介绍 初始化| 初始化

CPOL=0 CPHA=1 模式二:SCK空闲时为低, SCK后沿采样 采样结果为:01010101b 从SCK的后沿 开始采样

从机选 择 释放从 机

SPI主机

P0.0

SPI从机

SSEL

数据传 输完成

SCK

SCK

需发送 的数据

DATA

MISO MISO

DATA

目

录

1 2 3 4 5

SPI简介与特性 SPI基本操作 SPI寄存器结构 SPI操作流程与示例 SPI使用注意事项

SPI寄存器结构 寄存器结构

FPCLK 时钟计数寄存器 (S0SPCCR) FPCLK经分频后为收 发模块提供时钟信号

选中从机 发送数据 等待数据发送完成 释放从机 返回接收到的数据

void SSendData (uint8 ucdata) { S0SPDR = ucdata; while ((S0SPSR & 0x80) == 0); }

发送数据 等待数据发送完成

目

录

1 2 3 4 5

SPI简介与特性 SPI基本操作 SPI寄存器结构 SPI操作流程与示例 SPI使用注意事项

Bit7:SPIF Bit4:MODF SPI状态寄存器

SPI中断标志寄存器 SPINT[0] 置位

目

录

1 2 3 4 5

SPI简介与特性 SPI基本操作 SPI寄存器结构 SPI操作流程与示例 SPI使用注意事项

SPI操作流程与示例 主机、从机初始化 操作流程与示例|主机、 操作流程与示例

void SPISlaveInit (void) void SPIMasterInit (uint8 fdiv) { { S0SPCR = (0 << 5) | 主机模式/从机模式 主机模式 从机模式 S0SPCR = (1 << 5) | (0 << 7) | 不使用中断 (0 << 7) | (0 << 2) | 帧长度为8位 帧长度为 位 (0 << 2) | (0 << 6) | (0 << 6) | 先发送高位 (1 << 4) | (1 << 4) | 时钟极性为1 时钟极性为 (0 << 3); (0 << 3); 时钟相位为0 时钟相位为 } if (fdiv < 8) { fdiv = 8; 设置时钟频率 } S0SPCCR = fdiv & 0xfe; }

SPI初始化配置 数据寄存器 (S0SPDR) 收发模块 控制寄存器 (S0SPCR) 反映收发模块 的状态信息 状态寄存器 (S0SPSR) 反映传输完成 的中断信息 中断标志寄存器 (S0SPINT) 数据移位寄存器 SPI控制 器的核心

SPI寄存器结构 寄存器结构

SPI控制寄存器

SPI传输完成 发生模式错误

SPI初始化 时钟极性、相位 初始化|时钟极性、 初始化

时钟极性控制位——CPOL

该位决定了SPI总线空闲时,SCK时钟线的电平状态。 CPOL=0,当SPI总线空闲时,SCK时钟线为低电平; CPOL=1,当SPI总线空闲时,SCK时钟线为高电平。

时钟相位控制位——CPHA

该位决定了SPI总线上数据的采样位置。 CPHA=0,SPI总线在时钟线的第1个跳变沿采样数据; CPHA=1,SPI总线在时钟线的第2个跳变沿采样数据。

1 帧长度

2

3

4

5

67Βιβλιοθήκη 8帧长度为8低位在前

帧格式

SPI收发数据 主机发送、从机接收 收发数据|主机发送、 收发数据

从机选 择 释放从 机

SPI主机

主机提 供时钟

P0.0

SPI从机

SSEL

需发送 的数据

SCK

SCK

数据传 输完成

DATA

MOSI MOSI

DATA 数据编码 后发送

SPI收发数据 主机接收、从机发送 收发数据|主机接收、 收发数据

SPI特性 特性

同一时刻只允许主机和一个从机进行通信 SPI总线可以连接一个主机和多个从机 SPI总线通信是全双工的

LPC1700 (主机) 主机)

从机

从机

从机

SPI总线

从机

从机

从机

目

录

1 2 3 4 5

SPI简介与特性 SPI基本操作 SPI寄存器结构 SPI操作流程与示例 SPI使用注意事项

SPI操作流程与示例 数据发送 操作流程与示例| 操作流程与示例

uint8 MSendData (uint8 ucdata) { IO0CLR |= SPI_CS; S0SPDR = ucdata; while ((S0SPSR & 0x80) == 0); IO0SET |= SPI_CS; return (S0SPDR); }

CPOL=1 CPHA=1 模式四:SCK空闲时为高, SCK后沿采样 采样结果为:01010101b 从SCK的前沿 开始采样

总线空闲时, SCK为高电平

SCK

0 MOSI

1

0

1

0

1

0

1

SPI初始化 帧设置 初始化| 初始化

帧长度:可以设置成8~16位 帧格式:设置高位先发送还是低位先发送

配置帧长度为8,低位先发送,情形如下所示:

SPI使用注意事项 使用注意事项

连接时,MOSI、MISO不能交叉连接; 使用时注意主机和从机的模式设置匹配; SPI主机提供总线时钟; 作为主机使用时,SSEL引脚可以作为I/O口使 用;指定作为SSEL功能后,则必须无效。

同步串行外设接口(SPI) 同步串行外设接口

LPC1700系列Cortex-M3微控制器

目

录

1 2 3 4 5

SPI简介与特性 SPI基本操作 SPI寄存器结构 SPI操作流程与示例 SPI使用注意事项

SPI简介 简介

SPI是一种同步串行外设接口,允许MCU与外围设备 以串行方式通信。SPI控制器使LPC1700系列Cortex-M3能 与众多外设通信,从而大大增强了处理器的外设扩展能力。

从机选择 SSEL 串行时钟 SCK

LPC1700

MISO MOSI

主机输入从机输出 主机输出从机输入

SSEL:指示被选择参与数据传输的从机(低电平有效) MISO:单向信号线,数据通过它由从机传输到主机 MOSI:单向信号线,数据通过它由主机传输到从机 SCK:用于同步SPI接口间数据传输的时钟信号

总线空闲时, SCK为低电平

SCK

0 MOSI

1

0

1

0

1

0

1

SPI初始化 模式介绍 初始化| 初始化

CPOL=1 CPHA=0 模式三:SCK空闲时为高, SCK前沿采样 采样结果为:10101010b 从SCK的前沿 开始采样

总线空闲时, SCK为高电平

SCK

1 MOSI

0

1

0

1

0

1

0

SPI初始化 模式介绍 初始化| 初始化