PLDM8-2中文资料

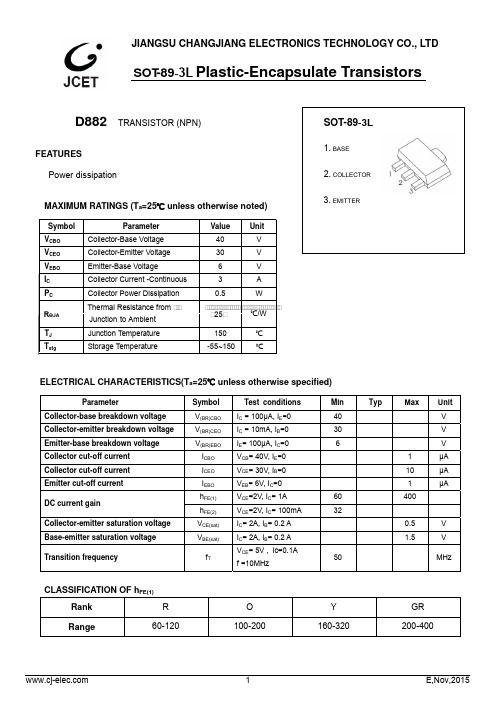

D882中文资料_数据手册_参数

Symbol VCBO VCEO VEBO IC PC

RӨJA

TJ Tstg

Parameter Collector-Base Voltage Collector-Emitter Voltage Emitter-Base Voltage Collector Current -Continuous Collector Power Dissipation Thermal Resistance from Junction to Ambient Junction Temperature Storage Temperature

Dimensions In Millimeters

Min

Max

1.400

1.600

0.320

0.520

0.400

0.580

0.350

0.440

4.400

4.600

1.550 REF.

2.300

2.600

3.940

4.250

1.500 TYP.

3.000 TYP.

0.900

1.200

Dimensions In Inches

O 100-200

Y 160-320

GR 200-400

1

EA,,NJouvn,,22001154

Typical Characteristics

Static Characteristic

2.00

COMMON EMITTER

1.75

10mA 9mA 8mA

T =25 ℃ a

COLLECTOR-EMITTER SATURATION

100

10

1 1

3000 1000

EP2C8Q208C8中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

Cyclone II器件手册,第1卷ii内容章修订日期............................................... ............................喜关于本手册............................................... .............................十三如何触点Altera ..........................................................................................................................十三印刷约定....................................................................................................................十三第一节Cyclone II器件系列数据表修订记录.................................................................................................................................... 1-1第1章简介简介............................................................................................................................................低成本嵌入式处理解决方案............................................ ......................................低成本DSP解决方案.................................................................................................................特征...................................................................................................................................................参考文献.........................................................................................................................文档修订历史记录.................................................................................................................1–1 1–1 1–1 1–2 1–9 1–9第2章Cyclone II架构功能说明.......................................................................................................................... 2-1逻辑元件....................................................................................................................................... 2-2LE操作模式........................................................................................................................ 2-4逻辑阵列模块................................................................................................................................ 2-7LAB互连............................................................................................................................ 2-8LAB控制信号......................................................................................................................... 2-8MultiTrack互联..................................................................................................................... 2-10行互连.......................................................................................................................... 2-10列互连.................................................................................................................... 2-12设备路由............................................................................................................................... 2-15全局时钟网络和锁相环.......................................... ..................................... 2-16专用时钟管脚..................................................................................................................... 2-20双用时钟引脚.............................................................................................................. 2-20全局时钟网络................................................................................................................... 2-21全局时钟网络分布.............................................. .............................................. 2-23锁相环.................................................................................................................................................. 2-25嵌入式存储器............................................................................................................................. 2-27内存模式............................................................................................................................... 2-30时钟模式.................................................................................................................................... 2-31M4K路由接口.................................................................................................................. 2-31iii内容嵌入式乘法器........................................................................................................................乘法器模式............................................................................................................................嵌入式乘法器路由接口.............................................. .......................................I / O结构及特点....................................................................................................................外部存储器接口.......................................................................................................可编程驱动强度.....................................................................................................漏极开路输出........................................................................................................................摆率控制...........................................................................................................................总线防护持..........................................................................................................................................可编程上拉电阻............................................. .................................................. ...高级I / O标准支持............................................ .................................................. ..高速差分接口............................................. .................................................系列片上端接.........................................................................................................I / O组........................................................................................................................................多电压I / O接口.................................................................................................................2–32 2–35 2–36 2–37 2–44 2–49 2–50 2–51 2–51 2–51 2–52 2–53 2–55 2–57 2–60第3章配置与测试IEEE标准. 1149.1(JTAG)边界扫描支持........................................... ..................................构造.........................................................................................................................................操作模式...................................................................................................................................配置计划......................................................................................................................... Cyclone II自动单粒子翻转检测........................................... ...........................定制电路....................................................................................................................软件界面.............................................................................................................................文档修订历史记录.................................................................................................................3–1 3–5 3–5 3–6 3–7 3–7 3–7 3–8第4章热插拔和上电复位简介............................................................................................................................................旋风II热插拔规格............................................ ................................................设备可以在电源时会驱动.......................................... ...........................................I / O引脚防护持三态电期间...................................... ......................................在Cyclone II器件热插拔功能实现......................................... ..............上电复位电路...................................................................................................................."唤醒"时间Cyclone II器件........................................ ...............................................结论..............................................................................................................................................文档修订历史记录.................................................................................................................4–1 4–1 4–2 4–2 4–3 4–5 4–5 4–7 4–7第5章直流特性和时序规范运行条件........................................................................................................................... 5-1单端I / O标准.......................................................................................................... 5-5差分I / O标准.............................................................................................................. 5-7DC特性不同针类型............................................ ......................................... 5-11片上端接规格............................................. .............................................. 5-12能量消耗........................................................................................................................... 5-13时序规格.......................................................................................................................... 5-14预,决赛时序规范............................................. ................................ 5-14演出.................................................................................................................................... 5-15 ivCyclone II器件手册,第1卷内容内部时序...............................................................................................................................Cyclone II时钟时序参数............................................. ..............................................时钟网络偏移加法器.......................................................................................................IOE可编程延迟.............................................................................................................不同I默认容性负载/ O标准......................................... .................I / O延迟.......................................................................................................................................最大输入和输出时钟频率............................................ ........................................高速I / O时序规格........................................... ............................................外部存储器接口规范.............................................. ....................................JTAG时序规范..........................................................................................................PLL时序规范............................................................................................................占空比失真.........................................................................................................................DCD测量技术............................................... .................................................. ..参考文献.......................................................................................................................文档修订历史记录...............................................................................................................5–18 5–23 5–29 5–30 5–31 5–33 5–46 5–55 5–63 5–64 5–66 5–67 5–68 5–74 5–74第6章参考和订购信息软体..................................................................................................................................................器件引脚输出.....................................................................................................................................订购信息...........................................................................................................................文档修订历史记录.................................................................................................................6–1 6–1 6–1 6–2第二节.时钟管理修订记录.................................................................................................................................... 6-1第7章锁相环在Cyclone II器件简介............................................................................................................................................ 7-1Cyclone II PLL硬件概述............................................. .................................................. ... 7-2PLL参考时钟产生.............................................. .................................................. ... 7-6时钟反馈模式....................................................................................................................... 7-10正常模式.................................................................................................................................. 7-10零延迟缓冲器模式................................................................................................................ 7-11无补偿模式............................................................................................................... 7-12源同步模式........................................................................................................... 7-13硬件特性.............................................................................................................................. 7-14时钟倍频和科.............................................. .................................................. .. 7-14可编程占空比........................................................................................................... 7-15移相实施.............................................. .................................................. .... 7-16控制信号................................................................................................................................ 7-17手动时钟切换............................................................................................................. 7-20时钟................................................................................................................................................ 7-21全局时钟网络................................................................................................................... 7-21时钟控制模块....................................................................................................................... 7-24全局时钟网络时钟源产生............................................ .......................... 7-26全局时钟网络掉电............................................. .............................................. 7-28vCyclone II器件手册,第1卷。

ASTMD882-02(中文)塑料薄板材抗拉特性的试验方法[1]

![ASTMD882-02(中文)塑料薄板材抗拉特性的试验方法[1]](https://img.taocdn.com/s3/m/6b515aec0342a8956bec0975f46527d3240ca6c3.png)

ASTMD882-02(中⽂)塑料薄板材抗拉特性的试验⽅法[1]ASTM D 882-02 : 测量塑料薄膜和薄⽚材拉伸性能测量塑料薄膜和薄⽚材拉伸性能的标准⽅法1. 测试应⽤范围1.1本测试⽤于测试塑料薄膜和⽚材(厚度⼩于1.0毫⽶)的拉伸性能。

注1——⽚材厚度⼩于0.25毫⽶(0.01英⼨)的即被定义为薄膜。

注2——厚度为1.0毫⽶(0.04英⼨)或者更厚⽚材的拉伸测试试验要根据D638进⾏。

1.2本测试应该被⽤来测试所有在所描述的厚度范围以内以及在要使试验机的负荷量程以内的全部塑料材料。

1.2.1静态过磅——恒定分离速率的夹具分离测试——在本⽅法中,夹具以恒定的速度抓住试样的⼀端将其分离。

1.3在这些测试⽅法中,测量试样的伸长可以从夹具分离距离、伸长指⽰器和标距线的位移得出。

1.4包括了在⼀个应变速率时测试拉伸弹性模量的步骤。

注3:模量的测量⼀般基于夹具分离的距离作为试样的伸长值。

然⽽,本标准也包括了使⽤如图5.2所述的伸长仪的情况。

1.5本测试所得的数据适⽤于⼯程设计或与其相关。

1.6 SI制单位即作为标准单位。

括号内的数值仅供参考。

1.7 本标准不适⽤于解决所相关的所有安全问题,仅涉及到它的应⽤。

建⽴相关的安全健康规则和使⽤前相关规定是使⽤者的责任。

规定2给出了相关的安全参考⽂献。

注4—本测试与ISO527-3类似,但在技术上⼆者并不能等同。

在ISO527-3中允许其他试样类型,特定的测试速度并要求使⽤伸长计或在试样上作测量标线。

2.参考⽂献2.1 ASTM标准D 618放置测试塑料的实施⽅法。

D 638测试塑料的拉伸⽅法。

D 4000塑料材料的分类⽅法。

E 4 试验机的负荷校正⽅法。

E 691 在实验室间进⾏测试精密度检测的⽅法。

2.2 ISO标准ISO527-3确定塑料的拉伸性质—第三部分:塑料薄膜和⽚材的测试条件。

3. 术语3.1定义——与塑料拉伸相关的术语或者符号在D 638的附件中。

PLG微型热敏打印机开发手册V1.3

PLG微型热敏打印机开发手册V1.3目录第一章概述----------------------------------------------------------------------------------------1第二章通讯接口-----------------------------------------------------------------------------------22.1RS-232接口--------------------------------------------------------------------------------22.2红外接口-----------------------------------------------------------------------------------3第三章指令说明------------------------------------------------------------------------------------43.1打印控制指令-----------------------------------------------------------------------------------53.1.1ESC@------------------------------------------------------------------------------------53.1.2LF---------------------------------------------------------------------------------------53.1.3CR---------------------------------------------------------------------------------------53.1.4FF---------------------------------------------------------------------------------------53.1.5ESC J n----------------------------------------------------------------------------------63.1.6ESC d n----------------------------------------------------------------------------------6 3.2字符参数设置指令-------------------------------------------------------------------------------63.2.1ESC!N----------------------------------------------------------------------------------63.2.2ESC M n----------------------------------------------------------------------------------73.2.3GS!n-----------------------------------------------------------------------------------73.2.4ESC-n----------------------------------------------------------------------------------83.2.5ESC E n----------------------------------------------------------------------------------83.2.6ESC G n----------------------------------------------------------------------------------83.2.7GS B n-----------------------------------------------------------------------------------8 3.3打印排版设置指令-------------------------------------------------------------------------------93.3.1ESC$nL nH------------------------------------------------------------------------------93.3.2ESC2------------------------------------------------------------------------------------93.3.3ESC3n----------------------------------------------------------------------------------93.3.4ESC\nL nH------------------------------------------------------------------------------93.3.5ESC SP n--------------------------------------------------------------------------------10 3.4图形打印指令----------------------------------------------------------------------------------103.4.1ESC*m nL nH d1…dk--------------------------------------------------------------------103.4.2GS'------------------------------------------------------------------------------------11 3.5条形码打印命令--------------------------------------------------------------------------------123.5.1GS k------------------------------------------------------------------------------------123.5.2GS h n----------------------------------------------------------------------------------123.5.3GS w n----------------------------------------------------------------------------------123.5.4GS H n----------------------------------------------------------------------------------133.5.5GS f n----------------------------------------------------------------------------------13 3.6汉字打印指令----------------------------------------------------------------------------------133.6.1FS&------------------------------------------------------------------------------------143.6.2FS.------------------------------------------------------------------------------------14附录----------------------------------------------------------------------------------------------15 A英文字符集-----------------------------------------------------------------------------15 B预印刷黑标说明-------------------------------------------------------------------------15第一章概述PLG微型热敏打印机是一款便携式热敏打印机,使用可充电电池供电,可带机充电,使用RS-232接口和IrDA红外接口,可用于各种仪器仪表、手持设备的数据打印。

得力 DL82、DZ82系列扫描仪用户手册 说明书

请将装置尽量靠近计算机,让接口数据线能够轻松地连接装置与计算 机。

请勿将装置或其电源适配器放置在下列环境中: 室外 靠近灰尘、水或热源 易受电击、震动、温度极高或极低、湿度高及阳光直射的位置

使用本装置时请保持手部干燥。避免造成电击伤害。 除非装置文件中另有明确说明,否则切勿自行拆卸或试图改装电源适配

保证

本书内容若有更动,本公司将不另行通知。 本公司对本文档内容不做任何保证,包括(并不限于)对某项特殊目的的适 用性的隐含保证。 对因此造成的错误,或因装修、效能或本产品使用上造成的不固定或严重 损害,本公司不负任何责任。

CCC_EMI 警告 警告: 在居住环境中,运行此设备可能会造成无线电干扰。 *本产品属于第一级 LED 产品。

5. 保养及维修扫描仪.................................................. 5-1

5.1 清理扫描仪玻璃镜片 ....................................... 5-1 5.2 清洁自动进纸装置 .......................................... 5-2 5.3 执行清洁模式 ............................................... 5-5 5.4 清洁超声波感应器 .......................................... 5-6 5.5 擦拭玻璃镜片 ............................................... 5-7 5.6 耗材更换 ..................................................... 5-8

2SD882;中文规格书,Datasheet资料

October 2007Rev 31/82SD882NPN medium power transistorFeatures■High current■Low saturation voltage ■Complement to 2SB772Applications■Voltage regulation ■Relay driver ■Generic switch ■Audio power amplifier ■DC-DC converterDescriptionThe device is a NPN transistor manufactured by using planar technology resulting in rugged high performance devices. The complementary PNP type is 2SB772.Table 1.Device summaryOrder code Marking Package Packing 2SD882D882SOT -32T ubeAbsolute maximum ratings2SD882 1 Absolute maximum ratingsTable 2.Absolute maximum ratingSymbol Parameter Value UnitV CBO Collector-base voltage (I E = 0) 60VV CEO Collector-emitter voltage (I B = 0) 30VV EBO Collector-base voltage (I C = 0) 5VI C Collector current3AI CM Collector peak current (t P < 5ms)6AI B Base current1AI BM Base peak current (t P < 5ms)2AP TOT T otal dissipation at T c = 25°C12.5WT STG Storage temperature-65 to 150°CT J Max. operating junction temperature150°CTable 3.Thermal dataSymbol Parameter Value UnitR thJ-case Thermal resistance junction-case max10°C/W 2/83/82 Electrical characteristics(T CASE = 25°C; unless otherwise specified)Table 4.Electrical characteristicsSymbol ParameterTest conditions Min.Typ.Max.Unit I CES Collector cut-off current(V BE = 0)V CE = 60 V 10µA I CEO Collector cut-off current (I B = 0)V CE = 30 V 100µA I EBOEmitter cut-off current (I C = 0)V EB = 5 V10µAV (BR)CEO(1)Collector-emitter breakdownvoltage (I B = 0 )I C = 10 mA 30VV (BR)CBO Collector-base breakdownvoltage(I E = 0 )I C = 100 µA60VV (BR)EBO Emitter-base breakdownvoltage(I C = 0 )I E = 100 µA5V V CE(sat)(1)Collector-emitter saturationvoltageI C = 1 A I B = 50 mAI C = 2 A I B = 100 mAI C = 3 A I B = 150 mA 0.40.71.1V V V V BE(sat)(1)1.Pulsed duration = 300 ms, duty cycle ≤1.5%.Base-emitter saturation voltage I C = 2 A I B = 100 mA 1.2Vh FE DC current gain I C = 100 mA V CE = 2 V I C = 1 A V CE = 2 V I C = 3 A V CE = 2 V 1008030300f TTransition frequencyI C = 0.1 A V CE = 10 V100MHzcharacteristics (curves) 2.1 Typical4/82SD882Package mechanical data 3 Package mechanical dataIn order to meet environmental requirements, ST offers these devices in ECOPACK®packages. These packages have a Lead-free second level interconnect . The category ofsecond level interconnect is marked on the package and on the inner box label, incompliance with JEDEC Standard JESD97. The maximum ratings related to solderingconditions are also marked on the inner box label. ECOPACK is an ST trademark.ECOPACK specifications are available at: 5/8Package mechanical data2SD8826/82SD882Revision history7/84 Revision historyTable 5.Document revision historyDate RevisionChanges09-Sep-20052Final datasheet. New template 02-Oct-20073Updated mechanical data2SD8828/8Please Read Carefully:Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.All ST products are sold pursuant to ST’s terms and conditions of sale.Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.UNLESS O THERWISE SET FO RTH IN ST’S TERMS AND CO NDITIO NS O F SALE ST DISCLAIMS ANY EXPRESS O R IMPLIED WARRANTY WITH RESPECT TO THE USE AND/O R SALE O F ST PRO DUCTS INCLUDING WITHO UT LIMITATIO N IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS EXPRESSLY APPRO VED IN WRITING BY AN AUTHO RIZED ST REPRESENTATIVE, ST PRO DUCTS ARE NO T RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.ST and the ST logo are trademarks or registered trademarks of ST in various countries.Information in this document supersedes and replaces all information previously supplied.The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.© 2007 STMicroelectronics - All rights reservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America分销商库存信息: STM2SD882。

三种车型VIN含义及常见车型代码

常见车型VIN含义及车型代码前言VIN(Vehicle Identification Number),中文名叫车辆识别代码, 是制造厂为了识别而给一辆车指定的一组字码。

SAE标准规定:VIN码由17位字符组成,所以俗称十七位码。

它包含了车辆的生产厂家、年代、车型、车身型式及代码、发动机代码及组装地点等信息。

正确解读VIN码,对于我们正确地识别车型,以致进行正确地诊断和维修都是十分重要的。

车辆识别代码经过排列组合,可以使同一车型的车在30年之内不会发生重号现象,具有对车辆的唯一识别性,因此可称为"汽车身份证"。

VIN的历史可以追溯到1949年。

但直到1981年之前,标准一直处于变换中。

比如:1965-1969年的VIN有9位,当生产量超过1百万之后采用10位;1970-1980年的VIN则固定为10位。

现行的17位汽车识别码始于1981年。

我国已于1996年底颁布了相关标准,并已于1997年开始实行。

实际操作中,1999年1月1日以后被初次登记的车辆必须拥有车辆识别代码。

VIN中不会包含 I、O、Q 三个英文字母。

从左到右数起,第十位编码为车辆出厂年月。

目录一、奔驰类1.1奔驰车型VIN含义:1.2奔驰车型VIN所在位置:1.3常见年份对照表:1.4奔驰车型常见发动机代码1.5奔驰变速箱型号含义:二、宝马类2.1宝马车型VIN含义:2.2宝马车型常见车型代码:2.3宝马车型VIN所在位置:2.4宝马变速箱型号含义:三、奥迪类3.1奥迪车型VIN含义:3.2奥迪车型常见车型代码:3.3奥迪车型VIN所在位置:3.4奥迪变速箱型号含义:1.1奔驰VIN含义WDB 220 167 1A326964WDB表示德国生产常用见生产地名代表WDB-West germany Daimler-Benz 德国WDC---M-Class Europe 欧洲产M-ClassWEB---EVOBUS Mercedes-Benz 奔驰-EVOBUSWKK---EVOBUS Setra Setra产的EVOBUS3AM---Mexico 墨西哥4JG----M-Class except Europe 欧洲外产M-Class8AB-Argentine 阿根廷8AC-Argentine 阿根廷9BM-Brazil 巴西ADB-South Africa 南非KPA---South Korea Transporter 韩国KPD--- South Korea 韩国KPG--- South Korea 韩国NMB---Turkey 土耳其V AG---G-Wagon Steyr Steyr产的G-ClassVF9---EVOBUS France 法国-EVOBUSVSA---Spain 西班牙LE4---China 中国WDB 220 167 1A326964220表示S-Class常用见级别所代表车型底盘号内部分组100-299 轿车;300-399卡车/公共汽车;400-499 专用车;600-699 卡车;700-799 主要部件WDB 220 167 1A3269640—Sedan1—LWB Sedan 加长2—Station Wagen 旅行车3---Coupe 双门运动型轿车4---Cabriolet/roadster 双门敞篷跑车5---Chassis with partial body 轿车底盘6--LWB Chassis with partial body加长轿车底盘7—Sports8—Pull manWDB 220 167 1A32696400-09 四缸柴油发动机04=E22010-19 五缸柴油发动机10=E25020-29 六缸柴油发动机20=E30030-49四缸汽油发动机35=E20050-69 六缸汽油发动机55=E320 63=S320 67=S35070-79 八---十二缸汽油发动机75=S60080-84 AWD 替代能源发动机85-99 Alternative propulsion替代能源动力WDB 220 167 1A3269641=左舵2=右舵WDB 220 167 1A326964A,B,C,D,E=Sindelfingen(新德芬根)F,G,H=Breman(布莱门)J=RastattWDB 220 167 1A326964326964装配出厂顺序号1. 2奔驰车架号VIN的位置1、行驶证2、前挡风玻璃左前下部3、诊断电脑、数据卡4、前乘客座椅底下,右后座椅下。

GAL16V8高性能E2CMOS PLD通用阵列逻辑说明书

I II I/O/QI/O/QI/O/Q I/O/Q I/O/Q I/CLKI I I I II I I GNDVcc I/O/QI/O/Q I/O/Q I/O/Q I/O/Q I/O/Q I/O/Q I/O/QI/OEPLCCDIPI/CLKII/O/QII/O/QII/O/QII/O/QII/O/QII/O/QII/O/QII/O/QI/OECopyright © 2004 Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.LATTICE SEMICONDUCTOR CORP ., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A.August 2004Tel. (503) 268-8000; 1-800-LATTICE; FAX (503) 268-8556; •HIGH PERFORMANCE E 2CMOS ® TECHNOLOGY —3.5 ns Maximum Propagation Delay —Fmax = 250 MHz—3.0 ns Maximum from Clock Input to Data Output —UltraMOS ® Advanced CMOS Technology•50% to 75% REDUCTION IN POWER FROM BIPOLAR —75mA Typ Icc on Low Power Device —45mA Typ Icc on Quarter Power Device •ACTIVE PULL-UPS ON ALL PINS•E 2CELL TECHNOLOGY —Reconfigurable Logic —Reprogrammable Cells —100% Tested/100% Yields—High Speed Electrical Erasure (<100ms)—20 Year Data Retention•EIGHT OUTPUT LOGIC MACROCELLS—Maximum Flexibility for Complex Logic Designs —Programmable Output Polarity—Also Emulates 20-pin PAL ® Devices with Full Function/Fuse Map/Parametric Compatibility •PRELOAD AND POWER-ON RESET OF ALL REGISTERS —100% Functional Testability •APPLICATIONS INCLUDE:—DMA Control—State Machine Control—High Speed Graphics Processing —Standard Logic Speed Upgrade•ELECTRONIC SIGNATURE FOR IDENTIFICATION •LEAD-FREE PACKAGE OPTIONSDescriptionThe GAL16V8, at 3.5 ns maximum propagation delay time, com-bines a high performance CMOS process with Electrically Eras-able (E 2) floating gate technology to provide the highest speed performance available in the PLD market. High speed erase times (<100ms) allow the devices to be reprogrammed quickly and ef-ficiently.The generic architecture provides maximum design flexibility by allowing the Output Logic Macrocell (OLMC) to be configured by the user. An important subset of the many architecture configura-tions possible with the GAL16V8 are the PAL architectures listed in the table of the macrocell description section. GAL16V8 devices are capable of emulating any of these PAL architectures with full function/fuse map/parametric compatibility.Unique test circuitry and reprogrammable cells allow complete AC,DC, and functional testing during manufacture. As a result, Lattice Semiconductor delivers 100% field programmability and function-ality of all GAL products. In addition, 100 erase/write cycles and data retention in excess of 20 years are specified.Pin ConfigurationI/CLKI I I I I I I I GNDVcc I/O/QI/O/Q I/O/Q I/O/Q I/O/Q I/O/Q I/O/Q I/O/QI/OE)s n (d p T )s n (u s T )s n (o c T )A m (c c I #g n i r e d r O eg a k c a P 5.35.20.3511J L 3-D 8V 61L A G C C L P d a e L -025345118V 61L A G 5-D J L C C L P d a e L -025.7751518V 61L A G 7-D LP P I D c i t s a l P n i P -021518V 61L A G 7-D J L C C L P d a e L -021518V 61L A G 7-D LS -02n i P C I O S 0101755P Q 01-D 8V 61L A G P I D c i t s a l P n i P -0255J Q 01-D 8V 61L A G C C L P d a e L -025118V 61L A G 01-D P L P I D c i t s a l P n i P -025118V 61L A G 01-D J L C C L P d a e L -025118V 61L A G 01-D LS n i P -02C I O S 51210155P Q 51-D 8V 61L A G P I D c i t s a l P n i P -0255J Q 51-D 8V 61L A G C C L P d a e L -0209P L 51-D 8V 61L A G P I D c i t s a l P n i P -0209L 51-D 8V 61L A G J d a e L -02C C L P 09L 51-D 8V 61L A G S C I O S n i P -025*******P Q 52-D 8V 61L A G P I D c i t s a l P n i P -0255J Q 52-D 8V 61L A G C C L P d a e L -0209P L 52-D 8V 61L A G P I D c i t s a l P n i P -0209L 52-D 8V 61L A G J C C L P d a e L -0209L 52-D 8V 61L A G S-02n i P CI O S )s n (d p T )s n (u s T )s n (o c T )A m (c c I #g n i r e d r O eg a k c a P 5.7750318V 61L A G 7-D I P L P I D c i t s a l P n i P -020318V 61L A G 7-D I J L C C L P d a e L -020********V 61L A G 01-D I P L P I D c i t s a l P n i P -020318V 61L A G 01-D I J L C C L P d a e L -025********I P L 51-D 8V 61L A G P I D c i t s a l P n i P -02031I J L 51-D 8V 61L A G C C L P d a e L -020*******I P Q 02-D 8V 61L A G P I D c i t s a l P n i P -0256I J Q 02-D 8V 61L A G C C L P d a e L -025*******I P Q 52-D 8V 61L A G P I D c i t s a l P n i P -0256I J Q 52-D 8V 61L A G C C L P d a e L -02031I P L 52-D 8V 61L A G P I D c i t s a l P n i P -02031IJ L 52-D 8V 61L A G CC L P d a e L -02Industrial Grade SpecificationsConventional PackagingCommercial Grade SpecificationsBlank = Commercial I = IndustrialGradePackage PowerL = Low Power Q = Quarter PowerSpeed (ns)XXXXXXXX XXX XX XDevice Name_P = Plastic DIPPN = Lead-free Plastic DIP J = PLCCJN = Lead-free PLCC S = SOICGAL16V8D Lead-Free PackagingCommercial Grade Specifications)s n (d p T )s n (u s T )s n (o c T )A m (c c I #g n i r e d r O eg a k c a P 5.35.20.3511N J L 3-D 8V 61L A G C C L P d a e L -02e e r F -d a e L 5345118V 61L A G 5-D J L N e e r F -d a e L C C L P d a e L -025.7751518V 61L A G 7-D L N P e e r F -d a e L P I D c i t s a l P n i P -021518V 61L A G 7-D J L N e e r F -d a e L C C L P d a e L -020101755N P Q 01-D 8V 61L A G P I D c i t s a l P n i P -02e e r F -d a e L 55N J Q 01-D 8V 61L A G C C L P d a e L -02e e r F -d a e L 5118V 61L A G 01-D P L N e e r F -d a e L P I D c i t s a l P n i P -025118V 61L A G 01-D J L N e e r F -d a e L C C L P d a e L -025*******P Q 51-D 8V 61L A G N e e r F -d a e L P I D c i t s a l P n i P -0255J Q 51-D 8V 61L A G N e e r F -d a e L C C L P d a e L -0209P L 51-D 8V 61L A G N e e r F -d a e L P I D c i t s a l P n i P -0209L 51-D 8V 61L A G N J e e r F -d a e L d a e L -02C C L P 52512155P Q 52-D 8V 61L A G N e e r F -d a e L P I D c i t s a l P n i P -0255J Q 52-D 8V 61L A G N e e r F -d a e L C C L P d a e L -0209P L 52-D 8V 61L A G N e e r F -d a e L P I D c i t s a l P n i P -0209L 52-D 8V 61L A G NJ e e r F -d a e L CC L P d a e L -02The following discussion pertains to configuring the output logicmacrocell. It should be noted that actual implementation is accom-plished by development software/hardware and is completely trans-parent to the user.There are three global OLMC configuration modes possible: simple, complex, and registered. Details of each of these modes are illustrated in the following pages. Two global bits, SYN and AC0, control the mode configuration for all macrocells. The XOR bit of each macrocell controls the polarity of the output in any of the three modes, while the AC1 bit of each of the macrocells controls the input/output configuration. These two global and 16 individ-ual architecture bits define all possible configurations in a GAL16V8 . The information given on these architecture bits is only to give a better understanding of the device. Compiler software will trans-parently set these architecture bits from the pin definitions, so the user should not need to directly manipulate these architecture bits. The following is a list of the PAL architectures that the GAL16V8 can emulate. It also shows the OLMC mode under which the GAL16V8 emulates the PAL architecture.PAL Architectures GAL16V8 Emulated by GAL16V8Global OLMC Mode 16R8Registered16R6Registered16R4Registered16RP8Registered16RP6Registered16RP4Registered16L8Complex16H8Complex16P8Complex10L8Simple12L6Simple14L4Simple16L2Simple10H8Simple12H6Simple14H4Simple16H2Simple10P8Simple12P6Simple14P4Simple16P2SimpleSoftware compilers support the three different global OLMC modes as different device types. These device types are listed in the table below. Most compilers have the ability to automatically select the device type, generally based on the register usage and output enable (OE) usage. Register usage on the device forces the soft-ware to choose the registered mode. All combinatorial outputs with OE controlled by the product term will force the software to choose the complex mode. The software will choose the simple mode only when all outputs are dedicated combinatorial without OE control. The different device types listed in the table can be used to override the automatic device selection by the software. For further details, refer to the compiler software manuals.When using compiler software to configure the device, the user must pay special attention to the following restrictions in each mode. In registered mode pin 1 and pin 11 are permanently configured as clock and output enable, respectively. These pins cannot be con-figured as dedicated inputs in the registered mode.In complex mode pin 1 and pin 11 become dedicated inputs and use the feedback paths of pin 19 and pin 12 respectively. Because of this feedback path usage, pin 19 and pin 12 do not have the feedback option in this mode.In simple mode all feedback paths of the output pins are routed via the adjacent pins. In doing so, the two inner most pins ( pins 15 and 16) will not have the feedback option as these pins are always configured as dedicated combinatorial output.Registered Complex Simple Auto Mode SelectABEL P16V8R P16V8C P16V8AS P16V8 CUPL G16V8MS G16V8MA G16V8AS G16V8LOG/iC GAL16V8_R GAL16V8_C7GAL16V8_C8GAL16V8 OrCAD-PLD"Registered"1"Complex"1"Simple"1GAL16V8A PLDesigner P16V8R2P16V8C2P16V8C2P16V8A TANGO-PLD G16V8R G16V8C G16V8AS3G16V81) Used with Configuration keyword.2) Prior to Version 2.0 support.3) Supported on Version 1.20 or later.V IL Input Low Voltage Vss – 0.5—0.8V V IH Input High Voltage2.0—Vcc+1V I IL 1Input or I/O Low Leakage Current 0V ≤ V IN ≤ V IL (MAX.)——–100µA I IH Input or I/O High Leakage Current3.5V ≤ V IN ≤ V CC——10µA V OL Output Low Voltage I OL = MAX. V in = V IL or V IH ——0.5V V OH Output High Voltage I OH = MAX. V in = V IL or V IH2.4——V I OLLow Level Output CurrentL-3/-5 & -7 (Ind. PLCC)——16mA L-7 (Except Ind. PLCC)/-10/-15/-25——24mAQ-10/-15/-20/-25I OH High Level Output Current ——–3.2mA I OS 2Output Short Circuit CurrentV CC = 5V V OUT = 0.5V T A = 25°C–30—–150mACommercial Devices:Ambient Temperature (T A )...............................0 to 75°C Supply voltage (V CC )with Respect to Ground .....................+4.75 to +5.25V Industrial Devices:Ambient Temperature (T A )...........................–40 to 85°C Supply voltage (V CC )with Respect to Ground .....................+4.50 to +5.50VSupply voltage V CC ......................................–0.5 to +7V Input voltage applied ..........................–2.5 to V CC +1.0V Off-state output voltage applied .........–2.5 to V CC +1.0V Storage Temperature ................................–65 to 150°C Ambient Temperature withPower Applied........................................–55 to 125°C1.Stresses above those listed under the “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress only ratings and functional operation of the device at these or at any other conditions above those indicated in the operational sections of this specification is not implied (while programming, follow the programming specifications).Over Recommended Operating Conditions (Unless Otherwise Specified)SYMBOLPARAMETER CONDITIONMIN.TYP .3MAX.UNITS COMMERCIAL I CC Operating PowerV IL = 0.5V V IH = 3.0V L -3/-5/-7/-10—75115mA Supply Currentf toggle = 15MHz Outputs OpenL-15/-25—7590mA Q-10/-15/-25—4555mAINDUSTRIAL I CC Operating PowerV IL = 0.5V V IH = 3.0V L -7/-10/-15/-25—75130mA Supply Currentf toggle = 15MHz Outputs OpenQ -20/-25—4565mA1) The leakage current is due to the internal pull-up resistor on all pins. See Input Buffer section for more information.2) One output at a time for a maximum duration of one second. Vout = 0.5V was selected to avoid test problems caused by tester ground degradation. Characterized but not 100% tested.3) Typical values are at Vcc = 5V and T A = 25 °Ct pd A Input or I/O to Comb. Output 1 3.51517.5ns t co A Clock to Output Delay 131415ns t cf 2—Clock to Feedback Delay— 2.5—3—3ns t su —Setup Time, Input or Feedback before Clock ↑ 2.5—3—5—ns t h—Hold Time, Input or Feedback after Clock ↑0——0—ns A Maximum Clock Frequency with 182—142.8—100—MHz External Feedback, 1/(tsu + tco)A Maximum Clock Frequency with 200—166—125—MHz Internal Feedback, 1/(tsu + tcf)AMaximum Clock Frequency with 250—166—125—MHz No Feedbackt wh —Clock Pulse Duration, High 2 4—3 4—4—ns t wl —Clock Pulse Duration, Low 2 4—3 4—4—ns t en B Input or I/O to Output Enabled — 4.51619ns B OE to Output Enabled — 4.51616ns t disC Input or I/O to Output Disabled — 4.51519ns COE to Output Disabled—4.51516ns-5 MIN.MAX.SYMBOLPARAMETER MAXIMUM*UNITS TEST CONDITIONS C I Input Capacitance 8pF V CC = 5.0V, V I = 2.0V C I/OI/O Capacitance8pFV CC = 5.0V, V I/O = 2.0V*Characterized but not 100% tested.Over Recommended Operating Conditions-7 MIN.MAX.UNITS PARAMETERTESTCOND 1.DESCRIPTIONCOM / INDCOM1) Refer to Switching Test Conditions section.2) Calculated from f max with internal feedback. Refer to fmax Descriptions section.3) Refer to fmax Descriptions section. Characterized but not 100% tested.4) Characterized but not 100% tested.f max 3-3 t pd A Input or I/O to Comb. Output 310315320325ns t co A Clock to Output Delay 27210211212ns t cf 2—Clock to Feedback Delay—6—8—9—10ns t su —Setup Time, Input or Fdbk before Clk ↑7.5—12—13—15—ns t h—Hold Time, Input or Fdbk after Clk ↑0—0—0—0—ns AMaximum Clock Frequency with 66.7—45.5—41.6—37—MHzExternal Feedback, 1/(tsu + tco)f max 3A Maximum Clock Frequency with 71.4—50—45.4—40—MHz Internal Feedback, 1/(tsu + tcf)AMaximum Clock Frequency with 83.3—62.5—50—41.6—MHz No Feedbackt wh —Clock Pulse Duration, High 6—8—10—12—ns t wl —Clock Pulse Duration, Low 6—8—10—12—ns t en B Input or I/O to Output Enabled 110—15—18—20ns B OE to Output Enabled 110—15—18—20ns t dis C Input or I/O to Output Disabled 110—15—18—20ns COE to Output Disabled110—15—18—20nsOver Recommended Operating ConditionsUNITS -25MIN.MAX.-20 MIN.MAX.-15 MIN.MAX.-10 MIN.MAX.PARAM.DESCRIPTIONTESTCOND 1.COM / INDCOM / INDINDCOM / INDSYMBOLPARAMETER MAXIMUM*UNITS TEST CONDITIONS C I Input Capacitance 8pF V CC = 5.0V, V I = 2.0V C I/OI/O Capacitance8pFV CC = 5.0V, V I/O = 2.0V*Characterized but not 100% tested.1) Refer to Switching Test Conditions section.2) Calculated from f max with internal feedback. Refer to fmax Descriptions section.3) Refer to fmax Descriptions section. Characterized but not 100% tested.Vol vs Iol00.20.40.610203040Iol (mA)V o l (V )Voh vs Ioh1234501020304050Ioh (mA)V o h (V )Voh vs Ioh33.23.43.63.8401234Ioh (mA)V o h (V )Normalized Icc vs Vcc0.80.911.11.24.504.755.00 5.25 5.50Supply Voltage (V)N o r m a l i z e d I c cNormalized Icc vs Temp0.70.80.911.11.21.3-55-25255075100125Temperature (deg. C)N o r m a l i z e d I c cNormalized Icc vs Freq.0.80.911.11.21.31.40255075100Frequency (MHz)N o r m a l i z e d I c cDelta Icc vs Vin (1 input)24680.511.522.533.54Vin (V)D e l t a I c c (m A )Input Clamp (Vik)0102030405060-2-1.5-1-0.5Vik (V)I i k (m A )。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

For other values & Custom Designs, contact factory.

Specifications subject to change without notice.

15801 Chemical Lane, Huntington Beach, CA 92649-1595

Tel: (714) 898-0960 • Fax: (714) 896-0971

PLDM 1/98

Rhombus

Industries Inc.

FAST / TTL Buffered I/O 4-Bit Programmable Delay Modules

GENERAL: For Operating Specifications and Test Conditions, see Tables I and VI on page 5 of this catalog. Delays specified for the Leading Edge. Buffered input and output.

Operating Temp. Range ...................................... 0O C to +70O C Temperature Coefficient ........................... < 500ppm/O C typical Minimum Input Pulse Width ............................ 40% max. Delay Supply Current, I CC ............................. 90 mA typ., 105 mA max

.300(7.62)

.600(15.24)

.300(7.62)

.800(20.32)

32

26

24

713

16

3

17

1819.500(12.70)

.600(15.24)

1.650 MAX (41.91) MAX

.030(0.76)TYP.

.050(1.27)TYP.

.295(7.49) .300(7.62)

.400(10.16) MAX.

.010(0.25) TYP. .100(2.54) TYP. .020(0.51) TYP. .120(3.05) MIN.

Dimensions in Inches (mm)

Electrical Specifications at 25O C

ENABLE input (Pin 15) is active low.Output will be disabled (remain low)when " E " is high.

Electrical Specifications at 25O C

4-Bit TTL Part Number Delay per Step (ns)Error ref.

to 0000(ns)Initial Delay (ns)Referenced to "0000" - Delay (ns) per Program Setting (P4*P3*P2*P1)

00000000000100100011010001010110011110001001101010111100110111101111PLDM15-1 1.0 ± 0.5± 1.0 15 ± 10.0 1.0 2.0 3.0 4.0 5.0 6.07.08.09.010.011.012.013.014.015.0PLDM15-2 2.0 ± 0.7± 1.5 15 ± 10.0 2.0 4.0 6.08.010.012.014.016.018.020.022.024.026.028.030.0PLDM15-5 5.0 ± 1.0± 3.0 15 ± 10.0 5.010.015.020.025.030.035.040.045.050.055.060.065.070.075.0PLDM15-1010 ± 1.5± 5.0 15 ± 10.010.020.030.040.050.060.070.080.090.0100.110.0120.0130.0140.0150.04-Bit FAST Part Number Delay per Step (ns)Error ref.

to 0000(ns)Initial Delay (ns)Referenced to "0000" - Delay (ns) per Program Setting (P4*P3*P2*P1)

00000000000100100011010001010110011110001001101010111100110111101111PLDM8-0.5 0.5 ± .25± 0.8 8 ± 10.00.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0 6.57.07.5PLDM8-1 1.0 ± 0.5± 1.0 8 ± 10.0 1.0 2.0 3.0 4.0 5.0 6.07.08.09.010.011.012.013.014.015.0PLDM8-1.5 1.5 ± 0.6± 1.5 8 ± 10.0 1.5 3.0 4.5 6.07.59.010.512.013.515.016.518.019.521.022.5PLDM8-2 2.0 ± 0.7± 1.5 8 ± 10.0 2.0 4.0 6.08.010.012.014.016.018.020.022.024.026.028.030.0PLDM8-2.5 2.5 ± 0.7± 1.5 8 ± 10.0 2.5 5.07.510.012.515.017.520.022.525.027.530.032.535.037.5PLDM8-3 3.0 ± 0.7± 2.0 8 ± 10.0 3.0 6.09.012.015.018.021.024.027.030.033.036.039.042.045.0PLDM8-3.5 3.5 ± 0.7± 2.5 8 ± 10.0 3.57.010.514.017.521.024.528.031.535.038.542.045.549.052.5PLDM8-4 4.0 ± 0.8± 3.0 8 ± 10.0 4.08.012.016.020.024.028.032.036.040.044.048.052.056.060.0PLDM8-4.5 4.5 ± 0.8± 3.0 8 ± 10.0 4.59.013.518.022.527.031.536.040.545.049.554.058.563.067.5PLDM8-5 5.0 ± 1.0± 3.0 8 ± 10.0 5.010.015.020.025.030.035.040.045.050.055.060.065.070.075.0PLDM8-1010 ± 1.5± 5.0 8 ± 10.010.020.030.040.050.060.070.080.090.0100.110.0120.0130.0140.0150.0FAST / TTL 4-Bit Schematic

CUMULATIVE TOLERANCES : "Error" Tolerance is for

Programmed Delays Referenced to Initial Delay, Setting "0000."For example, the setting "1111" delay of PLDM15-1 is 15.0 ± 1.0referenced to "0000," and 30.0 ± 2.0 referenced to the input.

P27GND

16P326

OUT

4-Bit Programmable

Delay Line Input Buffer Vcc 32

Vcc 3P113P424

17

18

19

IN

GND

15E

Output Buffer

25

元器件交易网。