P1727B-08ST中文资料

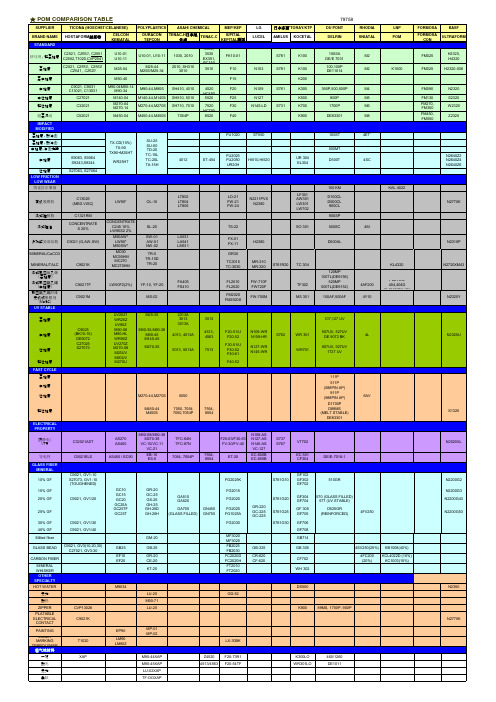

POM___代替品牌对照表

S737 S767

VT702 EC 501 CF304

N2520XL

DE/E-7018-1

FG2025K GR-20 GC-25 GS-25 GH-25 GH-25D GH-25H FG2015 GA510 GA520 GA705 (GLASS FILLED) FG2020 GN455 GN755 FG2025 FG1025A FG2030 MF3020 MF3025 FB2025 FB2030 FC2020D FC2020H FT2010 FT2020 GR-220 GC-225 GC-225

S761G1 0

GF102 GF302 GF702 GF304 GF704 GF 305 GF705 GF706 GF708 GB714

510GR

N2200G2 N2200G3

S761G2 0 S761G2 5 S761G3 0

570 (GLASS FILLED) D525GR (REINFORCED) 4FV250

100 KM D100CL D500CL 900CL 900SP 500SC 4SI

KAL 4022

有机脱模机

LW90*

OL-10

N2770K

添加硅树脂 添加硅油

多功能异常结构 MINERAL/CaC O3 MINERAL/TAL C 添加聚四 氟乙烯 (高粘度) 添加聚四氟乙烯 (中粘度) 聚四氟乙烯纤维 无机物脱模剂 (MoS2) UV STABLE 高粘度

DS500

N2350

K900

89MS, 1700P, 900P N2770K

MP-01 MP-02 LX-30BK

M90-44XAP M90-45XAP LU-02XAP TF-OOXAP AW,NW,SW, PW-01 XAP

上海百事电缆有限公司朗达自动闭路传动交流自动闸类型SNB DB27T5KN电视潜线类断网器说明书

B /l-"' A2 1'rTHIS COPY IS PROVIDED ON A RESTRICTED BASIS AND IS NOT TO BE USED IN ANY WAY DETRIMENTAL TO THE INTERESTS OF PANDUIT CORP.•g •1·,{ 1 I20A, SINGLE-POLEELECTRO MECHANICALSWITCH/ BREAKER (6)PL � 7B27 B37 B47 B57 B671:I•ol1·1·�·11·�·11·�·1! 18 !C:8 !£8 1·�·11·�·11·�·1!�8 !S8 !98REAR VIEW443.0[17.44]•IL 10 197.4[7.77]OJI• •TOP VIEW -lHJ481.0 SEE PLUG OPTIONS[18.94] �/SEE SHEET 2 FOR LOAD BANK DESIGNATIONS�1:=mB1� J I-� I-� 94�I-� I-� I ct> �!!a,! �I465.0I [18.31] IPLUG/RECEPTACLE BLOCK FRONT VIEWIEC 60309, 4P 5W, 6HIP67 (WATERTIGHT)30A, 346-415V MAXRATED INPUT24A DERATEDf3IEC 60309, 4P 5W, 6HIEC 60320/C19IP44 (SPLASHPROOF)30A, 346-415V MAX 16A, 250V MAXRATED INPUT RATED OUTPUT24A DERATEDNEMA L22-30P, 4P 5W30A, 277-480V MAXRATED INPUT24A DERATED01A 3/21/2019 WAC DACU JAWIREV DATE BY CHK APR2T 35.2I127.0 ---j 15.0FOR LENGTH I[1.39] I[5.00]®f-.[.59] ♦SEE SHEET 2PART NUMBERTABLE ]: ® I�19.; J [.76] SIDE VIEWRELEASED TO PRODUCTION P06BDESCRIPTION ECN'(71 IPANDUIT P/N WEIGHTI P06B##M-XXYZ SEE SHEET 2SPECIFICATION:1. STANDARDUNIT TYPE:ORIENTATION:OUTLET QTY & TYPEINPUT VOLTAGE:INPUT CURRENT:BREAKER QTY & TYPE:INPUT PHASE:RATED POWER:INPUT PLUGINPUT POWER CORD:BASICHORIZONTAL, 1USEE SHEET 2 FOR CONFIGURATIONS200-240/346-415VAC30A (24A DERATED)(6) 20A, SINGLE-POLETHREE-PHASE WYE17.3 kVASEE SHEET 2 FOR CONFIGURATIONSSEE SHEET 2FOR PART NUMBERTABLEREGULATORY STANDARD: RoHS COMPLIANT2. ADDITIONALCIRCUIT BREAKERS RATED AT 10kAIC3. ACCESSORIES:(1) QUICK-START GUIDENOTES:1. PRIMARY DIMENSIONS ARE IN MILLIMETERS. SECONDARYDIMENSIONS ARE IN IINCHES]2 .INSTALLATION SHALL COMPLY WITH ALL APPLICABLENATIONAL, STATE, AND LOCAL CODES3.VISIT OUR ON-LINE CATALOG AT FOR ACURRENT LIST OF PRODUCTS APPLICABLE FOR USE WITHTHIS PRODUCT4.FOR FULL PRODUCT FUNCTIONALITY REFER TO USER MANUAL5.DRAWING VIEWS SHOW THE INPUT CORD IN THE "FRONT FED"CONFIGURATIONIDENTIFICATIONFOR FINISHED GOOD PART NUMBER & DESCRIPTION TABLE SEESHEET 2 CONFIGURABLE PART NUMBERS: P06B##M -XXYZIXX: FINISHED GOOD COLORBL=BLACK YL=YELLOWRD=RED BU=BLUEWH =Wl-mE GN =GREENT1I r---Y: INPUT FEED TYPE Z: INPUT CORD LENGTH6=FRONT FEDA=1METERB=2METERC=3METERFOUR CHARACTER SUFFIX FOR AL TE RNA TEPRODUCT CONFIGURATIONSWE ASK THAT YOU CHECK FULLY THE SIGNDIMENSIONS, NOTES, AND SIGNTHE CLIENTSIGNATUTE BOX.THE JOB WILL NOT PROGRESS WITHOUT DATESIGNED APPROVAL. PLEASE DO NOT DELAYIN RETURNING PROOF AS IT WILL AFFECT PRINTDELIVERY.11 I LLINTELLIGENT SERIES POU" " N ''-P06B##M-XXYZCUSTOMER DRAWINGILL N..H RulDUITUNLESS OTHERWISE SPECIFIED,PIMENSIONAL TOLERANCES ARE: mm [IN]Tolerance (mm)D-@ THRIDANGLEPROJECTIONWWAC1I,,I''03/15/19 -O<LS50 I±0.550<LS250 ±1.0250<LS500 ±1.5SOO<L:S:1000 ±2.51000<LS2000 ±4.0I',,NTSw "'"'=-, ,_\!\"r, �-r, ._J f.i 1_r,P06B DCSHEET 1 OF 2 I a�Bh>A(6)C19。

MCP1727-ADJEMF系列规格书,Datasheet 资料

© 2007 Microchip Technology Inc.DS21999B-page 1MCP1727Features• 1.5A Output Current Capability•Input Operating Voltage Range: 2.3V to 6.0V •Adjustable Output Voltage Range: 0.8V to 5.0V •Standard Fixed Output Voltages:-0.8V, 1.2V, 1.8V, 2.5V, 3.0V, 3.3V, 5.0V•Other Fixed Output Voltage Options Available Upon Request•Low Dropout Voltage: 330mV Typical at 1.5A •Typical Output Voltage Tolerance: 0.5%•Stable with 1.0µF Ceramic Output Capacitor •Fast response to Load Transients •Low Supply Current: 120µA (typ)•Low Shutdown Supply Current: 0.1µA (typ)•Adjustable Delay on Power Good Output •Short Circuit Current Limiting and Overtemperature Protection•3x3 DFN-8 and SOIC-8 Package OptionsApplications•High-Speed Driver Chipset Power •Networking Backplane Cards •Notebook Computers •Network Interface Cards •Palmtop Computers •2.5V to 1.XV RegulatorsDescriptionThe MCP1727 is a 1.5A Low Dropout (LDO) linear regulator that provides high current and low output voltages in a very small package. The MCP1727comes in a fixed (or adjustable) output voltage version,with an output voltage range of 0.8V to 5.0V. The 1.5A output current capability, combined with the low output voltage capability, make the MCP1727 a good choice for new sub-1.8V output voltage LDO applications that have high current demands.The MCP1727 is stable using ceramic output capacitors that inherently provide lower output noise and reduce the size and cost of the entire regulator solution. Only 1µF of output capacitance is needed to stabilize the LDO.Using CMOS construction, the quiescent current consumed by the MCP1727 is typically less than 120µA over the entire input voltage range, making it attractive for portable computing applications that demand high output current. When shut down, the quiescent current is reduced to less than 0.1µA.The scaled-down output voltage is internally monitored and a power good (PWRGD) output is provided when the output is within 92% of regulation (typical). An external capacitor can be used on the C DELAY pin to adjust the delay from 200µs to 300ms.The overtemperature and short circuit current-limiting provide additional protection for the LDO during system fault conditions.Package TypesV IN V IN SHDN GND PWRGDC DELAYSenseV OUT V IN V IN SHDN GND PWRGDC DELAY ADJ V OUT Adjustable (SOIC-8)Fixed (SOIC-8)V IN V IN SHDN GND PWRGDC DELAY Sense V OUT 1122334455667788Fixed (3x3 DFN)V IN V IN SHDN GND PWRGDC DELAY V OUT Adjustable (3x3 DFN)ADJ 12345678123456781.5A, Low Voltage, Low Quiescent Current LDO RegulatorMCP1727DS21999B-page 2© 2007 Microchip Technology Inc.Typical ApplicationMCP1727 Adjustable Output VoltageV IN SHDN GNDPWRGD C DELAY ADJ V OUT 123456781µFPWRGDV OUT = 1.2V @ 1A 100k Ω4.7µFV IN = 2.3V to 2.8VOn OffV IN20k Ω40k ΩR 1R 2C 1C 2R 31000pFC 3MCP1727 Fixed Output VoltageV IN SHDN GNDPWRGD C DELAY Sense V OUT 12345678PWRGDV OUT = 1.8V @ 1AV IN = 2.3V to 2.8VOn OffV IN1µF100k Ω4.7µFC 1C 2R 11000pFC 3© 2007 Microchip Technology Inc.DS21999B-page 3MCP1727Functional Block Diagram - Adjustable OutputEA+–V OUTPMOSR fC f I SNSOvertemperature V REFComp92% of V REFT DELAYPWRGDC DELAY V INDriver w/limit and SHDNGNDSoft-StartADJUndervoltage Lock Out V INReferenceSHDNSHDN SHDN Sensing(UVLO)MCP1727DS21999B-page 4© 2007 Microchip Technology Inc.Functional Block Diagram - Fixed OutputEA+–V OUTPMOSR fC f I SNSOvertemperature V REFComp92% of V REFT DELAYPWRGDC DELAY V INDriver w/limit and SHDNGNDSoft-StartSenseUndervoltage Lock Out V INReferenceSHDNSHDN SHDN Sensing(UVLO)MCP17271.0ELECTRICALCHARACTERISTICSAbsolute Maximum Ratings †V IN....................................................................................6.5V Maximum Voltage on Any Pin..(GND – 0.3V) to (V DD + 0.3)V Maximum Power Dissipation.........Internally-Limited (Note6) Output Short Circuit Duration................................Continuous Storage temperature.....................................-65°C to +150°C Maximum Junction Temperature, T J...........................+150°C ESD protection on all pins (HBM/MM)........... ≥2kV;≥ 200V † Notice: Stresses above those listed under “Maximum Rat-ings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Expo-sure to maximum rating conditions for extended periods may affect device reliability.AC/DC CHARACTERISTICSElectrical Specifications: Unless otherwise noted, V IN = V OUT(MAX) + V DROPOUT(MAX)(Note1), V R=1.8V for Adjustable Output,I OUT = 1mA, C IN = C OUT = 4.7µF (X7R Ceramic), T A = +25°C.Boldface type applies for junction temperatures, T J (Note7) of -40°C to +125°CParameters Sym Min Typ Max Units ConditionsInput Operating Voltage V IN 2.3 6.0V Note1Input Quiescent Current I q—120220µA I L = 0mA, V IN = Note1,V OUT = 0.8V to 5.0VInput Quiescent Current forSHDN ModeI SHDN—0.13µA SHDN = GNDMaximum Output Current I OUT 1.5——A V IN = 2.3V to 6.0VV R = 0.8V to 5.0V, Note1Line RegulationΔV OUT/(V OUT x ΔV IN)—0.050.16%/V(Note1) ≤ V IN≤ 6VLoad RegulationΔV OUT/V OUT-1.0±0.5 1.0%I OUT = 1mA to 1.5A,V IN = Note1, (Note4)Output Short Circuit Current I OUT_SC— 2.2—A V IN = Note1, R LOAD<0.1Ω,Peak CurrentAdjust Pin Characteristics (Adjustable Output Only)Adjust Pin Reference Voltage V ADJ0.4020.4100.418V V IN = 2.3V to V IN=6.0V,I OUT = 1mAAdjust Pin Leakage Current I ADJ-10±0.01+10nA V IN = 6.0V, V ADJ=0V to6V Adjust Temperature Coefficient TCV OUT—40—ppm/°C Note3Fixed-Output Characteristics (Fixed Output Only)Voltage Regulation V OUT V R - 2.5%V R±0.5%V R + 2.5%V Note2Note1:The minimum V IN must meet two conditions: V IN ≥ 2.3V and V IN ≥ V OUT(MAX) + V DROPOUT(MAX).2:V R is the nominal regulator output voltage for the fixed cases. V R = 1.2V, 1.8V, etc. V R is the desired set point output voltage for the adjustable cases. V R = V ADJ* ((R1/R2)+1). Figure4-1.3:TCV OUT = (V OUT-HIGH – V OUT-LOW) *106 / (V R * ΔTemperature). V OUT-HIGH is the highest voltage measured over the temperature range. V OUT-LOW is the lowest voltage measured over the temperature range.4:Load regulation is measured at a constant junction temperature using low duty-cycle pulse testing. Load regulation is tested over a load range from 1mA to the maximum specified output current.5:Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its nominal value that was measured with an input voltage of V OUT = V R + V DROPOUT(MAX).6:The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air. (i.e., T A, T J, θJA). Exceeding the maximum allowable powerdissipation will cause the device operating junction temperature to exceed the maximum +150°C rating. Sustainedjunction temperatures above 150°C can impact device reliability.7:The junction temperature is approximated by soaking the device under test at an ambient temperature equal to the desired junction temperature. The test time is small enough such that the rise in the junction temperature over theambient temperature is not significant.© 2007 Microchip Technology Inc.DS21999B-page 5MCP1727DS21999B-page 6© 2007 Microchip Technology Inc.Dropout Characteristics Dropout VoltageV IN -V OUT—330550mVNote 5, I OUT = 1.5A, V IN(MIN)=2.3VPower Good Characteristics PWRGD Input Voltage Operat-ing RangeV PWRGD_VIN1.0— 6.0VT A = +25°C1.2— 6.0T A = -40°C to +125°C For V IN < 2.3V, I SINK =100µAPWRGD Threshold Voltage (Referenced to V OUT )V PWRGD_TH———%V OUTFalling Edge899295V OUT < 2.5V Fixed, V OUT = Adj.909294V OUT >= 2.5V FixedPWRGD Threshold Hysteresis V PWRGD_HYS 1.0 2.0 3.0%V OUTPWRGD Output Voltage Low V PWRGD_L —0.20.4V I PWRGD SINK = 1.2mA,ADJ = 0V, SENSE = 0V PWRGD Leakage P WRGD _LK—1—nAV PWRGD = V IN = 6.0V PWRGD Time DelayT PGRising EdgeR PULLUP = 10k ΩI CDELAY = 140nA (Typ)—200—µs C DELAY =OPEN 103055ms C DELAY =0.01µF —300—ms C DELAY =0.1µFDetect Threshold to PWRGD Active Time Delay T VDET-PWRGD—200—µsV ADJ or V SENSE = V PWRGD_TH + 20mV to V PWRGD_TH - 20mVShutdown Input Logic High Input V SHDN-HIGH 45%V IN V IN = 2.3V to 6.0V Logic Low InputV SHDN-LOW 15%V IN V IN = 2.3V to 6.0V SHDN Input Leakage Current SHDN ILK-0.1±0.001+0.1µAV IN =6V, SHDN =V IN ,SHDN = GNDAC Performance Output Delay From SHDN T OR100µsSHDN = GND to V IN V OUT = GND to 95% V RAC/DC CHARACTERISTICS (CONTINUED)Electrical Specifications: Unless otherwise noted, V IN = V OUT(MAX) + V DROPOUT(MAX) (Note 1), V R =1.8V for Adjustable Output, I OUT = 1mA, C IN = C OUT = 4.7µF (X7R Ceramic), T A = +25°C.Boldface type applies for junction temperatures, T J (Note 7) of -40°C to +125°CParametersSymMinTypMaxUnitsConditionsNote 1:The minimum V IN must meet two conditions: V IN ≥ 2.3V and V IN ≥ V OUT(MAX) + V DROPOUT(MAX).2:V R is the nominal regulator output voltage for the fixed cases. V R = 1.2V, 1.8V, etc. V R is the desired set point output voltage for the adjustable cases. V R = V ADJ * ((R 1/R 2)+1). Figure 4-1.3:TCV OUT = (V OUT-HIGH – V OUT-LOW ) *106 / (V R * ΔTemperature). V OUT-HIGH is the highest voltage measured over the temperature range. V OUT-LOW is the lowest voltage measured over the temperature range.4:Load regulation is measured at a constant junction temperature using low duty-cycle pulse testing. Load regulation is tested over a load range from 1mA to the maximum specified output current.5:Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its nominal value that was measured with an input voltage of V OUT = V R + V DROPOUT(MAX).6:The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junctiontemperature and the thermal resistance from junction to air. (i.e., T A , T J , θJA ). Exceeding the maximum allowable power dissipation will cause the device operating junction temperature to exceed the maximum +150°C rating. Sustained junction temperatures above 150°C can impact device reliability.7:The junction temperature is approximated by soaking the device under test at an ambient temperature equal to the desired junction temperature. The test time is small enough such that the rise in the junction temperature over the ambient temperature is not significant.© 2007 Microchip Technology Inc.DS21999B-page 7MCP1727TEMPERATURE SPECIFICATIONSOutput Noisee N—2.0—µV/√HzI OUT = 200mA, f = 1kHz, C OUT = 10µF (X7R Ceramic), V OUT = 2.5VPower Supply Ripple Rejection RatioPSRR —60—dBf = 100Hz, C OUT = 10µF,I OUT = 10mA,V INAC = 30mV pk-pk,C IN = 0µFThermal Shutdown Temperature T SD —150—°C I OUT = 100µA, V OUT = 1.8V, V IN = 2.8VThermal Shutdown Hysteresis ΔT SD—10—°CI OUT = 100µA, V OUT = 1.8V, V IN = 2.8VElectrical Specifications: Unless otherwise indicated, all limits apply for V IN = 2.3V to 6.0V.ParametersSymMinTypMaxUnitsConditionsTemperature RangesOperating Junction Temperature Range T J -40—+125°C Steady State Maximum Junction Temperature T J ——+150°C TransientStorage Temperature Range T A-65—+150°CThermal Package Resistances Thermal Resistance, 8LD 3x3 DFNθJA—41—°C/W4-Layer JC51-7Standard Board with viasThermal Resistance, 8LD SOICθJA—150—°C/W4-Layer JC51-7 Standard BoardAC/DC CHARACTERISTICS (CONTINUED)Electrical Specifications: Unless otherwise noted, V IN = V OUT(MAX) + V DROPOUT(MAX) (Note 1), V R =1.8V for Adjustable Output, I OUT = 1mA, C IN = C OUT = 4.7µF (X7R Ceramic), T A = +25°C.Boldface type applies for junction temperatures, T J (Note 7) of -40°C to +125°CParametersSym Min Typ Max Units ConditionsNote 1:The minimum V IN must meet two conditions: V IN ≥ 2.3V and V IN ≥ V OUT(MAX) + V DROPOUT(MAX).2:V R is the nominal regulator output voltage for the fixed cases. V R = 1.2V, 1.8V, etc. V R is the desired set point output voltage for the adjustable cases. V R = V ADJ * ((R 1/R 2)+1). Figure 4-1.3:TCV OUT = (V OUT-HIGH – V OUT-LOW ) *106 / (V R * ΔTemperature). V OUT-HIGH is the highest voltage measured over the temperature range. V OUT-LOW is the lowest voltage measured over the temperature range.4:Load regulation is measured at a constant junction temperature using low duty-cycle pulse testing. Load regulation is tested over a load range from 1mA to the maximum specified output current.5:Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its nominal value that was measured with an input voltage of V OUT = V R + V DROPOUT(MAX).6:The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junctiontemperature and the thermal resistance from junction to air. (i.e., T A , T J , θJA ). Exceeding the maximum allowable power dissipation will cause the device operating junction temperature to exceed the maximum +150°C rating. Sustained junction temperatures above 150°C can impact device reliability.7:The junction temperature is approximated by soaking the device under test at an ambient temperature equal to the desired junction temperature. The test time is small enough such that the rise in the junction temperature over the ambient temperature is not significant.MCP1727DS21999B-page 8© 2007 Microchip Technology Inc.2.0TYPICAL PERFORMANCE CURVESNOTE: Unless otherwise indicated V OUT = 1.8V (Adjustable), V IN = 2.8V, C OUT = 4.7µF Ceramic (X7R), C IN = 4.7µF Ceramic (X7R), I OUT = 1mA, Temperature = +25°C, V IN = V OUT + 0.6V, RPWRGD = 10k Ω To V IN .NOTE: Junction Temperature (T J ) is approximated by soaking the device under test to an ambient temperature equal to the desired Junction temperature. The test time is small enough such that the rise in Junction temperature over the Ambient temperature is not significant.FIGURE 2-1:Quiescent Current vs. Input Voltage (1.2V Adjustable).FIGURE 2-2:Ground Current vs. Load Current (1.2V Adjustable).FIGURE 2-3:Quiescent Current vs. Junction Temperature (1.2V Adjustable).FIGURE 2-4:Line Regulation vs. Temperature (1.2V Adjustable).FIGURE 2-5:Load Regulation vs.Temperature.FIGURE 2-6:Adjust Pin Voltage vs.Temperature.Note:The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.MCP1727 NOTE: Unless otherwise indicated V OUT = 1.8V (Adjustable), V IN = 2.8V, C OUT = 4.7µF Ceramic (X7R), C IN = 4.7µF Ceramic (X7R), I OUT = 1mA, Temperature = +25°C, V IN = V OUT + 0.6V, RPWRGD = 10kΩ To V IN.FIGURE 2-7:Dropout Voltage vs. Load Current (Adjustable Version).FIGURE 2-8:Dropout Voltage vs. Temperature (Adjustable Version).FIGURE 2-9:Power Good (PWRGD) Time Delay vs. Temperature.FIGURE 2-10:Quiescent Current vs. Input Voltage (0.8V Fixed).FIGURE 2-11:Quiescent Current vs. Input Voltage (2.5V Fixed).FIGURE 2-12:Ground Current vs. Load Current.© 2007 Microchip Technology Inc.DS21999B-page 9MCP1727DS21999B-page 10© 2007 Microchip Technology Inc.NOTE: Unless otherwise indicated V OUT = 1.8V (Adjustable), V IN = 2.8V, C OUT = 4.7µF Ceramic (X7R), C IN = 4.7µF Ceramic (X7R), I OUT = 1mA, Temperature = +25°C, V IN = V OUT + 0.6V, RPWRGD = 10k Ω To V IN .FIGURE 2-13:Quiescent Current vs.Temperature.FIGURE 2-14:I SHDN vs. Temperature.FIGURE 2-15:Line Regulation vs. Temperature (0.8V Fixed).FIGURE 2-16:Line Regulation vs. Temperature (2.5V Fixed).FIGURE 2-17:Load Regulation vs. Temperature (V OUT < 2.5V Fixed).FIGURE 2-18:Load Regulation vs. Temperature (V OUT ≥ 2.5V Fixed).NOTE: Unless otherwise indicated V OUT = 1.8V (Adjustable), V IN = 2.8V, C OUT = 4.7µF Ceramic (X7R), C IN = 4.7µF Ceramic (X7R), I OUT = 1mA, Temperature = +25°C, V IN = V OUT + 0.6V, RPWRGD = 10kΩ To V IN.FIGURE 2-19:Dropout Voltage vs. Load Current.FIGURE 2-20:Dropout Voltage vs. Temperature.FIGURE 2-21:Short Circuit Current vs. Input Voltage.FIGURE 2-22:Output Noise Voltage Density vs. Frequency.FIGURE 2-23:Power Supply Ripple Rejection (PSRR) vs. Frequency (V OUT = 1.2V Adj.).FIGURE 2-24:Power Supply Ripple Rejection (PSRR) vs. Frequency (V OUT = 1.2V Adj.).NOTE: Unless otherwise indicated V OUT = 1.8V (Adjustable), V IN = 2.8V, C OUT = 4.7µF Ceramic (X7R), C IN = 4.7µF Ceramic (X7R), I OUT = 1mA, Temperature = +25°C, V IN = V OUT + 0.6V, RPWRGD = 10kΩ To V IN.FIGURE 2-25:Power Supply Ripple Rejection (PSRR) vs. Frequency (V OUT = 2.5V Fixed).FIGURE 2-26:Power Supply Ripple Rejection (PSRR) vs. Frequency (V OUT = 2.5V Fixed).FIGURE 2-27: 2.5V (Fixed) Startup from V IN.FIGURE 2-28: 2.5V (Fixed) Startup from Shutdown.FIGURE 2-29:Power Good (PWRGD) Timing with C BYPASS of 1000pF.FIGURE 2-30:Power Good (PWRGD) Timing with C BYPASS of 0.1µF.NOTE: Unless otherwise indicated V OUT = 1.8V (Adjustable), V IN = 2.8V, C OUT = 4.7µF Ceramic (X7R), C IN = 4.7µF Ceramic (X7R), I OUT = 1mA, Temperature = +25°C, V IN = V OUT + 0.6V, RPWRGD = 10kΩ To V IN.FIGURE 2-31:Dynamic Line Response (0.8V Fixed).FIGURE 2-32:Dynamic Line Response (2.5V Fixed).FIGURE 2-33:Dynamic Load Response (2.5V Fixed, 10mA to 1000mA).FIGURE 2-34:Dynamic Load Response (2.5V Fixed, 100mA to 1000mA).3.0PIN DESCRIPTIONThe descriptions of the pins are listed in Table3-1. TABLE 3-1:PIN FUNCTION TABLE3.1Input Voltage Supply (V IN)Connect the unregulated or regulated input voltage source to V IN. If the input voltage source is located several inches away from the LDO, or the input source is a battery, it is recommended that an input capacitor be used. A typical input capacitance value of 1µF to 10µF should be sufficient for most applications.3.2Shutdown Control Input (SHDN) The SHDN input is used to turn the LDO output voltage on and off. When the SHDN input is at a logic-high level, the LDO output voltage is enabled. When the SHDN input is pulled to a logic-low level, the LDO output voltage is disabled. When the SHDN input is pulled low, the PWRGD output also goes low and the LDO enters a low quiescent current shutdown state where the typical quiescent current is 0.1µA.3.3Ground (GND)Connect the GND pin of the LDO to a quiet circuit ground. This will help the LDO power supply rejection ratio and noise performance. The ground pin of the LDO only conducts the quiescent current of the LDO (typically 120µA), so a heavy trace is not required. For applications have switching or noisy inputs tie the GND pin to the return of the output capacitor. Ground planes help lower inductance and voltage spikes caused by fast transient load currents and are recommended for applications that are subjected to fast load transients.3.4Power Good Output (PWRGD)The PWRGD output is an open-drain output used to indicate when the LDO output voltage is within 92% (typically) of its nominal regulation value. The PWRGD threshold has a typical hysteresis value of 2%. The PWRGD output is typically delayed by 200µs (typical, no capacitance on C DELAY pin) from the time the LDO output is within 92% + 3% (max hysteresis) of the regulated output value on power-up. This delay time is controlled by the C DELAY pin.3.5Power Good Delay Set-Point Input(C DELAY)The C DELAY input sets the power-up delay time for the PWRGD output. By connecting an external capacitor from the C DELAY pin to ground, the typical delay times for the PWRGD output can be adjusted from 200µs (no capacitance) to 300ms (0.1µF capacitor). This allows for the optimal setting of the system reset time.3.6Output Voltage Sense/Adjust Input(ADJ/Sense)3.6.1ADJFor adjustable applications, the output voltage is connected to the ADJ input through a resistor divider that sets the output voltage regulation value. This provides the user the capability to set the output voltage to any value they desire within the 0.8V to 5.0V range of the device.Fixed Output AdjustableOutputName Description11V IN Input Voltage Supply22V IN Input Voltage Supply33SHDN Shutdown Control Input (active-low)44GND Ground55PWRGD Power Good Output (open-drain)66C DELAY Power Good Delay Set-Point Input—7ADJ Voltage Sense Input (adjustable version)7—Sense Voltage Sense Input (fixed voltage version)88V OUT Regulated Output VoltageExposed Pad Exposed Pad EP Exposed Pad of the DFN Package (ground potential)3.6.2SenseFor fixed output voltage versions of the device, the SENSE input is used to provide output voltage feedback to the internal circuitry of the MCP1727. The SENSE pin typically improves load regulation by allowing the device to compensate for voltage drops due to packaging and circuit board layout.3.7Regulated Output Voltage (V OUT) The V OUT pin(s) is the regulated output voltage of the LDO. A minimum output capacitance of 1.0µF is required for LDO stability. The MCP1727 is stable with ceramic, tantalum and aluminum-electrolytic capacitors. See Section4.3 “Output Capacitor” for output capacitor selection guidance.3.8Exposed Pad (EP)The 3x3 DFN package has an exposed pad on the bottom of the package. This pad should be soldered to the Printed Circuit Board (PCB) to aid in the removal of heat from the package during operation. The exposed pad is at the ground potential of the LDO.4.0DEVICE OVERVIEWThe MCP1727 is a high output current, Low Dropout(LDO) voltage regulator with an adjustable delay power-good output and shutdown control input. The low dropout voltage of 330mV typical at 1.5A of current makes it ideal for battery-powered applications. Unlike other high output current LDOs, the MCP1727 only draws a maximum of 220µA of quiescent current.4.1LDO Output Voltage The MCP1727 LDO is available with either a fixed output voltage or an adjustable output voltage. The output voltage range is 0.8V to5.0V for both versions. 4.1.1ADJUST INPUTThe adjustable version of the MCP1727 uses the ADJ pin (pin 7) to get the output voltage feedback for output voltage regulation. This allows the user to set the output voltage of the device with two external resistors.The nominal voltage for ADJ is 0.41V.Figure 4-1 shows the adjustable version of the MCP1727. Resistors R 1 and R 2 form the resistor divider network necessary to set the output voltage.With this configuration, the equation for setting V OUT is:EQUATION 4-1:FIGURE 4-1:Typical adjustable output voltage application circuit.The allowable resistance value range for resistor R 2 is from 10k Ω to 200k Ω. Solving the equation for R 1yields the following equation:EQUATION 4-2:4.2Output Current and CurrentLimitingThe MCP1727 LDO is tested and ensured to supply a minimum of 1.5A of output current. The MCP1727 has no minimum output load, so the output load current can go to 0mA and the LDO will continue to regulate the output voltage to within tolerance.The MCP1727 also incorporates an output current limit.If the output voltage falls below 0.7V due to an overload condition (usually represents a shorted load condition),the output current is limited to 2.2A (typical). If the overload condition is a soft overload, the MCP1727 will supply higher load currents of up to 3A. The MCP1727should not be operated in this condition continuously as it may result in failure of the device. However, this does allow for device usage in applications that have higher pulsed load currents having an average output current value of 1.5A or less.Output overload conditions may also result in an over-temperature shutdown of the device. If the junction temperature rises above 150°C, the LDO will shutdown the output voltage. See Section 4.9 “Overtem-perature Protection” for more information on overtemperature shutdown.4.3Output CapacitorThe MCP1727 requires a minimum output capacitance of 1µF for output voltage stability. Ceramic capacitors are recommended because of their size, cost and environmental robustness qualities.Aluminum-electrolytic and tantalum capacitors can be used on the LDO output as well. The Equivalent Series Resistance (ESR) of the electrolytic output capacitor must be no greater than 1 ohm. The output capacitor should be located as close to the LDO output as is practical. Ceramic materials X7R and X5R have low temperature coefficients and are well within the acceptable ESR range required. A typical 1µF X7R 0805 capacitor has an ESR of 50 milli-ohms.Larger LDO output capacitors can be used with the MCP1727 to improve dynamic performance and power supply ripple rejection performance. A maximum of 22µF is recommended. Aluminum-electrolytic capacitors are not recommended for low-temperature applications of ≤ 25°C.V OUT V ADJ R 1R 2+R 2------------------⎝⎠⎛⎞=Where:V OUT =LDO Output VoltageV ADJ=ADJ PinVoltage(typically 0.41V)V IN SHDN GNDPWRGD C DELAY ADJ V OUT 123456781µFV OUT 4.7µF V INOn OffV IN R 1R 2C 1C21000pFC 3MCP1727-ADJR 1R 2V OUT V ADJ–V ADJ --------------------------------⎝⎠⎛⎞=Where:V OUT =LDO Output VoltageV ADJ=ADJ PinVoltage(typically 0.41V)4.4Input CapacitorLow input source impedance is necessary for the LDO output to operate properly. When operating from batteries, or in applications with long lead length (> 10 inches) between the input source and the LDO, some input capacitance is recommended. A minimum of 1.0µF to 4.7µF is recommended for most applications.For applications that have output step load requirements, the input capacitance of the LDO is very important. The input capacitance provides the LDO with a good local low-impedance source to pull the transient currents from in order to respond quickly to the output load step. For good step response performance, the input capacitor should be of equivalent (or higher) value than the output capacitor. The capacitor should be placed as close to the input of the LDO as is practical. Larger input capacitors will also help reduce any high-frequency noise on the input and output of the LDO and reduce the effects of any inductance that exists between the input source voltage and the input capacitance of the LDO.4.5Power Good Output (PWRGD)The PWRGD output is used to indicate when the output voltage of the LDO is within 92% (typical value, see Section1.0 “Electrical Characteristics” for Minimum and Maximum specifications) of its nominal regulation value.As the output voltage of the LDO rises, the PWRGD output will be held low until the output voltage has exceeded the power good threshold plus the hysteresis value. Once this threshold has been exceeded, the power good time delay is started (shown as T PG in the Electrical Characteristics table). The power good time delay is adjustable via the C DELAY pin of the LDO (see Section4.6 “C DELAY Input”). By placing a capacitor from the C DELAY pin to ground, the power good time delay can be adjusted from 200µs (no capacitance) to 300ms (0.1µF capacitor). After the time delay period, the PWRGD output will go high, indicating that the output voltage is stable and within regulation limits.If the output voltage of the LDO falls below the power good threshold, the power good output will transition low. The power good circuitry has a 170µs delay when detecting a falling output voltage, which helps to increase noise immunity of the power good output and avoid false triggering of the power good output during fast output transients. See Figure4-2 for power good timing characteristics.When the LDO is put into Shutdown mode using the SHDN input, the power good output is pulled low immediately, indicating that the output voltage will be out of regulation. The timing diagram for the power good output when using the shutdown input is shown in Figure4-3.The power good output is an open-drain output that canbe pulled up to any voltage that is equal to or less than the LDO input voltage. This output is capable of sinking 1.2mA (V PWRGD < 0.4V maximum).FIGURE 4-2:Power Good Timing. FIGURE 4-3:Power Good Timing fromShutdown.4.6C DELAY InputThe C DELAY input is used to provide the power-up delay timing for the power good output, as discussed in the previous section. By adding a capacitor from the C DELAY pin to ground, the PWRGD power-up time delay can be adjusted from 200µs (no capacitance on C DELAY) to 300ms (0.1µF of capacitance on C DELAY). See Section1.0 “Electrical Characteristics” for C DELAY timing tolerances.T PGT VDET_PWRGD V PWRGD_THV OUTPWRGDV OLV OHV INSHDNV OUT30µs70µsT ORPWRGDT PG。

苦参素的药理作用与临床应用

tr,2004;13(Supp l)B S1353王波,刘衡川.番石榴的降血糖作用研究.现代预防医学,2005;32 (10)B1293~12944Oh WK,L ee C H,Lee M S,et a.l Anti d i abeti c effects of extracts fro m Psi d i um guajava.J Ethnophar m aco,l2005;96(3)B411~4155Lu tterodt GD.Inhibiti on of gastro i ntes ti nal rel ease of acetylcholi n e by querceti n as a poss i b l e m ode of action of Psi d i um guajava leaf extracts i n the treat m en t of acute d iarrhoeal d isease.J E t hnophar m aco,l1989;25(3)B235 ~2476M oral esMA,T ortoriell o J,M eckes M,et a.l Calci um-antagon ist effect of querceti n and its relati on w i th t he s p as m olytic properti es of Psi d i um gua j ava L.A rch M ed Res,1994;25(1)B17~217Re L,Barocci S,Cap itan iC,et a.l E ffects of so m e n atural extracts on the acet y l choli ne rel ease at t h e m ou s e n euro m uscu l ar j unction.Phar m aco l Res, 1999;39(3)B239~2458程天印,朱深海,韦显凯,等.番石榴叶止泻机制的初步研究.畜牧与兽医,2005;37(2)B13~159A ri m a H,D anno G.Is o l ation of an ti m icrob ial co m pounds from guava (Psi d i um guaj ava L.)and t h ei r str u ctural el uci d ati on.Bi osciB i otechnol Bi o2 ch e m,2002;66(8)B1727~173010蔡玲斐,徐迎.番石榴叶提取物对常见细菌的体外抗菌作用.医药导报,2005;24(12)B1095~109711陈国宝,陈宝田,王沈歌,等.番石榴叶体内抗轮状病毒的实验研究.新中医,2003;35(12)B65~6712张文举,陈宝田,朱全红,等.石榴叶中提取的槲皮素和2-羟基熊果酸体外抗人轮状病毒作用.中草药,2005;36(1)B76~7913张学森,周迎春,吴依芬,等.番石榴叶治疗小儿诺瓦克样病毒性腹泻的临床观察.成都中医药大学学报,2006;29(3)B20~2114Conde Garci a EA,N asci m en t o VT,San tiago San t os AB,et a.l Inotropic effects of extracts of Psidi um guajava L.(gu ava)l eaves on t he gu i n ea p i g a2 tri u m.Braz JM ed Bi ol Res,2003;36(5)B661~66815O j e wole J A.H ypoglyce m ic and hypotensive effects of Psi d i um gua j ava L i nn.(M yrtaceae)l eaf aqu eous extract.M et hods Fi nd Exp Cli n Phar m aco l, 2005;27(10)B689~69516Ji m en ez-E scri g A,R i ncon M,Pu li do R,et a.l Gu ava fru it(Psidiu m gu aj ava L.)as a n e w sou rce of an ti oxi dan t d i etary fi b er.J Agric Food Che m, 2001;49(11)B5489~549317Tha i pong K,Boonp rakob U,C i sneros-Zevall os L,et a.l H yd roph ilic and lipoph ili c an ti ox i dant acti viti es of guava fru its.Southeast A si an J Trop M ed Pub licH ealt h,2005;36(Supp l4)B254~25718Q i an H,N i hori m bere V.An tioxidant power of phytoc h e m icals from Psidiu m guajava l ea.f J Zh eji ang U n i v Sc,i2004;5(6)B676-68319Ya m ash i ro S,Noguch iK,M atsuzak iT,et a.l Card i op rotecti ve effects of extracts fro m Ps i d i um guaj ava L and L i m on i um wri ghti,i Ok i na wan m ed ici nal p l ants,agai nst i sche m i a-reperfusion i n j u ry i n perfused rat hearts.Phar m a2 col ogy,2003;67(3)B128~13520R ah m atA,Abu BakarMF,Faez ah N,et a.l The effects of cons um pti on of guava(ps i d i um guajava)or papaya(cari ca papaya)on t otal anti ox i dan t and li p i d profil e i n nor m alm ale you t h.As i a Pac J C li n Nutr,2004;13(Sup2 p l)B10621H si eh C L,L i n YC,KoW S,et a.l Inh i b it ory effect of so m e selected nu2 traceutic h erbs on LDL glycati on i nduced by g l ucose and glyoxa.l J E t hno2 phar m aco,l2005;102(3)B357~36322M anosroi J,Dhum tano m P,M anosroi A,et a.l Anti-pro lif erative ac2 tivit y of ess en tial oil extract ed fro m Tha im ed ici nal plants on KB and P388 cell li n es.Can cer Lett,2006;235(1)B114~12023Seo N,Ito T,W ang N,et a.l An ti-allerg i c Psidiu m gu aj ava extracts exert an an titu m or effect by i nh i b ition ofT regu latory cells and res u ltan t aug2 m en t ati on ofTh1cells.Anticancer Res,2005;25(6A)B3763~377024裘宇容,王伟.肿瘤细胞多药耐药基因及产物p糖蛋白检测方法的研究进展.国外医学:临床生物化学与检验学分册,1999;20(5)B214~ 21525J unyaprasert VB,Soon t hornchareonnon N,Thongprad itchote S,et a.l Inh i b i tory effect of Thai p l ant extracts on P-glycoprotei n m ed i ated effl ux. Phytot h er R es,2006;20(1)B79~8126Shaheen HM,A li B H,A l qara w i AA,et a.l E ffect of Psi d i um guaj ava leaves on so m e aspects of t he central nervou s syste m i n m i ce.Phytot h er Res, 2000;14(2)B107~11127Jai arj P,Khoohas wan P,W ongk raj ang Y,et a.l Anti cough and anti m i2 crob ial acti viti es of Ps i d i um gu aj ava L i nn.leaf ex tract.J E thn ophar m aco,l 1999;67(2)B203~21228Roy CK,Ka m at h J V,Asad M,et a.l H epatop rot ecti ve acti v i ty ofPs i d i um guaj ava L i nn.l eaf extract.Ind ian J Exp Bi o,l2006;44(4)B305~311苦参素的药理作用与临床应用刘四海,戴华(解放军202医院药剂科,沈阳110003)苦参素是中药苦参中提取的有效成分,内含氧化苦参碱98%以上及少量氧化槐果碱。

PS12机芯培训课件

主要集成电路及功能介绍

主板 序 号 位号 型号 主要功能 在内部完成对各种信号的音视频解码处理,和不适合PDP电视显 示的各种格式转换。 DDR Flash,整机控制程序放置于其中 EEPROM(HDMI) EEPROM(VGA) 音频通道选择切换开关 输出模拟音频和视频信号 伴音功放

1

2 3 4 5 6 7 8

VGA信号输入接口电路

MST9X88L内部处理电路简介 TA、AV、Y/C、YPBPR、VGA、HDMI信号经 接口电路输入主芯片U9(MST9X88L)后, 在集成块内部完成A/D变换、切换、 同步 信号提取、数字降噪、去隔行处理、帧频 变换、图像时实缩放、彩色空间变换及色 彩、对比度调整、Gamma校正、屏显菜单 及TTL或LVDS信号形成。实现将不同的输 入格式变成统一的上屏信号格式。下图为 集成块内部电路框图(附文字说明)。

侧AV板

侧AV板用于AV音视频输入,S端子Y/C信号输入

按键K板组件 K板组件有7个功能按键。用户通过该组件可以 对PDP电视方便地进行操作。

屏组件 屏组件有电源板、扫描维持板、扫描缓冲板(上/下)、维持板、逻辑 控制板、逻辑驱动板、COF等组件。用以将来自主板经处理后的图像信号进行再处 理,转换成PDP显示屏所需要的信号,从而在屏上显示出图像。

侧AV及S端子Y/C信号输入电路

AV2及S端子Y/C信号输入电路

高清分量信号(YPBPR)输入

高清多媒体接口 (HDMI)输入

MST9X88有一路HDMI接收端口,同时 还兼容DVI/HDCP接收标准。 MST9X88可支持高达165MHZ的带宽, 完全符合HDMI 1.2的标准,最高可支 持1080P的输入,另外,采用差分信号 输入可支持长线功能,最多可支持长达 30M的长线,完全可以满足一般和特殊 用途要求。

大金空调P板 监控板 协议转换器 说明书

中百锐-接口板使用说明摘要:大金空调监控板远程控制面板智能家居机房P板协议转换器购买地址: /WyzFLJ一、历史版本V2.0—2004.V3.0—2009.V5.0—2013.V5.1—2013.二、外形结构图1.外形结构采用铝壳结构,带簧片螺钉紧固,9位5.08可拔插凤凰接线端子;2.外形图如下三、性能参数1.输入电源:对于硬件版本为2.0版输入电源为8-12V AC/DC;对于硬件版本为3.0以后输入电源为8-24V AC/DC[建议使用9V,800MA];2.通讯接口:可选择RS485方式和RS232方式,通过跳线或拨码设置,见安装说明。

四、安装说明1.接线端子定义2.接线方法①电源接入端为VIN1和VIN2,不分正负极性;②RS485连接端为RXD/B和TXD/A(通讯模式要设置为RS485模式);③RS232连接端为RXD/B、TXD/A及GND(通讯模式要设置为RS485模式);④空调连接端为对应的P1、P2。

3.通讯模式设定RS485方式的设定①版本为2.0和3.0设置方法:面对接线端,J4,J5短接左边两跳针(J4,J5皆为3针跳针,中间针为公共针);②版本为5.0设置方法:K1断开,S2置485,S1(蓝色自锁按键开关)弹起;③版本为5.1设置方法:S1置TB,S2置RS485。

RS232方式的设定①版本为2.0和3.0设置方法:面对接线端,J4,J5短接右边边两跳针(J4,J5皆为3针跳针,中间针为公共针);②版本为5.0设置方法:K1短接,S2置S232,S1(蓝色自锁按键开关)压下;③版本为5.1设置方法:S1置TA,S2置RS232。

4.注意事项:①电源接入端为VIN1和VIN2(不分正负极性),输入电源不得使用GND端子,GND端子是与主机通讯方式为RS232时使用的;②确保接线正确(接线端与定义连接一致,端子之间不能有短路,端子不能虚接)时才可通电测试;③通讯模式一定要设置正确,出厂默认设置为RS485方式;④本设备安装置干燥通风处,不得安装在潮湿或容易积水的位置。

类比推理在库仑定律建立中的作用_兼论类比推理的局限性

收稿日期: 2008 04 22; 修改日期: 2008 07 01 作者简介: 兰智高( 1968- ) , 男, 湖北武穴人, 黄冈师范学院物理科学 与技术学 院副教授, 华 中科技大 学在职 博士研 究

生, 主要研究方向为学科教学论、物理学史 . 通讯联系人: 万小龙( 1964- ) , 男, 江苏常州人, 华中科技大学哲学系教授, 博士, 主要研究方向为现代科 学哲学和量 子

第一个提出电作用力与距离平方成反比的是

英国 著 名的 物 理学 普 里斯 特 利 ( J ∃ P riest ley, 1733- 1804) [ 10] . 他在 1767 年发表的 电学的历 史和现状!被认为是 18 世纪最好的电学教材, 也

是科学史中的第一部电学史. 他总结了前人和他

那个时代的重要电学发现, 并与他本人的重要的 电学研究成果融汇在一起. 普里斯特利最重要的

成正比,

从而得到

F

%

1 r2

,

这样就证明了电吸引力

第 11 期

兰智高, 等: 类比推理在库仑定律建立中的 作用 兼论类比推理的局限性

39

也遵循距离平方反比的规律. 库仑在第二篇论文 的结论部分中将电作用力的定律总结为: ∀ 2 个带 电球, 以及 2 个带电分子间的电作用, 不论是排斥 力还是吸引力, 与 2 个带电分子的电流体密度的 积成正比, 而与距离平方成反比. #[ 10]

仪器, 却获得了相当可靠而且精确的结果. ∀ 他成

功的关键在于掌握了牛顿万有引力定律这一理论

武器, 通过数学处理, 将直接测量变为间接测量,

并且用上了示零法精确地判断结果, 从而得到了 电力的平方反比定律. #[ 12]

2. 3 库仑定律的建立 与其说是库仑发现了库仑定律, 还不如说是

P1727资料

ETAL and P1727 are Trade Marks of Profec Technologies Ltd. The Trade Mark ETAL is registered at the UK Trade Marks Registry.

Profec Technologies Ltd. is the owner of the design right under the Copyright Designs and Patents Act 1988 and no rights or licences are hereby granted or implied to any third party.

P1727 is certified to IEC 950, EN 60950, UL1950 and EN 41003. P1727 is a UL Recognized Component and is supported by a BABT Certificate of Recognition, a CSA Certificate of Compliance and an IEC CB Test Certificate.

January 2001

1537

Ω

-

160

mH

-

-

H

-

-

kΩ

ETALDOC 110/7

Page 2 of 4

January 2001

元器件交易网Equival Nhomakorabeant Circuit

Fig 1 LINE

CONSTRUCTION

P1727

Recommended Circuit

Fig 2

Through "loss" (including voltage ratio) 6.7dB plus less than 0.8dB excluding effect of any DC blocking capacitor. Response: ±0.3dB 200Hz - 4kHz

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Preliminary SpecificationP1727/66Low Power Notebook LCD Panel EMI Reduction ICFEATURES•FCC approved method of EMI attenuation•Generates a low EMI spread spectrum of the input clock frequency•Optimized for frequency range:P1727X: 20MHz to 40MHzP1766X: 40MHz to 80MHz•Internal loop filter minimizes external components and board space•8 different frequency deviations ranging from +/-0.625% to –3.50%•Low inherent cycle-to-cycle jitter• 3.3V operating voltage•CMOS/TTL compatible inputs and outputs•Ultra low power CMOS designTBD mA @3.3V, 54 MHzTBD mA @3.3V, 65 MHz•Supports notebook VGA and other LCD timing controller applications•Available in 8 pin SOIC and TSSOP•Qualified for Industrial Temp Spec. (+85C)PRODUCT DESCRIPTIONThe P1727/66 is a versatile spread spectrum frequency modulator designed specifically for a wide range of clock frequencies. The P1727/66 reduces electromagnetic interference (EMI) at the clock source, allowing system wide reduction of EMI of down stream (clock and data dependent signals). The P1727/66 allows significant system cost savings by reducing the number of circuit board layers and shielding that are traditionally required to pass EMI regulations.The P1727/66 modulates the output of a single PLL in order to “spread” the bandwidth of a synthesized clock, thereby decreasing the peak amplitudes of its harmonics. This results in significantly lower system EMI compared to the typical narrow band signal produced by oscillators and most clock generators. Lowering EMI by increasing a signal’s bandwidth is called “spread spectrum clock generation”.The P1727/66 uses the most efficient and optimized modulation profile approved by the FCC and is implemented by using a proprietary all-digital method.APPLICATIONSThe P1727/66 is targeted towards notebook LCD displays, other displays using an LVDS interface, PC peripheral devices, and embedded systems.Figure 1 – P1727/66 Pin DiagramCLKINVDDVSSFigure 2 – P1727/66 Block DiagramTable 1-Power Down SelectionPD# Spread Spectrum ModOut PLL ModeDown0 N/A Disabled Disabled Power1 ON Normal Normal NormalTable 2 Frequency Deviation SelectionP/N DeviationP/N DeviationP1727/66A -1.25% P1727/66E +/-0.625%P1727/66B -1,75% P1727/66F +/-0.875%P1727/66C -2.50% P1727/66G +/-1.25%P1727/66D -3.50% P1727/66H +/-1.75%PIN DESCRIPTIONPIN # Name Type Description1 CLKIN I Connect to externally generated clock signal.2 VDD P Connect to +3.3V3 VSS P Ground Connection. Connect to system ground.4 ModOut O Spread Spectrum Clock Output.output.5 REF I Referenceconnect6 N/C N/CNoconnectNo7 N/C N/C8 PD# I Pull low to enable Power Down Mode. This pin has an internal pull-upresistor.Figure 3 – P1727/66 Schematic for notebook VGA applicationABSOLUTE MAXIMUM RATINGSSymbol Parameter RatingUnit V DD, V IN Voltage on any pin with respect to GND -0.5 to +7.0 VT STG Storage Temperature -65 to +125 ºCT A Operating Temperature 0 to +70 ºCDC ELECTRICAL CHARACTERISTICSSymbol Parameter Min Typ Max UnitV IL Input Low Voltage GND – 0.3 - 0.8 VV IH Input High Voltage 2.0 - V DD + 0.3 VI IL Input Low Current (100 KΩ input pull-upresistor on inputs SR0, 1) - - -35µAI IH Input High Current (100 KΩ input pull-down resistor on input SSON) - - 35µAI XOL XOUT Output Low Current(@ 0.4V, V DD = 3.3V) - 3 -mAI XOH XOUT Output High Current(@ 2.5V, V DD = 3.3V) - 3 -mAV OL Output Low Voltage(V DD=3.3V, I OL = 20 mA) - - 0.4VV OH Output High Voltage(V DD=3.3V, I OH = 20 mA)2.5 - - VI DD Static Supply CurrentStandby Mode- TBD - mAI CC Dynamic Supply CurrentNormal Mode (3.3V and 10 pF loading) TBDf IN-minTBDf IN-typTBDf IN-maxmAV DD Operating Voltage TBD 3.3 TBD Vt ON Power Up Time(First locked clock cycle after power up)- 0.18 - mS Z OUT Clock Output Impedance - 50 - ΩAC ELECTRICAL CHARACTERISTICSSymbol Parameter Min Typ Max Unitf IN Input Frequency: P1727-XP1766-X 2040- 4080MHzt LH Note 1 Output Rise Time(measured at 0.8V to 2.0V)0.7 0.9 1.1 nst HL Note 1 Output Fall Time(measured at 2.0V to 0.8V)0.6 0.8 1.0 nst JC Jitter (cycle to cycle) - - TBD ps t D Output Duty Cycle 45 50 55 %Figure 6 – Mechanical Package Outline, (8 Pin SOIC)Figure 7 – Mechanical Package Outline, (8 Pin TSSOP)INCHES MILLIMETERS SYMBOLMIN NOR MAX MIN NOR MAX A 0.0570.0640.071 1.45 1.63 1.80 A1 0.0040.0070.010 0.10 0.18 0.25 A2 0.0530.0610.069 1.35 1.55 1.75 B 0.0120.0160.020 0.51 0.41 0.31 C 0.0040.0060.001 0.10 0.15 0.25 D 0.1860.1940.202 4.72 4.92 5.12 E 0.1480.1560.164 3.75 3.95 4.15e 0.050 BSC 1.27 BSCH 0.2240.2360.248 5.70 6.00 6.30 L 0.0120.0200.028 0.30 0.50 0.70 a 0° 5° 8° 0° 5° 8°INCHES MILLIMETERS SYMBOL MIN NOR MAX MIN NOR MAX A - - 0.047 - - 1.10 A1 0.002- 0.006 0.05 - 0.15 A2 0.0310.0390.041 0.80 1.00 1.05 B 0.007- 0.012 0.19 - 0.30 C 0.004- 0.008 0.09 - 0.20 D 0.1140.1180.122 2.90 3.00 3.10 E0.1690.1730.177 4.30 4.40 4.50e0.026 BSC 0.65 BSCH 0.2440.2520.260 6.20 6.40 6.60 L 0.0180.0240.030 0.45 0.60 0.75 a 0° - 8° 0° - 8°Ordering Information:I =Industrial Temperature Range (-25°C to 85°C)Example:ORDERING INFORMATIONOrdering Number Marking Package Type Qty. / Reel Temperature P1727/66X-08ST P1727/66X 8 PIN SOIC, TUBE 0°C TO 70°C P1727/66X-08SR P1727/66X 8 PIN SOIC, TAPE & REEL 2,500 0°C TO 70°C P1727/66X-08TT P1727/66X 8 PIN TSSOP, TUBE 0°C TO 70°C P1727/66X-08TR P1727/66X 8 PIN TSSOP, TAPE & REEL 2,500 0°C TO 70°C "Licensed under U.S. Patent Nos. 5,488,627 and 5,631,920"。