芯片AD1833A

常用dac芯片(CommonDACchip)

常用dac芯片(Common DAC chip)常用dac芯片 (转)Tda154014 bit DAC (Serial Output)Philips早期的cd使用的芯片, 1986年11月14日研发, 解析力一般, 音色温暖,28脚封装, 供电比较特殊 (+ 5V, - 5V, - 17V), i2s架构S / n 80dB 85dB / type / min后缀表示不同的封装模式Tda1540d14 bit DAC (Serial Output)Tda1540pn14 bit DAC (Serial Output)Tda1540td14 bit DAC (Serial Output)Tda1541Dual 16 bit DACPhilips最出名的dac芯片, 1985年11月研发, 韵味十足, 柔情似水, 人声出色, 个频段十分均衡耐听为philips打下了大大的疆土28脚封装, 供电 (+ 5, - 5, - 15), i2s架构, S / n 90dB / min / type 声道分离 80dB 95db后缀a是1541的升级版, s1表示精选Tda1541aHigh Performance Stereo 16 bit DACTda1541a / N2High Performance Stereo 16 bit DACTda1541a / N2 / R1High Performance Stereo 16 bit DACTda1541a / N2 / S1High Performance Stereo 16 bit DAC(关东: 至今还在一些dac内能见到身影, 经典程度可见一斑)Tda1543Dual 16 bit DAC Economy Version i2S Input formatPhilips为小型设备开发的芯片, 1991年2月研发解析力一般, 音色温暖, 中频迷人, 密度很厚度令人吃惊8脚封装 (t为16脚), 供电 + 5V, S / n 96dB 分离90dbTda1543tDual 16 bit DAC Economy Version i2S Input formatTda1545Stereo Continuous Calibration DAC第一款continuous Calibration DAC, 1993年3月研发 | 音色不明8脚封装 (att为14脚), 供电 + 5V, S / n 声道分离 95db 98Db Tda1545aStereo Continuous Calibration DACTda1545atStereo Continuous Calibration DACTda1545attStereo Continuous Calibration DACTda1547Dual Top Performance Bitstream DACPhilips为顶级音频设备开发的超级芯片, 1991年9月研发采用比特流技术的1比特dac,和他搭配的采用比特流技术的芯片saa7350, 他整合了三阶静噪和1比特dac两片芯片音色兼顾韵味和速度,收放自如, 频响宽广, 气势宏伟, 适合各种音乐32脚封装, 供电 (+ 5, - 3.5) S / N / a计权 113 dB THD 101db声道分离115dbAd Audio D / a convertersart #DNR (DAC DAC dB SNR (dB) THD + N @ 1 kHz (- 3dB) Product Description price * (1000 to 4999) functionAd1955 120 110 multibit Sigma Delta D / W / SACD playback $6.86 DAC(关东: 同为当今顶级dac之一的 "ad1955" 与bb顶旗舰 "PCM1792" 互有特色)Ad1853 116 117 - 104 24 bit 192kHz multibit Sigma Delta DAC current output DAC $7.59)Ad1852 114 114 104 stereo, 24 bit, 192 kHz multibit Sigma Delta D / a $5.57 (Voltage Output DACAd1854 112 113 97 complete single chip D / a $4.05 stereo audio DACAd1953 112 112 100 sigmadsp 3 CH, 26 / 48 bit D / a Processing $7.14 CCD, Signal ProcessorAd1954 112 112 100 sigmadsp 3 CH, 26 / 48 bit D / a Processing $7.14 CCD, Signal Processorad1933 110 110 96 192 khz, 24 bit codec w / pll $3.66 dacad1833a 110 110 95 multi ch, 24 bit 192 khz, sigma delta d / a $3.98 dacad1958 109, 108 96, stereo, 24 bit 192 khz multibit sigma delta d / w / pll * * dacad1934 108 108 96 192 khz, 24 bit codec w / pll, ci and spi. $3.15 dacad1851 96 110 90 16 - bits, 16 3 fs pcm audio dacs dual 5v supplies $4.71 dacad1857 94 - 90 stereo, single supply 16 / 18 / 20 bit sigma delta d / a * * dacad1859 94 - 88 stereo, single supply 18 - bit sigma delta d / a new $4.45 dacad1858 94 - 90 stereo, single supply 16 bit sigma delta d / a * * dacad1868 92 98 88 single supply dual 18 bit audio dac dac * *ad1866 90 95 86 single supply dual 16 bit audio dac $10.57 dac(关东: 原文对ad的dac介绍的很简单.)pcm1700dual 18 bit audio monolithic digital to analog converter1702的哥哥, 也是大名鼎鼎, 早起很多大牌的解码器都用他内含两个dac单元, 分别转换左右两个声道的信号, 易产生左右声道相互干扰, 是他差声的原因pcm1700pdual 18 bit audio monolithic digital to analog converterpcm1700p - jdual 18 bit audio monolithic digital to analog converterpcm1700p - kdual 18 bit audio monolithic digital to analog converterpcm1700udual 18 bit audio monolithic digital to analog converterpcm1700u - jdual 18 bit audio monolithic digital to analog converterpcm1700u - kdual 18 bit audio monolithic digital to analog converterpcm1702bicmos advanced sign magnitude 20 - bit digital to analog converter当年bb公司的顶级解码, 音质出众.pcm1702的并联应用被广泛使用在高档cd唱机和高档dac解码器中, 著名的音响公司accuphase (金嗓子) 曾将多片pcm1702并联用于一个声道解码, 结果得到一代精品cd机dp - 55pcm1702 - jbicmos advanced sign magnitude 20 - bit digital to analog converterpcm1702 - kbicmos advanced sign magnitude 20 - bit digital to analogconverterpcm1702pbicmos advanced sign magnitude 20 - bit digital to analog converterpcm1702ubicmos advanced sign magnitude 20 - bit digital to analog converter(关东: 很多老烧友当年的梦中情人.多阶20bit的高转换精度也同时带来了高昂的成本)pcm170424 bit, 96khz bicmos sign - magnitude digital to analog converter1702的升级版, 速度, 频响, 声场都非常出色pcm1704u24 bit, 96khz bicmos sign - magnitude digital to analog converter(关东: 作为bb顶级dac "pcm1702" 的继任者, 老骥伏枥的"pcm1704" 仍然在很多机器中续写着hifi神话)pcm1710stereo audio digital to analog convertervcd里用的最多, 我就不说了pcm1710ustereo audio digital to analog converter(Kanto: when I just appeared, I also polished CD with finished boards, and the quality of the equivalent multi - grade 20Bit accuracy at that time has made me sit up and take notice.)PCM1715DUAL, VOLTAGE, OUTPUT, CMOS, DELTA-SIGMA, DIGITAL-TO-ANALOG, CONVERTER, WITH, ON-CHIP,, DIGITAL, FILTER, PCM1715UDUAL, VOLTAGE, OUTPUT, CMOS, DELTA-SIGMA, DIGITAL-TO-ANALOG, CONVERTER, WITH(Kanto: also appeared in many VCD)PCM171624-BIT, 96KHZ, SAMPLING, CMOS, DELTA-SIGMA, STEREO, AUDIO, CONVERTER, DIGITAL-TO-ANALOGWarm type, some DVD use him(Kanto: warm tone of a DAC, equivalent multi-level conversion,accuracy of 24Bit/96KHz, cost-effective. The 420 year old CD, who used it after DIY, is still serving himselfPCM1720STEREO, AUDIO, DIGITAL-TO-ANALOG, CONVERTER, MPEG2/AC-3, COMPATIBLEChips used in DVDPCM173024-BIT, 192-KHZ, SAMPLING, ADVANCED, SEGMENT, AUDIO, STEREO, DIGITAL-TO-ANALOG, CONVERTERPCM1730E24-BIT, 192-KHZ, SAMPLING, ADVANCED, SEGMENT, AUDIO, STEREO, DIGITAL-TO-ANALOG, CONVERTER, PCM1730E/2K24-BIT, 192-KHZ, SAMPLING, ADVANCED, SEGMENT, AUDIO, STEREO, DIGITAL-TO-ANALOG, CONVERTERPCM173224-BIT, 96KHZ, STEREO, AUDIO, DIGITAL-TO-ANALOG, CONVERTER, WITH, DECODER, HDCDWith HDCD, a lot of CD and DVD use him(Kanto: many domestic products have adopted the CD)PCM1733STEREO, AUDIO, DIGITAL-TO-ANALOG, CONVERTER, 18, BITS, 96KHZ, SAMPLINGA simplified version of 1732PCM173824-BIT, 192KHZ, SAMPLING, ADVANCED, SEGMENT, AUDIO-STEREO, DIGITAL-TO-ANALOG, CONVERTERHigh quality DAC, DSD and PCM dual function chips, are often used in advanced decodersPCM1738E24-BIT, 192KHZ, SAMPLING, ADVANCED, SEGMENT, AUDIO-STEREO, DIGITAL-TO-ANALOG, CONVERTER, PCM1738E2K24-BIT, 192KHZ, SAMPLING, ADVANCED, SEGMENT, AUDIO-STEREO, DIGITAL-TO-ANALOG, CONVERTERPCM173924-BIT, 192KHZ, SAMPLING, ENHANCED, MULTI-LEVEL, DELTA-SIGMA, AUDIO, DIGITAL-TO-ANALOG, CONVERTERPCM1739E24-BIT, 192KHZ, SAMPLING, ENHANCED, MULTI-LEVEL, DELTA-SIGMA, AUDIO, DIGITAL-TO-ANALOG, CONVERTERPCM1792BIT, 192KHZ, SAMPLING, ADVANCED, SEGMENT, AUDIO, STEREO, DIGITAL,, TO, ANALOG, CONVERTERBB's strongest DAC chip today uses hardware and software control, superior quality, and unmatched metrics, which are used in advanced SACD decoding, PCM1792DBBIT, 192KHZ, SAMPLING, ADVANCED, SEGMENT, AUDIO, STEREO, DIGITAL,, TO, ANALOG, CONVERTERPCM1792DBRBIT, 192KHZ, SAMPLING, ADVANCED, SEGMENT, AUDIO, STEREO, DIGITAL,, TO, ANALOG, CONVERTER(Kanto wine: pursue the past, yesterday fragrant far to [PCM1702]; the whole night long memories, Qin Yun [PCM1704]! Is the flagship PCM1792 of BB now capable of writing its predecessors?PCM1793The "BIT 192KHZ SAMPLING ADVANCED SEGMENT AUDIO STEREO DIGITAL TO ANALOG CONVERTER"It's also a very NB chipPCM1793DBThe "BIT 192KHZ SAMPLING ADVANCED SEGMENT AUDIO STEREO DIGITAL TO ANALOG CONVERTER"PCM1793DBR24位192kHz采样先进的部分音频立体声数字模拟转换器pcm179424位192kHz的采样,先进的部分,音频立体声数字模拟转换器1792的简化版本,音质据说比1792差那么一点点pcm1794db24位192kHz的采样,先进的部分,音频立体声数字模拟转换器pcm1794dbr24位192kHz的采样,先进的部分,音频立体声数字模拟转换器pcm179624bit 192 kHz的采样先进的部分音频立体声数字模拟转换器pcm1796db24bit 192 kHz的采样先进的部分音频立体声数字模拟转换器PCM1796DBR24bit 192 kHz的采样先进的部分音频立体声数字模拟转换器pcm179824位,192-khz采样先进的部分,音频立体声数字模拟转换器1792和1794的简化版本,只支持硬件控制,音质在三兄弟里最差,虽然最差但也比一般的好上不少,谁叫它是旗舰呢pcm1798db24位,192-khz采样先进的部分,音频立体声数字模拟转换器pcm1798dbr24位,192-khz采样先进的部分,音频立体声数字模拟转换器pcm2702与16位立体数位类比转换器接口USB类的DAC芯片,可被电脑直接识别,USB解码器的首选,但受到电脑的电波干扰,抖动问题等的影响,音质无法和上面那些专业的比,但非常适合我们DIY们,没有别的,就因为他简单pcm2702e与16位立体数位类比转换器接口pcm2704立体声音频DAC与U##接口,单端耳机输出的PDF输出pcm2704db立体声音频DAC与U##接口,单端耳机输出的PDF输出pcm2704dbr 立体声音频DAC与U##接口,单端耳机输出的PDF输出pcm2705立体声音频DAC与U##接口,单端耳机输出的PDF输出pcm2705db 立体声音频DAC与U##接口,单端耳机输出的PDF输出pcm2705dbr 立体声音频DAC与U##接口,单端耳机输出的PDF输出pcm2706立体声音频DAC与U##接口,单端耳机输出的PDF输出PCM2706PJT 立体声音频DAC与U##接口,单端耳机输出的PDF输出pcm2706pjtr 立体声音频DAC与U##接口,单端耳机输出的PDF输出pcm2707立体声音频DAC与U##接口,单端耳机输出的PDF输出PCM2707PJT 立体声音频DAC与U##接口,单端耳机输出的PDF输出pcm2707pjtrstereo audio dac with u## interface, single ended headphone output and s / pdf outputstereo audio codec with u## interface, single ended analog input / output and s / pdifpcm2900estereo audio codec with u## interface, single ended analog input / output and s / pdif pcm2900e / 2kstereo audio codec with u## interface, single ended analog input / output and s / pdifpcm2901stereo audio codec with u## interface single ended analog input / output and s / p difpcm2901estereo audio codec with u## interface single ended analog input / output and s / p dif pcm2901e / 2kstereo audio codec with u## interface single ended analog input / output and s / p difpcm2902stereo audio codec with u## interface, single ended analog input / output and s / pdifstereo audio codec with u## interface, single ended analog input / output and s / pdif pcm2902e / 2kstereo audio codec with u## interface, single ended analog input / output and s / pdifpcm5416 bit digital to analog converter monolithic音质一般, 体积庞大, 样子挺yy但素质不高, 早期的日本顶级cd喜欢用他, 音色温暖, 解析力不好, 声音较粗 (别拍我...)pcm54hp16 bit digital to analog converter monolithicpcm54jp16 bit digital to analog converter monolithicpcm54kp16 bit digital to analog converter monolithicpcm5516 bit digital to analog converter monolithic16 bit digital to analog converter monolithicpcm55jp16 bit digital to analog converter monolithicpcm56serial input 16 bit digital to analog converter monolithic小巧精干, 声音不错, 声场解析力较好, 但数码味较重, 声音较硬, 是bb早期最成功的作品之一pcm56pserial input 16 bit digital to analog converter monolithic pcm56p - jserial input 16 bit digital to analog converter monolithic pcm56p - kserial input 16 bit digital to analog converter monolithic pcm56p - lserial input 16 bit digital to analog converter monolithicserial input 16 bit digital to analog converter monolithicpcm58jprecision, 18 bit monolithic audio digital to analog converter音色厚实甜美, 解析声场在同级产品中十分出众, 现在也有很多dac 产品还在用他, 但停产多时, 价格较高pcm58kprecision, 18 bit monolithic audio digital to analog converter pcm58pprecision, 18 bit monolithic audio digital to analog converter pcm61serial input 16 bit monolithic audio digital to analog converter很多性价比较高的老cd都用他, 音色平衡, 也是经典芯片pcm61j - p串行输入18位单片音频数位类比转换器pcm61k串行输入18位单片音频数位类比转换器pcm61p串行输入18位单片音频数位类比转换器pcm61p-p串行输入18位单片音频数位类比转换器pcm63共线⒙20位单片音频数位类比转换器超铌的芯片,声音出色,甜美厚实,解析力强,声场宏伟,但低频锻相对较瘦,高档解码器的宠儿,浓郁的王者气魄,但价格太高,只能YYpcm63p共线⒙20位单片音频数位类比转换器pcm63p-j共线⒙20位单片音频数位类比转换器pcm63p-k共线⒙20位单片音频数位类比转换器并联使用DAC可提高等效比特数,提高转换精度,效果相当显著,最直接的感觉就是音乐的厚度感和力度感在高档机中应用比较广泛并联使用DAC。

常用AD芯片介绍

常用AD芯片介绍AD芯片是指模数转换芯片(Analog-to-Digital Converter),主要用于将模拟信号转换为数字信号。

它在现代电子设备中扮演着极为重要的角色,并广泛应用于通信、医疗、工业控制、汽车电子以及消费电子等领域。

下面将介绍几种常用的AD芯片。

1.AD7780:AD7780是一款高精度、低功耗的24位模数转换器。

它具有灵活的配置选项,可用于多种测量应用,如温度、压力、力量和湿度传感器。

AD7780能够提供高达23.8位的有效分辨率,具有低噪声和低漂移性能。

该芯片还提供了多种接口选项,如SPI接口和串行接口数据格式,以满足不同系统的需要。

2.AD7671:AD7671是一款12位的高速模数转换器。

它具有高采样率和低功耗的特点,能够提供高达1MSPS的转换速率。

AD7671还具有低失真、高信噪比和快速响应等优点,适用于高速数据采集和信号处理应用。

该芯片还提供了多种输入范围和接口选项,以满足不同应用场景的需求。

3.AD7903:AD7903是一款8位的高速模数转换器。

它具有高速采样率和低功耗的特点,能够提供高达20MSPS的转换速率。

AD7903还具有低功耗和小封装等优点,适用于便携式和嵌入式应用。

该芯片还配备了内部参考电压和自校准电路,提高了转换的精度和稳定性。

4.AD7175-2:AD7175-2是一款高精度、低功耗的24位模数转换器。

它具有内置低噪声放大器和可编程增益放大器,能够适应不同信号强度的测量需求。

AD7175-2具有极低的失真和漂移性能,能够提供高达23.8位的有效分辨率。

该芯片还支持多种接口选项,如SPI接口和I²C接口,以方便与其他外围设备的连接。

5.AD7760:AD7760是一款高精度、低功耗的24位模数转换器。

它能够提供高达256kSPS的转换速率,并具有低噪声和低漂移性能。

AD7760还具有自动校准和过采样滤波器等功能,提高了转换的精度和稳定性。

常用DAC芯片

常用DAC芯片(转)TDA154014-BIT DAC (SERIAL OUTPUT)Philips早期的cd使用的芯片,1986年11月14日研发,解析力一般,音色温暖,28脚封装,供电比较特殊(+5v,-5v,-17v),I2S架构S/N 80dB/min 85dB/Type后缀表示不同的封装模式TDA1540D14-BIT DAC (SERIAL OUTPUT)TDA1540PN14-BIT DAC (SERIAL OUTPUT)TDA1540TD14-BIT DAC (SERIAL OUTPUT)TDA1541DUAL 16-BIT DACPhilips最出名的dac芯片,1985年11月研发,韵味十足,柔情似水,人声出色,个频段十分均衡耐听为Philips打下了大大的疆土28脚封装,供电(+5,-5,-15),I2S架构,S/N 90dB/min 95dB/Type 声道分离80dB后缀A是1541的升级版,S1表示精选TDA1541ASTEREO HIGH PERFORMANCE 16-BIT DACTDA1541A/N2STEREO HIGH PERFORMANCE 16-BIT DACTDA1541A/N2/R1STEREO HIGH PERFORMANCE 16-BIT DACTDA1541A/N2/S1STEREO HIGH PERFORMANCE 16-BIT DAC(关东:至今还在一些DAC内能见到身影,经典程度可见一斑)TDA1543DUAL 16-BIT DAC ECONOMY VERSION I2S INPUT FORMATPhilips为小型设备开发的芯片,1991年2月研发解析力一般,音色温暖,中频迷人,密度很厚度令人吃惊8脚封装(T为16脚),供电+5v,S/N 96dB 分离90dBTDA1543TDUAL 16-BIT DAC ECONOMY VERSION I2S INPUT FORMATTDA1545STEREO CONTINUOUS CALIBRA TION DAC第一款CONTINUOUS CALIBRATION dac,1993年3月研发|音色不明8脚封装(ATT为14脚),供电+5v,S/N 98dB 声道分离95dBTDA1545ASTEREO CONTINUOUS CALIBRA TION DACTDA1545ATSTEREO CONTINUOUS CALIBRA TION DACTDA1545ATTSTEREO CONTINUOUS CALIBRA TION DACTDA1547DUAL TOP-PERFORMANCE BITSTREAM DACPhilips为顶级音频设备开发的超级芯片,1991年9月研发采用比特流技术的1比特dac,和他搭配的采用比特流技术的芯片SAA7350,他整合了三阶静噪和1比特dac两片芯片音色兼顾韵味和速度,收放自如,频响宽广,气势宏伟,适合各种音乐32脚封装,供电(+-5,-3.5)S/N 113dB/A计权THD-101dB声道分离115dBAD Audio D/A Convertersart#DAC DNR (dB) SNR (dB) DAC THD+N @ 1 kHz (-3dB) Product Description Price* (1000-4999) FunctionAD1955 120 120 110 Multibit Sigma-Delta D/A w/ SACD Playback $6.86 DAC(关东:同为当今顶级DAC之一的“AD1955”与BB顶旗舰“PCM1792”互有特色)AD1853 116 117 104 24-bit 192 kHz Multibit Sigma-Delta DAC (Current Output) $7.59 DAC AD1852 114 114 104 Stereo, 24-bit 192 kHz Multibit Sigma-Delta D/A (V oltage Output) $5.57 DACAD1854 113 112 97 Complete Single Chip Stereo Audio D/A $4.05 DACAD1953 112 112 100 SigmaDSP 3 Ch, 26-/48-Bit Processing D/A $7.14 DAC, Signal Processor AD1954 112 112 100 SigmaDSP 3 Ch, 26-/48-Bit Processing D/A $7.14 DAC, Signal Processor AD1933 110 110 96 192 kHz, 24-Bit CODEC w/ PLL $3.66 DACAD1833A 110 110 95 Multi-Ch, 24-bit 192 kHz, Sigma-Delta D/A $3.98 DACAD1958 109 108 96 Stereo, 24-bit 192 kHz Multibit Sigma-Delta D/A w/ PLL ** DACAD1934 108 108 96 192 kHz, 24-Bit CODEC w/ PLL, IC and SPI. $3.15 DACAD1851 96 110 90 16-Bit, 16 3 FS PCM Audio DACs Dual 5V Supplies $4.71 DACAD1857 94 - 90 Stereo, Single Supply 16/18/20-bit Sigma-Delta D/A ** DACAD1859 94 - 88 Stereo, Single Supply 18-bit Integrated Sigma-Delta D/A $4.45 DACAD1858 94 - 90 Stereo, Single Supply 16-bit Sigma-Delta D/A ** DACAD1868 92 98 88 Single Supply Dual 18-Bit Audio DAC ** DACAD1866 90 95 86 Single Supply Dual 16-Bit Audio DAC $10.57 DAC(关东:原文对AD的DAC介绍的很简单。

HT16K33A RAM映射LED驱动器说明书

Rev. 1.0012022-05-12HT16K33ARAM 映射16×8 带 按键扫描的LED驱动器特性•工作电压:4.5V~5.5V •内部RC 振荡器 •I 2C 总线接口•16×8位RAM 用于存储显示数据•最大显示模式为16×8:16SEGs 和8COMs •读/写地址自动递增•多达13×3按键矩阵扫描功能 •16阶调光电路•封装类型:20/24/28-pin SOP/SSOP应用领域•工业控制指示器•数字时钟、温度计、计数器、万用表 •机顶盒•录像机设备 •仪表读数•其它消费类应用 •LED 显示概述HT16K33A 是一款存储器映射和多功能LED 控制驱动芯片。

该芯片支持最大128点的显示模式(16SEGs ×8COMs)以及最大13×3的按键矩阵扫描电路。

HT16K33A 的软件配置特性使其适用于多种LED 应用,包括LED 模块和显示子系统。

HT16K33A 通过双向I 2C 接口可与大多数微控制器进行通信。

方框图VDDVSSSDASCLRev. 1.0022022-05-122019181716151413121112345678910VDD SDA SCL ROW0/K1ROW1/K2ROW2/K3ROW3/K4ROW4/K5ROW5/K6ROW6/K7VSS COM0/AD COM1/KS0COM2/KS1COM3/KS2COM4COM5COM6COM7ROW7/K8/INTHT16K33A 20 SOP-A/SSOP-A VDD SDA SCL ROW0/A1ROW1/A0ROW2/K1ROW3/K2ROW4/K3ROW5/K4ROW6/K5ROW7/K6ROW8/K7VSS COM0/AD COM1/KS0COM2/KS1COM3/KS2COM4COM5COM6COM7ROW11/K10/INTROW10/K9ROW9/K8HT16K33A 24 SOP-A/SSOP-A 242322212019181716151413123456789101112VDD SDA SCL ROW0/A2ROW1/A1ROW2/A0ROW3/K1ROW4/K2ROW5/K3ROW6/K4ROW7/K5ROW8/K6ROW9/K7ROW10/K8VSS COM0/AD COM1/KS0COM2/KS1COM3/KS2COM4COM5COM6COM7ROW15/K13/INTROW14/K12ROW13/K11ROW12/K10ROW11/K9HT16K33A 28 SOP-A/SSOP-A28272625242322212019181716151234567891011121314Rev. 1.0032022-05-12内部连接简图极限参数电源供应电压 ..............V SS-0.3V ~ V SS+6.5V 端口输入电压 .............V SS-0.3V ~ V DD+0.3V 工作温度 ................................. -40℃~ 85℃储存温度 ................................-60°C ~ 150°C注:这里只强调额定功率,超过极限参数所规定的范围将对芯片造成损害,无法预期芯片在上述标示范围外的工作状态,而且若长期在标示范围外的条件下工作,可能影响芯片的可靠性。

中频信号的ad和da转换芯片

中频信号的ad和da转换芯片摘要:1.中频信号的AD 和DA 转换芯片的概述2.中频信号AD 和DA 转换芯片的工作原理3.中频信号AD 和DA 转换芯片的性能指标4.中频信号AD 和DA 转换芯片的应用领域5.市场上主要的中频信号AD 和DA 转换芯片生产商正文:1.中频信号的AD 和DA 转换芯片的概述中频信号的AD 和DA 转换芯片,是指将模拟信号转换为数字信号,或将数字信号转换为模拟信号的芯片,主要用于中频信号的处理和传输。

在中频信号的处理中,AD 转换芯片用于将中频信号的模拟信号转换为数字信号,DA 转换芯片则用于将数字信号转换为模拟信号,以供后续的处理和传输。

2.中频信号AD 和DA 转换芯片的工作原理AD 转换芯片的工作原理主要是将模拟信号转换为数字信号。

其主要由采样器、量化器和编码器三部分组成。

采样器负责将模拟信号进行采样,量化器负责将采样后的信号进行量化,编码器则将量化后的信号进行编码,生成数字信号。

DA 转换芯片的工作原理主要是将数字信号转换为模拟信号。

其主要由解码器、量化器和采样器三部分组成。

解码器负责将数字信号进行解码,量化器负责将解码后的信号进行量化,采样器则负责将量化后的信号进行采样,生成模拟信号。

3.中频信号AD 和DA 转换芯片的性能指标中频信号的AD 和DA 转换芯片的性能指标主要有采样率、转换速率、量化位数、噪声等。

采样率和转换速率决定了芯片的转换速度和精度,量化位数决定了芯片的转换精度,噪声则影响了芯片的转换质量。

4.中频信号AD 和DA 转换芯片的应用领域中频信号的AD 和DA 转换芯片广泛应用于通信、广播、计算机等领域。

在通信领域,用于信号的调制和解调;在广播领域,用于信号的传输和接收;在计算机领域,用于数据的处理和存储。

5.市场上主要的中频信号AD 和DA 转换芯片生产商市场上主要的中频信号AD 和DA 转换芯片生产商有德州仪器、ADI、TI 等。

华硕主板

数字家庭主板M2NDH-支持AMD®SocketAM2Athlon64FX/Athlo64X2/Athlon64/Sempron -AMDLive!™Ready-强大扩充能力:1xPCI-Ex16、2xPCI-E、3xPCI-华硕WiFi-APSolo-华硕DHRemote™-华硕MP3-In™-华硕Q-Connector-高保真音频中央处理器支持AMD®SocketAM2Athlon64FX/Athlo64X2/Athlon64/Sempron 支持AMDCool'n'Quiet™技术AMD64架构,同时兼容32位和64位计算AMDLive!™Ready芯片组NVIDIAnForce®430MCP前端总线2000/1600MT/s内存双通道内存架构4x240-pinDIMM内存插槽,支持最大容量高达8GB的DDR2800/667/533ECC和non-ECC、un-buffered内存扩充插槽1xPCI-Expressx16插槽2xPCI-Expressx1插槽3xPCI2.2插槽存储装置/RAID-1xUltraDMA133/100/66/33-4xSerialATA3.0Gb/s-NVIDIAMediaShield™RAID通过SerialA TA设备支持RAID0、1、0+1、5和JBOD网络功能NVIDIAnForce®430内建GigabitMAC,支持externalAttansicPHY无线局域网:54MbpsIEEE802.11b/g(华硕WiFi-APSolo)音频功能ADI6声道高保真音频CODEC背板S/PDIF数字音频输出USB高达8个USB2.0/1.1接口M2N-VMDH-AMDSocketAM2-NVIDIAGeForce6100/nForce430-双通道DDR2800/667/533-1xPCIExpressx16+1xPCIExpressx1+2xPCI-双VGA:DVI-D和D-Sub-8声道高保真音频-2x1394a接口中央处理器支持AMD®SocketAM2Athlon64X2/Athlon64FX/Athlon64/Sempro nAMDCool'n'Quiet™技术AMD64架构,兼容32位和64位计算AMDLive!™Ready芯片组NVIDIAGeForce6100/nForce430前端总线2000/1600MT/s 内存双通道内存架构4x240-pinDIMM插槽,支持最大容量为8GB的DDR2800/667/533non-ECC,un-buffered内存显卡集成GeForce6100GPU高清晰视频处理,最高分辨率可达1920x1440(@75Hz)支持RGB显示;UXGA1600x1200(@60Hz)支持DVI-D显示支持双VGA输出:DVI-D和RGB注意:DVI-D不能用来输出RGB信号至CRT。

目前常用的DA芯片

目前常用AD/DA芯片简介目前生产AD/DA的主要厂家有ADI、TI、BB、PHILIP、MOTOROLA等,武汉力源公司拥有多年从事电子产品的经验和雄厚的技术力量支持,已取得排名世界前列的模拟IC生产厂家ADI、TI公司代理权,经营全系列适用各种领域/场合的AD/DA器件。

1. AD公司AD/DA器件耗仅是1mW。

AD7705是基于微控制器(MCU)、数字信号处理器(DSP)系统的理想电路,能够进一步节省成本、缩小体积、减小系统的复杂性。

应用于微处理器(MCU)、数字信号处理(DSP)系统,手持式仪器,分布式数据采集系统。

2)3V/5V CMOS信号调节AD转换器:AD7714AD7714是一个完整的用于低频测量应用场合的模拟前端,用于直接从传感器接收小信号并输出串行数字量。

它使用Σ-Δ转换技术实现高达24位精度的代码而不会丢失。

输入信号加至位于模拟调制器前端的专用可编程增益放大器。

调制器的输出经片内数字滤波器进行处理。

数字滤波器的第一次陷波通过片内控制寄存器来编程,此寄存器可以调节滤波的截止时间和建立时间。

AD7714有3个差分模拟输入(也可以是5个伪差分模拟输入)和一个差分基准输入。

单电源工作(+3V或+5V)。

因此,AD7714能够为含有多达5个通道的系统进行所有的信号调节和转换。

AD7714很适合于灵敏的基于微控制器或DSP的系统,它的串行接口可进行3线操作,通过串行端口可用软件设置增益、信号极性和通道选择。

AD7714具有自校准、系统和背景校准选择,也允许用户读写片内校准寄存器。

CMOS结构保证了很低的功耗,省电模式使待机功耗减至15μW(典型值)。

3)微功耗8通道12位AD转换器:AD7888AD7888是高速、低功耗的12位AD转换器,单电源工作,电压范围为2.7V~5.25V,转换速率高达125ksps,输入跟踪-保持信号宽度最小为500ns,单端采样方式。

AD7888包含有8个单端模拟输入通道,每一通道的模拟输入范围均为0~Vref。

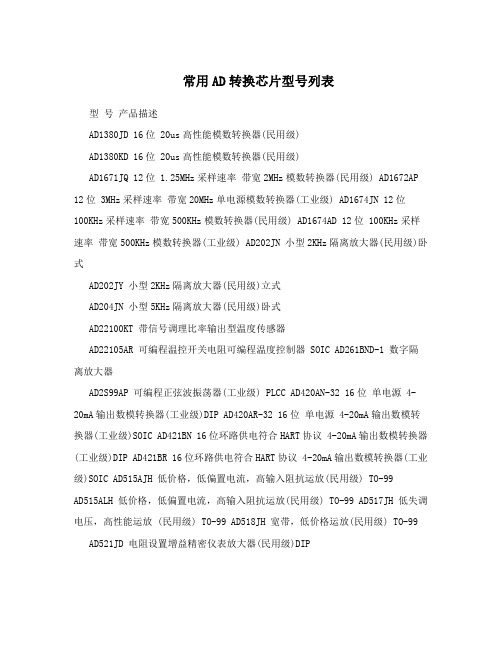

常用AD转换芯片型号列表

常用AD转换芯片型号列表型号产品描述AD1380JD 16位 20us高性能模数转换器(民用级)AD1380KD 16位 20us高性能模数转换器(民用级)AD1671JQ 12位 1.25MHz采样速率带宽2MHz模数转换器(民用级) AD1672AP 12位 3MHz采样速率带宽20MHz单电源模数转换器(工业级) AD1674JN 12位100KHz采样速率带宽500KHz模数转换器(民用级) AD1674AD 12位 100KHz采样速率带宽500KHz模数转换器(工业级) AD202JN 小型2KHz隔离放大器(民用级)卧式AD202JY 小型2KHz隔离放大器(民用级)立式AD204JN 小型5KHz隔离放大器(民用级)卧式AD22100KT 带信号调理比率输出型温度传感器AD22105AR 可编程温控开关电阻可编程温度控制器 SOIC AD261BND-1 数字隔离放大器AD2S99AP 可编程正弦波振荡器(工业级) PLCC AD420AN-32 16位单电源 4-20mA输出数模转换器(工业级)DIP AD420AR-32 16位单电源 4-20mA输出数模转换器(工业级)SOIC AD421BN 16位环路供电符合HART协议 4-20mA输出数模转换器(工业级)DIP AD421BR 16位环路供电符合HART协议 4-20mA输出数模转换器(工业级)SOIC AD515AJH 低价格,低偏置电流,高输入阻抗运放(民用级) TO-99AD515ALH 低价格,低偏置电流,高输入阻抗运放(民用级) TO-99 AD517JH 低失调电压,高性能运放 (民用级) TO-99 AD518JH 宽带,低价格运放(民用级) TO-99 AD521JD 电阻设置增益精密仪表放大器(民用级)DIPAD524AD 引脚设置增益高精度仪表放大器(工业级)DIP AD526BD 软件编程仪表放大器(工业级)DIPAD526JN 软件编程仪表放大器(民用级)DIPAD532JH 模拟乘法器(民用级)TO-99AD534JD 模拟乘法器(民用级)DIPAD534JH 模拟乘法器(民用级)TO-99AD536AJH 集成真有效值直流转换器(民用级)TO-99 AD536AJD 集成真有效值直流转换器(民用级)DIPAD536AJQ 集成真有效值直流转换器(民用级)DIPAD537JH 150KHZ集成压频转换器(民用级)TO-99AD537SH 150KHZ集成压频转换器(军用级)TO-99AD538AD 单片实时模拟乘法器(工业级)DIPAD539JN 宽带双通道线性乘法器(民用级)DIPAD542JH 低价格,低偏置电流,高输入阻抗运放(民用级) TO-99 AD545ALH 低偏置电流,高输入阻抗运放(民用级) TO-99 AD546JN 静电计放大器(民用级)DIP AD547JH 低价格,低偏置电流,高输入阻抗运放(民用级) TO-99 AD548JN 精密 BiFET输入运放(民用级)DIPAD549JH 低偏置电流,高输入阻抗运放(民用级) TO-99 AD549LH 低偏置电流,高输入阻抗运放(民用级) TO-99 AD5539JN 高速运放(民用级)DIP AD557JN 微处理器兼容完整7位电压输出数模转换器(民用)DIP AD558JN 微处理器兼容完整8位电压输出数模转换器(民用)DIP AD565AJD 12位 0.25us电流输出数模转换器(民用)DIP AD568JQ 12位超高速电流输出数模转换器(民用)DIP AD569JN 16位 3us电流输出数模转换器(民用)DIP AD570JD/+ 8位 25us模数转换器(民用)DIP AD574AJD 12位 25us模数转换器(民用)DIP AD574AKD 12位 25us模数转换器(民用)DIP AD578KN 12位 3us模数转换器(民用)DIPAD580JH 精密 2.5V电压基准源(民用级)TO-52 AD580LH 精密 2.5V电压基准源(民用级)TO-52 AD581JH 精密 10V电压基准源(民用级)TO-5 AD582KD 0.7us采样保持放大器(民用)DIPAD584JH 引脚设置输出电压基准源(民用级)TO-99 AD584JN 引脚设置输出电压基准源(民用级)DIP AD585AQ 3us采样保持放大器(工业级)DIPAD586JN 精密 5V电压基准源(民用级)DIP。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

REV.0AD1833AInformation furnished by Analog Devices is believed to be accurate andreliable. However, no responsibility is assumed by Analog Devices for itsuse, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 Fax: 781/326-8703© 2003 Analog Devices, Inc. All rights reserved.Multichannel, 24-Bit, 192 kHz, ⌺-⌬ DACFEATURES5 V Stereo Audio System with 3.3 V Tolerant Digital InterfaceSupports 96 kHz Sample Rates on 6 Channels and192 kHz on 2 ChannelsSupports 16-/20-/24-Bit Word LengthsMultibit ⌺-⌬ Modulators withPerfect Differential Linearity Restoration for Reduced Idle Tones and Noise FloorData Directed Scrambling DACs—Least Sensitive to JitterDifferential Output for Optimum PerformanceDACs Signal-to-Noise and Dynamic Range:110 dB–94 dB THD + N—6-Channel Mode–95 dB THD + N—2-Channel ModeOn-Chip Volume Control per Channel with 1024-Step Linear ScaleSoftware Controllable Clickless MuteDigital De-emphasis ProcessingSupports 256؋ f S, 512؋ f S, and 768؋ f S MasterClock ModesPower-Down Mode Plus Soft Power-Down Mode Flexible Serial Data Port with Right-Justified,Left-Justified, I2S Compatible, and DSP Serial Port Modes Supports Packed Data Mode and TDM Mode48-Lead LQFP Plastic PackageAPPLICATIONSDVD Video and Audio PlayersHome Theater SystemsAutomotive Audio SystemsSet-Top BoxesDigital Audio Effects ProcessorsFUNCTIONAL BLOCK DIAGRAMMCLKCDATACLATCHCCLKOUTLP1OUTLN1OUTLP2OUTLN2OUTLP3OUTLN3OUTRP3OUTRN3OUTRP2OUTRN2OUTRP1OUTRN1ZERO FLAGSDV DVAV D DRESETSOUTL/RCLKBCLKSDIN1SDIN2SDIN3GENERAL DESCRIPTIONThe AD1833A is a complete, high performance, single-chip, multichannel, digital audio playback system. It features six audio playback channels, each comprising a high performance digital interpolation filter, a multibit S-D modulator featuring Analog Devices’ patented technology, and a continuous-time voltage-out analog DAC section. Other features include an on-chip clickless attenuator and mute capability for each channel, programmed through an SPI compatible serial control port.The AD1833A is fully compatible with all known DVD formats, accommodating word lengths of up to 24 bits at sample rates of 48kHz and 96 kHz on all six channels while supporting a 192kHz sample rate on two channels. It also provides the Redbook stan-dard 50m s/15 m s digital de-emphasis filters at sample rates of32kHz, 44.1kHz, and 48kHz.The AD1833A has a very flexible serial data input port that allows glueless interconnection to a variety of ADCs, DSP chips, AES/EBU receivers, and sample rate converters. It can be con-figured in right-justified, left-justified, I2S, or DSP serial port compatible modes. The AD1833A accepts serial audio data in MSB first, twos complement format. The AD1833A can be operated from a single 5 V power supply; it also features a separate supply pin for its digital interface that allows it to be interfaced to devices using 3.3 V power supplies.The AD1833A is fabricated on a single monolithic integrated circuit and is housed in a 48-lead LQFP package for operation from –40∞C to +85∞C.REV. 0–2–AD1833A–SPECIFICATIONSParameter Min Typ Max Unit Test ConditionsANALOG PERFORMANCEDIGITAL-TO-ANALOG CONVERTERSDynamic Range (20 Hz to 20 kHz, –60 dBFS Input)with A-Weighted Filter AD1833AA 106.5110.0dB AD1833AA 110.5dB f S = 96 kHzAD1833AC107.0dB Total Harmonic Distortion + Noise–95–89dB Two channels active –94dB Six channels active–95dB 96 kHz, two channels active –94dB 96 kHz, six channels activeSNR110dB Interchannel Isolation 108dBDC Accuracy Gain Error±3%Interchannel Gain Mismatch 0.2%Gain Drift80ppm/∞C Interchannel Crosstalk (EIAJ Method)–120dBInterchannel Phase Deviation±0.1Degrees Volume Control Step Size (1023 Linear Steps)0.098%Volume Control Range (Max Attenuation)+63.5 (0.098)dB (%)Mute Attenuation–63.5 (0.098)dB (%)De-emphasis Gain Error±0.1dBFull-Scale Output Voltage at Each Pin (Single-Ended) 1 (2.8)V rms (V p-p)Output Resistance Measured Differentially 150W Common-Mode Output Volts2.2VDAC INTERPOLATION FILTER—8ϫ Mode (48 kHz)Pass Band21.768kHzPass-Band Ripple ±0.01dB Stop Band24kHz Stop-Band Attenuation 70dB Group Delay510m s DAC INTERPOLATION FILTER—4ϫ Mode (96 kHz)Pass Band37.7kHz Pass-Band Ripple ±0.03dB Stop Band55.034kHz Stop-Band Attenuation 70dB Group Delay160m sDAC INTERPOLATION FILTER—2ϫ Mode (192 kHz)Pass Band89.954kHzPass-Band Ripple ±1dB Stop Band 104.85kHz Stop-Band Attenuation 70dB Group Delay140m sTEST CONDITIONS, UNLESS OTHERWISE NOTED *Supply Voltages (AV DD , DV DDX )5 V Ambient Temperature 25∞CInput Clock 12.288 MHz, (8؋ Mode)Input SignalNominally 1 kHz, 0 dBFS (Full-Scale)Input Sample Rate48 kHzMeasurement Bandwidth 20 Hz to 20 kHz Word Width24 Bits Load Capacitance 100 pF Load Impedance 10 k W*Performance is identical for all channels (except for the I nterchannel Gain Mismatch and Interchannel Phase Deviation specifications).AD1833AParameter Min Typ Max Unit Test Conditions DIGITAL I/OInput Voltage HI 2.4VInput Voltage LO0.8VOutput Voltage HI DV DD2–0.4VOutput Voltage LO0.4VPOWER SUPPLIESSupply Voltage (AV DD and DV DD1) 4.55 5.5VSupply Voltage (DV DD2) 3.3DV DD1VSupply Current I ANALOG38.542mASupply Current I DIGITAL4248mA Active2mA Power-DownPower Supply Rejection Ratio1 kHz 300 mV p-p Signal at Analog Supply Pins–60dB20 kHz 300 mV p-p Signal at Analog Supply Pins–50dBSpecifications subject to change without notice.DIGITAL TIMING(Guaranteed over –40؇C to +85؇C, AV DD = DV DD = 5 V ؎ 10%)Parameter Min Max Unit CommentsMASTER CLOCK AND RESETt ML MCLK LO (All Modes)*15ns24 MHz clock, clock doubler bypassedt MH MCLK HI (All Modes)*15ns24 MHz clock, clock doubler bypassedt PDR PD/RST LO20nsSPI PORTt CCH CCLK HI Pulsewidth20nst CCL CCLK LO Pulsewidth20nst CCP CCLK Period80nst CDS CDATA Setup Time10ns To CCLK risingt CDH CDATA Hold Time10ns From CCLK risingt CLS CLATCH Setup10ns To CCLK risingt CLH CLATCH Hold10ns From CCLK risingDAC SERIAL PORTt DBH BCLK HI15nst DBL BCLK LO15nst DLS L/RCLK Setup10ns To BCLK risingt DLH L/RCLK Hold10ns From BCLK risingt DDS SDATA Setup10ns To BCLK risingt DDH SDATA Hold15ns From BCLK risingTDM MODE MASTERt TMBD BCLKTDM Delay20ns From MCLK risingt TMFSD FSTDM Delay10ns From BCLKTDM risingt TMDDS SDIN1 Setup15ns To BCLKTDM fallingt TMDDH SDIN1 Hold15ns From BCLKTDM fallingTDM MODE SLAVEf TSB BCLKTDM Frequency256 ϫ f St TSBCH BCLKTDM High20nst TSBCL BCLKTDM Low20nst TSFS FSTDM Setup10ns To BCLKTDM fallingt TSFH FSTDM Hold10ns From BCLKTDM fallingt TSDDS SDIN1 Setup15ns To BCLKTDM fallingt TSDDH SDIN1 Hold15ns From BCLKTDM fallingAUXILIARY INTERFACEt AXLRD L/RCLK Delay10ns From BCLK fallingt AXDD Data Delay10ns From BCLK fallingt AXBD AUXBCLK Delay20ns From MCLK rising*MCLK symmetry must be better than 60:40 or 40:60.Specifications subject to change without notice.REV. 0–3–REV. 0–4–AD1833AMCLKPD/RSTFigure 1.MCLK and RESET TimingCLATCHCCLKCINBCLKL/RCLKSDATALEFT-JUSTIFIEDMODESDATARIGHT-JUSTIFIEDMODESDATA I 2S MODEFigure 3.Serial Port TimingMCLKBCLKTDMFSTDMSDIN1Figure 4.TDM Master and Slave Mode TimingREV. 0AD1833A–5–ABSOLUTE MAXIMUM RATINGS *(T A = 25∞C, unless otherwise noted.)AV DD , DV DDX to AGND, DGND . . . . . . . . –0.3 V to +6.5 V AGND to DGND . . . . . . . . . . . . . . . . . . . . –0.3 V to +0.3 V Digital I/O Voltage to DGND . . . . . –0.3 V to DV DD2 + 0.3 V Analog I/O Voltage to AGND . . . . . . –0.3 V to AV DD + 0.3 V Operating Temperature RangeIndustrial (A Version) . . . . . . . . . . . . . . . –40∞C to +85∞C Storage Temperature Range . . . . . . . . . . . . –65∞C to +150∞C Maximum Junction Temperature . . . . . . . . . . . . . . . . 150∞CLQFP, q JA Thermal Impedance . . . . . . . . . . . . . . . . . 91∞C/W Lead Temperature, SolderingVapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . . 215∞C Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220∞C*Stresses above those listed under Absolute Maximum Ratings may cause perma-nent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute maximum rating may be applied at any one time.MCLKAUXL/R CLKAUX DA T Figure 5.Auxiliary Interface TimingORDERING GUIDEModelTemperature Range Package Description Package Option AD1833AAST –40∞C to +85∞C Low Profile Quad Flat Package ST-48AD1833ACST–40∞C to +85∞C Low Profile Quad Flat Package ST-48EVAL-AD1833AEB Evaluation BoardAD1833AAST-REEL –40∞C to +85∞C Low Profile Quad Flat Package ST-48AD1833ACST-REEL–40∞C to +85∞CLow Profile Quad Flat PackageST-48CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD1833A features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoidperformance degradation or loss of functionality.REV. 0AD1833A–6–PIN CONFIGURATIONOUTRP1OUTRN1AV DD AV DD AGND AGND AGND OUTLP1OUTLN1AV DD AV DD AGND AGND AGND DGND DV DD1ZEROA ZERO3R DGND DV DD2RESET ZERO1L ZERO3L ZERO1RO U T L N 2O U T L P 2O U T L N 3O U T L P 3A V D DF I L T D F I L T R AG N D O U T R P 3O U T R N 3O U T R P 2O U T R N 2Z E R O 2R C L A T C H C D A T AC C L K L /R C L KB C L K M C L K S D I N 1S D I N 2S D I N 3S O U T Z E R O 2LPIN FUNCTION DESCRIPTIONSPin No.Mnemonic IN/OUT Description1OUTLP1O DAC 1 Left Channel Positive Output.2OUTLN1ODAC 1 Left Channel Negative Output.3, 4, 33, 34, 44AV DD Analog Supply.5, 6, 7, 30, 31, 32, 41AGND Analog Ground.8, 29DGND Digital Ground.9DV DD1Digital Supply to Core Logic.10ZEROA O Flag to Indicate Zero Input on All Channels.11ZERO3R O Flag to Indicate Zero Input on Channel 3 Right.12ZERO3L O Flag to Indicate Zero Input on Channel 3 Left.13ZERO2R O Flag to Indicate Zero Input on Channel 2 Right.14CLATCH I Latch Input for Control Data (SPI Port).15CDATA I Serial Control Data Input (SPI Port).16CCLK I Clock Input for Control Data (SPI Port).17L/RCLK I/O Left/Right Clock for DAC Data Input; FSTDM Input in TDM Slave Mode;FSTDM Output in TDM Master Mode.18BCLK I/O Bit Clock for DAC Data Input; BCLKTDM Input in TDM Slave Mode; BCLKTDM Output in TDM Master Mode.19MCLK I Master Clock Input.20SDIN1I Data Input for Channel 1 Left/Right (Data Stream Input in TDM and Packed Modes).21SDIN2I/O Data Input for Channel 2 Left/Right (L/RCLK Output to Auxiliary DAC in TDM Mode).22SDIN3I/O Data Input for Channel 3 Left/Right (BCLK Output to Auxiliary DAC in TDM Mode).23SOUT O Auxiliary I 2S Output (Available in TDM Mode).24ZERO2L O Flag to Indicate Zero Input on Channel 2 Left.25ZERO1R O Flag to Indicate Zero Input on Channel 1 Right.26ZERO1L O Flag to Indicate Zero Input on Channel 1 Left.27RESET I Power-Down and Reset Control.28DV DD2Power Supply to Output Interface Logic.35OUTRN1O DAC 1 Right Channel Negative Output.36OUTRP1O DAC 1 Right Channel Positive Output.37OUTRN2O DAC 2 Right Channel Negative Output.38OUTRP2O DAC 2 Right Channel Positive Output.39OUTRN3ODAC 3 Right Channel Negative Output.REV. 0AD1833A–7–DEFINITION OF TERMS Dynamic RangeThe ratio of a full-scale input signal to the integrated input noise in the pass band (20 Hz to 20 kHz), expressed in decibels. Dynamic range is measured with a –60 dB input signal and is equal to (S/[THD + N]) +60 dB. Note that spurious harmonics are below the noise with a –60 dB input, so the noise level establishes the dynamic range. The dynamic range is specified with and without an A-Weight filter applied.Signal to (Total Harmonic Distortion + Noise)[S/(THD + N)]The ratio of the root-mean-square (rms) value of the fundamental input signal to the rms sum of all other spectral components in the pass band, expressed in decibels.Pass BandThe region of the frequency spectrum unaffected by the attenuation of the digital decimator’s filter.Pass-Band RippleThe peak-to-peak variation in amplitude response from equal-amplitude input signal frequencies within the pass band, expressed in decibels.Stop BandThe region of the frequency spectrum attenuated by the digital decimator’s filter to the degree specified by stop-band attenuation.Gain ErrorWith a near full-scale input, the ratio of actual output to expected output, expressed as a percentage.Interchannel Gain MismatchWith identical near full-scale inputs, the ratio of outputs of the two stereo channels, expressed in decibels.Gain DriftChange in response to a nearly full-scale input with a change in temperature, expressed as parts-per-million (ppm/∞C).Crosstalk (EIAJ Method)Ratio of response on one channel with a grounded input to a full-scale 1 kHz sine wave input on the other channel, expressed in decibels.Power Supply RejectionWith no analog input, signal present at the output when a 300 mV p-p signal is applied to the power supply pins, expressed in decibels of full scale.Group DelayIntuitively, the time interval required for an input pulse to appear at the converter’s output, expressed in ms. More precisely, the derivative of radian phase with respect to the radian frequency at a given frequency.Group Delay VariationThe difference in group delays at different input frequencies.Specified as the difference between the largest and the smallest group delays in the pass band, expressed in m s.PIN FUNCTION DESCRIPTIONS (continued)Pin No.Mnemonic IN/OUT Description40OUTRP3ODAC 3 Right Channel Positive Output.42FILTR Reference/Filter Capacitor Connection. Recommend 0.1 m F/10 m F decouple to analog ground.43FILTD Filter Capacitor Connection. Recommend 0.1 m F/10 m F decouple to analog ground.45OUTLP3O DAC 3 Left Channel Positive Output.46OUTLN3O DAC 3 Left Channel Negative Output.47OUTLP2O DAC 2 Left Channel Positive Output.48OUTLN2ODAC 2 Left Channel Negative Output.REV. 0AD1833A –8–0.01000.20.40.60.81.0 1.21.41.61.82.00.0080.0060.0040.0020–0.002–0.004–0.006–0.008–0.010d BHz؋104TPC 1.Pass-Band Response, 8ϫ Mode102.002.052.102.152.202.25 2.302.352.402.45 2.500–10–20–30d BHz؋104–40–50–60–70–80–90–100TPC 2.Transition Band Response, 8ϫMode 00.51.52.02.53.00–20–40–60–80–100–120–140–160d BHz؋1051.0TPC plete Response, 8ϫ Mode –Typical Performance Characteristics0.1000.51.01.52.0 2.53.03.50.080.060.040.020–0.02–0.04–0.06–0.08–0.10d BHz؋104TPC 4.Pass-Band Response, 4ϫ Mode0.500.51.01.52.0 2.53.03.54.00.40.30.20.10–0.1–0.2–0.3–0.4–0.5d BHz؋104TPC 5.40 kHz Pass-Band Response, 4ϫ Mode104.04.24.44.64.85.0 5.25.45.65.86.00–10–20–30d BHz؋104–40–50–60–70–80–90–100TPC 6.Transition Band Response, 4ϫ ModeREV. 0AD1833A–9––20–40–60–80–100–120–140–160d BHz؋105TPC plete Response, 4ϫ Mode2.0123456781.50.50–0.5–1.0–1.5–2.0d BHz؋1041.0TPC 8.80 kHz Pass-Band Response, 2ϫ Mode 100.800.850.900.951.00 1.05 1.10 1.151.200–10–20–30d BHz؋105–40–50–60–70–80–90–100TPC 9.Transition Band Response, 2ϫ Mode00.5 1.5 2.0–20–40–60–80–100–120–140–160d BHz؋1051.0TPC plete Response, 2ϫ ModeREV. 0AD1833A–10–FUNCTIONAL DESCRIPTION Device ArchitectureThe AD1833A is a six-channel audio DAC featuring multibit sigma-delta (S -D ) technology. The AD1833A features three stereo converters (providing six channels); each stereo channel is con-trolled by a common bit-clock (BCLK) and synchronization signal (L/RCLK).General OverviewThe AD1833A is designed to run with an internal MCLK(IMCLK) of 24.576MHz and a modulator rate of 6.144MHz (i.e., IMCLK/4). From this IMCLK frequency, sample rates of 48kHz and 96kHz can be achieved on six channels or 192kHz can be achieved on two channels. The internal clock should never be run at a higher frequency but may be reduced to achieve lower sampling rates, i.e., for a sample rate of 44.1 kHz, the appro-priate internal MCLK is 22.5792 MHz. The modulator rate scales in proportion with the MCLK scaling.InterpolatorThe interpolator consists of as many as three stages of sample rate doubling and half-band filtering followed by a 16-sample zero order hold (ZOH). The sample rate doubling is achieved by zero stuffing the input samples, and a digital half-band filter is used to remove any images above the band of interest and to bring the zero samples to their correct values.The interpolator output must always be at a rate of IMCLK/64.Depending on the interpolation rates selected, one, two, or all three stages of doubling may be switched in. This allows for three different sample rate inputs for any given IMCLK. For an IMCLK of 24.576 MHz, all three doubling stages are used with a 48 kHz input sample rate; with a 96 kHz input sample rate, only two doubling stages are used; and with a 192 kHz input samplerate, only one doubling stage is used. In each case, the input sample frequency is increased to 384 kHz (IMCLK/64). The ZOH holds the interpolator samples for upsampling by the modulator. This is done at a rate 16 times the interpolator output sample rate.ModulatorThe modulator is a 6-bit, second order implementation and uses data scrambling techniques to achieve perfect linearity. The modu-lator samples the output of the interpolator stage(s) at a rate of (IMCLK/4).OPERATING FEATURES SPI Register DefinitionsThe SPI port allows flexible control of the device’s programmable functions. It is organized around nine registers: six individual channel volume registers and three control registers. Each write operation to the AD1833A SPI control port requires 16 bits of serial data in MSB-first format. The four most significant bits are used to select one of nine registers (seven register addresses are reserved),and the bottom 10 bits are written to that register. This allows a write to one of the nine registers in a single 16-bit transaction. The SPI CCLK signal is used to clock in the data. The incoming data should change on the falling edge of this signal and remain valid during the rising edge. At the end of the 16CCLK periods,the CLATCH signal should rise to latch the data internally into the AD1833A (see Figure 2).The serial interface format used on the control port uses a 16-bit serial word, as shown in Table I. The 16-bit word is divided into several fields: Bits 15 through 12 define the register address, Bits 11and 10 are reserved and must be programmed to 0, and Bits 9through 0 are the data field (which has specific definitions,depending on the register selected).Table I.Control Port MapRegister Address Reserved 1Data Field 1521413121110987654321NOTES 1Must be programmed to zero.2Bit 15 = MSB.Bit 15Bit 14Bit 13Bit 12Register Function 0000DAC Control 10001DAC Control 20010DAC Volume 10011DAC Volume 20100DAC Volume 30101DAC Volume 40110DAC Volume 50111DAC Volume 61000DAC Control 31001Reserved 1010Reserved 1011Reserved 1100Reserved 1101Reserved 1110Reserved 1111ReservedAD1833ATable II. DAC Control Register 1 Function Data-Word Width Power-Down RESET Interpolator ModeAddressReserved1De-emphasisSerial Mode15–12 000011 010 09–8 00 = None 01 = 44.1 kHz 10 = 32.0 kHz 11 = 48.0 kHz7–5 000 = I S 001 = RJ 010 = DSP 011 = LJ 100 = Pack Mode 1 (256) 101 = Pack Mode 2 (128) 110 = TDM Mode 111 = Reserved24–3 00 = 24 Bits 01 = 20 Bits 10 = 16 Bits 11 = Reserved2 0 = Normal 1 = PWRDWN1–0 00 = 8 (48 kHz)2 01 = 2 (192 kHz)2 10 = 4 (96 kHz)2 11 = ReservedNOTES 1 Must be programmed to zero. 2 For IMCLK = 24.576 MHz.DAC CONTROL REGISTER 1 De-emphasisDAC Word WidthThe AD1833A has a built-in de-emphasis filter that can be used to decode CDs that have been encoded with the standard Redbook 50 ms/15 ms emphasis response curve. Three curves are available, one each for 32 kHz, 44.1 kHz, and 48 kHz sampling rates. The filters may be selected by writing to Control Bits 9 and 8 in DAC Control Register 1 (see Table III).Table III. De-emphasis SettingsThe AD1833A will accept input data in three separate wordlengths—16 bits, 20 bits, and 24 bits. The word length may be selected by writing to Control Bits 4 and 3 in DAC Control Register 1 (see Table V).Table V. Word Length SettingsBit 4 0 0 1 1Power-Down ControlBit 3 0 1 0 1Word Length 24 Bits 20 Bits 16 Bits ReservedBit 9 0 0 1 1Bit 8 0 1 0 1De-emphasis Disabled 44.1 kHz 32 kHz 48 kHzThe AD1833A can be powered down by writing to Control Bit 2 in DAC Control Register 1 (see Table VI).Table VI. Power-Down ControlData Serial Interface ModeThe AD1833A’s serial data interface is designed to accept data in a wide range of popular formats including I2S, right-justified (RJ), left-justified (LJ), and flexible DSP modes. The L/RCLK pin acts as the word clock (or frame sync) to indicate sample interval boundaries. The BCLK defines the serial data rate while the data is input on the SDIN1–SDIN3 pins. The serial mode settings may be selected by writing to Control Bits 7 through 5 in the DAC Control Register 1 (see Table IV).Table IV. Data Serial Interface Mode SettingsBit 2 0 1Interpolator ModePower-Down Setting Normal Operation Power-Down ModeBit 7 0 0 0 0 1 1 1 1Bit 6 0 0 1 1 0 0 1 1Bit 5 0 1 0 1 0 1 0 1Serial Mode I 2S Right Justify DSP Left Justify Packed Mode 1 (256) Packed Mode 2 (128) TDM Mode ReservedThe AD1833A’s DAC interpolators can be operated in one of three modes—8 , 4 , or 2 — then correspond to 48 kHz, 96 kHz, and 192 kHz modes, respectively (for IMCLK = 24.576 MHz). The interpolator mode may be selected by writing to Control Bits 1 and 0 in DAC Control Register 1 (see Table VII).Table VII. Interpolator Mode SettingsBit 1 0 0 1 1Bit 0 0 1 0 1Interpolator Mode 8x (48 kHz)* 2x (192 kHz)* 4x (96 kHz)* Reserved*For IMCLK = 24.576 MHz.REV. 0–11–AD1833ADAC CONTROL REGISTER 2DAC Control Register 2 contains individual channel mute controls for each of the six DACs. Default operation (bit = 0) is muting off. Bits 9 through 6 of Control Register 2 are reserved and should be programmed to zero (see Table VIII).DAC CONTROL REGISTER 3 Stereo ReplicateThe AD1833A allows the stereo information on Channel 1 (SDIN1—Left 1 and Right 1) to be copied to Channels 2 and 3 (Left/Right 2 and Left/Right 3). These signals can be used in an external summing amplifier to increase potential signal SNR. Stereo replicate mode can be enabled by writing to control Bit 5 (see Table XI). Note that replication is not reflected in the zero flag status.Table VIII. DAC Control Register 2Function Address 15–12 0001 Reserved* 11 0 10 0 Reserved* 9–6 0 5 Channel 6 0 = Mute Off 1 = Mute On 4 3 Mute Control 2 Channel 3 0 = Mute Off 1 = Mute On 1 0Channel 5 Channel 4 0 = Mute Off 0 = Mute Off 1 = Mute On 1 = Mute OnChannel 2 Channel 1 0 = Mute Off 0 = Mute Off 1 = Mute On 1 = Mute On*Must be programmed to zero.Table IX. Muting ControlBit 5 X X X X X 1Bit 4 X X X X 1 XBit 3 X X X 1 X XBit 2 X X 1 X X XBit 1 X 1 X X X XBit 0 1 X X X X XMuting Mute Channel 1 Mute Channel 2 Mute Channel 3 Mute Channel 4 Mute Channel 5 Mute Channel 6Table X. DAC Control Register 3 Function Address 15–12 1000 Stereo Replicate Reserved* Reserved* (192 kHz) 11 0 10 0 9–6 0 5 0 = Normal 1 = Replicate MCLK Select 4–3 00 = IMCLK = MCLK 01 = IMCLK = MCLK 10 = IMCLK = MCLK 2 1 2 /3 Zero Detect 2 0 = Active High 1 = Active Low Reserved* 1 0 TDM Mode 0 0 = Master 1 = Slave*Must be programmed to zero.Table XI. Stereo ReplicateBit 5 0 1Stereo Mode Normal Channel 1 Data Replicated on Channels 2 and 3–12–REV. 0AD1833AMCLK SelectThe AD1833A allows the matching of available external MCLK frequencies to the required internal MCLK rate. The MCLK modification factor can be selected from 2, 1, or 2/3 by writing to Bit 4 and Bit 3 of Control Register 3. Internally, the AD1833A requires an MCLK of 24.576 MHz for sample rates of 48 kHz, 96 kHz, and 192 kHz. In the case of 48 kHz data with an MCLK of 256 fS, a clock doubler is used, whereas with an MCLK of 768 fS, a divide-by-3 block ( 3) is first implemented followed by a clock doubler. With an MCLK of 512 fS, the MCLK is passed through unmodified (see Table XII).Table XII. MCLK Settingsa global zero flag that indicates all channels contain zero data. The polarity of the zero signal is programmable by writing to Control Bit 2 (see Table XIII). In right-justified mode, the six individual channel flags are best used as three stereo zero flags by combining pairs of them through suitable logic gates. Then, when both the left and right inputs are zero for 1024 clock cycles, i.e., a stereo zero input for 1024 sample periods, the combined result of the two individual flags will become active, indicating a stereo zero.Table XIII. Zero DetectBit 2 0 1Channel Zero Status Active High Active LowBit 4 0 0 1 1Bit 3 0 1 0 1Modification Factor MCLK 2 Internally MCLK 1 Internally MCLK 2/3 Internally ReservedDAC Volume Control RegistersChannel Zero StatusThe AD1833A provides individual logic output status indicators when zero data is sent to a channel for 1024 or more consecutive sample periods in all modes except right-justified. There is alsoThe AD1833A has six volume control registers, one for each of the six DAC channels. Volume control is exercised by writing to the relevant register associated with each DAC. This setting is used to attenuate the DAC output. Full-scale setting (all 1s) is equivalent to zero attenuation (see Table XV).Table XIV. MCLK vs. Sample Rate SelectionSampling Rate fS (kHz) 32 64 128 44.1 88.2 176.4 48 96 192Interpolator Mode Required 8 4 2 8 4 2 8 4 2Internal MCLK Required (MHz) 16.384Suitable External MCLK Frequencies (MHz) MCLK 2 MCLK 1 MCLK 8192 16.384 24.5762/322.579211.289622.579233.868824.57612.28824.57636.864Table XV. Volume Control RegistersAddress 15–12 0 0 0 0 0 0 0 0 1 1 1 1 1 1 0 0 1 1 0 1 0 1 0 1Reserved* 11 0 10 0Volume Control 9–0 Channel 1 Volume Control (OUTL1) Channel 2 Volume Control (OUTR1) Channel 3 Volume Control (OUTL2) Channel 4 Volume Control (OUTR2) Channel 5 Volume Control (OUTL3) Channel 6 Volume Control (OUTR3)*Must be programmed to zero.REV. 0–13–。