PLL锁相环时钟设定

Cyclone器件中PLL的使用

Cyclone器件中PLL的使用摘要:CycloneFPGA具有锁相环(PLL)和全局时钟网络,提供完整的时钟管理方案。

CyclonePLL具有时钟倍频和分频、相位偏移、可编程占空比和外部时钟输出,进行系统级的时钟管理和偏移控制。

AlteraQuartuII软件无需任何外部器件,就可以启用CyclonePLL和相关功能。

本文将介绍如何设计和使用CyclonePLL功能。

PLL常用于同步内部器件时钟和外部时钟,使内部工作的时钟频率比外部时钟更高,时钟延迟和时钟偏移最小,减小或调整时钟到输出(TCO)和建立(TSU)时间。

关键字:CycloneFPGA锁相环PLL1.硬件结构每个CycloneFPGA包括具有多达两个PLL。

表1为几种型号CycloneFPGA内可用的PLL数量。

表1注释:(1)位于器件的左侧中部(2)位于器件的右侧中部表2:CyclonePLL功能功能时钟倍频和分频相位偏移可编程占空比内部时钟输出数量外部时钟输出数量(4)锁定端口可以输入逻辑阵列PLL 时钟输出可以输入逻辑阵列说明M/(N某后cale计数器)(1)小至156皮秒(p)的增量幅度(2),(3)每个PLL两个输出每个PLL一个输出表2注释:(1)M,N和后cale计数器的值从1至32;(2)最小的相位偏移量为压控振荡器(VCO)周期除以8;(3)对于角度调整,CycloneFPGA的偏移输出频率的增量至少为45o。

更小的角度增量可能取决于PLL时钟输出的倍频/分频系数;(4)100脚的扁平四方封装(TQFP)的EP1C3器件不支持PLLLVDS输出或外部时钟输出,144脚TQFP封装的EP1C6PLL2不支持外部时钟输出。

PLL主要作用就是把内部/外部时钟的相位和频率同步于输入参考时钟。

PLL由许多部分组成,共同完成相位调整。

CyclonePLL采用一个相位频率检测器(PFD)把参考输入时钟的上升沿和反馈时钟对齐。

根据占空比规定确定下降沿。

fpga的pll指标 -回复

fpga的pll指标-回复“FPGA的PLL指标”引言:现如今的数字系统设计中,可编程逻辑器件(FPGA)在嵌入式系统和数字电路应用中扮演着关键的角色。

时钟信号作为数字系统设计中的核心,对于FPGA来说尤为重要。

为了提供高质量的时钟信号,FPGA通常配备了可编程锁相环(PLL)。

本文将介绍FPGA的PLL指标,包括时钟输入范围、频率分辨率、锁定时间、输出抖动和相位噪声等特性。

一、时钟输入范围:时钟输入范围是指PLL接受的时钟信号的频率范围。

对于FPGA的PLL,时钟输入范围通常由两个参数确定:最小输入频率和最大输入频率。

最小输入频率定义了PLL能够稳定工作的最低频率,而最大输入频率则定义了PLL能够接受的最高频率。

这两个参数一般以赫兹(Hz)为单位进行表示。

二、频率分辨率:频率分辨率是指PLL可以实现的最小变化范围。

在FPGA中,频率分辨率通常由一个数字控制字(Digital Control Word,DCW)来定义。

该数字控制字由FPGA的软件编程确定,并决定了PLL输出频率的调整步长。

频率分辨率的大小决定了PLL输出频率的精度。

三、锁定时间:锁定时间是指PLL从接收新的输入时钟信号到输出的时钟信号稳定并达到设定频率的时间。

锁定时间受到PLL内部电路的延迟以及输入信号的稳定性的影响。

通常情况下,锁定时间越短越好,因为短的锁定时间意味着FPGA可以更快地响应时钟频率的变化。

四、输出抖动:输出抖动是指PLL输出时钟信号的时间抖动。

时间抖动是指相邻时钟周期之间的时间差异。

由于PLL内部电路中的噪声以及输入时钟信号的不稳定性,输出时钟信号存在一定的抖动。

对于某些应用,如高精度时序要求的系统,输出抖动可能是一个重要的考虑因素。

五、相位噪声:相位噪声是指PLL输出时钟信号的相位抖动。

相位抖动是指相邻时钟周期之间的相位差异。

相位噪声对于时钟数据同步、高速串行通信和精确频率合成等应用至关重要。

低相位噪声的PLL可以提供更稳定和可靠的时钟信号。

PLL锁相环时钟设定

PLL锁相环时钟设定未配置锁相环时(OSCCLK_PLLSEL=0):总线频率=外部晶振频率(OSCCLK)/2配置锁相环时(OSCCLK_PLLSEL=1): 系统时钟由锁相环提供,总线频率=倍频后频率(PLLCLK)/2时钟频率计算方法Fvco=2*Fosc*(SYNDIN+1)/(REFDIV+1)Fpll=Fvco/(2*POSTDIV)当POSTDIV=0时,Fpll=FvcoFbus=Fpll/2CRGFLG_LOCK==1时,说明PLLCLK稳定,可输出。

锁相环从设定到稳定需要时间,故期间应加几条空语句。

例程:void CLK_Init(void) {CLKSEL=0x00; //选择OSCCLK为系统时钟源16M PLLCTL_PLLON=1; //开启锁相环,锁相环电路允许//频率设定80M时SYNR = 0xc0 | 0x09;REFDV = 0x80 | 0x01;POSTDIV = 0x00; // PLLCLOCK=2*osc*(1+SYNR)/(1+REFDV)=160MHz; _asm(nop);_asm(nop);while(!CRGFLG_LOCK); // 时钟频率已稳定,锁相环频率锁定CLKSEL_PLLSEL=1; //使能锁相环时钟}PWM模块PWME:PWM允许寄存器,置1时允许输出。

PWMPOL:极性寄存器。

置1时首先输出高电平。

2、3、6、7、置1时clock SB 作为时钟源,置0时clock B作为时钟源PWMCAE:居中对齐允许寄存器,只有当通道输出禁止时才能设置此寄存器置1时为居中对齐,置0时左对齐PWMSCLA:比例因子寄存器A;用于提供clock SA的比例因子Clock SA的时钟频率= clock A/(2*PWMSCLA)当PWMSCLA为0时比例因子默认为256. CLOCKSB 计算方法类似,寄存器为PWMSCLB。

PWMCNTx:通道计数寄存器,一般设置值为0x00;PWMPERx:周期寄存器;左对齐时周期计算方法:PWMxPeriod=指定时钟周期乘以PWMPERx的值居中对齐时=指定时钟周期乘PWMPERx的值再乘2;PWMDTYx:占空比寄存器。

pll 时钟相位的作用

pll 时钟相位的作用

PLL(Phase-Locked Loop,锁相环)时钟相位的作用在于:

1.调整时钟频率:通过PLL的频率合成、频率分频和频率锁定等功能,可以

将输入的时钟信号(如50MHz)转换成符合特定要求的输出时钟信号(如150MHz)。

同时,PLL能够实现时钟频率的稳定性控制和抖动降低。

2.保持时钟相位:由于时钟信号在传输过程中容易因信号衰减、干扰等原因

而发生相位偏移或漂移,PLL通过引入反馈机制,使输出时钟与输入时钟在相位上保持一致,消除了输入时钟信号的相位抖动和漂移问题,提高了时序稳定性和系统性能。

时钟发生模块CGM与锁相环PLL

12.2.1 锁相环PLL的基本概念(1)锁相技术与频率合成技术①锁相技术:就是实现相位自动控制的一门科学,利用它可以得到频带范围宽、波道多、稳定度高、精度高的频率源。

②频率合成技术:就是利用一个或几个具有高稳定度和高精度的频率源(一般由晶体振荡器产生),通过对它们进行加减(混频),乘(倍频),除(分频)运算,产生大量的具有相同频率稳定度和频率精度的频率信号。

锁相环频率合成技术在通讯、雷达、导航、宇航、遥控遥测、电子技术测量等领域都有广泛的应用。

为了得到稳定度高、精度高的频率源,通常采用频率合成技术。

频率合成技术主要有两种:直接频率合成技术和间接频率合成技术。

③直接频率合成技术:是将一个或几个晶体振荡器产生的频率信号通过谐波发生器产生一系列频率信号,然后再对这些频率信号进行倍频、分频和混频,最后得到大量的频率信号。

其优点是:频率稳定度高,频率转换时间短(可达微秒量级),能做到很小的频率间隔。

缺点是:系统中要用到大量的混频器、滤波器等,从而导致体积大,成本高,安装调试复杂,故只用于频率精度要求很高的场合。

④间接频率合成技术:是利用锁相技术来产生大量的具有高稳定度和高精度的频率源。

由于间接频率合成器的关键部件是锁相环,故通常称为锁相环频率合成器。

由于锁相环频率合成器的主要部件都易于集成,一般只加一个分频器和一个一阶低通滤波器,故其具有体积小、重量轻、成本低、安装和调试简单等优点。

锁相环频率合成器在性能上逐渐接近直接频率合成器,所以它在电子技术中得到了日益广泛的应用,并在应用中得到迅速发展。

(2)锁相环频率合成器的基本原理锁相环频率合成器的各个部件基准频率源:基准频率源提供一个稳定频率源,其频率为fr,一般用精度很高的石英晶体振荡器产生,是锁相环的输入信号。

签相器:签相器是一个误差检测元件。

它将基准频率源的输出信号fr的相位与压控振荡器输出信号fo的相位相比较,产生一个电压输出信号ud,其大小取决于两个输入信号的相位差。

PLL设计关键基础及基本参数确定方法

PLL设计关键基础及基本参数确定方法PLL(锁相环)是一种电路设计技术,用于将输入信号的频率和相位合成为与参考信号相同的输出信号。

它在各种应用领域中具有广泛的应用,包括通信系统、数据传输、时钟发生器、频率合成器等。

1.建立模型:确定所需的频率范围和准确度,并选择适当的振荡器作为参考信号源。

建立时钟和相位比较器的模型,以及低通滤波器等组成部分的模型。

2.频率范围和准确度:确定PLL所需的输出频率范围和准确度。

这取决于具体的应用需求,如通信系统中需要的频率范围和准确度。

一般来说,更高的频率范围和准确度要求会导致设计更复杂的PLL电路。

3.反馈环:选择适当的反馈环型式,如基本PLL、全数字PLL或混合模拟数字PLL。

这取决于应用需求和设计复杂度。

基本PLL适用于频率较低的应用,但对相位噪声较敏感。

全数字PLL则采用数字环路滤波器,具有更高的鲁棒性和可控性。

4. 相位锁定范围(Phase Locked Loop Range):确定PLL的相位锁定范围,即输入信号的相位偏移量。

这取决于具体应用中的信号变化范围和要求。

较大的相位锁定范围会导致更高的设计复杂度。

5.闭环带宽:确定PLL的闭环带宽,即相位比较器输出与输出信号的相位偏差之间的关系。

较大的闭环带宽可以提供更高的锁定速度,但可能会导致更高的相位噪声。

6. 电源抑制比(Power Supply Rejection Ratio,PSRR):确定PLL对电源噪声的抑制能力。

电源噪声可能会影响PLL的性能,因此需要设计合适的滤波器和抑制电源噪声的能力。

7.噪声性能:确定PLL对输入信号噪声和环路滤波器自身噪声的敏感度。

这取决于环路滤波器的设计和反馈环的类型。

一般来说,全数字PLL 具有更好的噪声性能。

8.稳定性和抖动:确定PLL的稳定性和抖动性能。

PLL需要能够在各种工作条件下保持稳定,不受温度、电源变化等因素的影响。

抖动性能衡量了PLL输出信号的时钟稳定性。

pll锁相环

第11讲 PLL锁相环一、PLL的概述:Cyclone PLL具有时钟倍频和分频、相位偏移、可编程占空比和外部时钟输出,进行系统级的时钟管理和偏移控制。

Altera® Quartus® II软件无需任何外部器件,就可以启用Cyclone PLL和相关功能。

PLL常用于同步内部器件时钟和外部时钟,使内部工作的时钟频率比外部时钟更高,时钟延迟和时钟偏移最小,减小或调整时钟到输出(TCO)和建立(TSU)时间。

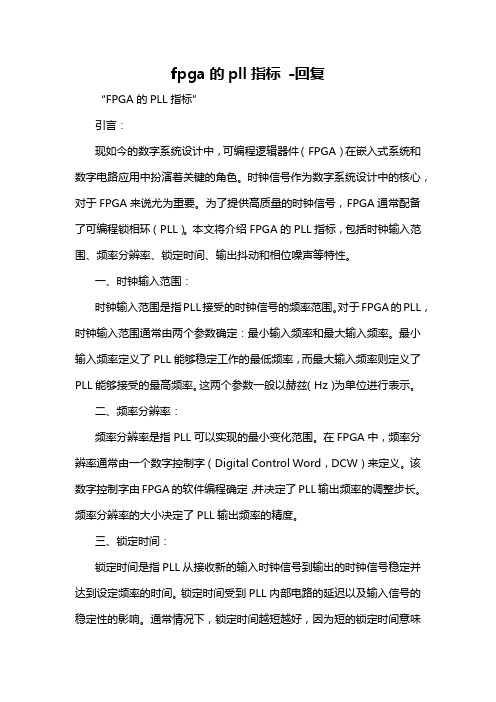

硬件结构每个Cyclone FPGA包括具有多达两个PLL。

表1为种型号Cyclone FPGA内可用的PLL数量。

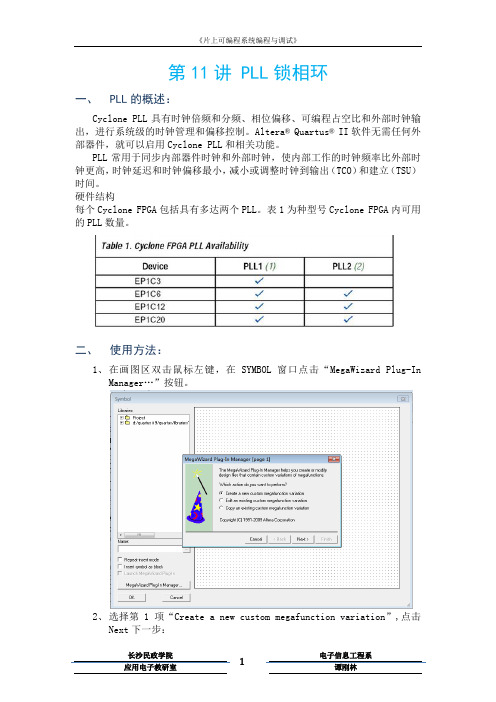

二、使用方法:1、在画图区双击鼠标左键,在SYMBOL窗口点击“MegaWizard Plug-InManager…”按钮。

2、选择第1项“Create a new custom megafunction variation”,点击Next下一步:3、在I/0选项中选中ALTPLL,并在命名栏给PLL取个名字,如PLL1:4、点击下一步:5、将速度等级设置为8,输入时钟频率设为50MHZ,输出时钟补偿为C0,点击下一步:6、将Create an ‘areset’input to asynchronously reset the PLL和Create ‘locked’output两个选项前的钩去掉:7、点击下一步:8、在Clock multiplication factor栏设置倍频率,如上图设置为2,也就是说在输入为50MHZ的情况下,经过PLL后频率变为100MHZ。

在Clock division factor栏可以设置分频率,也就相当于将输入的频率除以所设置的系数。

点击下一步:此页不选择C1,点击下一步:此页不选择e0,点击下一步:此页不做选择,点击下一步:9、点击Finish完成设置。

锁相环配置时钟

锁相环配置时钟锁相环作为一个提供系统时钟的模块,是一个基本的模块,几乎每次编程序都得用到。

下面记一下怎样配置锁相环来设定想要的系统时钟。

锁相环PLL、自时钟模式和前面说的实时中断RTI、看门狗COP都属于系统时钟与复位CRG中的模块,固前面用到的寄存器,这里有些会再用到。

在程序中配置锁相环的步骤如下:第一、禁止总中断;第二、寄存器CLKSEL的第七位置0,即CLKSEL_PLLSEL=0。

选择时钟源为外部晶振OSCCLK,在PLL程序执行前,内部总线频率为OSCCLK/2。

CLKSEL_PLLSEL=0时,系统时钟由外部晶振直接提供,系统内部总线频率=OSCCLK/2(OSCCLK为外部晶振频率)。

CLKSEL_PLLSEL=1时,系统时钟由锁相环提供,此时系统内部总线频率=PLLCLK/2 (PLLCLK为锁相环倍频后的频率)。

第三、禁止锁相环PLL,即PLLCTL_PLLON=0。

当PLLCTL_PLLON=0时,关闭PLL电路。

当PLLCTL_PLLON=1时,打开PLL电路。

第四、根据想要的时钟频率设置SYNR和REFDV两个寄存器。

SYNR和REFDV两个寄存器专用于锁相环时钟PLLCLK的频率计算,计算公式是:PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)其中,PLLCLK为PLL模块输出的时钟频率;OSCCLK为晶振频率;SYNR、REFDV 分别为寄存器SYNR、REFDV中的值。

这两个寄存器只有在PLLSEL=0时才能够写入(这里就是第二步的设置原因所在了)。

第五、打开PLL,即PLLCTL_PLLON=1。

第六、CRGFLG_LOCK位,确定PLL是否稳定。

当锁相环PLL电路输出的频率达到目标频率的足够小的误差范围内时,LOCK位置1,此时说明PLLCLK已经稳定,可以作为系统的时钟了。

该位在正常情况下为只读位。

第七、PLLCLK稳定后,允许锁相环时钟源PLLCLK为系统提供时钟,即CLKSEL_PLLSEL=1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PLL锁相环时钟设定

未配置锁相环时(OSCCLK_PLLSEL=0):

总线频率=外部晶振频率(OSCCLK)/2

配置锁相环时(OSCCLK_PLLSEL=1): 系统时钟由锁相环提供,总线频率=倍频后频率(PLLCLK)/2

时钟频率计算方法

Fvco=2*Fosc*(SYNDIN+1)/(REFDIV+1)

Fpll=Fvco/(2*POSTDIV)当POSTDIV=0时,Fpll=Fvco

Fbus=Fpll/2

CRGFLG_LOCK==1时,说明PLLCLK稳定,可输出。

锁相环从设定到稳定需要时间,故期间应加几条空语句。

例程:

void CLK_Init(void) {

CLKSEL=0x00; //选择OSCCLK为系统时钟源16M PLLCTL_PLLON=1; //开启锁相环,锁相环电路允许

//频率设定80M时

SYNR = 0xc0 | 0x09;

REFDV = 0x80 | 0x01;

POSTDIV = 0x00; // PLLCLOCK=2*osc*(1+SYNR)/(1+REFDV)=160MHz; _asm(nop);_asm(nop);

while(!CRGFLG_LOCK); // 时钟频率已稳定,锁相环频率锁定CLKSEL_PLLSEL=1; //使能锁相环时钟

}

PWM模块

PWME:PWM允许寄存器,置1时允许输出。

PWMPOL:极性寄存器。

置1时首先输出高电平。

2、3、6、7、置1时clock SB 作为时钟源,置0时clock B作为时钟源

PWMCAE:居中对齐允许寄存器,只有当通道输出禁止时才能设置此寄存器置1时为居中对齐,置0时左对齐

PWMSCLA:比例因子寄存器A;用于提供clock SA的比例因子

Clock SA的时钟频率= clock A/(2*PWMSCLA)当PWMSCLA为0时比例因子默认为256. CLOCKSB 计算方法类似,寄存器为PWMSCLB。

PWMCNTx:通道计数寄存器,一般设置值为0x00;

PWMPERx:周期寄存器;

左对齐时周期计算方法:PWMxPeriod=指定时钟周期乘以PWMPERx的值居中对齐时=指定时钟周期乘PWMPERx的值再乘2;

PWMDTYx:占空比寄存器。

占空比计算方法:极性为1时:Duty Cycle=PWMDTYx/PWMPERx*100%

极性为0时(PWMPERx-PWMDTYx)/PWMPERx

例程

void PWM_128init(void)

{

PWMPRCLK=0x00; //ClockA and ClockB等于总线时钟80M

PWMCLK=0xc2; //通道7、1选择SB、SA时钟源,通道5,3选择A,B时钟源PWMSCLB=0x14; //SB时钟源为40分频为2M

PWMSCLA=0x14; //SA时钟源2M;

PWMCTL=0xf0; //级联67 级联45 级联23 级联01

PWMCAE=0x00; //pwm左对齐输出

PWMCNT01=0;

PWMCNT23=0;

PWMCNT45=0;

PWMCNT67=0;

PWMPOL=0XFF; //初始输出高电平

PWMPER67 = 40000; //67通道输出50HZ的频率2M/40000

PWMPER45 = 8000; //45通道输出10k频率80M/8000

PWMPER23 = 8000; //23通道输出10k频率80M/8000

PWMPER01=40000;

PWMDTY67 = 2800; //67通道初始PWM高电平时间为1.5ms

PWMDTY45 = 2000; //45 通道初始占空比0%

PWMDTY23 =2000; //23通道初始占空比0

PWMDTY01=3000;

PWME=0XAA; //7,5,3,1通道使能

}

SPI模块

五、SPIDR 数据寄存器

SPI数据寄存器是SPI数据的输入和输出寄存器,写该寄存器会允许一个字节进入队列并发送。

如果SPI被配置成主机,当前面的数据发送完成,排在队列的数据会立即被发送。

SPISR寄存器中的发送空标志SPTEF表明SPI数据寄存器准备接收新的数据。

当SPIF=1时SPIDR中接收的数据是有效的。

SPI的编程方法:

1、初始化:设置控制寄存器SPICR1、SPICR2,及波特率寄存器SPIBR。

在此设

定SPI的工作方式,时钟极性,时钟相位,及各种中断允许等。

2、发送与接收数据的编写:作为主机方,只要将数据写入SPIDR,然后检查SPISR

的SPTEF位,若为1,则表示数据已经发送出去。

若同时接收对方送来的数据,则接着检查SPISR的SPIF位,若为1,则表示要接的数据已经进入数据寄存器,可以取出了。

SCI模块

SCI模块复用PS口的4个引脚,(0~3)作为RXD、TXD、RXD1、TXD1. SCI波特率寄存器(SCIBDH和SCIBDL)

SCI波特率=SCI模块时钟/(16*寄存器的值)。