SPI时钟模式的配置

SPI协议详解

【转】SPI协议详解SPI总线协议及SPI时序图详解2009-11-10 22:10SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

上升沿发送、下降沿接收、高位先发送。

上升沿到来的时候,sdo上的电平将被发送到从设备的寄存器中。

下降沿到来的时候,sdi上的电平将被接收到主设备的寄存器中。

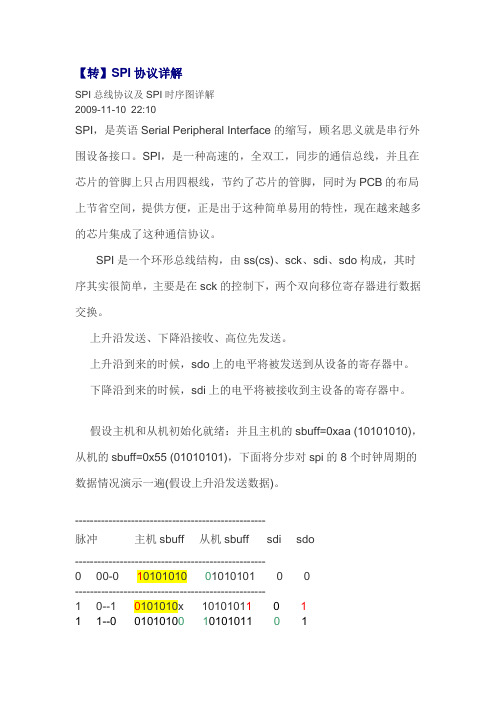

假设主机和从机初始化就绪:并且主机的sbuff=0xaa (10101010),从机的sbuff=0x55 (01010101),下面将分步对spi的8个时钟周期的数据情况演示一遍(假设上升沿发送数据)。

---------------------------------------------------脉冲主机sbuff 从机sbuff sdi sdo---------------------------------------------------0 00-0 10101010 01010101 0 0---------------------------------------------------1 0--1 0101010x 101010110 11 1--0 0101010010101011 0 1---------------------------------------------------2 0--1 1010100x 01010110 1 02 1--0 1010100101010110 10---------------------------------------------------3 0--1 0101001x 101011010 13 1--0 0101001010101101 0 1---------------------------------------------------4 0--1 1010010x 01011010 1 04 1--0 1010010101011010 10---------------------------------------------------5 0--1 0100101x 101101010 15 1--0 0100101010110101 0 1---------------------------------------------------6 0--1 1001010x 01101010 1 06 1--0 1001010101101010 10---------------------------------------------------7 0--1 0010101x 110101010 17 1--0 0010101011010101 0 1---------------------------------------------------8 0--1 0101010x 10101010 1 08 1--0 0101010110101010 10---------------------------------------------------这样就完成了两个寄存器8位的交换,上面的0--1表示上升沿、1--0表示下降沿,sdi、sdo相对于主机而言的。

[Note][Aurix2G_TC397_MCAL]SPI相关配置

![[Note][Aurix2G_TC397_MCAL]SPI相关配置](https://img.taocdn.com/s3/m/9f26e9a81b37f111f18583d049649b6648d7090d.png)

[Note][Aurix2G_TC397_MCAL]SPI相关配置0 SPI1 General1.1 SpiDriverSpiSystemClock在MCU模块配置的系统时钟。

主要参考McuQSPIFrequency和McuQspiClockSourceSelection1.2 Spi GeneralSpiCancelApi默认是禁⽤的SpiChannelBuffersAllowed (0 -> 2)⽤户可以决定采⽤哪⼀个buffer0:内部buffer1:外部buffer2:内部外部都可以默认是外部bufferSpiInitDeInitApiMode默认选择 SPI_MCAL_SUPERVISOR,因为driver的代码⼤多在supervisor下运⾏的SpiMulticoreCheckEnable多核检查是否开启。

我理解是看driver是否是在单核还是多核上运⾏。

SpiInitCheckApi默认关闭,如果APP有安全⽅⾯的需求和功能,则打开。

SpiRuntimeApiMode决定运⾏时,采⽤什么模式。

默认是SPI_MCAL_SUPERVISOR,理由同上。

SpiDevErrorDetect决定开发时错误是否被检测。

也就是DET。

在debug的时候默认打开。

SpiSafetyCheckEnable是否开启安全检查。

默认关闭,但是如果APP有安全⽅⾯的要求,必须打开。

SpiHwStatusApi决定 API Spi_GetHWUnitStatus是否启⽤。

主要决定,是否app需要了解硬件的状态。

SpiInterruptibleSeqAllowed默认关闭。

决定是否可以中断序列。

只有在SPI level 1or2时才有⽤。

SpiLevelDelivered决定启⽤什么通讯驱动。

1. L0:同步传输,也就是不适⽤DMA⽅式,只是采⽤CPU。

2. L1:异步传输,采⽤DMA⽅式。

3. L2:同时启⽤DMA和CPU两种⽅式。

spi工作原理

spi工作原理

SPI(Serial Peripheral Interface)是一种同步串行通信接口,用于在芯片之间传输数据。

它由主设备(Master)和从设备(Slave)组成,主设备控制通信的时钟信号,并发送和接收

数据。

SPI工作原理如下:

1. 时钟信号同步:SPI使用时钟信号将主设备和从设备保持同步。

主设备产生时钟信号,从设备根据时钟信号进行数据传输。

2. 主从选择:主设备通过选择特定的从设备使其处于工作模式。

可以通过片选引脚(Slave Select,SS)来选择从设备。

3. 数据传输:主设备发送一个数据位到从设备,从设备接收并响应主设备发送的数据位。

数据在时钟的上升沿或下降沿进行传输。

4. 数据帧:SPI通信以数据帧为基本传输单位。

数据帧由一个

数据位和可能的附加控制位组成。

数据位可以是单向的(只能由主设备发送)或双向的(主从设备都可以发送和接收)。

5. 传输模式:SPI支持多种传输模式,如CPOL(Clock Polarity)和CPHA(Clock Phase)。

CPOL决定时钟信号在空

闲状态时的电平,CPHA决定数据采样的时机。

6. 传输速率:SPI的传输速率由时钟信号的频率决定。

一般来说,SPI的传输速率比较高,可以达到几十兆赫兹甚至上百兆

赫兹。

需要注意的是,SPI是一种点对点的通信接口,每次传输只能有一个主设备和一个从设备进行通信。

如果需要与多个设备进行通信,需要使用多个SPI接口或者使用其他的通信协议。

spi工作模式

spi工作模式SPI(Serial Peripheral Interface)是一种同步串行数据总线,它是一种简单而高效的通信协议,常用于连接微控制器和外部设备,如传感器、存储器、显示屏等。

SPI工作模式是一种全双工的通信模式,它通过四根线进行通信,包括时钟线(SCLK)、数据输入线(MISO)、数据输出线(MOSI)和片选线(SS)。

SPI工作模式的时序图如下所示:在SPI通信中,主设备负责产生时钟信号,并通过片选线选择从设备。

主设备通过MOSI线发送数据给从设备,在同一时钟周期内,从设备也通过MISO线返回数据给主设备。

因此,SPI是一种全双工的通信方式,能够实现双向数据传输。

SPI通信的速度取决于时钟频率和数据传输的位数。

在SPI工作模式中,时钟信号的频率是可调的,可以根据实际需求进行设置。

一般来说,SPI的时钟频率可以达到几十MHz甚至上百MHz,因此具有较高的数据传输速度。

SPI通信的片选线(SS)用于选择从设备。

在多个从设备的情况下,主设备可以通过片选线选择要和其通信的从设备,其他从设备则处于非选中状态。

这样就可以实现多个从设备和一个主设备之间的通信,提高了系统的灵活性和可扩展性。

SPI通信具有较低的硬件成本,因为它只需要四根线就可以实现双向数据传输。

这使得SPI在嵌入式系统中得到广泛应用,例如单片机和外围设备之间的通信、传感器和控制器之间的数据传输等。

总的来说,SPI工作模式是一种简单而高效的通信方式,具有较高的数据传输速度和较低的硬件成本。

它在嵌入式系统中得到了广泛的应用,为微控制器和外部设备之间的通信提供了一种可靠的解决方案。

希望本文对SPI工作模式有所了解,并能在实际应用中发挥作用。

SPI时钟模式的配置

S P I时钟模式的配置 The latest revision on November 22, 2020【S P I基础知识简介】设备与设备之间通过某种硬件接口通讯,目前存在很多种接口,SPI接口是其中的一种。

SPI中分Master主设备和Slave从设备,数据发送都是由Master控制。

一个master可以接一个或多个slave。

常见用法是一个Master接一个slave,只需要4根线:SCLK:SerialClock,(串行)时钟MISO:MasterInSlaveOut,主设备输入,从设备输出MOSI:MasterOutSlaveIn,主设备输出,从设备输入SS:SlaveSelect,选中从设备,片选SPI由于接口相对简单(只需要4根线),用途算是比较广泛,主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

即一个SPI的Master通过SPI与一个从设备,即上述的那些Flash,ADC等,进行通讯。

而主从设备之间通过SPI进行通讯,首先要保证两者之间时钟SCLK要一致,互相要商量好了,要匹配,否则,就没法正常通讯了,即保证时序上的一致才可正常讯。

而这里的SPI中的时钟和相位,指的就是SCLk时钟的特性,即保证主从设备两者的时钟的特性一致了,以保证两者可以正常实现SPI通讯。

【SPI相关的缩写或说法】先简单说一下,关于SPI中一些常见的说法:SPI的极性Polarity和相位Phase,最常见的写法是CPOL和CPHA,不过也有一些其他写法,简单总结如下:(1)CKPOL(ClockPolarity)=CPOL=POL=Polarity=(时钟)极性(2)CKPHA(ClockPhase)=CPHA=PHA=Phase=(时钟)相位(3)SCK=SCLK=SPI的时钟(4)Edge=边沿,即时钟电平变化的时刻,即上升沿(risingedge)或者下降沿(fallingedge)对于一个时钟周期内,有两个edge,分别称为:Leadingedge=前一个边沿=第一个边沿,对于开始电压是1,那么就是1变成0的时候,对于开始电压是0,那么就是0变成1的时候;Trailingedge=后一个边沿=第二个边沿,对于开始电压是1,那么就是0变成1的时候(即在第一次1变成0之后,才可能有后面的0变成1),对于开始电压是0,那么就是1变成0的时候;本文采用如下用法:极性=CPOL相位=CPHASCLK=时钟第一个边沿和第二个边沿【SPI的相位和极性】CPOL和CPHA,分别都可以是0或时1,对应的四种组合就是:Mode0CPOL=0,CPHA=0Mode1CPOL=0,CPHA=1Mode2CPOL=1,CPHA=0Mode3CPOL=1,CPHA=1【CPOL极性】先说什么是SCLK时钟的空闲时刻,其就是当SCLK在数发送8个bit比特数据之前和之后的状态,于此对应的,SCLK在发送数据的时候,就是正常的工作的时候,有效active的时刻了。

单片机技术应用 SPI简介

SPI一、SPI简介SPI(Serial Peripheral Interface )是串行外围接口设备,是一种高速的,全双工,同步的通信总线,并且在芯片上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是处于这种简单易用的特性,现在越来越多的芯片集成了这种协议。

SPI 是一个环形总线结构,由ss(cs)、sck、sdi、sdo 构成,其时序其实很简单,主要是在sck 的控制下,两个双向移位寄存器进行数据交换。

因为是全双工同步通信,所以在传输数据时,左边主机的数据从移位寄存器进入MOSI线上进入右边的从机,并存入最低位,同时从机的最高位通过MISO传输到主机的最低位,当第二位数据进行发送时,最低位的数据会向左移一位并将新数据存入最低位。

二、通信协议1、物理层motorola公司首先提出的全双工三线同步串行外围接口,采用主从模式(Master Slave)架构;支持多slave 模式应用,一般仅支持单Master(单主机模式)。

管脚三线SPI:SCLK(时钟线),MISO(主机接收从机发送),MOSI(主机发送从机接收)四线SPI:CS(片选线),SCLK,MISO,MOSI片选:被选,确定该设备处于何种工作模式连接方式2、数据链路层SPI采用位协议,------高位在前,低位在后SPI有四种工作模式,SPI0 SPI1 SPI2 SPI3SPI 模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

SPI时钟模式的配置

SPI时钟模式的配置SPI(Serial Peripheral Interface)时钟模式是指在SPI通信中,时钟信号的工作模式。

SPI是一种同步的串行通信协议,在通信过程中,数据的传输是由时钟信号来驱动的。

不同的时钟模式可以定义时钟信号的相位和极性,以适应不同的通信需求。

时钟信号的相位(Clock Phase)定义了数据采样的时机,即在时钟信号的何处取样数据。

时钟信号的极性(Clock Polarity)定义了数据的有效电平是高电平还是低电平。

SPI协议中常用的时钟模式有四种,分别是Mode 0、Mode 1、Mode 2和Mode 3、以下是各个时钟模式的具体配置及特点:1. Mode 0:-时钟极性(CPOL):0-时钟相位(CPHA):0-特点:时钟信号在空闲状态为低电平,数据在时钟的下降沿采样,即数据在时钟信号的前半个周期准备好。

2. Mode 1:-时钟极性(CPOL):0-时钟相位(CPHA):1-特点:时钟信号在空闲状态为低电平,数据在时钟的上升沿采样,即数据在时钟信号的后半个周期准备好。

3. Mode 2:-时钟极性(CPOL):1-时钟相位(CPHA):0-特点:时钟信号在空闲状态为高电平,数据在时钟的上升沿采样。

4. Mode 3:-时钟极性(CPOL):1-时钟相位(CPHA):1-特点:时钟信号在空闲状态为高电平,数据在时钟的下降沿采样。

SPI的时钟模式需要根据具体的通信需求来配置。

通常在SPI设备的Datasheet中会指定默认的时钟模式,开发者需要根据SPI设备的要求来配置相应的时钟模式。

时钟模式的选择取决于设备的工作方式和通信时序的要求。

例如,如果SPI设备在时钟信号的上升沿将数据放置到总线上并在下降沿进行采样,则应选择Mode 0或Mode 2、如果设备在下降沿将数据放置到总线上并在上升沿进行采样,则应选择Mode 1或Mode 3。

SPI接口使用简介

AX1003 SPI接口使用简介AN-AX1000-005-V10-CH-SPI2006年8月版本 1.0 1 SPI协议简介SPI(Serial Peripheral Interface)是一种串行同步通讯协议,由一个主设备和一个或多个从设备组成,主设备启动一个与从设备的同步通讯,从而完成数据的交换。

SPI接口由SDI(串行数据输入),SDO(串行数据输出),SCK(串行移位时钟),CS (从使能信号)四种信号构成,CS决定了唯一的与主设备通信的从设备,如没有CS信号,则只能存在一个从设备,主设备通过产生移位时钟来发起通讯。

通讯时,数据由SDO输出,SDI输入,数据在时钟的上升或下降沿由SDO输出,在紧接着的下降或上升沿由SDI读入,这样经过8/16次时钟的改变,完成8/16位数据的传输。

2 AX1003的SPI接口AX1003有两个同步串行通讯接口,SSP1和SSP2,均支持SPI接口协议,其中SSP1支持SPI的主模式和从模式,SSP2支持SPI的主模式。

两个的接口的使用介绍分别如下。

3 SSP1的SPI使用SSP1支持四种模式的SPI,可以工作在主模式或从模式,它的接口和以下3条I/O复用。

Serial Data Out (SPIDO) – RD2Serial Data In (SPIDI) – RD3Serial Clock (SPICLK) – RD13.1 控制寄存器SPI的寄存器由SPI_CTRL(SPI控制寄存器)和SPI_BUF(SPI数据缓存)构成。

均为8位的寄存器。

SPI_CTRL可设置SPI的工作方式,时钟频率,触发SPI的发送或接收,产生通讯完成的标志,模块的使能和中断允许。

3.2 工作模式设置SPI的工作模式由SPI_CTRL的SPIEDGE和SPIIDST来设置,可配置成四种模式,其信号时序如图 3-1所示。

SPIIDST = 0,SPIEDGE = 0 时钟(SPICLK)在空闲时为低电平,在下降沿时采样SPIIDST = 0,SPIEDGE = 1 时钟(SPICLK)在空闲时为低电平,在上升沿时采样SPIIDST = 1,SPIEDGE = 0 时钟(SPICLK)在空闲时为高电平,在上升沿时采样SPIIDST = 1,SPIEDGE = 1 时钟(SPICLK)在空闲时为高电平,在下降沿时采样3.3 时钟频率设置SPI工作在主模式时需设置其时钟频率,可由SPI_CTRL的SPIFRQ来配置,可选择由系统时钟的64/16/4分频,或Timer2溢出时间的2分频来产生SPI的时钟。

基于SPI的实时时钟系统设计

工 业控制

基于 S I P 的实B t钟系统设计 -3 ,, J

许 荣

( 国船 舶 重 工 集 田公 司 第七 一 六 研 览 所 研 究 生 部 . 江 苏连 云港 2 2 0 ) 中 2 0 6

l引 言

随符城 m交通 ¨趋 娥忙 .蛆彳 简 的 定 配} 佾 控 『 f ’ j 制功能的交通情 控 制机.由于尤法满足我 嘲犬部 分地 交通拄制的婴求,在实 l r 逐渐 做1线 “ 波惜”控 : p : 绿 制平 I " 域 涮拄制1 机所特代 在实脱这两 类控 制的l 址 柄 中.时 址 一 } 个瓜蛭的参敬. l 为 蚓踏 u的绿 _ 倌 l 帽f 蔗的 州衙 餐参考缝 .g T米珊定 ; 世堑泉的错 f 时I f i 】

收徜 l嘲: 05 l一i 1 20 一 2 O J

维普资讯

应 操作 的 函数 指 针 ,并 把 控 制 枞 交 给 该 函数 。

① 读函数

函数 定 义 :

sai s ie t pi r (rc fe ttc sz s d su ti t l

J 午

3工 作 原 理

D 19 S 3 0有 I 6个内f 寄 存器 .每个街 , 器椰 有凄/ } l 5 f 惭个地址 分圳供滨/ 州十 ‘ 使川 .陲地址n 高 4f 地址 为0 讧 . 写地 址 的商 4仳 地址 为 8 ,低 4位 行村【 l 读/ I 叼 D 19 S 30内部寄存 器都需 . 发送 8批地址 J 选f 屯 十 占廿 教 J 匹l 0 n 发Ⅲ刚 步时 钟 信 . 数据绒 ( S 、 舌量 计4 0 s MO I MI S O) 1 【 制 J跳 卅 产乍 柯娥 觳 搬 蚌你持 3 n : 『 一 _ l 0 s以给 D I9 S 3 0接收 j 擞作蚶 A g R 2 0 H镪连续 发送 1 T l M90 6位

SD卡的SPI模式

SD卡的SPI模式7 SPI模式7.1 介绍SPI模式由一个由基于闪存SD存储卡提供的次要通信协议组成.此模式是SD存储卡协议的子集。

此接口在上电(CMD0)后的每一个复位命令期间被选择。

SPI标准只定义物理链接,而不提供数据传输协议。

SD存储卡SPI执行利用SD存储卡协议和命令集的子集。

7.2 SPI总线协定SD卡是基于命令和数据流,这些命令和数据流以一个起始位开始,以停止位结束的.SPI通道是面向字节的.每个命令或数据块都是由多个8位字节构成,且每个字节与CS片选信号对齐(例如:此长度是8时钟周期的倍数)。

类似于SD存储卡协议,SPI短信是由命令,响应和数据块环组成。

所有的通信都由主机控制,主机通过拉低CS来启动每个总线事务。

SPI模式下的响应行为有三个方面和SD模式不同:1、被选择的卡总是回应命令。

2、使用附加的(8位)响应结构。

3、当卡遇到一个数据检索问题时,它会用一个响应错误来回应(替换预期的数据块),而不是SD模式中的超时。

除了命令响应之外,每一个在写操作期间发送到卡的数据块将以一个特殊的数据响应令牌来被响应。

一个数据块可能和一个写块(WRITE_BL_LEN)一样大,也可能和一个信号字一样小。

部分块的读/写操作都被卡中CSD寄存器中所叙述的被选择的项使能。

7.2.1 模式选择SD卡从SD模式中唤醒。

如果CS信号在复位命令(CMD0)被接收期间被拉低,并进入空闲模式,如果认为是SD模式被需求则不会响应此命令,仍在SD模式下。

如果SPI模式被需求,则卡将会切换到SPI,且用SPI模式R1响应。

唯一返回SD模式的方法是进入上电周期。

在SPI模式下,SD存储卡协议状态机不被遵守。

所有的在SPI模式下被支持的SD存储卡命令总是可用的。

7.2.2 总线传输保护每个在总线上传输的SD存储卡令牌被CRC位保护。

在SPI模式下,SD存储卡提供一个非保护模式。

此模式使系统用可靠的数据链接来建立,以排除(否定)硬件或软件需要执行CRC 生成和校验功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SPI时钟模式的配置【SPI基础知识简介】设备与设备之间通过某种硬件接口通讯,目前存在很多种接口,SPI接口是其中的一种。

SPI中分Master主设备和Slave从设备,数据发送都是由Master控制。

—个master可以接一个或多个slave o常见用法是一个Master接一个slave,只需要4根线:SCLK : Serial Clock,(串行)时钟MISO : Master In Slave Out,主设备输入,从设备输出MOSI : Master Out Slave In,主设备输出,从设备输入SS: Slave Select,选中从设备,片选SPI由于接口相对简单(只需要4根线),用途算是比较广泛,主要应用在EEPROM, FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

即一个SPI的Master通过SPI与一个从设备,即上述的那些Flash, ADC等,进行通讯。

而主从设备之间通过SPI进行通讯,首先要保证两者之间时钟SCLK要一致,互相要商量好了,要匹配,否则,就没法正常通讯了,即保证时序上的一致才可正常讯。

而这里的SPI中的时钟和相位,指的就是SCLk时钟的特性,即保证主从设备两者的时钟的特性一致了,以保证两者可以正常实现SPI通讯。

【SPI相关的缩写或说法】先简单说一下,关于SPI中一些常见的说法:SPI的极性Polarity和相位Phase,最常见的写法是CPOL和CPHA,不过也有—些其他写法,简单总结如下:(1)CKPOL (Clock Polarity) = CPOL = POL = Polarity =(时钟)极性(2)CKPHA (Clock Phase) = CPHA = PHA = Phase =(时钟)相位(3)SCK二SCLK二SPI 的时钟⑷Edge=边沿,即时钟电平变化的时刻,即上升沿(rising edge)或者下降沿(falling edge)对于一个时钟周期内,有两个edge,分别称为:Leading edge=前一个边沿二第一个边沿,对于开始电压是1,那么就是1变成0 的时候,对于开始电压是0,那么就是0变成1的时候;Trailing edge二后一个边沿二第二个边沿,对于开始电压是1,那么就是0变成1 的时候(即在第一次1变成0之后,才可能有后面的0变成1),对于开始电压是0,那么就是1变成0的时候;本文采用如下用法•极性二CPOL相位=CPHASCLK二时钟第一个边沿和第二个边沿[SPI的相位和极性】CPOL和CPHA,分别都可以是0或时1,对应的四种组合就是:Mode 0 CPOL=0, CPHA=OMode 1 CPOL=0, CPHA=1Mode 2 CPOL=1, CPHA=OMode 3 CPOL=1, CPHA=1[CPOL极性】先说什么是SCLK时钟的空闲时刻,其就是当SCLK在数发送8个bit比特数据之前和之后的状态,于此对应的,SCLK在发送数据的时候,就是正常的工作的时候,有效active的时刻了。

先说英文,其精简解释为:Clock Polarity = IDLE state of SCK O再用中文详解:SPI的CPOL,表示当SCLK空闲idle的时候,其电平的值是低电平0还是高电平1 :CPOL=0,时钟空闲idle时候的电平是低电平,所以当SCLK有效的时候,就是高电平,就是所谓的active-high ;CPOL=1,时钟空闲idle时候的电平是高电平,所以当SCLK有效的时候,就是低电平,就是所谓的active-low ;[CPHA相位】首先说明一点,capture strobe = latch = read = sample,都是表示数据采样,数据有效的时刻。

相位,对应着数据采样是在第几个边沿(edge),是第一个边沿还是第二个边沿,0对应着第一个边沿,1对应着第二个边沿。

对于:CPHA=O,表示第一个边沿:对于CPOL=0, idle时候的是低电平,第一个边沿就是从低变到高.所以是上升沿;对于CPOL=1, idle时候的是高电平,第一个边沿就是从高变到低,所以是下降沿;CPHA=1.表示第二个边沿:对于CPOL=0, idle时候的是低电平,第二个边沿就是从高变到低,所以是下降沿;对于CPOL=1, idle时候的是高电平,第一个边沿就是从低变到高.所以是上升沿;此处,再多解释一下可能会遇到的CKP和CKE,其是Microchip的PIC系列芯片中的说法。

(1) CKP 是Clock Polarity Select,就是极性二CPOL :CKP,虽然名字和CPOL不一样,但是都是指时钟相位的选择,定义也—样:CKP: Clock Polarity Select bit1 = Idle state for clock (CK) is a high level0 = Idle state for clock (CK) is a low level所以不多解释。

(2) CKE 是Clock Edge Select,就是相ft=CPHA :CKE: SPI Clock Edge Select bit1 = Transmit occurs on transition from active to Idle clock state0 = Transmit occurs on transition from Idle to active clock state意思是1=(数据)传输发生在时钟从有效状态转到空闲状态的那一时刻0=(数据)传输发生在时钟从空闲状态转到有效状态的那一时刻其中,数据传输的时刻,即图中标出的“数据transmit传输的时刻”,很明显,该时刻是一个时钟和下一个时钟之间交界的地方,对应的不论是上升沿还是下降沿,都与我们前面提到的CPHA=数据采样的时刻,的边沿方向所相反。

所以,此处的CKE,正好与CPHA相反。

所以,CKP和CKE所对应的取值的含义为:When CKP = 0:CKE=1 => Data transmitted on rising edge of SCKCKE=0 => Data transmitted on falling edge of SCKWhen CKP = 1:CKE=1 => Data transmitted on falling edge of SCKCKE=0 => Data transmitted on rising edge of SCK【如何看懂和记忆CPOL和CPHA]所以,关于在其他地方介绍的,看似多么复杂难懂难记忆的CPOL和CPHA, 其实经过上面解释,就肯容易看懂了:去看时序图,如果起始的始终SCLK的电平是0,那么CPOL=0.如果是1,那么CPOL=1, 然后看数据采样时刻,即时序图数据线上的数据那个矩形区域的中间所对应的位置,对应到上面SCLK时钟的位置,对应着是第一个边沿或是第二个边沿,即CPHA是0或1。

(对应的是上升沿还是还是下降沿,要根据对应的CPOL 的值,才能确定)。

即:(1)如何判断CPOL : SCLK的空闲时候的电压,是0还是1,决定了CPOL是0还是1 ;(2)如何判断CPHA :而数据采样时刻对应着的SCLK的电平,是第一个边沿还是第二个边沿,对应着CPHA为0还是1。

SCLK的极性,相位,边沿之间的内在逻辑关系SCLK空闲时刻电压低电平CPOL = 0高电平CPOL = 1数据采样时刻,SCLK的edge是第一个还是第二个第一个边沿CPHA = 0上升沿(开始的电平是低电压0,而第一个边沿,只能是从0变到1,即上升沿)下降沿第二个边沿CPHA= 1下降沿上升沿(开始电平是高电平1,第二个边沿,肯定是从低电平0变到高电平1,因为第一个边沿肯定是从高电平1,变到低电平0)【软件中如何设置SPI的极性和相位】SPI分主设备和从设备,两者通过SPI协议通讯。

而设置SPI的模式,是从设备的模式.决定了主设备的模式。

所以要先去搞懂从设备的SPI是何种模式,然后再将主设备的SPI的模式,设置和从设备相同的模式,即可正常通讯。

对于从设备的SPI是什么模式,有两种:(1)固定的,有SPI从设备硬件决定的SPI从设备,具体是什么模式,相关的datasheet中会有描述,需要自己去datasheet中找到相关的描述,即:关于SPI从设备,在空闲的时候,是高电平还是低电平,即决定了CPOL是0还是1 ;然后再找到关于设备是在上升沿还是下降沿去采样数据,这样就是,在定了CPOL的值的前提下,对应着可以推算出CPHA是0还是1 了。

举例1 :CC2500 - Low-Cost Low-Power GHz RF Transceiver 的datasheet 中SPI 的时序图从图中可以看到,最开始的SCLK和结束时候的SCLK,即空闲时刻的SCLK,是低电平,推导岀CPOL=0,然后可以看到数据采样的时候,即数据最中间的那一点,对应的是SCLK的第一个边沿,所以CPHA=O (此时对应的是上升沿)。

举例2 :SSD1289 - 240 RGB x 320 TFT LCD Controller Driver 的datasheet 中提到:U SDI is shifted into 8-bit shift register on every rising edge of SCK in the order of data bit 7, data bit 6 ... data bit 0・"意思是,数据是在上升沿采样,所以可以断定是CPOL=0, CPHA=0,或者CPOL=l t CPHA=1的模式,但是至于是哪种模式。

按理来说,接下来应该再去确定SCLK空闲时候是高电平还是低电平,用以确定CPOL是0还是1,但是datasheet中没有提到这点。

所以,此处,目前不太确定,是两种模式都支持,还是需要额外找证据却确定CPOL是0还是1.(2)可配置的,由软件自己设定从设备也是一个SPI控制器,4种模式都支持,此时只要自己设置为某种模式即可。

然后知道了从设备的模式后,再去将SPI主设备的模式,设置为和从设备模式一样,即可。

对于如何配置SPI的CPOL和CPHA的话,不多细说,多数都是直接去写对应的SPI控制器中对应寄存器中的CPOL和CPHA那两位,写0或写1即可。

举例:此处遇到的C8051F347中的SPI就是一个SPI的controller控制器,即支持软件配置CPOL和CPHA的值,四种模式都支持,此处C8051F347作为SPI从设备,设置了CPOL=1, CPHA=O的模式因此,此处对应主芯片Blackfin F537 中的SPI控制器,作为Master主设备其SPI的模式也要设置为CPOL=1, CPHA=0o【待解决问题】对于软件去如何设置主设备(和从设备)的CPOL和CPHA的值,是搞懂了,知道两者要匹配才可以正常通讯,但是对于CPOL和CPHA这四种模式,不同的模式之间,相对来说有何优缺点,比如是否哪种模式更稳定,数据更不容易出错等等,还是不清楚【总结】1. IT方面的资料,国内的,还是把问题讲明白的太少,想搞懂问题,还是得去找英文的。