SPI时钟模式的配置

SPI协议详解

【转】SPI协议详解SPI总线协议及SPI时序图详解2009-11-10 22:10SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

上升沿发送、下降沿接收、高位先发送。

上升沿到来的时候,sdo上的电平将被发送到从设备的寄存器中。

下降沿到来的时候,sdi上的电平将被接收到主设备的寄存器中。

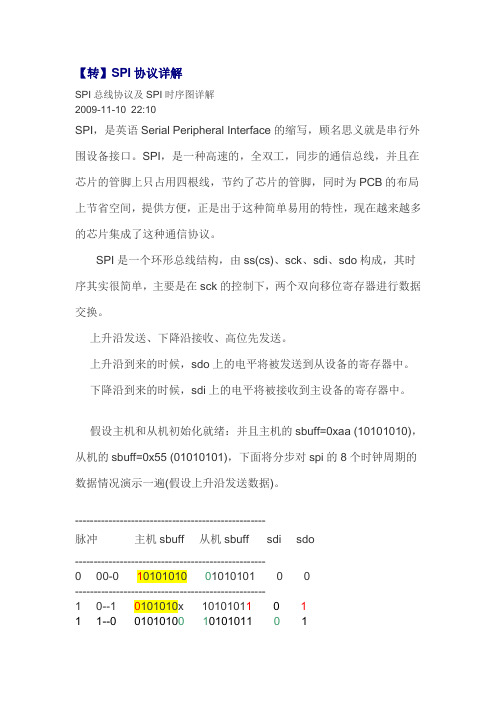

假设主机和从机初始化就绪:并且主机的sbuff=0xaa (10101010),从机的sbuff=0x55 (01010101),下面将分步对spi的8个时钟周期的数据情况演示一遍(假设上升沿发送数据)。

---------------------------------------------------脉冲主机sbuff 从机sbuff sdi sdo---------------------------------------------------0 00-0 10101010 01010101 0 0---------------------------------------------------1 0--1 0101010x 101010110 11 1--0 0101010010101011 0 1---------------------------------------------------2 0--1 1010100x 01010110 1 02 1--0 1010100101010110 10---------------------------------------------------3 0--1 0101001x 101011010 13 1--0 0101001010101101 0 1---------------------------------------------------4 0--1 1010010x 01011010 1 04 1--0 1010010101011010 10---------------------------------------------------5 0--1 0100101x 101101010 15 1--0 0100101010110101 0 1---------------------------------------------------6 0--1 1001010x 01101010 1 06 1--0 1001010101101010 10---------------------------------------------------7 0--1 0010101x 110101010 17 1--0 0010101011010101 0 1---------------------------------------------------8 0--1 0101010x 10101010 1 08 1--0 0101010110101010 10---------------------------------------------------这样就完成了两个寄存器8位的交换,上面的0--1表示上升沿、1--0表示下降沿,sdi、sdo相对于主机而言的。

SPI时钟模式的配置

S P I基础知识简介设备与设备之间通过某种硬件接口通讯;目前存在很多种接口;SPI接口是其中的一种..SPI中分Master主设备和Slave从设备;数据发送都是由Master控制..一个master可以接一个或多个slave..常见用法是一个Master接一个slave;只需要4根线:SCLK:SerialClock;串行时钟MISO:MasterInSlaveOut;主设备输入;从设备输出MOSI:MasterOutSlaveIn;主设备输出;从设备输入SS:SlaveSelect;选中从设备;片选SPI由于接口相对简单只需要4根线;用途算是比较广泛;主要应用在EEPROM;FLASH;实时时钟;AD转换器;还有数字信号处理器和数字信号解码器之间..即一个SPI的Master通过SPI与一个从设备;即上述的那些Flash;ADC等;进行通讯..而主从设备之间通过SPI进行通讯;首先要保证两者之间时钟SCLK要一致;互相要商量好了;要匹配;否则;就没法正常通讯了;即保证时序上的一致才可正常讯..而这里的SPI中的时钟和相位;指的就是SCLk时钟的特性;即保证主从设备两者的时钟的特性一致了;以保证两者可以正常实现SPI通讯..SPI相关的缩写或说法先简单说一下;关于SPI中一些常见的说法:SPI的极性Polarity和相位Phase;最常见的写法是CPOL和CPHA;不过也有一些其他写法;简单总结如下:1CKPOLClockPolarity=CPOL=POL=Polarity=时钟极性2CKPHAClockPhase=CPHA=PHA=Phase=时钟相位3SCK=SCLK=SPI的时钟4Edge=边沿;即时钟电平变化的时刻;即上升沿risingedge或者下降沿fallingedge对于一个时钟周期内;有两个edge;分别称为:Leadingedge=前一个边沿=第一个边沿;对于开始电压是1;那么就是1变成0的时候;对于开始电压是0;那么就是0变成1的时候;Trailingedge=后一个边沿=第二个边沿;对于开始电压是1;那么就是0变成1的时候即在第一次1变成0之后;才可能有后面的0变成1;对于开始电压是0;那么就是1变成0的时候;本文采用如下用法:极性=CPOL相位=CPHASCLK=时钟第一个边沿和第二个边沿SPI的相位和极性CPOL和CPHA;分别都可以是0或时1;对应的四种组合就是:Mode0CPOL=0;CPHA=0Mode1CPOL=0;CPHA=1Mode2CPOL=1;CPHA=0Mode3CPOL=1;CPHA=1CPOL极性先说什么是SCLK时钟的空闲时刻;其就是当SCLK在数发送8个bit比特数据之前和之后的状态;于此对应的;SCLK在发送数据的时候;就是正常的工作的时候;有效active的时刻了..先说英文;其精简解释为:ClockPolarity=IDLEstateofSCK..再用中文详解:SPI的CPOL;表示当SCLK空闲idle的时候;其电平的值是低电平0还是高电平1:CPOL=0;时钟空闲idle时候的电平是低电平;所以当SCLK有效的时候;就是高电平;就是所谓的active-high;CPOL=1;时钟空闲idle时候的电平是高电平;所以当SCLK有效的时候;就是低电平;就是所谓的active-low;CPHA相位首先说明一点;capturestrobe=latch=read=sample;都是表示数据采样;数据有效的时刻..相位;对应着数据采样是在第几个边沿edge;是第一个边沿还是第二个边沿;0对应着第一个边沿;1对应着第二个边沿..对于:CPHA=0;表示第一个边沿:对于CPOL=0;idle时候的是低电平;第一个边沿就是从低变到高;所以是上升沿;对于CPOL=1;idle时候的是高电平;第一个边沿就是从高变到低;所以是下降沿;CPHA=1;表示第二个边沿:对于CPOL=0;idle时候的是低电平;第二个边沿就是从高变到低;所以是下降沿;对于CPOL=1;idle时候的是高电平;第一个边沿就是从低变到高;所以是上升沿;此处;再多解释一下可能会遇到的CKP和CKE;其是Microchip的PIC系列芯片中的说法.. 1CKP是ClockPolaritySelect;就是极性=CPOL:CKP;虽然名字和CPOL不一样;但是都是指时钟相位的选择;定义也一样:CKP:ClockPolaritySelectbit1=IdlestateforclockCKisahighlevel0=IdlestateforclockCKisalowlevel所以不多解释..2CKE是ClockEdgeSelect;就是相位=CPHA:CKE:SPIClockEdgeSelectbit1=TransmitoccursontransitionfromactivetoIdleclockstate0=TransmitoccursontransitionfromIdletoactiveclockstate意思是1=数据传输发生在时钟从有效状态转到空闲状态的那一时刻0=数据传输发生在时钟从空闲状态转到有效状态的那一时刻其中;数据传输的时刻;即图中标出的“数据transmit传输的时刻”;很明显;该时刻是一个时钟和下一个时钟之间交界的地方;对应的不论是上升沿还是下降沿;都与我们前面提到的CPHA=数据采样的时刻;的边沿方向所相反..所以;此处的CKE;正好与CPHA相反..所以;CKP和CKE所对应的取值的含义为:WhenCKP=0:CKE=1=>DatatransmittedonrisingedgeofSCKCKE=0=>DatatransmittedonfallingedgeofSCKWhenCKP=1:CKE=1=>DatatransmittedonfallingedgeofSCKCKE=0=>DatatransmittedonrisingedgeofSCK如何看懂和记忆CPOL和CPHA所以;关于在其他地方介绍的;看似多么复杂难懂难记忆的CPOL和CPHA;其实经过上面解释;就肯容易看懂了:去看时序图;如果起始的始终SCLK的电平是0;那么CPOL=0;如果是1;那么CPOL=1;然后看数据采样时刻;即时序图数据线上的数据那个矩形区域的中间所对应的位置;对应到上面SCLK时钟的位置;对应着是第一个边沿或是第二个边沿;即CPHA是0或1..对应的是上升沿还是还是下降沿;要根据对应的CPOL的值;才能确定..即:1如何判断CPOL:SCLK的空闲时候的电压;是0还是1;决定了CPOL是0还是1;2如何判断CPHA:而数据采样时刻对应着的SCLK的电平;是第一个边沿还是第二个边沿;对应着CPHA为0还是1..SCLK的极性;相位;边沿之间的内在逻辑关系SCLK空闲时刻电压低电平CPOL=0高电平CPOL=1数据采样时刻;SCLK的edge是第一个还是第二个第一个边沿CPHA=0上升沿开始的电平是低电压0;而第一个边沿;只能是从0变到1;即上升沿下降沿第二个边沿CPHA=1下降沿上升沿开始电平是高电平1;第二个边沿;肯定是从低电平0变到高电平1;因为第一个边沿肯定是从高电平1;变到低电平0软件中如何设置SPI的极性和相位SPI分主设备和从设备;两者通过SPI协议通讯..而设置SPI的模式;是从设备的模式;决定了主设备的模式..所以要先去搞懂从设备的SPI是何种模式;然后再将主设备的SPI的模式;设置和从设备相同的模式;即可正常通讯..对于从设备的SPI是什么模式;有两种:1固定的;有SPI从设备硬件决定的SPI从设备;具体是什么模式;相关的datasheet中会有描述;需要自己去datasheet中找到相关的描述;即:关于SPI从设备;在空闲的时候;是高电平还是低电平;即决定了CPOL是0还是1;然后再找到关于设备是在上升沿还是下降沿去采样数据;这样就是;在定了CPOL的值的前提下;对应着可以推算出CPHA是0还是1了..举例1:CC2500-Low-CostLow-Power2.4GHzRFTransceiver的datasheet中SPI的时序图从图中可以看到;最开始的SCLK和结束时候的SCLK;即空闲时刻的SCLK;是低电平;推导出CPOL=0;然后可以看到数据采样的时候;即数据最中间的那一点;对应的是SCLK的第一个边沿;所以CPHA=0此时对应的是上升沿..举例2:SSD1289-240RGBx320TFTLCDControllerDriver的datasheet中提到:“SDIisshiftedinto8-bitshiftregisteroneveryrisingedgeofSCKintheorderofdatabit7 ;databit6……databit0.”意思是;数据是在上升沿采样;所以可以断定是CPOL=0;CPHA=0;或者CPOL=1;CPHA=1的模式;但是至于是哪种模式..按理来说;接下来应该再去确定SCLK空闲时候是高电平还是低电平;用以确定CPOL是0还是1;但是datasheet中没有提到这点..所以;此处;目前不太确定;是两种模式都支持;还是需要额外找证据却确定CPOL是0还是1. 2可配置的;由软件自己设定从设备也是一个SPI控制器;4种模式都支持;此时只要自己设置为某种模式即可..然后知道了从设备的模式后;再去将SPI主设备的模式;设置为和从设备模式一样;即可..对于如何配置SPI的CPOL和CPHA的话;不多细说;多数都是直接去写对应的SPI控制器中对应寄存器中的CPOL和CPHA那两位;写0或写1即可..举例:此处遇到的C8051F347中的SPI就是一个SPI的controller控制器;即支持软件配置CPOL 和CPHA的值;四种模式都支持;此处C8051F347作为SPI从设备;设置了CPOL=1;CPHA=0的模式;因此;此处对应主芯片BlackfinF537中的SPI控制器;作为Master主设备;其SPI的模式也要设置为CPOL=1;CPHA=0..待解决问题对于软件去如何设置主设备和从设备的CPOL和CPHA的值;是搞懂了;知道两者要匹配才可以正常通讯;但是对于CPOL和CPHA这四种模式;不同的模式之间;相对来说有何优缺点;比如是否哪种模式更稳定;数据更不容易出错等等;还是不清楚总结1.IT方面的资料;国内的;还是把问题讲明白的太少;想搞懂问题;还是得去找英文的..2.有问题;指望别人;还是不行的;凡事还是得指望自己;才有用..。

[Note][Aurix2G_TC397_MCAL]SPI相关配置

![[Note][Aurix2G_TC397_MCAL]SPI相关配置](https://img.taocdn.com/s3/m/9f26e9a81b37f111f18583d049649b6648d7090d.png)

[Note][Aurix2G_TC397_MCAL]SPI相关配置0 SPI1 General1.1 SpiDriverSpiSystemClock在MCU模块配置的系统时钟。

主要参考McuQSPIFrequency和McuQspiClockSourceSelection1.2 Spi GeneralSpiCancelApi默认是禁⽤的SpiChannelBuffersAllowed (0 -> 2)⽤户可以决定采⽤哪⼀个buffer0:内部buffer1:外部buffer2:内部外部都可以默认是外部bufferSpiInitDeInitApiMode默认选择 SPI_MCAL_SUPERVISOR,因为driver的代码⼤多在supervisor下运⾏的SpiMulticoreCheckEnable多核检查是否开启。

我理解是看driver是否是在单核还是多核上运⾏。

SpiInitCheckApi默认关闭,如果APP有安全⽅⾯的需求和功能,则打开。

SpiRuntimeApiMode决定运⾏时,采⽤什么模式。

默认是SPI_MCAL_SUPERVISOR,理由同上。

SpiDevErrorDetect决定开发时错误是否被检测。

也就是DET。

在debug的时候默认打开。

SpiSafetyCheckEnable是否开启安全检查。

默认关闭,但是如果APP有安全⽅⾯的要求,必须打开。

SpiHwStatusApi决定 API Spi_GetHWUnitStatus是否启⽤。

主要决定,是否app需要了解硬件的状态。

SpiInterruptibleSeqAllowed默认关闭。

决定是否可以中断序列。

只有在SPI level 1or2时才有⽤。

SpiLevelDelivered决定启⽤什么通讯驱动。

1. L0:同步传输,也就是不适⽤DMA⽅式,只是采⽤CPU。

2. L1:异步传输,采⽤DMA⽅式。

3. L2:同时启⽤DMA和CPU两种⽅式。

spi工作原理

spi工作原理

SPI(Serial Peripheral Interface)是一种同步串行通信接口,用于在芯片之间传输数据。

它由主设备(Master)和从设备(Slave)组成,主设备控制通信的时钟信号,并发送和接收

数据。

SPI工作原理如下:

1. 时钟信号同步:SPI使用时钟信号将主设备和从设备保持同步。

主设备产生时钟信号,从设备根据时钟信号进行数据传输。

2. 主从选择:主设备通过选择特定的从设备使其处于工作模式。

可以通过片选引脚(Slave Select,SS)来选择从设备。

3. 数据传输:主设备发送一个数据位到从设备,从设备接收并响应主设备发送的数据位。

数据在时钟的上升沿或下降沿进行传输。

4. 数据帧:SPI通信以数据帧为基本传输单位。

数据帧由一个

数据位和可能的附加控制位组成。

数据位可以是单向的(只能由主设备发送)或双向的(主从设备都可以发送和接收)。

5. 传输模式:SPI支持多种传输模式,如CPOL(Clock Polarity)和CPHA(Clock Phase)。

CPOL决定时钟信号在空

闲状态时的电平,CPHA决定数据采样的时机。

6. 传输速率:SPI的传输速率由时钟信号的频率决定。

一般来说,SPI的传输速率比较高,可以达到几十兆赫兹甚至上百兆

赫兹。

需要注意的是,SPI是一种点对点的通信接口,每次传输只能有一个主设备和一个从设备进行通信。

如果需要与多个设备进行通信,需要使用多个SPI接口或者使用其他的通信协议。

spi工作模式

spi工作模式SPI(Serial Peripheral Interface)是一种同步串行数据总线,它是一种简单而高效的通信协议,常用于连接微控制器和外部设备,如传感器、存储器、显示屏等。

SPI工作模式是一种全双工的通信模式,它通过四根线进行通信,包括时钟线(SCLK)、数据输入线(MISO)、数据输出线(MOSI)和片选线(SS)。

SPI工作模式的时序图如下所示:在SPI通信中,主设备负责产生时钟信号,并通过片选线选择从设备。

主设备通过MOSI线发送数据给从设备,在同一时钟周期内,从设备也通过MISO线返回数据给主设备。

因此,SPI是一种全双工的通信方式,能够实现双向数据传输。

SPI通信的速度取决于时钟频率和数据传输的位数。

在SPI工作模式中,时钟信号的频率是可调的,可以根据实际需求进行设置。

一般来说,SPI的时钟频率可以达到几十MHz甚至上百MHz,因此具有较高的数据传输速度。

SPI通信的片选线(SS)用于选择从设备。

在多个从设备的情况下,主设备可以通过片选线选择要和其通信的从设备,其他从设备则处于非选中状态。

这样就可以实现多个从设备和一个主设备之间的通信,提高了系统的灵活性和可扩展性。

SPI通信具有较低的硬件成本,因为它只需要四根线就可以实现双向数据传输。

这使得SPI在嵌入式系统中得到广泛应用,例如单片机和外围设备之间的通信、传感器和控制器之间的数据传输等。

总的来说,SPI工作模式是一种简单而高效的通信方式,具有较高的数据传输速度和较低的硬件成本。

它在嵌入式系统中得到了广泛的应用,为微控制器和外部设备之间的通信提供了一种可靠的解决方案。

希望本文对SPI工作模式有所了解,并能在实际应用中发挥作用。

SPI时钟模式的配置

S P I时钟模式的配置 The latest revision on November 22, 2020【S P I基础知识简介】设备与设备之间通过某种硬件接口通讯,目前存在很多种接口,SPI接口是其中的一种。

SPI中分Master主设备和Slave从设备,数据发送都是由Master控制。

一个master可以接一个或多个slave。

常见用法是一个Master接一个slave,只需要4根线:SCLK:SerialClock,(串行)时钟MISO:MasterInSlaveOut,主设备输入,从设备输出MOSI:MasterOutSlaveIn,主设备输出,从设备输入SS:SlaveSelect,选中从设备,片选SPI由于接口相对简单(只需要4根线),用途算是比较广泛,主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

即一个SPI的Master通过SPI与一个从设备,即上述的那些Flash,ADC等,进行通讯。

而主从设备之间通过SPI进行通讯,首先要保证两者之间时钟SCLK要一致,互相要商量好了,要匹配,否则,就没法正常通讯了,即保证时序上的一致才可正常讯。

而这里的SPI中的时钟和相位,指的就是SCLk时钟的特性,即保证主从设备两者的时钟的特性一致了,以保证两者可以正常实现SPI通讯。

【SPI相关的缩写或说法】先简单说一下,关于SPI中一些常见的说法:SPI的极性Polarity和相位Phase,最常见的写法是CPOL和CPHA,不过也有一些其他写法,简单总结如下:(1)CKPOL(ClockPolarity)=CPOL=POL=Polarity=(时钟)极性(2)CKPHA(ClockPhase)=CPHA=PHA=Phase=(时钟)相位(3)SCK=SCLK=SPI的时钟(4)Edge=边沿,即时钟电平变化的时刻,即上升沿(risingedge)或者下降沿(fallingedge)对于一个时钟周期内,有两个edge,分别称为:Leadingedge=前一个边沿=第一个边沿,对于开始电压是1,那么就是1变成0的时候,对于开始电压是0,那么就是0变成1的时候;Trailingedge=后一个边沿=第二个边沿,对于开始电压是1,那么就是0变成1的时候(即在第一次1变成0之后,才可能有后面的0变成1),对于开始电压是0,那么就是1变成0的时候;本文采用如下用法:极性=CPOL相位=CPHASCLK=时钟第一个边沿和第二个边沿【SPI的相位和极性】CPOL和CPHA,分别都可以是0或时1,对应的四种组合就是:Mode0CPOL=0,CPHA=0Mode1CPOL=0,CPHA=1Mode2CPOL=1,CPHA=0Mode3CPOL=1,CPHA=1【CPOL极性】先说什么是SCLK时钟的空闲时刻,其就是当SCLK在数发送8个bit比特数据之前和之后的状态,于此对应的,SCLK在发送数据的时候,就是正常的工作的时候,有效active的时刻了。

SPI-4接口的时钟方案

SPI-4接口的时钟方案

面对当今复杂的FPGA 设计,时钟是至关重要的,工程的成败往往取决

于它。

而对于SPI-0 接口设计来说,由于输入时钟高于311 MHz,并且是双沿

采样的,所以时钟设计显得更加重要。

对于Xilinx Virtex-5 器件来说,内部提

供了全局时钟和区域时钟两大时钟网络,我们分别利用这两大资源来设计SPI-

4 的时钟方案。

全局时钟如图1 所示,区域时钟如图2 所示。

其中,RDCLK

是Sink Core 的输入时钟,Sysclk 为Source Core 的参考时钟,TSCLK 为Source Core 的状态信息通道的输入时钟,用户可以根据实际情况来选择。

图1 全局时钟

图2 区域时钟

此外,TDCLK 由SysClkO_GP 经过FPGA 的IO 模块内的ODDR 输出。

tips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。

spi时序图怎么看?spi时序图详解分析

spi时序图怎么看?spi时序图详解分析https:///is/ecFhoa5/我做产品的时候,最怕就是做IIC和SPI的通信。

这两种协议时序哪怕是延时时间有误差,都有可能导致通信不上。

出现问题的时候,如果没设备也很难排查问题到底出在哪⾥。

有时候这个产品写好的时序程序,换⼀个单⽚机⽤同⼀个程序移植过去就不⾏了。

⽽且很多公司都没有设备可以调试这些协议,⼤多数时候都是完全靠蒙。

今天就拿新⼿⽐较头痛的SPI来进⾏时序图的分析和讲解,看不懂你打我!我记得第⼀次SPI通讯的时候,完全是照抄⽹络上的程序,因为芯⽚⼿册的时序图看起来太可怕了,根本看不懂。

后⾯各种模拟时序写多了,才有了经验,然后⽤经验去理解数据⼿册以及⽹络上的教程。

很多新⼿看各种数据⼿册和教程被吓到了,其实很多时候不是你的问题,⽽是数据⼿册和教程写得太学术化了。

举个例⼦,就像SPI协议⽤CPOL和CPHA真值表来选择不同的模式。

因为在很多SPI接⼝芯⽚的数据⼿册根本没提CPOL和CPHA这两个东西,那要怎么知道芯⽚的通讯模式?其实是要我们⾃⼰根据芯⽚⼿册的时序图去分析模式的,⽽不会直接告诉你是⽤的哪个模式。

所以在看时序之前,我们先要了解CPOL和CPHA到底有啥区别。

CPHA是⽤来控制数据是在第⼀个跳变沿还是第⼆个跳变沿采集的。

通过上图可以看到:CPHA=0的时候,数据是在第⼀个跳变沿的时候就会被采集。

CPHA=1的时候,数据是在第⼆个跳变沿的时候才会被采集。

那问题来了,到底是上升沿还是下降沿采集?这个就由CPOL来决定了:CPOL=0的时候是上升沿采集。

CPOL=1的时候是下降沿采集。

除此以外,CPOL还决定了我们时钟线SCLK空闲时的状态。

除此以外,CPOL还决定了我们时钟线SCLK空闲时的状态。

CPOL=0的时候表⽰SCLK在空闲时为低电平。

CPOL=1的时候表⽰SCLK在空闲时为⾼电平。

Ok,明⽩了这个,我们再分析4种模式的时序图。

1. 模式0(CPOL=0 CPOL=0)CPOL = 0:时钟线空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿CPHA = 0:数据在第1个跳变沿(上升沿)采样时序图如下:2.模式1(CPOL=0 CPOL=1)CPOL = 0:空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿CPHA = 1:数据在第2个跳变沿(下降沿)采样时序图如下:3.模式2(CPOL=1 CPOL=0)CPOL = 1:空闲时是⾼电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿CPHA = 0:数据在第1个跳变沿(下降沿)采样时序图如下:4.模式3(CPOL=1 CPOL=1)CPOL = 1:空闲时是⾼电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿CPHA = 1:数据在第2个跳变沿(上升沿)采样时序图如下:这样看是不是对4种模式的区别⽐较清晰了?下⾯,我们再拿OLED的驱动芯⽚SSD1306的时序图来作为实战讲解。

单片机技术应用 SPI简介

SPI一、SPI简介SPI(Serial Peripheral Interface )是串行外围接口设备,是一种高速的,全双工,同步的通信总线,并且在芯片上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是处于这种简单易用的特性,现在越来越多的芯片集成了这种协议。

SPI 是一个环形总线结构,由ss(cs)、sck、sdi、sdo 构成,其时序其实很简单,主要是在sck 的控制下,两个双向移位寄存器进行数据交换。

因为是全双工同步通信,所以在传输数据时,左边主机的数据从移位寄存器进入MOSI线上进入右边的从机,并存入最低位,同时从机的最高位通过MISO传输到主机的最低位,当第二位数据进行发送时,最低位的数据会向左移一位并将新数据存入最低位。

二、通信协议1、物理层motorola公司首先提出的全双工三线同步串行外围接口,采用主从模式(Master Slave)架构;支持多slave 模式应用,一般仅支持单Master(单主机模式)。

管脚三线SPI:SCLK(时钟线),MISO(主机接收从机发送),MOSI(主机发送从机接收)四线SPI:CS(片选线),SCLK,MISO,MOSI片选:被选,确定该设备处于何种工作模式连接方式2、数据链路层SPI采用位协议,------高位在前,低位在后SPI有四种工作模式,SPI0 SPI1 SPI2 SPI3SPI 模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

SPI时钟模式的配置

SPI时钟模式的配置SPI(Serial Peripheral Interface)时钟模式是指在SPI通信中,时钟信号的工作模式。

SPI是一种同步的串行通信协议,在通信过程中,数据的传输是由时钟信号来驱动的。

不同的时钟模式可以定义时钟信号的相位和极性,以适应不同的通信需求。

时钟信号的相位(Clock Phase)定义了数据采样的时机,即在时钟信号的何处取样数据。

时钟信号的极性(Clock Polarity)定义了数据的有效电平是高电平还是低电平。

SPI协议中常用的时钟模式有四种,分别是Mode 0、Mode 1、Mode 2和Mode 3、以下是各个时钟模式的具体配置及特点:1. Mode 0:-时钟极性(CPOL):0-时钟相位(CPHA):0-特点:时钟信号在空闲状态为低电平,数据在时钟的下降沿采样,即数据在时钟信号的前半个周期准备好。

2. Mode 1:-时钟极性(CPOL):0-时钟相位(CPHA):1-特点:时钟信号在空闲状态为低电平,数据在时钟的上升沿采样,即数据在时钟信号的后半个周期准备好。

3. Mode 2:-时钟极性(CPOL):1-时钟相位(CPHA):0-特点:时钟信号在空闲状态为高电平,数据在时钟的上升沿采样。

4. Mode 3:-时钟极性(CPOL):1-时钟相位(CPHA):1-特点:时钟信号在空闲状态为高电平,数据在时钟的下降沿采样。

SPI的时钟模式需要根据具体的通信需求来配置。

通常在SPI设备的Datasheet中会指定默认的时钟模式,开发者需要根据SPI设备的要求来配置相应的时钟模式。

时钟模式的选择取决于设备的工作方式和通信时序的要求。

例如,如果SPI设备在时钟信号的上升沿将数据放置到总线上并在下降沿进行采样,则应选择Mode 0或Mode 2、如果设备在下降沿将数据放置到总线上并在上升沿进行采样,则应选择Mode 1或Mode 3。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

S P I时钟模式的配置集团标准化小组:[VVOPPT-JOPP28-JPPTL98-LOPPNN]【S P I基础知识简介】设备与设备之间通过某种硬件接口通讯,目前存在很多种接口,SPI接口是其中的一种。

SPI中分Master主设备和Slave从设备,数据发送都是由Master控制。

一个master可以接一个或多个slave。

常见用法是一个Master接一个slave,只需要4根线:SCLK:SerialClock,(串行)时钟MISO:MasterInSlaveOut,主设备输入,从设备输出MOSI:MasterOutSlaveIn,主设备输出,从设备输入SS:SlaveSelect,选中从设备,片选SPI由于接口相对简单(只需要4根线),用途算是比较广泛,主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

即一个SPI的Master通过SPI与一个从设备,即上述的那些Flash,ADC等,进行通讯。

而主从设备之间通过SPI进行通讯,首先要保证两者之间时钟SCLK要一致,互相要商量好了,要匹配,否则,就没法正常通讯了,即保证时序上的一致才可正常讯。

而这里的SPI中的时钟和相位,指的就是SCLk时钟的特性,即保证主从设备两者的时钟的特性一致了,以保证两者可以正常实现SPI通讯。

【SPI相关的缩写或说法】先简单说一下,关于SPI中一些常见的说法:SPI的极性Polarity和相位Phase,最常见的写法是CPOL和CPHA,不过也有一些其他写法,简单总结如下:(1)CKPOL(ClockPolarity)=CPOL=POL=Polarity=(时钟)极性(2)CKPHA(ClockPhase)=CPHA=PHA=Phase=(时钟)相位(3)SCK=SCLK=SPI的时钟(4)Edge=边沿,即时钟电平变化的时刻,即上升沿(risingedge)或者下降沿(fallingedge)对于一个时钟周期内,有两个edge,分别称为:Leadingedge=前一个边沿=第一个边沿,对于开始电压是1,那么就是1变成0的时候,对于开始电压是0,那么就是0变成1的时候;Trailingedge=后一个边沿=第二个边沿,对于开始电压是1,那么就是0变成1的时候(即在第一次1变成0之后,才可能有后面的0变成1),对于开始电压是0,那么就是1变成0的时候;本文采用如下用法:极性=CPOL相位=CPHASCLK=时钟第一个边沿和第二个边沿【SPI的相位和极性】CPOL和CPHA,分别都可以是0或时1,对应的四种组合就是:Mode0CPOL=0,CPHA=0Mode1CPOL=0,CPHA=1Mode2CPOL=1,CPHA=0Mode3CPOL=1,CPHA=1【CPOL极性】先说什么是SCLK时钟的空闲时刻,其就是当SCLK在数发送8个bit比特数据之前和之后的状态,于此对应的,SCLK在发送数据的时候,就是正常的工作的时候,有效active的时刻了。

先说英文,其精简解释为:ClockPolarity=IDLEstateofSCK。

再用中文详解:SPI的CPOL,表示当SCLK空闲idle的时候,其电平的值是低电平0还是高电平1:CPOL=0,时钟空闲idle时候的电平是低电平,所以当SCLK有效的时候,就是高电平,就是所谓的active-high;CPOL=1,时钟空闲idle时候的电平是高电平,所以当SCLK有效的时候,就是低电平,就是所谓的active-low;【CPHA相位】首先说明一点,capturestrobe=latch=read=sample,都是表示数据采样,数据有效的时刻。

相位,对应着数据采样是在第几个边沿(edge),是第一个边沿还是第二个边沿,0对应着第一个边沿,1对应着第二个边沿。

对于:CPHA=0,表示第一个边沿:对于CPOL=0,idle时候的是低电平,第一个边沿就是从低变到高,所以是上升沿;对于CPOL=1,idle时候的是高电平,第一个边沿就是从高变到低,所以是下降沿;CPHA=1,表示第二个边沿:对于CPOL=0,idle时候的是低电平,第二个边沿就是从高变到低,所以是下降沿;对于CPOL=1,idle时候的是高电平,第一个边沿就是从低变到高,所以是上升沿;此处,再多解释一下可能会遇到的CKP和CKE,其是Microchip的PIC系列芯片中的说法。

(1)CKP是ClockPolaritySelect,就是极性=CPOL:CKP,虽然名字和CPOL不一样,但是都是指时钟相位的选择,定义也一样:CKP:ClockPolaritySelectbit1=Idlestateforclock(CK)isahighlevel0=Idlestateforclock(CK)isalowlevel所以不多解释。

(2)CKE是ClockEdgeSelect,就是相位=CPHA:CKE:SPIClockEdgeSelectbit1=TransmitoccursontransitionfromactivetoIdleclockstate0=TransmitoccursontransitionfromIdletoactiveclockstate意思是1=(数据)传输发生在时钟从有效状态转到空闲状态的那一时刻0=(数据)传输发生在时钟从空闲状态转到有效状态的那一时刻其中,数据传输的时刻,即图中标出的“数据transmit传输的时刻”,很明显,该时刻是一个时钟和下一个时钟之间交界的地方,对应的不论是上升沿还是下降沿,都与我们前面提到的CPHA=数据采样的时刻,的边沿方向所相反。

所以,此处的CKE,正好与CPHA相反。

所以,CKP和CKE所对应的取值的含义为:WhenCKP=0:CKE=1=>DatatransmittedonrisingedgeofSCKCKE=0=>DatatransmittedonfallingedgeofSCKWhenCKP=1:CKE=1=>DatatransmittedonfallingedgeofSCKCKE=0=>DatatransmittedonrisingedgeofSCK【如何看懂和记忆CPOL和CPHA】所以,关于在其他地方介绍的,看似多么复杂难懂难记忆的CPOL和CPHA,其实经过上面解释,就肯容易看懂了:去看时序图,如果起始的始终SCLK的电平是0,那么CPOL=0,如果是1,那么CPOL=1,然后看数据采样时刻,即时序图数据线上的数据那个矩形区域的中间所对应的位置,对应到上面SCLK时钟的位置,对应着是第一个边沿或是第二个边沿,即CPHA是0或1。

(对应的是上升沿还是还是下降沿,要根据对应的CPOL的值,才能确定)。

即:(1)如何判断CPOL:SCLK的空闲时候的电压,是0还是1,决定了CPOL是0还是1;(2)如何判断CPHA:而数据采样时刻对应着的SCLK的电平,是第一个边沿还是第二个边沿,对应着CPHA为0还是1。

SCLK的极性,相位,边沿之间的内在逻辑关系SCLK空闲时刻电压低电平CPOL=0高电平CPOL=1数据采样时刻,SCLK的edge是第一个还是第二个第一个边沿CPHA=0上升沿(开始的电平是低电压0,而第一个边沿,只能是从0变到1,即上升沿)下降沿第二个边沿CPHA=1下降沿上升沿(开始电平是高电平1,第二个边沿,肯定是从低电平0变到高电平1,因为第一个边沿肯定是从高电平1,变到低电平0)【软件中如何设置SPI的极性和相位】SPI分主设备和从设备,两者通过SPI协议通讯。

而设置SPI的模式,是从设备的模式,决定了主设备的模式。

所以要先去搞懂从设备的SPI是何种模式,然后再将主设备的SPI的模式,设置和从设备相同的模式,即可正常通讯。

对于从设备的SPI是什么模式,有两种:(1)固定的,有SPI从设备硬件决定的SPI从设备,具体是什么模式,相关的datasheet中会有描述,需要自己去datasheet中找到相关的描述,即:关于SPI从设备,在空闲的时候,是高电平还是低电平,即决定了CPOL是0还是1;然后再找到关于设备是在上升沿还是下降沿去采样数据,这样就是,在定了CPOL的值的前提下,对应着可以推算出CPHA是0还是1了。

举例1:CC2500-Low-CostLow-Power2.4GHzRFTransceiver的datasheet中SPI的时序图从图中可以看到,最开始的SCLK和结束时候的SCLK,即空闲时刻的SCLK,是低电平,推导出CPOL=0,然后可以看到数据采样的时候,即数据最中间的那一点,对应的是SCLK的第一个边沿,所以CPHA=0(此时对应的是上升沿)。

举例2:SSD1289-240RGBx320TFTLCDControllerDriver的datasheet中提到:“SDIisshiftedinto8-bitshiftregisteroneveryrisingedgeofSCKintheorderofdatabi t7,databit6……databit0.”意思是,数据是在上升沿采样,所以可以断定是CPOL=0,CPHA=0,或者CPOL=1,CPHA=1的模式,但是至于是哪种模式。

按理来说,接下来应该再去确定SCLK空闲时候是高电平还是低电平,用以确定CPOL是0还是1,但是datasheet中没有提到这点。

所以,此处,目前不太确定,是两种模式都支持,还是需要额外找证据却确定CPOL是0还是1.(2)可配置的,由软件自己设定从设备也是一个SPI控制器,4种模式都支持,此时只要自己设置为某种模式即可。

然后知道了从设备的模式后,再去将SPI主设备的模式,设置为和从设备模式一样,即可。

对于如何配置SPI的CPOL和CPHA的话,不多细说,多数都是直接去写对应的SPI控制器中对应寄存器中的CPOL和CPHA那两位,写0或写1即可。

举例:此处遇到的C8051F347中的SPI就是一个SPI的controller控制器,即支持软件配置CPOL和CPHA的值,四种模式都支持,此处C8051F347作为SPI从设备,设置了CPOL=1,CPHA=0的模式,因此,此处对应主芯片BlackfinF537中的SPI控制器,作为Master主设备,其SPI的模式也要设置为CPOL=1,CPHA=0。

【待解决问题】对于软件去如何设置主设备(和从设备)的CPOL和CPHA的值,是搞懂了,知道两者要匹配才可以正常通讯,但是对于CPOL和CPHA这四种模式,不同的模式之间,相对来说有何优缺点,比如是否哪种模式更稳定,数据更不容易出错等等,还是不清楚【总结】1.IT方面的资料,国内的,还是把问题讲明白的太少,想搞懂问题,还是得去找英文的。