器件编程和实验系统介绍

在系统可编程模拟器件在教学实验中的设计和应用

平 台 。设 计 了一 个 电源 转 换 、 控 和 保 护 的 电 路 实 验 , 综 合 了 模 拟 可 编 程 和 逻 辑 可 编 程 技 术 , 有 设 计 新 监 它 具 颖 、 识 面 广 、 合 性 强 等 特 点 , 够 充 分 培 养 学 生 的实 践 能 力 和 创 造 能 力 。 知 综 能

兰 墨

二兰 !

实

验

技

术

与

管

理

第 2 6卷

第 8期

2 0 年 8月 09

CNl — 2 3 / 1 0 4 T

Ex e i n a c no o y a d M a a e n p rme t lTe h lg n n g me t

Hale Waihona Puke Vo . 6 No. Au . 2 0 12 8 g 0 9

( u ngx o a i a G a iV c ton lCole fM e ha c la e t ia e hn og lge O c nia nd El c rc lT c ol y,N a ni 0 7,Chia) n ng 5 00 3 n

A b ta t Th p ri r du e he s r t r nd f a ur sofip src : e pa e nto c s t tuc u ea e t e s PA C30,a pr r m mab ea l vie Ba e og a l naog de c . sd on t lc r ct c olgy t a hng e e i e t ltor ,a cr ui e pe i e orp he ee toni e hn o e c i xp rm n alp a f m ic t x rm ntf owe o e son,s e — rc nv r i up r v so nd p ot c in i e i e ii n a r e to s d sgn d. I e r tn b h pr gr m m a e a a o e hnoog n o a m a e l c l nt g a ig ot o a bl n l g t c l y a d pr gr m bl ogia t c no o e h l gy,t i ic i xp rm e ih isne y d sgn, wi l ow ld nd s r gl om p e e i ec r hs cr ute e i ntw t t wl e i dey kn e gea ton y c r h nsv ha —

Cortex-M4原理与实践实验报告I2C编程及应用

Cortex-M4原理与实践实验报告题目:I2C编程及应用一、实验目的1.了解I2C总线的特点和功能。

2.学会C语言模拟I2C时序。

3.学会用I2C总线对PCA9557芯片进行操作。

二、实验设备1.计算机一台,操作系统为Windos11或Windos10,装有CCSv11.0软件。

2.EK-TM4C1294XL实验开发板一块。

B连接线一条。

三、实验原理和流程1. I2C总线介绍Inter-IC总线又称I2C总线是一种简单的双向一线制串行通信总线。

多个符合I2C总线标准的器件都可以通过同一条I2C总线进行通信,而不需要额外的地址译码器。

I2C总线应用中主要涉及如下几个基本概念:发送器:本次传送中发送数据(不包括地址和命令)到总线的器件。

接收器:本次传送中从总线接收数据(不包括地址和命令〉的器件。

主机:初始化发送、产生时钟信号和终止发送的器件,它可以是发送器或接收器。

主机通常是微控制器。

从机:被主机寻址的器件,它可以是发送器或接收器。

I2C总线仅使用两个信号:SDA和 SCL。

SDA是双向串行数据线,SCL是双向串行时钟线。

当SDA和SCL线为高电平时,总线为空闲状态。

I2C总线连接方式如图1所示。

在时钟SCL的高电平期间,SDA线上的数据必须保持稳定。

SDA仅可在时钟SCL为低电平时改变,如图2所示。

I2C 总线的协议定义了两种状态;起始和停止。

当SCL 为高电平时,在SDA 线上从高到低的跳变被定义为起始条件;而当SCL 为高电平时,在SDA 线上从低到高的天边则被定义为停止条件。

总线在起始条件之后被看作为忙状态。

总线在停止条件之后被看作为空闲。

如图3所示。

图 3 I2C总线起始条件和停止条件 SDA 线上的每个字节必须为8位长。

不限制每次传输的字节书。

每个字节后面必须带有一个应答位。

数据传输是MSB 在前。

当接收器不能接受另一个完整的字节时,它可以将时钟线SCL 拉倒低电平,以迫使发送器进入等待状态。

可编程逻辑器件实验报告

一、实验目的通过本次实验,使学生掌握可编程逻辑器件(FPGA)的基本原理和操作方法,了解其结构特点和应用领域。

通过实验,培养学生动手实践能力和创新意识,提高学生运用FPGA进行数字系统设计和验证的能力。

二、实验原理可编程逻辑器件(FPGA)是一种高度集成的数字电路,具有可编程性、可扩展性和可重用性。

FPGA主要由可编程逻辑单元、可编程互连资源、时钟管理单元、I/O单元等组成。

通过编程,用户可以根据自己的需求定制FPGA内部逻辑结构,实现各种数字电路功能。

FPGA编程通常采用硬件描述语言(HDL),如VHDL或Verilog。

HDL描述了电路的功能和结构,通过编译和综合,生成FPGA内部的逻辑资源分配和互连关系。

实验中,我们将使用Quartus II软件进行FPGA编程和仿真。

三、实验内容1. FPGA基础操作(1)安装Quartus II软件,熟悉软件界面和基本操作。

(2)搭建FPGA实验平台,包括FPGA开发板、电源、连接线等。

(3)将FPGA开发板连接到计算机,进行硬件初始化和配置。

2. FPGA编程(1)使用VHDL或Verilog语言编写实验程序,实现简单的数字电路功能,如全加器、编码器、译码器等。

(2)将编写好的程序导入Quartus II软件,进行编译和综合。

(3)观察编译报告,检查程序语法错误和资源占用情况。

(4)进行仿真,验证程序功能是否正确。

3. FPGA下载与验证(1)将编译后的程序下载到FPGA芯片中。

(2)使用示波器或逻辑分析仪等工具,观察FPGA输出的波形,验证程序功能。

(3)根据实验要求,修改程序参数,优化电路性能。

四、实验步骤1. 搭建实验平台(1)将FPGA开发板连接到计算机,确保所有连接线正确。

(2)检查电源电压,确保FPGA芯片供电正常。

2. 编写程序(1)打开Quartus II软件,创建新工程。

(2)选择合适的HDL语言,编写实验程序。

(3)保存程序,并添加到工程中。

8051实验指导书

第一部分系统介绍一、系统概述1)、微处理器:i80c31,它的P1口、P3口皆对用户开放,供用户使用。

2)、时钟频率:6.0MHz3)、存储器:程序存储器与数据存储器统一编址,最多可达64k,板载ROM(监控程序27C256)12k;RAM1(程序存储器6264)8k供用户下载实验程序,可扩展达32k;RAM2(数据存储器6264)8k供用户程序使用,可扩展达32k。

(RAM程序存储器与数据存储器不可同时扩至32k,具体与厂家联系)。

(见图1-1:存储器组织图)。

在程序存储器中,0000H----2FFFH为监控程序存储器区,用户不可用,4000H----5FFFH为用户实验程序存储区,供用户下载实验程序。

数据存储器的范围为:6000H----7FFFH,供用户实验程序使用。

注意:因用户实验程序区位于4000H-----5FFFH,用户在编写实验程序时要注意,程序的起始地址应为4000H,所用的中断入口地址均应在原地址的基础上,加上4000H。

例如:外部中断0的原中断入口为0003H,用户实验程序的外部中断0的中断程序入口为4003H,其他类推,见表1-1。

4)、可提供的对8051的基本实验为了提高微机教学实验质量,提高实验效率,在该系统的实验板上,除微处理器外、程序存储器、数据存储器外,还增加了8255并行接口、8250串行控制器、8279键盘、显示控制器、8253可编程定时器、A/D、D/A转换、单脉冲、各种频率的脉冲发生器、输入、输出电路等模块,各部分电路既相互独立、又可灵活组合,能满足各类学校,不同层次微机实验与培训要求。

可提供的实验如下:(1)、8051P1口输入、输出实验(2)、简单的扩展输入、输出实验(3)、8051定时器/计数器实验(4)、8051外中断实验(5)、8279键盘扫描、LED显示实验(6)、8255并行口输入、输出实验(7)、8253定时器/计数器实验(8)、8259中断实验(9)、串行口通讯实验(10)、ADC0809 A/D转换实验(11)、DAC0832 D/A转换实验(12)、存储器扩展实验(13)、交通灯控制实验FFFFH用户I/O区CFEFH系统I/O区,CFBFH用户I/O区7FFFHRAM2用户实验程序区供用户下载实验程序4FFFHRAM1用户实验程序数据区2FFFHROM系统监控程序区0000H图1:存储器系统组织图中断名称 8051原中断程序入口用户实验程序响应程序入口外中断0 0003H 4003H定时器0中断 000BH 400BH外中断1 0013H 4013H定时器1中断 001BH 401BH串行口中断 0023H 4023H表1-1:用户中断程序入口表5)、资源分配本系统采用可编程逻辑器件(CPLD)EPM7128做地址的编译码工作,可通过芯片的JTAG接口与PC机相连,对芯片进行编程。

可编程逻辑器件第章第一章可编程逻辑器件简介

可编程逻辑器件第章第一章可编程逻辑器件简介引言电子设计的必由之路将是数字化,这已成为有目共睹的事实。

在数字化的道路上,我国电子设计技术的发展经历了许多重大的变革和飞跃。

从传统的应用SSI、MSI等通用的数字电路芯片构成电路系统到广泛地应用单片机,电子设计技术发生了一个巨大的飞跃。

今天,随着VLSI向更高层次的发展,电子产品市场运作节奏的进一步加快,电子设计技术已迈入一个全新的阶段,即CPLD/FPGA在EDA基础上的广泛应用。

它在更高层次上容纳了过去数字技术的优秀部分,但在电子设计的技术操作和系统构成上却发生了质的飞跃。

CPLD/FPGA不但在逻辑实现上是无限的,而且可触及硅片电路线度的物理极限,并兼有串行、并行工作方式,高速、高可靠性以及宽口径适用性等诸方面的特点。

不但如此,随着EDA 技术的发展和CPLD/FPGA向深亚微米领域的进军,它们与MCU、MPU、DSP、A/D、D/A、ROM和RAM等独立器件之间的功能界限将日益模糊。

特别是软/硬件IP芯核产业的迅猛发展,嵌入式通用与标准CPLD/FPGA器件呼之欲出,片上系统(SOC)已近在咫尺。

同时,CPLD/FPGA还打破了软硬件之间最后的屏障,使软硬件工程师有了共同的语言。

可以预测,未来的电子设计将是EDA的时代,而掌握EDA这门技术无疑已成为现代每一位电子设计工程技术人员必不可少的基本技能。

本篇正是鉴于这样的背景,介绍了可编程逻辑器件(PLD)CPLD/FPGA的结构以及通用的硬件描述语言(VHDL),并着重介绍了Altera公司的软件平台MAX+PLUSII的使用和在此基础上的PLD基本设计原理。

第一章可编程逻辑器件简介1.1PLD设计的数字系统的特点可编程逻辑器件(ProgrammedLogicDevice),简称PLD,是一种由用户通过编程定义其逻辑功能,从而实现各种设计要求的集成电路芯片。

它是70年代发展起来的新型逻辑器件,发展至今,已相继出现了PROM、EPROM、PLA、PAL、GAL和ISP等多个品种。

单片机整套实验及程序(交通灯_跑马灯等)

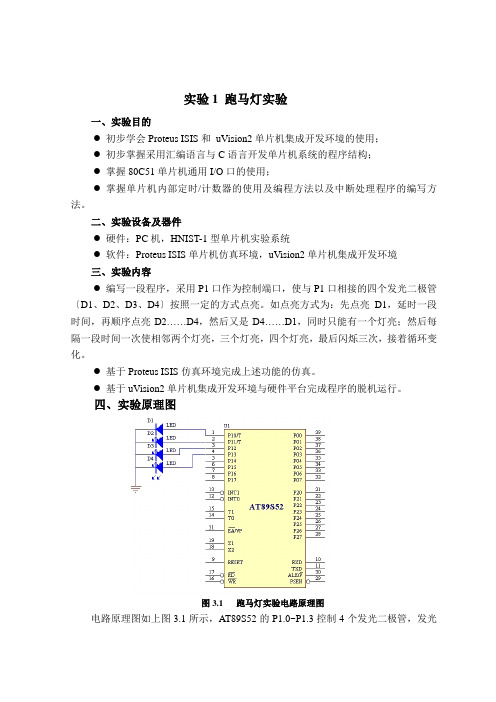

实验1 跑马灯实验一、实验目的●初步学会Proteus ISIS和uVision2单片机集成开发环境的使用;●初步掌握采用汇编语言与C语言开发单片机系统的程序结构;●掌握80C51单片机通用I/O口的使用;●掌握单片机内部定时/计数器的使用及编程方法以及中断处理程序的编写方法。

二、实验设备及器件●硬件:PC机,HNIST-1型单片机实验系统●软件:Proteus ISIS单片机仿真环境,uVision2单片机集成开发环境三、实验内容●编写一段程序,采用P1口作为控制端口,使与P1口相接的四个发光二极管〔D1、D2、D3、D4〕按照一定的方式点亮。

如点亮方式为:先点亮D1,延时一段时间,再顺序点亮D2……D4,然后又是D4……D1,同时只能有一个灯亮;然后每隔一段时间一次使相邻两个灯亮,三个灯亮,四个灯亮,最后闪烁三次,接着循环变化。

●基于Proteus ISIS仿真环境完成上述功能的仿真。

●基于uVision2单片机集成开发环境与硬件平台完成程序的脱机运行。

四、实验原理图图3.1 跑马灯实验电路原理图电路原理图如上图3.1所示,AT89S52的P1.0~P1.3控制4个发光二极管,发光二极管按照一定次序发光,相邻发光二极管的发光时间间隔可以通过定时器控制,还可以通过软件延时实现。

五、软件流程图与参考程序●主程序流程图如下:●参考程序#include<reg52.h>#include<intrins.h>#define uchar unsigned char#define uint unsigned intuchar aa,num,speed,flag;uchar code table[]={0x0e,0x0d,0x0b,0x07};uchar code table1[]={0x0a,0x05,0x09,0x06};uchar codetable2[]={0x0c,0x09,0x03,0x08,0x01,0x0e,0x0c,0x08,0x00};void delay(uint z)//延时函数{uint x;uchar y;for(x=z;x>0;x--)for(y=200;y>0;y--);}void init()//条件初始化函数{ flag=0;speed=10;//控制跑马灯流水速度TMOD=0x01;//中断方式TH0=(65535-50000)/256;TL0=(65536-50000)%256;//初值EA=1;//翻开总中断ET0=1;//翻开外中断0TR0=1;}void main(){init();//调用初始化函数while(1){if(flag){delay(2000);//调用延时函数for(num=0;num<4;num++)//从左至右间隔一个依次闪烁{P1=table[num];delay(2000);}for(num=3;num>0;num--)//从左至右间隔一个依次闪烁{P1=table[num];delay(2000);}for(num=0;num<4;num++)//从左至右间隔两个依次闪烁{P1=table1[num];delay(2000);}for(num=3;num>0;num--)//从左至右间隔两个依次闪烁{P1=table1[num];delay(2000);}for(num=0;num<6;num++)//两个,三个,四个跑马灯依次闪烁{P1=table2[num];delay(2000);}for(num=0;num<5;num++)//闪烁5次{P1=0xff;//全暗delay(2000);P1=0X00;//全亮delay(2000);}speed=speed-3;//变速if(speed==4){speed=10;}}}}void timer0() interrupt 1//中断函数{TH0=(65535-50000)/256;TL0=(65536-50000)%256;aa++;if(aa==speed){aa=0;flag=1;}}六、实验思考题●请用汇编指令完本钱实验内容,深刻理解汇编语言程序设计结构。

NOR-Flash存储器介绍及编程

NOR-Flash存储器介绍及编程NOR-Flash存储器1概述ADSP-BF532自身不具有ROM,因此必须外接ROM器件来存储放电后仍需要保存的代码和数据。

NOR Flash具有非易失性,并且可轻易擦写。

Flash技术结合了OTP存储器的成本优势和EEPROM的可再编程性能,因此得到了越来越广泛的使用。

在本实验中将主要介绍NOR Flash器件——Am29LV160D在Blackfin处理器系统中的应用。

NOR Flash采用标准总线接口与处理器交互,对它的读取不需要任何特殊的代码。

作为代码存储器,NOR Flash映射在处理器的异步存储区的0x2000,0000到0x201F,FFFF地址上。

若设定系统从Flash启动,则系统上电复位时,处理器就自动从Flash中取得指令运行。

因此NOR Flash中要存放系统启动代码,这些代码必须在系统上电时完成一系列初始化的工作。

经过了这些初始化,系统才得以正确启动并开始工作。

2 实验内容和目标本实验要实现的内容和目标读出FLASH的manufacturer ID和device ID。

对FLASH芯片进行整片擦出,并验证擦除是否成功(读出数据是否为为全0xFFFF)。

往FLASH起始地址写入0x5555,并读出,验证写入是否正确。

3实验分析1(Am29LV160D介绍进行实际编程之前,首先应了解NOR Flash器件Am29LV160D的特性和读写操作的要求。

Am29LV160D是由AMD公司推出的1M×16bit的CMOS 多用途Flash。

它的主要特性如下。

存储空间组织1M×16bit。

读写操作采用单一电源 2.7,3.6V。

可靠性, 可擦写100 000个周期(典型值);, 数据可保存100年。

低功耗- 动态电流 15mA(典型值);, 静态电流 4?A(典型值);, 自动低功耗模式4?A(典型值)。

扇区擦除能力统一为2K×16b大小的扇区。

STC单片机原理及应用:从器件、汇编、C到操作系统的分析和设

12.5红外通信 的原理及实现

1

13.1模数转换 器原理

13.2 STC单片 2

机内ADC的结 构原理

3 13.3 STC单片

机内ADC寄存 器组

4 13.4直流电压

测量及串口显 示

5 13.5直流电压

测量及LCD屏 显示

13.6交流电压 测量及LCD屏显

示

13.7温度测量 及串口显示

1

14.1脉冲宽度 调制原理

8.3运算符

4

8.4描述语句

5

8.5数组

1

8.6指针

2

8.7函数

3

8.8预编译指 令

4

8.9复杂数据 结构

5

8.10 C程序中 使用汇编语言

8.11 C语言端 口控制实现

8.12 C语言中 断程序实现

9.2 STC单片机复 位

9.1 STC单片机时 钟

9.3 STC单片机电 源模式

10.2 STC单片机比 较器寄存器组

02

7.2汇编代 码中段的分 配

03

7.3汇编语 言符号及规 则

04

7.4汇编语 言操作数描 述

06

7.6 KeilμVi sion5汇编 语言设计流 程

05

7.5汇编语 言控制描述

7.7单片机端口 控制汇编语言 程序设计

7.8单片机中断 汇编语言程序 设计

1

8.1常量和变 量

2

8.2数据类型

3

本书是为单片机相关课程教学而编写的教材。全书共分为17章,主要内容包括:单片机和嵌入式系统基础知 识,STC单片机硬件知识,STC单片机软件开发环境,数值表示及转换,STC单片机架构,STC单片机CPU指令系统, STC单片机汇编语言编程模型,STC单片机C语言编程模型,STC单片机时钟、复位和电源模式原理及实现,STC单 片机比较器原理及实现,STC单片机计数器和定时器原理及实现,STC单片机异步串行收发器原理及实现,STC单 片机ADC原理及实现,STC单片机增强型PWM发生器原理及实现,STC单片机SPI原理及实现,STC单片机 CCP/PCA/PWM模块原理及实现,RTX51操作系统原理及实现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

19

按键电路

20

10

按键与引脚对应关系

PIN_107 PIN_108 PIN_110 PIN_112 PIN_113 PIN_114 PIN_115 PIN_116 => => => => => => => => key1 key2 key3 key4 key5 key6 key7 key8

21

拨码开关电路

(2)打开电源

将电源线与试验箱的电源插座相连接 打开试验板的电源开关。

3

(2)在首次连接PC时,在PC端会出现“正在安装设备驱动 程序软件”,用户可以等待一段时间,直到搜索失败,或者 强制设置“跳过从Windows Update获得驱动程序软件”,转 入手动设置。

4

2

(3)此时打开我的电脑→管理→设备管理器,可在其他设备 中看到标有黄色问号的USB-Blaster设备

12

提供编程支持 (4)USB- Blaster下载电缆(用于USB口) ; (5)Ethernet- Blaster下载电缆(用于Ethernet网口) ;

对串行配置器件

2

1

器件编程

1. 硬件连接

(1)连接下载电缆

将“USB-Blaster”下载线的10针插头与试验箱中的10 pin调试插 座相连接,另一端与PC机的USB口相接;

FPGA: CycloneII系列EP2C8Q208C8芯片

12

6

资源分布

13

JTAG下载接口

注意:严禁带电拔插JTAG, 插拔下载线时必须断电!

14

7

正确

错误

15

外接电源

核心板和接口板均设有5V 电源插口,位置在PCB 左上角。随便接一个插口即可,一般插在接口板上 。 蓝白色(有的开发板是红色)那个按键就是全板电 源总开关,按下后即可接通电源,这时底板与核心 板左上角均有电源指示灯LED 点亮。

若Available hardware items栏中有USB-Blaster时,单击Current selected hardware 栏旁的下拉箭头,选中USB-Blaster然后close

9

器件编程

若Available hardware items栏中出现USB-Blaster时,执行以下 两步:

PIN_149 PIN_151 PIN_206 PIN_208

=> dig[1] => dig[3] => dig[5] => dig[7]

PIN_170 => seg[0] PIN_169 => seg[2] PIN_173 => seg[4] PIN_164 => seg[6]

PIN_165 => seg[1] PIN_175 => seg[3] PIN_168 => seg[5] PIN_171=> seg[7] 24

16

8

时钟和复位电路

PIN_23 => CLK0 (50MHz) PIN_131 => RESET (低电平有效) 17

LED电路

18

9

LED与引脚对应关系

PIN_142 PIN_141 PIN_139 PIN_138 PIN_137 PIN_135 PIN_134 PIN_133 => => => => => => => => led1 led2 led3 led4 led5 led6 led7 led8

(1)在编程器窗口中 选中“Program/Configure”复选框; (2)单击“Start”按钮,开始编程。 若完成编程,则在Message窗口中显示“Configuration succeeded”。

若要同时对多个器件编程,可以单击“Add File…”按钮, 添加编程文件。

11

实验系统介绍

适于产品研发阶段 器件编程方法: 用计算机及Altera专用编程电缆进行编程 优点: 编程方便、迅速, 便于修改。 缺点: 必须有计算机及专用编程电缆, 适于实验室内使用。

1

器件编程

二、Quartus Ⅱ的编程方法

Quartus Ⅱ的编程器(Programmer)使用经编译生成的 编程目标文件(.pof文件或.sof文件) 进行编程。 Altera公司编程器硬件包括: (1)MasterBlaster下载电缆(用于串口或USB口); (2) ByteBlasterMV下载电缆(用于并口); (3) ByteBlaster Ⅱ下载电缆(用于并口) ;

执行“Tools > Programmer”命令或快捷按钮,则编程器窗口自动打开 <工程文件名>.cdf文件,其中包括当前编程文件和所选器件等信息。

编程硬件设置

添加其它编程文件

编程器窗口

8

4

器件编程

3. 编程硬件设置 (1)在编程器窗口的Mode列表中选择JTAG模式; (2)单击“Hardware Setup”按钮,弹出“Hardware Setup”对话框;

添加编程硬件

(3)单击“Add Hardware”按钮,弹出“Add Hardware”对话 框; (4)在“Add Hardware”对话框中,从Hardware type列表中 选择“USB-Blaster”,单击“OK”,返回“Hardware Setup”对 话框; 10

5

器件编程

4. 进行编程

5

选中USB-Blaster设备,右键单击,选择“更新驱动程序软 件”,并且选择“浏览计算机以查找驱动程序软件”,浏览 Quartus II软件安装目录,选D:\altera\9.1\quartus\drivers\usbblaster(用户根据自己的软件安装目录,此处未必一样)

6

3

7

器件编程

2. 打开编程器窗口

PIN_128 PIN_127 PIN_118 PIN_117

=> => => =>

ckey[1] ckey[2] ckey[3] ckey[4]

22

11

数码管显示电路

23

与引脚对应关系

PIN_150 => PIN_152 => PIN_205 => PIN_207 =>

dig[0] dig[2] dig[4] dig[6]

器件编程

一、对Altera器件的编程方法

Quartus Ⅱ的编程器(Programmer)使用经编译生成的编程目 标文件进行编程——将其下载到Altera器件中。 MAX等E2PROM工艺器件(CPLD)的编程目标文件其后缀 为.pof ! SRAM工艺FPGA器件的编程目标文件其后缀为.sof !