手持式DDS信号源的设计与开发

DDS信号源的设计与实现(电子科大)

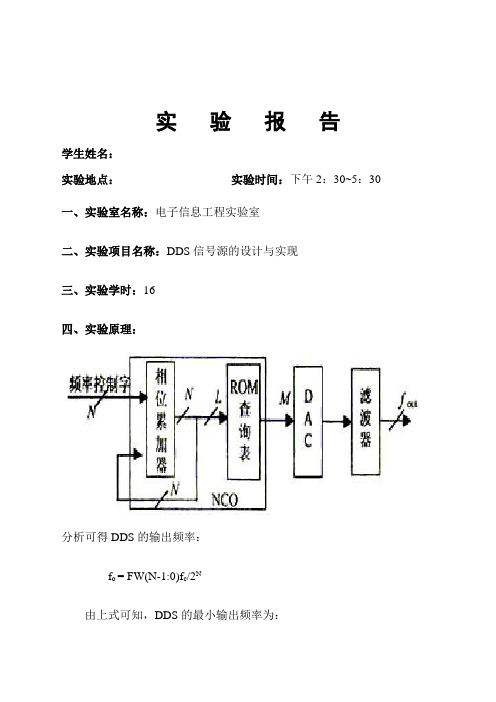

实验报告学生姓名:实验地点:实验时间:下午2:30~5:30一、实验室名称:电子信息工程实验室二、实验项目名称:DDS信号源的设计与实现三、实验学时:16四、实验原理:分析可得DDS的输出频率:f o = FW(N-1:0)f c/2N由上式可知,DDS的最小输出频率为:f omin = f c/2NDDS的频率分辨率为:f o = f c/2NDDS频率输入字的计算:FW(N-1:0) = 2N f0/f c五、实验目的:通过本实验项目,可使学生利用VHDL硬件描述语言对比较复杂的、综合性的实际电路系统进行设计、描述,利用EDA开发工具完成系统的综合、仿真,并用硬件平台完成系统的硬件实现, 着重培养学生的实际动手设计能力。

六、实验内容:1.EDA技术及VHDL2.EDA开发软件及实验箱的使用3.DDS信号源的设计与实现七、实验器材(设备、元器件):电脑,实验箱(带有EPF10K10 LC84-4芯片)八、实验步骤:① 创建新目录“D:\XX”,运行MAXPLUS II软件;② 打开Altera MAX+plus软件后,首先选择“File”中的“New”, 建立一个新的VHDL文件;③ 编辑VHDL源程序选择“Text Editor file”,再输入程序: library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity dds_nes isport (clk,swithc : in std_logic;freqin : in std_logic_vector(11 downto 0); --频率控制字宽:12位phasein : in std_logic_vector(5 downto 0); --相位字宽ampin : in std_logic_vector(7 downto 0); --加法器宽度ddsout : out integer range 0 to 255 );end dds_nes;architecture rtl of dds_nes issignal acc:std_logic_vector(11 downto 0);signal phaseadd: std_logic_vector(5 downto 0);signal romaddr: std_logic_vector(5 downto 0);signal freqw:std_logic_vector(11 downto 0);signal phasew:std_logic_vector(5 downto 0);signal romaddr_i:integer range 0 to 63;signal amp_t:std_logic_vector(15 downto 0);signal ddsout_t:integer range 0 to 255;beginprocess(clk)beginif clk'event and clk='1' thenif swithc='1' thenfreqw<=freqin;elsefreqw<=freqin+freqin;end if;phasew<=phasein;acc<=acc+freqw;end if;end process;phaseadd<=acc(11 downto 6)+phasew;romaddr<=phaseadd(5 downto 0);romaddr_i<=conv_integer(romaddr); --查找表字宽取整amp_t<=ampin*conv_std_logic_vector(ddsout_t,8);--8*8ddsout_t转为8位ddsout<=conv_integer(amp_t(15 downto 8)); --取高8位后转整process(romaddr_i)begincase romaddr_i iswhen 00 => ddsout_t<=255;when 01 => ddsout_t<=254;when 02 => ddsout_t<=252;when 03 => ddsout_t<=249;when 04 => ddsout_t<=245;when 05 => ddsout_t<=239;when 06 => ddsout_t<=233;when 07 => ddsout_t<=225;when 08 => ddsout_t<=217;when 09 => ddsout_t<=207;when 10 => ddsout_t<=197;when 11 => ddsout_t<=186;when 12 => ddsout_t<=174;when 13 => ddsout_t<=162;when 14 => ddsout_t<=150;when 15 => ddsout_t<=137;when 16 => ddsout_t<=124;when 17 => ddsout_t<=112;when 18 => ddsout_t<=99;when 19 => ddsout_t<=87;when 20 => ddsout_t<=75;when 22 => ddsout_t<=53; when 23 => ddsout_t<=43; when 24 => ddsout_t<=34; when 25 => ddsout_t<=26; when 26 => ddsout_t<=19; when 27 => ddsout_t<=13; when 28 => ddsout_t<=8; when 29 => ddsout_t<=4; when 30 => ddsout_t<=1; when 31 => ddsout_t<=0; when 32 => ddsout_t<=0; when 33 => ddsout_t<=1; when 34 => ddsout_t<=4; when 35 => ddsout_t<=8; when 36 => ddsout_t<=13; when 37 => ddsout_t<=19; when 38 => ddsout_t<=26; when 39 => ddsout_t<=34; when 40 => ddsout_t<=43; when 41 => ddsout_t<=53; when 42 => ddsout_t<=64; when 43 => ddsout_t<=75;when 45 => ddsout_t<=99;when 46 => ddsout_t<=112;when 47 => ddsout_t<=124;when 48 => ddsout_t<=137;when 49 => ddsout_t<=150;when 50 => ddsout_t<=162;when 51 => ddsout_t<=174;when 52 => ddsout_t<=186;when 53 => ddsout_t<=197;when 54 => ddsout_t<=207;when 55 => ddsout_t<=217;when 56 => ddsout_t<=225;when 57 => ddsout_t<=233;when 58 => ddsout_t<=239;when 59 => ddsout_t<=245;when 60 => ddsout_t<=249;when 61 => ddsout_t<=252;when 62 => ddsout_t<=254;when 63 => ddsout_t<=255;when others=>null;end case;end process;end rtl;④ 将源程序存为VHDL文件格式,并将VHDL文件设置为当前工程;⑤ 编译VHDL源文件,点击“MAX+plus II→Compiler→Start”进行编译,如果警告和错误不为0,要改正错误直至全部正确;⑥ 对照芯片,用导线依次对应连接好实验箱芯片的每一个接口;⑦ 确定无误后,打开试验箱与示波器电源,并运行程序,下载程序。

DDS信号源实验设计

DDS信号源实验设计作者:张磊来源:《硅谷》2015年第01期摘要本文主要介绍的是DDS信号源的组成及其工作原理。

在现实生活中DDS信号源的用处非常的大。

尤其是在关于电路方面的实验中,很多的电路实验中都需要信号发生器,而DDS信号发生器就是一个不错的选择。

因为在有些实验中要求的波形不同,所以要求设备能提供不同的输出波形用于选择。

DSS信号源模块硬件上由CM3(cortex-m3)内核的ARM芯片(STM32)和外围电路构成。

在我们实验室中的RZ8681D试验箱的DDS信号源能够输出多种波形,用起来非常的方便与快捷。

关键词 DDS信号源;ARM芯片中图分类号:TN782 文献标识码:A 文章编号:1671-7597(2015)01-0094-011 DDS信号源简介DDS信号源是为了电子电路设备实验提供多种不同的波形的一种功能强大的仪器。

它在现实生活中的应用十分广泛,它由频率合成器(相位累加器、波形ROM、低通滤波器)、cortex-m3内核的ARM芯片(STM32)、数模转换器DAC构成。

输入信号通过相位累加器、波形ROM、数模转换器DAC、低通滤波器的累加计算最后输出信号。

2 DDS信号源各模块原理1)相位累加器。

相位累加器,看它的名字就知道是对相位进行线性累加的寄存器。

相位累加器一般出现在频率合成器中,当你想要输出个波形,比如正弦波、方波、三角波,那么就应该输出一个周期中的很多个点才能得到一个失真的波形,这是这个失真波形很小,所以时钟信号频率是输出信号频率的N倍,然后时钟每增加1,相位就跟着增加1/x,然后输出波形rom,计算出它的瞬时值,再继续下一个时钟的循环,经过这样反复的N个周期以后,我们就可以得到完整的正弦或者余弦波了。

而这个计算的累加器就是相位累加器。

2)波形Rom。

波形Rom又叫正弦函数功能表Rom,它的意思就是波形存储器,顾名思义,就是存储波形的,它是用来储存在循环中产生的那些失真的很小的波形,也就是那些被经量化还有离散后的正弦波形幅值,用于来产生一个完整的波形,波形储存器就像一个存放成品零件的地方,用于组装更大的东西。

dds信号源课程设计

dds信号源课程设计一、课程目标知识目标:1. 学生能理解DDS(直接数字频率合成器)信号源的基本原理,掌握其工作流程。

2. 学生能掌握DDS信号源的关键参数,如频率、相位、幅度等,并了解它们之间的关系。

3. 学生能解释DDS信号源在电子技术中的应用,如信号发生、通信系统等。

技能目标:1. 学生能够操作DDS信号源硬件,进行基本的信号生成与调制。

2. 学生能够利用相关软件对DDS信号源进行编程控制,实现特定信号的输出。

3. 学生能够通过实验,分析DDS信号源的性能,提出优化方案。

情感态度价值观目标:1. 学生对电子技术产生兴趣,培养探索精神和创新意识。

2. 学生在实验和讨论过程中,培养团队合作精神和沟通能力。

3. 学生认识到DDS信号源在科技发展中的重要作用,增强社会责任感和使命感。

课程性质:本课程为电子技术实践课程,结合理论讲解和实验操作,提高学生对DDS信号源的理解和应用。

学生特点:学生为高中年级,具备一定的电子技术基础,对实验操作感兴趣,但需引导深入理解理论知识。

教学要求:注重理论与实践相结合,鼓励学生动手实践,培养解决实际问题的能力。

在教学过程中,关注学生个体差异,提供针对性的指导。

通过课程学习,使学生能够将所学知识应用于实际电子技术领域。

二、教学内容1. DDS信号源原理介绍:- 数字频率合成技术背景- DDS信号源基本工作原理- 频率、相位、幅度控制原理2. DDS信号源硬件结构:- 主要组成部分及其功能- 常见DDS芯片介绍- 硬件连接与操作方法3. DDS信号源编程控制:- 编程接口与协议- 常用编程语言及工具- 实例演示:信号生成与调制4. DDS信号源应用案例分析:- 信号发生器- 通信系统- 频率合成器5. 实验教学:- 实验一:DDS信号源基本操作- 实验二:信号生成与调制- 实验三:性能分析与优化6. 教学进度安排:- 第一周:原理介绍与硬件结构学习- 第二周:编程控制与实例演示- 第三周:应用案例分析- 第四周:实验教学与实践教学内容关联教材章节:- 第一章:电子技术基础- 第二章:数字频率合成技术- 第三章:DDS信号源硬件与编程- 第四章:实验与实践三、教学方法本课程采用以下多样化的教学方法,以激发学生的学习兴趣和主动性,提高教学效果:1. 讲授法:- 对于DDS信号源的基本原理、硬件结构、编程控制等理论知识,采用讲授法进行系统讲解,使学生掌握必要的基础知识。

DDS信号发生器设计和实现

DDS信号发生器设计和实现一、引言DDS(Direct Digital Synthesis)是一种基于数字信号处理技术的信号发生器设计方法。

DDS信号发生器是通过数字的方式直接生成模拟信号,相比传统的方法,具有频率稳定、调制灵活、抗干扰能力强等优势,广泛应用于频率合成、通信系统测试、医疗设备、雷达系统等领域。

本文将介绍DDS信号发生器的设计和实现。

二、DDS信号发生器的原理1.相位累加器:负责生成一个连续增加的相位角,通常以一个固定精度的二进制数表示。

2.频率控制器:用于控制相位累加器的相位角速度,从而控制信号的频率。

3.数字到模拟转换器:将相位累加器的输出转换为模拟信号。

4.系统时钟:提供时钟信号给相位累加器和频率控制器。

三、DDS信号发生器的设计步骤1.确定要生成的信号的频率范围和精度需求。

2. 选择适合的数字信号处理器或FPGA进行设计。

常用的DSP芯片有AD9910、AD9858等,FPGA则可选择Xilinx、Altera等厂商的产品。

3.根据需求设计相位累加器和频率控制器,相位累加器的位数和频率控制器的速度决定了信号的精度。

4.确定数字到模拟转换器的采样率和分辨率,选择合适的D/A转换芯片。

5. 编写控制程序和信号生成算法,包括相位累加器和频率控制器的控制。

可以使用C语言、Verilog HDL等进行编程。

6.进行硬件的布局和连线,将各个组件按照设计要求进行连接。

7.进行电源和接地的设计,确保稳定的供电和减少噪声干扰。

8.进行数字信号处理器或FPGA的编程,烧录控制程序。

9.进行信号输出测试,调整参数和算法,确保生成的信号符合要求。

10.编写使用说明书和性能测试报告,并对信号发生器进行完整性和可靠性测试。

四、DDS信号发生器的实现案例以实现一个简单的正弦信号发生器为例,介绍DDS信号发生器的实现过程。

1.确定生成的正弦信号范围为1Hz~10kHz,精度为0.1Hz。

2. 选择Xilinx的FPGA芯片,根据需要设计12位的相位累加器和24位的频率控制器。

DDS信号源设计原理

DDS信号源设计原理DDS(Direct Digital Synthesis,直接数字合成)是一种通过数字方式生成频率可调的信号的技术。

它主要由数字频率合成器(NCO)、数字控制的相位发生器和数字滤波器组成。

DDS信号源的设计原理涉及到数字信号处理、频率合成、相位发生和滤波等方面。

首先,DDS信号源的核心是数字频率合成器(NCO),它可以生成具有可调频率和可编程幅度的周期性信号。

NCO通过将一个参考时钟的频率分频得到一个相对稳定的时钟信号,并使用累加器来计算相位增量,然后通过查表的方式生成所需频率的正弦(或余弦)波形。

由于NCO的频率可以通过改变相位增量来实现,因此可以非常方便地实现频率的可编程性。

其次,DDS信号源在频率合成的过程中,利用相位发生器来实现频率可调。

相位发生器的作用是将相位增量乘以一个系数(在一定精度下实现乘法可以采用简化的移位和累加操作),得到每个时刻的相位值,并利用相位值查询三角函数表得到对应的幅度值。

通过改变相位增量和系数,可以实现对频率的精确控制。

此外,DDS信号源还采用数字滤波器来去除合成信号中的高频成分和噪声。

由于NCO合成的信号是采样间隔上是离散的,因此会引入非线性失真和混频等问题,这些问题都会导致合成信号中存在高频成分。

数字滤波器可以通过差分方程或频域滤波器的方式实现,将合成信号的频谱进行滤波,剔除不需要的高频成分和噪声。

总的来说,DDS信号源的设计原理可以归结为以下几个步骤:1)使用NCO生成参考时钟的分频时钟和相位增量;2)采用相位发生器将相位增量和系数相乘得到相位值;3)查表得到对应的幅度值;4)利用数字滤波器对合成信号进行滤波,去除高频成分和噪声;5)输出滤波后的合成信号。

DDS信号源具有以下优点:1)频率可调范围广;2)分辨率高,频率精度高;3)相位连续性好,相位精度高;4)幅度可编程;5)输出信号稳定性好;6)具有快速切换、变频和调制的能力等。

因此,在许多领域,例如无线通信、雷达测距、音频信号处理等方面都广泛应用了DDS信号源技术。

基于dds技术的信号源设计

基于dds技术的信号源设计DDS技术是目前广泛应用于数字信号处理和通信的核心技术之一。

基于DDS技术的信号源设计可以实现高精度、高稳定性、高灵活性和低噪声等优异的性能,因此在无线通信系统、卫星通信、雷达系统、测量仪器等领域得到了广泛应用。

一、DDS技术简介DDS全称Direct Digital Synthesis,即直接数字合成技术。

它是一种基于数字信号处理技术和先进的ASIC、FPGA和DSP技术的数字频率合成器。

数字频率合成技术是一种通过数字计算实现频率合成的技术,它克服了传统的模拟频率合成器存在频率稳定度和相位噪声等问题。

二、基于DDS技术的信号源设计基于DDS技术的信号源设计主要包括两个方面,即DDC和DUC。

1.DDCDDC全称Digital Down-Converter,即数字下变频器。

它是一种基于DDS技术实现的数字信号处理器件,能够将高频率信号数字化并进行数字信号处理,提取出信号中的基带信号或低通信号。

通常采用FPGA或DSP为核心芯片,通过数字计算、滤波、放大等步骤实现信号处理功能。

2.DUCDUC全称Digital Up-Converter,即数字上变频器。

它是一种基于DDS技术实现的数字信号处理器件,能够将基带信号或低通信号进行数字信号处理,并将其变换到高频率,形成高频信号。

通常采用FPGA或DSP为核心芯片,通过数字计算、滤波、放大等步骤实现信号处理功能。

三、基于DDS技术的信号源设计的优势基于DDS技术的信号源设计比传统的信号源设计具有许多优势:1.高精度:DDS技术采用数字计算的方式实现信号合成,能够实现非常高的频率精度和相位精度,使得合成的信号具有非常高的精度。

2.高稳定性:DDS技术能够对合成信号的频率、相位和幅度等参数进行精确控制,使得信号具有非常高的稳定性,不会因为环境温度或供电电压等因素的变化而导致信号出现偏差。

3.高灵活性:DDS技术能够实现任意的信号合成,使得用户能够非常灵活地产生各种形式的信号。

DDS信号源的设计

EDA技术与实践教程课题:DDS信号源的设计姓名:班级:DDS信号源的设计一.DDS的概述DDS是一种以全数字技术从相位概念出发直接合成所需波形的一种频率合成技术。

目前使用最广泛的方式是利用高速存储器查找表,然后通过高速DAC 输出已经用数字形式存入的正弦波。

DDS技术一般都是以数字控制振荡器NCO (Numerically Controlled Oscillator)为核心,来产生频率可调的sin正弦波的波形的数字量表示的幅值。

这些数字量表示的波形幅值再通过一个DAC (Digital-Analog Converter),得到正弦波的模拟量波形。

它是在时域中进行频率合成,从而能够对输出频率进行快速而且精确的控制,并且这种控制全部都是数字控制,因此可以提供非常高的频率精度。

二.DDS工作原理DDS的基本原理是利用采样定理,通过查表法产生波形。

DDS的结构有很多种,其基本的电路原理可用下图1 来表示:相位累加器由N位加法器与N位累加寄存器级联构成。

每来一个时钟脉冲FS,加法器将频率控制字K与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的数据输入端。

累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。

这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。

由此可以看出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。

用相位累加器输出的数据作为波形存储器(ROM)的相位取样地址,这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。

波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。

低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

DDS信号源设计数字系统设计实践

数字系统设计实践设计报告实验DDS信号源的设计摘要DDS是直接数字频率合成的缩写。

DDS技术是直接数字频率合成技术。

属于第三代频率合成技术,从“相位”概念合成频率。

该电路频率分辨率高,可实现快速频率切换,且在变化时能保持相位连续,易于实现频率、相位和幅度的数控调制。

利用DDS的这些优点,本实验采用FPGA+DAC设计了DDS信号发生器。

这个程序会输入一个频率控制字,然后传输到相位累加器,输出高8位到正弦查找表。

存储在表中的数字波形将由D/A转换器处理并滤波形成模拟波形。

控制字和输出频率将通过乘法器和除法器由十六进制转换成十进制,并显示在数码管上。

关键词:DDS,信号发生器,相位累积,频率目录一、设计任务1二、设计要求1三、系统方案13.1 频率控制字输入模块的论证与选择13.2 rom模块的论证与选择13.3 相位累加器模块的论证与选择23.4 相位寄存器模块的论证与选择23.5 频率控制字M转码输出模块的论证与选择2 3.6 输出频率转化输出模块的论证与选择33.7 输出选择模块的论证与选择3四、系统理论分析与计算34.1理论分析34.2理论计算4五、电路与程序设计45.1电路的设计45.1.1DDS信号源顶层图形设计45.1.2系统电路原理图55.2程序的设计55.2.1频率控制字输入模块的vhdl设计65.2.2相位累加器模块的vhdl设计75.2.3输出选择模块的vhdl设计8六、测试方案与测试结果96.1测试方案96.1.1软件测试96.1.2硬件测试96.2测试结果与分析106.2.1.测试结果106.2.2.测试分析与结论12一、设计任务利用FPGA+DAC设计了DDS信号发生器。

二、设计要求1.分辨率优于1Hz2.ROM表长8位,宽10位。

3.输出频率优于100kHz(每周期50点以上)4.显示信号频率/频率控制字(可切换)5.输入频率控制字或直接输出频率。

三、系统方案3.1频率控制字输入模块的演示和选择选项1:输入三位二进制数进行选择,分别给M加1,10,100,1000,10000,100000。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

为提高信号发生器的便携程度,本文提出了一种可以随身携带的宽带数字式信号源的设计方法:首先,系统以AD9834芯片为信号发生单元,通过单片机控制产生不同类型和频率的波形,分析了基于椭圆滤波器的设计方法,提出通过VCA810压控放大器实现多级信号放大,利用AD8132进行信号的精密整流和信号幅度采集,最后通过程控电阻进行线性电源芯片的电压控制输出。

该方法设计的信号发生器系统具备更便携、低成本、小体积、高性能等优点,克服传统DDS设计的不足,使得所设计的DDS信号源在低成本、低功耗方面有一个较大跃进。

1.引言直接数字频率合成技术(DDS)是一种新的频率合成技术(王文华,基于DDS技术的任意波形发生器研究:浙江大学,2002),它具有频率分辨率极高、频率切换速度快、切换相位连续、可输出宽带正交信号、输出信号相位噪声低、可产生任意波形、易于集成、体积小、重量轻等优点。

DDS的这些优点使得它已成为雷达、通信等系统中信号源的首选,是实现设备全数字化的一个关键技术(Solomon Max.Direct AWG sine wave synthesis with fixed clock frequency:Measurements,2002;Cardells-Tormo,F. Valls-Coquillat,A.Optimized FPGA-implementation of quadrature DDS:IEEE International Symposium on Circuits and Systems,2002;Chimakurthy,L.S.J.,Ghosh,M.,Dai,F.F.,Jaeger,R.C.A novel DDS using nonlinear ROM addressing with improved compression ratio and quantization noise:IEEE Transactions on Ultrasonics,Ferroelectrics and Frequency Control,2006;Ma Pinhong,Liu Ping.A Design of AWG Based on DDS Using the SOPC Technique:IEEE CEEM 2006)。

本文设计的DDS宽带信号源综合采用直接频率合成(DDS)、微处理器(MCU)、宽带信号放大与处理、幅度控制等技术。

DDS、MCU及其外围电路单元共同完成正弦波、三角波、方波等信号的输出功能;信号的输出参数可通过键盘进行设定,输出信号的类型、频率、幅度等关参数可以同时在液晶显示屏上显示。

2.系统概述图1 DDS信号源整体方案设计整个系统由电源管理部分(M1)、信号产生及处理部分(M2)和信号输出部分(M3)三部分组成。

在电池供电环境下,由电子开关及电压转换器件等组成的电源管理模块通过合理分配电能满足各模块的需求;MCU控制DDS发生器产生用户所需类型信号,并通过信号采集及幅度控制调整信号幅度,TTL/CMOS电平输出由升压电路配合DDS信号模块完成;液晶显示器和键盘作为输入输出设备为用户提供方便、快捷的功能切换和显示(康华光,电子技术基础模拟部分:高等教育出版社,2006)。

手持式DDS信号源的设计与开发常州市凯迪电器股份有限公司 姚步堂 郭发勇3.硬件系统设计3.1 AD9834波形输出设计AD9834信号输出幅度有公式,式中V refout 为AD9834内置电压,标准为1.2V ,R load 为负载电阻,为图2中RD4,R set 为配置电阻,为图2中RD1,为了使得输出信号失真度小、SDFR 大,通过调试发现不要改动RD1和RD4规定的标准值(分别为6.8K 欧姆和200欧姆),且应选择精度为0.1%的贴片电阻;此外,图2中电容CD9的存在起到了低通滤波器的作用,故CD9不可选取过大,经过反复调试,最终确定该电容选为10-20PF为宜。

图2 AD9834电路原理图3.2 椭圆滤波器设计本设计采用椭圆函数型滤波器,椭圆函数型滤波器在通带和阻带内都有起伏,由于通带内特性和阻带内特性都允许有起伏,因而椭圆函数型滤波器具有良好的截止特性(森 荣二,LC 滤波器设计与制作:科学出版社,2005)。

椭圆滤波器的设计步骤是首先考虑滤波的幅频特性、电路的输入输出阻抗匹配、截止频率等,然后根据设计参数确定具体曲线和归一化的元件值,最后再依据实际指标去归一化后得到实际的元件值。

欲设计技术指标是阻带频率是30M H z ,通带内起伏量为0.1dB ,特征阻抗为50Ω,阻带频率为2倍,阻带内有三个陷波点的七阶椭圆函数型LPF 。

归一化LPF ,特征阻抗为1Ω且截止频率为1/2πHz 的LPF ,可以根据这种归一化LPF 设计实际的滤波器各元件参数。

有两个步骤:截止频率变换和特征阻抗变换(徐云,迟忠君,张凯洪,等.基于DDS 技术的双通道任意波形信号发生器:仪器仪表学报,2006)。

以计算X1与X3(X1为电容,X3为电感)为例,C old =1.0037F ,L old =1.186398H ;由式:(1)特征阻抗变换的过程如下:(2) (3) (4)(5) (6)特征阻抗为1Ω且截止频率为1/2πHz 的元件参数见表1:表1 初始元件参数X1X2X3X4X51.003710.20165 1.18639 1.936980.03412X6X7X8X9X101.545601.985320.1269411.2702271.067202由(3)至(8)式可求得各元件的最终参数见表2:表2 元件参数最终结果X1X3X4X5106315205 3.6X6X8X9X1041013.4337112.7注:X3,X6,X9的单位是nH,其余元件参数是单位是pF。

由于从AD9834直接产生的信号是不符合正常使用的(对地的真有效值不为0),故先通过电容耦合,再通过电压跟随器和低通滤波器滤除信号噪声和干扰并提供0V 基准电压。

设计的椭圆滤波器电路如图3所示(图中所示为实际采用值):图3 七阶椭圆滤波器3.3 幅度控制模块设计在本方案中直接采用压控放大器实现幅度控制,压控放大器采用TI 公司的VGA 芯片VCA810提供宽带宽、宽增益调节范围(-40dB 至+40dB ),其3脚为增益控制引脚,设输入到该引脚的电平为V C ,则增益为,V C 脚输入电平范围为-2V 至0V ;采用TI 公司12bit 的TLV5638数模转换器,该D/A 内部自带基准电压、可通过设置寄存器输出0V 至2.048V 电平,通过减法器即可实现输入电平范围为-2V 至0V 的高精度增益控制,非常适合在此使用;后级调整运放采用TI 公司的轨至轨高速运算放大器THS4221实现10V 峰峰值输出。

其原理图如图4所示。

图4 VGA模块原理图图5 精密整流3.4 精密整流模块采用精密整流技术实现信号整流和平波,本方案采用AD8132实现,AD8132是一款低成本、差分或单端输入至差分输出放大器,通过电阻设置增益。

相对于运算放大器,AD8132在驱动差分输入ADC 或驱动长线路信号方面取得了重大进步。

它具有独特的内部反馈特性,在+10MHz 时可提供于-68dB 达成的输出增益和相位匹配平衡,能够抑制谐波并降低辐射电磁干扰(EMI)。

AD8132采用ADI 公司新一代XFCB 双极性工艺制造,-3dB 带宽为350MHz ,提供差分信号,+5MHz 时的无杂散动态范围(SFDR)为-99dBc ,而且成本低廉。

该器件无需使用具有高性能ADC 的变压器,并保留低频和直流信息。

在VOCM 引脚上施加电压便可调整差分输出的共模电平。

AD8132的一个重要应用即是实现信号整流、平波(见图5)。

3.5 数控LDO模块在本设计中采用低成本的LM317,采用D 2PAK 封装,数字电位器采用具有1024抽头的X9118,该电位器最大阻值为100K 欧姆。

设计的可控电源原理图为:图6 数数控电源原理图由LM317用法可知,其为1.2V 至37V 可调稳压器,,在此V REF =1.2V ,当V O =5V ,数字电位器阻值为最大100K 欧姆时,计算得到RP1为32K 欧姆,当V O =3V ,此时RD1为48K 欧姆,故数字电位器X9118在48K 欧姆至100K 欧姆之间变化,而数字电位器X9118总共有1024个抽头,满足步进为0.1V 的要求。

3.6 占空比可调模块由AD9834输出端提供三角波,送至超快速比较器TL3016,利用数字电位器提供参考电压,经比较产生占空比可调的方波。

后经电容耦合至由NPN 和PNP 两个三极管组成的推挽电路,可进行PWM 波形输出。

其电路原理图如图7所示。

图7 占空比可调方波产生电路4.结论本设计直接采用MCU 控制DDS专用芯片。

通过本设计的设计图8 手持式DDS信号源实现了一台以锂电池为电源的手持宽带信号源,如图8所示,正弦波输出频率范围为1HZ 至30MHZ ,方波三角波输出频率为1HZ 至500KHZ ;频率输出最小步进为0.1HZ ;设计采用的器件全部使用低功耗器件,可满足电池供电环境,在电池供电的情况下可作为手持式便携设备使用,采用手机液晶屏为首选,输入键盘将多项功能集约,减少按键数量,减小体积,操作更方便。

基金项目:江苏省重点研发计划项目(BE2017007-1)。

作者简介:姚步堂(1974—),现供职于常州市凯迪电器股份有限公司,研究方向为机电控制。

郭发勇(1989—),博士,现供职于常州市凯迪电器股份有限公司,研究方向为机器人与工业电子。

(上接第118页)将连续N 帧图像的像素灰度值的平均值作为背景图灰度值。

需要对背景图进行更新保证背景图的准确度。

每当无列队时就需要重新选取N 帧图像重复上面的步骤。

将原始图像与背景图都输入到向量机中,得到训练的图像。

实际过程中车辆的行驶速度是很快的,常用的车流量检测有三种背景差法、帧差法、基于光流的方法。

本文采用的是三帧差法对车辆进行运动检测(张萍,王琳,游星,基于SVM 分类的边缘提取算法:成都理工大学学报(自然科学版),2017)。

为了更准确的测量出车辆排队长度,提出比较精准的标定办法。

首先对待检测的车道进行标定目标检测框(检测框为黄色)如图4所示,在经过上述处理得到如图5所示的图片。

图4 处理前与图5处理后对检测框设置一个阈值,当框的长度小于这个阈值时,可以判断是车俩长度的末尾,即可算出像素的长度。

但像素的长度仅仅是二维空间长度,还需要进行转换成实际坐标。

图6所示,为摄像机的安装位置与道路示意图,通过式(1)可以将像素距离转换为实际的长度L 。