A Proposal for a High-Performance Active Hardware Architecture

对于这次比赛要求英语作文

对于这次比赛要求英语作文As the upcoming competition requires an English essay, I would like to write a high-quality essay that meets the requirements. After searching online and reading numerous samples, I have decided to write a 1500-word essay on the topic of "The Importance of Learning English."English has become a global language, and it is widely spoken and understood in many countries around the world. In today's world, it is essential to learn English as it is the language of international communication, business, and technology. English is the language of the internet, and it is the language used in most international conferences, meetings, and negotiations. Therefore, learning English is crucial for anyone who wants to succeed in the global economy.There are many benefits of learning English. First, it provides access to a vast array of knowledge and information. The majority of scientific research andpublications are written in English, and many of theworld's top universities use English as their primary language of instruction. By learning English, one can access this wealth of information and knowledge and stay up-to-date with the latest developments in their field.Second, English is the language of business. Many multinational companies use English as their primary language of communication, and it is essential for employees to be proficient in English to succeed in the business world. English is also the language of international trade, and it is crucial for anyone involved in import/export or international business to be able to communicate effectively in English.Third, learning English can open up many opportunities for travel and work abroad. English is the most commonly spoken language in the world, and it is the language used in many tourist destinations. By learning English, one can communicate with people from all over the world and experience different cultures and ways of life. Additionally, knowing English can make it easier to findwork in other countries, as many companies require employees to be proficient in English.Finally, learning English can improve one's cognitive abilities. Studies have shown that learning a second language can improve memory, problem-solving skills, and creativity. Learning English can also improve one's ability to multitask and improve their overall cognitiveflexibility.In conclusion, learning English is essential in today's globalized world. It provides access to knowledge, opens up opportunities for travel and work, and improves cognitive abilities. By investing time and effort into learning English, one can gain a competitive edge in the global economy and succeed in their personal and professional lives.。

英文修订版20100415

Labor Relations Safety & Health

Job Analysis

What to be learned ?

HR Planning

Compensation Management

Planning Security Maintenance Training & Acquirement & Development Deployment

Job Description

Job summary Duties and tasks KPI Organization Structure Chart Knowledge, skills, experience, personalities required

HR Functions

Methods of Data Collecting

What competencies do HRM professionals need?

HRM Professional Competencies

Honesty

Which one is more important?

Ability of Change Management Ability of Culture Management HRM Business Knowledge

The purpose of the job Tasks Responsibilities and duties Relationships Procedures Performance standards Authorities & obligations Context Knowledge, skills, experience, personalities required

BEC商务英语高级写作 建议Proposal PPT

大家应该也有点累了,稍作休息

大家有疑问的,可以询问和交流

on …

to recommend/ to study…

This proposal recommends a solution and provides budget and time schedule figures.

My proposal intends to make our company more effective and more authoritative at achieving its goals through improving the performance of both workers and managers.

2) Benefit:There is no denying that these improvements will bring vast profits to the company. Our employees will be able to work faster, more effectively and make greater use of technological innovations. Moreover, our company will be moreபைடு நூலகம்likely to easily overcome fierce competition in the market.

2. Background

极端环境微生物的研究进展

极端环境微生物的研究进展文件排版存档编号:[UYTR-OUPT28-KBNTL98-UYNN208][摘要]极端微生物通常分为六个类群:嗜热微生物、嗜冷微生物、嗜酸微生物、嗜碱微生物、嗜盐微生物、嗜压微生物。

极端环境中的微生物为了适应生存,逐步形成了独特的结构和生理机能,以适应环境。

因此,研究适应机理并利用其特殊生理机能具有重要的理论和实际意义,极端微生物能产生多种极端酶和其他生物活性物质,极端微生物资源的开发利用有着广阔的前景。

极端环境(extreme environment)泛指存在某些特殊物理和化学状态的自然环境,包括高温、低温、强酸、强碱、高盐、高压、高辐射和极端缺氧环境等,适合在极端环境中生活的微生物称为极端微生物(extremophiles)( Margesin and Schinner,2001【1】;Rothschild and Mancinelli,2001【2】;陈骏等,2006【3】;张敏和东秀珠,2006【4】).海洋极端环境一般是指与正常海洋环境绝然不同的物理化学环境,主要包括海底热泉、海底冷泉和泥火山环境,其次还包括高盐度(卤水)、强酸化、缺氧和滞流等海洋环境。

海洋极端微生物通常为化能自养生物(chemoautotroph),在分类体系上属于细菌和古细菌类,生活在无光、无氧或少氧环境,能利用一些海底热催化反应过程中产生的还原性小分子(H2、H2S和CH4 等)合成能量进行有机碳固定和新陈代谢,具有独特的基因类型、特殊生态群落、特殊生理机理和特殊代谢产物,有些属于内共生生物(endosymbiont)。

一、极端微生物的种类及其生理特点1.1 极端嗜热菌(Thermophiles)一般最适生长温度在90℃以上的微生物,被称做极端嗜热菌【5,6】。

已发现的极端嗜热菌有20多个属,大多是古细菌,生活在深海火山喷口附近或其周围区域【7】。

如斯坦福大学科学家发现的古细菌,最适生长温度为100℃,8O℃以下即失活;德国的斯梯特(K Stette)研究组在意大利海底发现的一族古细菌,能生活在110℃以上高温中,最适生长温度为98℃,降至84℃即停止生长;美国的巴罗斯(J.Baroos)发现一些从火山喷口中分离出的细菌可以生活在250℃的环境中,嗜热菌的营养范围很广。

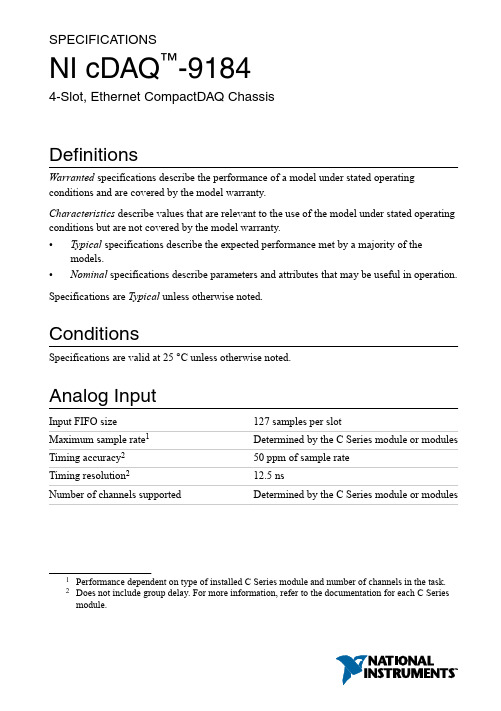

NI cDAQ

SPECIFICA TIONSNI cDAQ™-91844-Slot, Ethernet CompactDAQ ChassisDefinitionsWarranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty.Characteristics describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty.•Typical specifications describe the expected performance met by a majority of the models.•Nominal specifications describe parameters and attributes that may be useful in operation. Specifications are Typical unless otherwise noted.ConditionsSpecifications are valid at 25 °C unless otherwise noted.Analog InputInput FIFO size127 samples per slotMaximum sample rate1Determined by the C Series module or modules Timing accuracy250 ppm of sample rateTiming resolution212.5 nsNumber of channels supported Determined by the C Series module or modules 1Performance dependent on type of installed C Series module and number of channels in the task.2Does not include group delay. For more information, refer to the documentation for each C Series module.Analog OutputNumber of channels supportedHardware-timed taskOnboard regeneration16Non-regeneration Determined by the C Series module or modules Non-hardware-timed task Determined by the C Series module or modules Maximum update rateOnboard regeneration 1.6 MS/s (multi-channel, aggregate)Non-regeneration Determined by the C Series module or modules Timing accuracy50 ppm of sample rateTiming resolution12.5 nsOutput FIFO sizeOnboard regeneration8,191 samples shared among channels used Non-regeneration127 samples per slotAO waveform modes Non-periodic waveform,periodic waveform regeneration mode fromonboard memory,periodic waveform regeneration from hostbuffer including dynamic updateDigital Waveform CharacteristicsWaveform acquisition (DI) FIFOParallel modules511 samples per slotSerial modules63 samples per slotWaveform generation (DO) FIFOParallel modules2,047 samples per slotSerial modules63 samples per slotDigital input sample clock frequencyStreaming to application memory System-dependentFinite0 MHz to 10 MHz2| | NI cDAQ-9184 SpecificationsDigital output sample clock frequencyStreaming from application memory System-dependentRegeneration from FIFO0 MHz to 10 MHzFinite0 MHz to 10 MHzTiming accuracy50 ppmGeneral-Purpose Counters/TimersNumber of counters/timers4Resolution32 bitsCounter measurements Edge counting, pulse, semi-period, period,two-edge separation, pulse widthPosition measurements X1, X2, X4 quadrature encoding withChannel Z reloading; two-pulse encoding Output applications Pulse, pulse train with dynamic updates,frequency division, equivalent time sampling Internal base clocks80 MHz, 20 MHz, 100 kHzExternal base clock frequency0 MHz to 20 MHzBase clock accuracy50 ppmOutput frequency0 MHz to 20 MHzInputs Gate, Source, HW_Arm, Aux, A, B, Z,Up_DownRouting options for inputs Any module PFI, analog trigger, many internalsignalsFIFO Dedicated 127-sample FIFOFrequency GeneratorNumber of channels1Base clocks20 MHz, 10 MHz, 100 kHzDivisors 1 to 16 (integers)Base clock accuracy50 ppmOutput Any module PFI terminalNI cDAQ-9184 Specifications| © National Instruments| 3Module PFI CharacteristicsFunctionality Static digital input, static digital output, timinginput, and timing outputTiming output sources3Many analog input, analog output, counter,digital input, and digital output timing signals Timing input frequency0 MHz to 20 MHzTiming output frequency0 MHz to 20 MHzDigital TriggersSource Any module PFI terminalPolarity Software-selectable for most signalsAnalog input function Start Trigger, Reference Trigger,Pause Trigger, Sample Clock,Sample Clock TimebaseAnalog output function Start Trigger, Pause Trigger, Sample Clock,Sample Clock TimebaseCounter/timer function Gate, Source, HW_Arm, Aux, A, B, Z,Up_DownModule I/O StatesAt power-on Module-dependent. Refer to the documentationfor each C Series module.Network InterfaceNetwork protocols TCP/IP, UDPNetwork ports used HTTP:80 (configuration only), TCP:3580;UDP:5353 (configuration only), TCP:5353(configuration only); TCP:31415; UDP:7865(configuration only), UDP:8473 (configurationonly)Network IP configuration DHCP + Link-Local, DHCP, Static,Link-Local3Actual available signals are dependent on type of installed C Series module.4| | NI cDAQ-9184 SpecificationsHigh-performance data streams7Data stream types available Analog input, analog output, digital input,digital output, counter/timer input,counter/timer output, NI-XNET4Default MTU size1500 bytesJumbo frame support Up to 9000 bytesEthernetNetwork interface1000 Base-TX, full-duplex; 1000 Base-TX,half-duplex; 100 Base-TX, full-duplex;100 Base-TX, half-duplex; 10 Base-T,full-duplex; 10 Base-T, half-duplex Communication rates10/100/1000 Mbps, auto-negotiated Maximum cabling distance100 m/segmentPower RequirementsCaution The protection provided by the NI cDAQ-9184 chassis can be impaired ifit is used in a manner not described in the NI cDAQ-9181/9184/9188/9191 UserManual.Note Some C Series modules have additional power requirements. For moreinformation about C Series module power requirements, refer to the documentationfor each C Series module.Note Sleep mode for C Series modules is not supported in the NI cDAQ-9184.V oltage input range9 V to 30 VMaximum power consumption515 W4When a session is active, CAN or LIN (NI-XNET) C Series modules use a total of two data streams regardless of the number of NI-XNET modules in the chassis.5Includes maximum 1 W module load per slot across rated temperature and product variations.NI cDAQ-9184 Specifications| © National Instruments| 5Note The maximum power consumption specification is based on a fully populatedsystem running a high-stress application at elevated ambient temperature and withall C Series modules consuming the maximum allowed power.Power input connector 2 positions 3.5 mm pitch mini-combicon screwterminal with screw flanges, SauroCTMH020F8-0N001Power input mating connector Sauro CTF020V8, Phoenix Contact 1714977,or equivalentPhysical CharacteristicsWeight (unloaded)Approximately 643 g (22.7 oz)Dimensions (unloaded)178.1 mm × 88.1 mm × 64.3 mm(7.01 in. × 3.47 in. × 2.53 in.) Refer to thefollowing figure.Screw-terminal wiringGauge0.5 mm 2 to 2.1 mm2 (20 AWG to 14 AWG)copper conductor wireWire strip length 6 mm (0.24 in.) of insulation stripped from theendTemperature rating85 °CTorque for screw terminals0.20 N · m to 0.25 N · m (1.8 lb · in. to2.2 lb · in.)Wires per screw terminal One wire per screw terminalConnector securementSecurement type Screw flanges providedTorque for screw flanges0.20 N · m to 0.25 N · m (1.8 lb · in. to2.2 lb · in.)If you need to clean the chassis, wipe it with a dry towel.6| | NI cDAQ-9184 SpecificationsFigure 1. NI cDAQ-9184 Dimensions30.6 mm 47.2 mm Safety VoltagesConnect only voltages that are within these limits.V terminal to C terminal30 V maximum, Measurement Category IMeasurement Category I is for measurements performed on circuits not directly connected to the electrical distribution system referred to as MAINS voltage. MAINS is a hazardous liveNI cDAQ-9184 Specifications | © National Instruments | 7electrical supply system that powers equipment. This category is for measurements of voltages from specially protected secondary circuits. Such voltage measurements include signal levels, special equipment, limited-energy parts of equipment, circuits powered by regulatedlow-voltage sources, and electronics.Caution Do not connect the system to signals or use for measurements withinMeasurement Categories II, III, or IV.Note Measurement Categories CAT I and CAT O (Other) are equivalent. These testand measurement circuits are not intended for direct connection to the MAINsbuilding installations of Measurement Categories CAT II, CAT III, or CAT IV.Environmental-20 °C to 55 °C6Operating temperature (IEC 60068-2-1and IEC 60068-2-2)Caution To maintain product performance and accuracy specifications when theambient temperature is between 45 and 55 °C, you must mount the chassishorizontally to a metal panel or surface using the screw holes or the panel mount kit.Measure the ambient temperature at each side of the CompactDAQ system 63.5 mm(2.5 in.) from the side and 25.4 mm (1.0 in.) from the rear cover of the system. Forfurther information about mounting configurations, go to /info and enterthe Info Code cdaqmounting.-40 °C to 85 °CStorage temperature (IEC 60068-2-1 andIEC 60068-2-2)Ingress protection IP 30Operating humidity (IEC 60068-2-56)10% to 90% RH, noncondensingStorage humidity (IEC 60068-2-56)5% to 95% RH, noncondensingPollution Degree (IEC 60664)2Maximum altitude5,000 mIndoor use only.6When operating the NI cDAQ-9184 in temperatures below 0 °C, you must use the PS-15 powersupply or another power supply rated for below 0 °C.8| | NI cDAQ-9184 SpecificationsHazardous LocationsU.S. (UL)Class I, Division 2, Groups A, B, C, D, T4;Class I, Zone 2, AEx nA IIC T4Canada (C-UL)Class I, Division 2, Groups A, B, C, D, T4;Class I, Zone 2, Ex nA IIC T4Europe (ATEX) and International (IECEx)Ex nA IIC T4 GcShock and VibrationTo meet these specifications, you must direct mount the NI cDAQ-9184 system and affix ferrules to the ends of the terminal lines.Operational shock30 g peak, half-sine, 11 ms pulse (Tested inaccordance with IEC 60068-2-27. Test profiledeveloped in accordance withMIL-PRF-28800F.)Random vibrationOperating 5 Hz to 500 Hz, 0.3 g rmsNon-operating 5 Hz to 500 Hz, 2.4 g rms (Tested in accordancewith IEC 60068-2-64. Non-operating testprofile exceeds the requirements ofMIL PRF-28800F, Class 3.)Safety and Hazardous Locations StandardsThis product is designed to meet the requirements of the following electrical equipment safety standards for measurement, control, and laboratory use:•IEC 61010-1, EN 61010-1•UL 61010-1, CSA C22.2 No. 61010-1•EN 60079-0:2012, EN 60079-15:2010•IEC 60079-0: Ed 6, IEC 60079-15; Ed 4•UL 60079-0; Ed 6, UL 60079-15; Ed 4•CSA 60079-0:2011, CSA 60079-15:2012Note For UL and other safety certifications, refer to the product label or the OnlineProduct Certification section.NI cDAQ-9184 Specifications| © National Instruments| 9Electromagnetic CompatibilityThis product meets the requirements of the following EMC standards for electrical equipment for measurement, control, and laboratory use:•EN 61326-1 (IEC 61326-1): Class A emissions; Basic immunity•EN 55011 (CISPR 11): Group 1, Class A emissions•EN 55022 (CISPR 22): Class A emissions•EN 55024 (CISPR 24): Immunity•AS/NZS CISPR 11: Group 1, Class A emissions•AS/NZS CISPR 22: Class A emissions•FCC 47 CFR Part 15B: Class A emissions•ICES-001: Class A emissionsNote In the United States (per FCC 47 CFR), Class A equipment is intended foruse in commercial, light-industrial, and heavy-industrial locations. In Europe,Canada, Australia and New Zealand (per CISPR 11) Class A equipment is intendedfor use only in heavy-industrial locations.Note Group 1 equipment (per CISPR 11) is any industrial, scientific, or medicalequipment that does not intentionally generate radio frequency energy for thetreatment of material or inspection/analysis purposes.Note For EMC declarations and certifications, and additional information, refer tothe Online Product Certification section.CE ComplianceThis product meets the essential requirements of applicable European Directives, as follows:•2014/35/EU; Low-V oltage Directive (safety)•2014/30/EU; Electromagnetic Compatibility Directive (EMC)•2014/34/EU; Potentially Explosive Atmospheres (ATEX)Online Product CertificationRefer to the product Declaration of Conformity (DoC) for additional regulatory compliance information. To obtain product certifications and the DoC for this product, visit / certification, search by model number or product line, and click the appropriate link in the Certification column.10| | NI cDAQ-9184 SpecificationsEnvironmental ManagementNI is committed to designing and manufacturing products in an environmentally responsible manner. NI recognizes that eliminating certain hazardous substances from our products is beneficial to the environment and to NI customers.For additional environmental information, refer to the Minimize Our Environmental Impact web page at /environment. This page contains the environmental regulations and directives with which NI complies, as well as other environmental information not included in this document.Waste Electrical and Electronic Equipment (WEEE) EU Customers At the end of the product life cycle, all NI products must bedisposed of according to local laws and regulations. For more information abouthow to recycle NI products in your region, visit /environment/weee.电子信息产品污染控制管理办法(中国RoHS)中国客户National Instruments符合中国电子信息产品中限制使用某些有害物质指令(RoHS)。

a级英语作文模板请求信

a级英语作文模板请求信英文回答:Dear [Recipient Name],。

I hope this letter finds you well. I am writing to request your assistance in providing a sample of an A-level English template for a formal letter. As a student preparing for my A-level examinations, this resource would be of great value in developing my writing skills and improving my performance in the exam.I have been diligent in my studies and haveconsistently achieved high marks in my coursework. However, I believe that having access to a well-structured template would further enhance my ability to craft effective and persuasive formal letters. Such a template would provide me with a clear framework to follow, ensuring that my letters adhere to the conventions of formal writing and meet the expectations of the examiners.The template should ideally include sections for the following:Header: Including the sender's address, date, and recipient's address。

bec作文proposal格式

bec作文proposal格式英文回答:As a BEC (Business English Certificate) candidate, I would like to propose a format for the BEC writing task. The writing task is an important part of the BEC exam, and it is crucial to have a clear and effective format to follow. In my proposal, I will outline a format that I believe will help candidates to organize their ideas and write a coherent and persuasive essay.Firstly, the writing task should begin with an introduction that clearly states the topic and the candidate's position on the topic. This introduction should be concise and engaging, and it should provide a preview of the main points that will be discussed in the essay. For example, if the topic is about the advantages and disadvantages of working from home, the introduction should briefly mention the benefits and drawbacks of remote work.Next, the body of the essay should be divided into paragraphs, with each paragraph focusing on a different main point. Each paragraph should begin with a topic sentence that introduces the main point, followed by supporting details and examples. It is important to use transition words and phrases to connect the paragraphs and create a smooth flow of ideas. For instance, when discussing the benefits of remote work, one paragraph could focus on the flexibility it offers, while another paragraph could discuss the cost savings for both employees and employers.Finally, the essay should conclude with a summary of the main points and a restatement of the candidate's position on the topic. The conclusion should leave a strong impression on the reader and reinforce the main arguments presented in the essay. It is also a good idea to end with a call to action or a thought-provoking statement to leave the reader thinking about the topic.中文回答:作为一名BEC(商务英语证书)考生,我想提出一个BEC写作任务的格式。

找理想工作的英语作文

Finding the ideal job is a pursuit that many individuals embark on throughout their professional lives.The concept of an ideal job is subjective and varies from person to person,but there are certain universal aspects that contribute to making a job ideal.Here are some key points to consider when crafting an English essay on finding the ideal job:Title:The Quest for the Ideal JobIntroduction:The essay begins by defining what an ideal job means to different people.It sets the stage for discussing the common elements that make a job ideal,such as job satisfaction,financial stability,worklife balance,and career growth.Paragraph1:SelfUnderstandingThe first step in finding the ideal job is selfreflection.Understanding ones strengths, weaknesses,passions,and values is crucial.Discuss how selfawareness can guide job seekers towards careers that align with their personality and interests.Paragraph2:Research and ExplorationEmphasize the importance of researching various industries and job roles to gain a comprehensive understanding of the job market.Highlight the role of informational interviews,job shadowing,and networking in gathering insights about different professions.Paragraph3:Education and Skill DevelopmentDiscuss how continuous learning and skill development are essential for career advancement and finding the ideal job.Mention the value of formal education,certifications,and onthejob training in enhancing employability.Paragraph4:Setting Realistic GoalsExplain the significance of setting achievable career goals and the role of goalsetting in maintaining motivation and focus.Provide examples of SMART goals Specific,Measurable,Achievable,Relevant, Timebound in a job search context.Paragraph5:Adaptability and FlexibilityArgue that adaptability is a key trait for finding and maintaining an ideal job in a rapidly changing job market.Discuss how being open to new opportunities and flexible in ones career path can lead tounexpected but fulfilling job roles.Paragraph6:The Importance of NetworkingElaborate on the power of networking in uncovering job opportunities that may not be publicly advertised.Describe how building professional relationships can provide support,mentorship,and access to job leads.Paragraph7:WorkLife BalanceDiscuss the importance of finding a job that allows for a healthy balance between work and personal life.Mention how worklife balance contributes to overall wellbeing and job satisfaction.Paragraph8:Persistence and ResilienceEmphasize the need for persistence and resilience in the job search process,especially when facing rejections or setbacks.Provide tips on maintaining a positive attitude and learning from each job search experience.Conclusion:Summarize the key points discussed in the essay.Conclude by reiterating that finding the ideal job is a personal journey that requires selfawareness,continuous learning,and adaptability.Final Thoughts:Encourage readers to stay true to their values and aspirations while pursuing their ideal job.End on a hopeful note,suggesting that with determination and the right approach, anyone can find a job that brings them fulfillment and satisfaction.Remember to use clear,concise language and provide concrete examples to illustrate your points.The essay should be wellstructured,with a logical flow of ideas that guides the reader through your argument.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

A Proposal for a High-Performance Active Hardware ArchitectureTilman WolfWUCS-99-08February 15, 1999A Proposal for a High-Performance Active HardwareArchitectureTilman WolfDepartment of Computer ScienceWashington UniversityOne Brookings DriveSt. Louis, MO 63130wolf@February 15, 1999Current research in Active Networking is focused on developing softwarearchitectures and defining functionality of Execution Environments. Whileactive network systems show superior functionality compared to traditionalnetworks, they only operate at substantially lower link speeds. To increase theacceptance of Active Networks in environments where link speeds of severalGb/s are common, we propose a hardware architecture that performs high-speedpacket handling while providing the same flexibility as a common softwaresystem. The design exploits the independence between data streams for parallelprocessing. To measure the impact of different design decisions on theperformance of the system, we also propose a benchmark for Active Networkcomponents. This benchmark can be used for many Active Networkarchitectures and can help to standardize performance results.IntroductionActive networking is a new approach to generalize the capability of networks. By executing end user specified programs within the network, data packets can be handled in a customized way. This allows the easy introduction of new network layer protocols and applications without changing components of the network infrastructure. [1]To implement an active network, traditional network routers have to be augmented by the capability to execute customized code, which goes beyond the common header processing and signaling. Currently, this is achieved by using workstations as routers in the experimental ABONE [3]. The processing power of the general-purpose workstation CPU is shared among the operating system, the Execution Environment, and the processing of active packets. The limited computational power of the workstation restricts the data traffic to a few Mb/s [6]. This data rate is several orders of magnitude below the bandwidth of new data networks, which operate in the Gb/s range. For the evolving field of active networks it is crucial to be competitive withrespect to the end-to-end performance of current networks. This can be achieved partially by providing superior functionality. However, the throughput of an active network system also has to be increased to the range of Gb/s, otherwise the acceptance of active networks for real-world applications might be low.There is an approach that makes use of specialized hardware in form of an FPGA [4]. However, the complex programming and the incompatibility with software that is developed for Active Execution Environments (EE) limit the widespread use.Here we propose a hardware architecture for a high-performance Active Network Processing Element (ANPE) that can operate at link speeds in the range of Gb/s. This ANPE can be used on line cards of active routers in combination with a traditional high-performance switching fabric. Also, the ANPE can be used on network interface cards of workstations to reduce the load on the workstation CPU caused by processing active network traffic. The proposed hardware is designed to fit on a single ASIC. Such system-on-a-chip technology allows for the necessary high performance of all components to support high-bandwidth data traffic. The design is general enough to be used for different Execution Environment to make use of the most recent developments in Active Network software systems.In order to measure the performance of this system and compare it to other active network architectures, we propose a benchmark for active network components. This benchmark defines several typical Active Applications (AA) which cover a wide range of computational complexity and bandwidth, a suggested test environment, and measurement procedures.The following section describes a hardware architecture that makes use of the parallel nature of data streams to achieve high performance. Its functionality is illustrated, and concurrency and performance issues are described. The Active Processing Unit (APU) which provides the Execution Environment for the processing of the active packet is explained.The last section describes the proposed benchmark. The characteristics of Active Applications are described and used to determine a set of benchmark applications and a test environment.Hardware ArchitectureOur proposal for an Active Network Processing Element in hardware is based on current developments in ASIC technology. It is possible to combine flow classification, routing lookup, active processing, and scheduling in a single design. We show that parallel processing can be used to achieve high performance while keeping concurrency issues minimal.System-on-a-chip technologyThe levels of integration and chip sizes have increased over the last years to the point where it is possible to combine a processor and memory on a single ASIC. Thissystem-on-a-chip technology provides an easy way to build an ANPE with high computational power that is specialized on processing active network traffic.The conventional measure for the size of an ASIC is the number of logic gates or transistors on a chip. Figure 1 shows some real world examples obtained from press releases of several ASIC manufacturers. It shows that the number of logic gates approximately doubles each year. This estimate is a little bit more optimistic than predicted my Moore’s Law, which expects the size to double every 18 months.With an increasing level of integration, not only the size of ASICs increase, but also the clock speeds at which they are driven. Current clock rates can range up to 500 MHz.Fig. 1. Development in ASIC technology. The graph shows the number of logic gates that can be implemented on an ASIC. The increase is caused by larger die sizes as well as smaller feature sizes.As a direct result of improvements in hardware technology, the complexity of state-of-the-art processors increases, too. Figure 2 shows the transistor count of several lines of CPUs. The transistor count relates to the gate count of the ASIC 10:1. It shows that the CPU size doubles every two years, which is a smaller rate than the growth of ASICs.While today it is only possible to combine one or two processors with memory and control logic, one can expect that in a few years up to a dozen CPUs and memory can be put on a single ASIC. This assumption is the basis for our hardware design.Fig. 2. Development in CPU size. The graph shows the size of state-of-the art CPUs. The transistor count relates roughly 10:1 with the logic gate count from Figure 1.System OverviewWe propose to build an ASIC that contains all functionality required for the processing of active data traffic. The ASIC is designed to be easily used on line cards of common routers and on network interface cards of workstations to upgrade traditional network equipment to handle active data traffic. Figure 3 shows a system outline.Fig. 3. System outline for an Active Network using Active Network Processing Elements (ANPE). The main application for the ANPE is on line cards of routers where it processes and forwards active data packets. However, the ANPE can also be used on network interface cards of workstations where it decreases the load on the workstation CPU by handling the processing of active data traffic.Functional DesignOne goal of the ANPE design is to exploit the parallel nature of independent active data streams. In most cases, data of one stream is independent from data of other streams. This leads to the observation that, for most traffic, there is only a dependency between the packets of a particular stream. Therefore, packets need to be processed in order to assure that state information is accessible and consistent for all packets of a stream. The lack of inter-stream dependencies makes it possible to process several data streams in parallel without the need of concurrency control.Another observation is that a router handles active data traffic in three basic steps:•Routing and flow classification, which identifies the source and destination ofa packet. This is required to make the state information of the flow accessibleto that packet. Routing is not necessary when the ANPE is used on end systems.•Active processing, which executes the custom program code for that data packet.•Scheduling, which buffers the outgoing packet until it can be sent on the outgoing link.These three stages can be pipelined to increase performance since there is no interdependence between later stages and earlier ones. The functional design is shownin Figure 4.Fig. 4. Data flow in an Active Network Processing Element. In stage 1 a routing lookup is done and the packet is forwarded to the appropriate Active Processing Unit (APU). All packets of an active flow are handled by the same APU. The execution of the custom code is done in stage 2 by the APU. All outgoing packets go through the scheduler in stage 3. Traditional non-active traffic is not processed by an APU but goes directly to the scheduler.For the execution of custom code on the active packet an Active Processing Unit (APU) is used. This APU executes one or more Execution Environments to provide the functionality necessary to handle the active packet. In practice the APU can either be a general-purpose processor or a processor specialized for the needs of active processing. There is a by-pass around the APU stage, which is taken by non-active network traffic.Ideally, packets that belong to the same data stream are handled by the same APU. This way it can be guaranteed that packets are processed in order and the state information associated with the stream is kept consistent.Having several APUs available for active processing makes it easy to support several Execution Environments (EE). Each APU can possibly run a different EE. Packets that require a specific EE are then forwarded to the appropriate APU.ANPE DesignTo implement the above scheme we plan to use the layout shown in Figure 5.Fig. yout of the Active Network Processing Element. The Flow Classifier, the Active Processing Unit, and the Scheduler process data packets, which are stored in shared memory. The data path is shown in broad arrows, the control path in small arrows.Data FlowTo illustrate the interactions between the different components of the ANPE this section describes the processing of an active data packet.The general data flow is from left to right. Incoming data is received by the input interface, which stores the packet in the memory for data packets. This memory is a shared memory to which the input interface, the flow classifier, the APUs, and the scheduler have access. Once a packet is stored in the data memory it is not moved anymore. This way only a pointer to the packet has to be passed between the different processing stages instead of the complete packet, which greatly reduces the internal bandwidth of the ANPE.The Flow Classifier reads the header of an incoming packet, determines the stream to which the packet belongs, and does a routing lookup to decide the outgoing interface. Then it passes the packet to the appropriate APU for processing.The APU requires the custom code that has to be executed on the packet. If the packet is a capsule, it carries the code within it and can be executed easily. If the packet belongs to a programmable switch stream, it contains only a reference to the code. In this case the code will be loaded from the instruction and control memory. To load the code onto the ANPE a code server can be used as described in [5].Modifications to the data packet are done directly in the shared data memory. Adding a data cache to the APU makes repeated access to a packet more efficient.After the active processing, the scheduler is informed that the packet can be sent out. The output interface is responsible for the actual transmission of the packet. Once the packet has left the ANPE its data memory is reused for the next packet. Concurrency IssuesThe usage of shared memory raises issues of how shared access and concurrency are handled. Our design includes two shared memories: the instruction memory and the data memory.The instruction memory is shared among the APUs. Each APU accesses it to read program code. The only writing access to the instruction memory occurs when additional code for packet processing is added. This does not happen very frequently, and a simple scheme to avoid possible conflicts is to block read access for that moment. We are investigating to find out if a more sophisticated scheme is required.Conflicts on the data memory are avoided by assuring that no two components access the same memory location at the same time. Since a memory location corresponds to a data packet, only one processing component can have access to a packet at any time. This condition can be satisfied because the packet processing involves three steps: classification, processing, and scheduling. However, none of these steps occur in parallel for one packet. Additionally, the processing of a packet is done by only one APU, so there is no parallel processing on a single packet and no conflicts occur in the data memory.Performance IssuesThere are several components in the ANPE that have to be carefully designed to avoid bottlenecks that limit the throughput. In this section we give a brief reasoning of why the ANPE could handle high-speed data traffic. As an example we assume a link speed of 1.2 Gb/s (OC-12):•I/O performance: Every incoming data packet is written once into the data memory, read by the APU (and locally cached), possibly written back, and read by the output interface. Therefore every data byte crosses the memory bus at most four times. This requires 4.8 Gb/s of I/O-bandwidth, which results in a bus clock rate of 75 MHz for a 64 bit wide bus. This can be implemented with current technology.•Computational power: Assuming a small configuration with 5 parallel APUs witha clock rate of 400 MHz and 1 cycle per instruction, the ANPE can execute 2000million instructions per second for active processing. With the given data rate this gives about 16 instructions per byte of data.•Data memory size: The size of the data memory determines how long a packet can stay in the ANPE. A memory size of 1 MB can hold 6 milliseconds of link speed data traffic. During this time, a routing lookup, the active processing, and the scheduling have to take place.Active Processing UnitThe Active Processing Unit (APU) is the heart of the ANPE, as it executes the customized code that is used to handle each packet. The functionality of the APU also determines the capabilities of the ANPE. Additionally, the overall performance depends on the performance of the APU. Thus, The APU has to provide enough computational power to execute the code for every packet in the time allotted for that packet.There are two basic approaches for the implementation of an APU. In the first, the APU can be a standard workstation CPU. To provide the functionality for the EE it runs a standard OS. This approach is simple to implement, because current CPU designs and common OS software can be used.Another approach is to use a simpler, specialized processing unit that provides just enough functionality for an EE. Complex or rare instructions, like floating point operations, are not really necessary for basic active processing and can be left out or implemented in software. Since the hardware is specialized, only a small OS is required for the EE to run on. This approach can achieve better performance since the processing unit and the operating systems are tailored for active processing. However, it is also more complicated since it requires the design of a new processing unit and a corresponding OS.Design Issues to Achieve Good Overall PerformanceThere are several aspects that are important to build an Active Network Processing Element with a good overall performance:•functionality•performance•scalabilityThe following sections explain the reason behind each aspect and how good overall performance can be achieved.FunctionalityThe NodeOS[2] and the Execution Environment determine the functionality of an ANPE that is exposed to active packets. Typically, there is a tradeoff between additional features and performance. There are some basic features that are characteristics of an active network that have to be supported:•Execution of custom code that comes with the data packet either as the code directly (capsule approach) or as a reference (programmable switch approach).•Supporting the concept of streams for packets that go from the same source address / port number to the same destination address / port number (or from one source to several destinations in case of data-splitting, like multicast, or vice versa for data merging). This is important in order to be able to leave stream dependent state information for subsequent packets.•Providing basic functions that can be requested by the executed code, like access to routing information, queue lengths and load of the processing unit. These areimportant in order to make smart decisions by the code that comes with the packet.•Resource Control for memory and processor usage.•Load Balancing for systems with several processing units or systems with several ANPEs.PerformanceIn order to show good performance, an ANPE has to provide sufficient computational power for the active packets that it processes. Certainly it is possible to design custom code that overloads any active network system. The idea in defining 'sufficient' is to find among all typical and reasonable application the one that requires the most computational power. If a system can accommodate data traffic of this application at full link speed, one can safely assume that there is enough computational power to accommodate any other reasonable active applications.A System with lower computational power is still very useful for most applications, though the amount of traffic of the most complex application it can handle without getting overloaded must be specified.Another question is how a system handles the case when it runs short on computational power. Possible solutions are not to process all packets, to do admission control and deny access for flows that would overload the system, or to perform load balancing between several systems.ScalabilityOne major feature that assures the usefulness of an Active Network System is scalability. Currently, most aspects of active networking are still developing, and implemented systems consist of only a few workstations. Ideally, an ANPE has to be useful for large routers, too. Putting ANPEs on line cards makes it possible to use it on any size router without problems caused by poor scalability.The ANPE must also scale well with respect to the number of Execution Environments that might be required to handle active packets. Having multiple APUs that can handle several Execution Environments simultaneously should give flexibility with the number of supported EEs.BenchmarkCurrently it is very difficult to compare the performance of different active network systems. A major reason for this is the wide spectrum of functionality that these systems provide. Some systems put a higher emphasis on performance than others. Starting with the choice between the programmable switch approach and the capsule approach, one can implement Execution Environments with different levels of sophistication. Another hurdle for direct comparison is that most performance results are based on a single application that was used for a particular system.In order to allow an objective comparison between active network systems we propose a benchmark for active networks. This was also suggested by the DARPAITO Active Networks Working Group. With a standardized benchmark it is possible to compare the system performance of network components as well as end-to-end system performance. It also allows measuring the tradeoff between extended functionality and performance.It is very difficult to program one benchmark suite and compile it for all existing systems, since current active network systems are not standardized to one common Execution Environment. Therefore we propose a set of benchmark applications with clearly defined functionality. The implementation of these applications is left to the developers of the systems. That way it is also possible that developers can make use of special features of their system and show its performance.The proposed benchmark consists of• a set of active applications that covers a wide range of computational complexity, bandwidth and functionality,• a test environment that can show the system performance under a variety of loads and its scalability, and• a set of methods according to which the test are performed.The following sections specify these three components in detail.Benchmark ApplicationsTwo criteria are important for an application to be useful as a benchmark application. First, it has to be an Active Application and make use of the functionality provided by Active Networks. This way, one can see how a system performs when it does custom processing on a per packet basis. Applications that do not make use of processing on network nodes can be used for measuring how a system handles traditional network traffic, but this is not the main goal of the benchmark.Second, the computational complexity application should be clearly defined and ideally constant. This can be achieved by using stream applications. Active stream applications are characterized by continuous data flow, usually low dependence between packets, and no interactions with other streams. Examples for such stream applications are data encryption, media transcoding, and automatic protocol deployment. Non-stream applications are typically characterized by event-driven data transmission, like sending acks on a packet arrival, data merging and data splitting, and no constant bandwidth. Examples of these applications are network management applications, reliable multicast, sensor data fusion, and web caching. The variations in bandwidth due to event-driven transmissions make this category difficult to use for a benchmark. Also, these applications often require very complex functionality, like packet merging. This functionality might not be supported by all active network systems. Therefore, we only use reliable multicast as one application from this category and concentrate the benchmark on stream applications.The stream applications we use for the benchmark should cover the full range of possible computational complexity, from simple packet forwarding to highly complex data manipulations. In addition, it is helpful to have stream applications, which are variable in their bandwidth. Figure 6 shows a diagram illustrating the computational complexity and bandwidth of active applications.computationalcomplexityFig. 6.Bandwidth and computational complexity of typical Active Applications. This graph shows the applications used for the benchmark and their relation to each other.We selected the following Active Applications for the benchmark for the reasons given below:•Ping (transmission of a simple data packet back and forth between two nodes): It is a very simple application that can be executed on any active network system. It shows the minimum delay for a system, because the packet has to go through the complete data path, but it does not require any complex computation. The ping application can be adjusted to a variety of packet sizes and stream bandwidths.•Encryption (transmission of a data stream that is being encoded on the fly at the active network node): This application requires great computational power, because most encryption algorithms are fairly complex. The encryption application is expected to show the limits of most systems with respect to the computational power that they can provide. Encryption can be used for streams of all bandwidths.•Media Transcoding (transforming of a media stream from one format to another format, typically combined with change of compression ratio and quality): This application requires not only computational power, but also might need floating point operations (e.g. JPEG decoding / encoding). Depending on whether floating-point operations are implemented in software or hardware, there can be significant differences between systems. Media data streams are typically of higher bandwidth.•Reliable Multicast (transmission of a point to multi-point data stream in a reliable fashion): This application makes use of state information that can be stored on an active network node. Furthermore, it is an application that is event driven and requires the storage of a packet over a possibly longer period of time.•Automatic Protocol Deployment (on demand processing of data packets that belong to a previously uninstalled protocol): This application shows how well an active system can add new functionality into the data path processing. If there is a general concept of dynamically adding protocols to a system, the performance can be significantly better than treating a new protocol as a special case.•Regular non-active IP flow (transmission of common IP data packets): This application shows how a system can handle traditional IP packets. This is important to consider, because the active traffic and IP traffic will coexist in future systems.Test EnvironmentThe goal of the benchmark is to test the performance of an active network component. Therefore the basic configuration is to test the component by itself. Figure 7 shows a system outline for such a test. Additional tests can include testing the component on a line card in a router, in a real network environment, or on a testbed with several other active network nodes. For all those configurations this basic testing scheme can be used.Fig. 7. Test environment for benchmark measurements. The data packets are stored locally on the workstation that acts as data source. The data sink stores all packets that are sent out by the ANPE. These results can be compared offline to the expected results to measure throughput, packet loss, delay and correctness.The data traffic is generated by a workstation that sends packets from local storage to the active network component. The data is generated offline to assure that complex data generation programs do not delay the data transmission, and that reproducible results are being generated. This is especially important when high bandwidth data traffic has to be simulated.The output of the active network component is stored on a workstation that acts as a data sink. The results can then be compared offline to the expected results. This way the throughput, packet loss, and correctness can be determined.Testing MethodsUsing the above described test environment, it is possible to determine the following characteristics of the ANPE:•correctness of active processing•throughput and packet loss•packet delayBy varying the set of Active Applications, the stream bandwidth, the packet size, and the combination of streams, the following relations can be established. They help determine the performance of an ANPE. Possible bottlenecks can be found and eliminated.•Throughput and packet loss for different Active Applications. If throughput decreases and packet loss increases with the complexity of the Application, then the computational power of the ANPE is insufficient. If the packet loss is independent from the Active Application, then there might be a bottleneck in the general network components, like routing and flow classification, or in the switching fabric.•Throughput and packet loss for streams with different bandwidth. A system might show a different behavior if it handles few high bandwidth streams compared to many low bandwidth streams. If throughput decreases and packet loss increases with many low bandwidth streams, then the flow classification or the context switching on an APU might be a bottleneck. It is also possible that the packet loss increases with fewer high bandwidth streams. Fewer streams decrease the amount of parallelism, which the ANPE usually exploits. In an extreme case there might be only one stream at link rate, which would be handled by one APU with no parallel processing at all.•Delay and packet loss for combinations of Active Applications. If Execution Environments without resource management are used, this might show that computationally complex applications delay the processing of other streams.Although these questions are focused on the ANPE architecture, many similar observations can be made for most active networking components.Conclusions and Future WorkWe have proposed a hardware architecture for an Active Network Processing Element which will allow us to build network components for high bandwidth active data traffic. Using several parallel processing units on a single ASIC is an approach to increase the processing power of an ANPE. It deviates from the common direction of computer architecture that aims at building more and more complex single processor systems.The use of specialized hardware for active processing opens the interesting question if different aspects of active functionality should be implemented in the hardware, the Node OS, or the Execution Environment of a system.。