RapidIO高性能通信中间件设计

基于RapidIO的CORBA中间件ORB间通信方法[发明专利]

![基于RapidIO的CORBA中间件ORB间通信方法[发明专利]](https://img.taocdn.com/s3/m/f4ee090f9b89680202d8255a.png)

专利名称:基于RapidIO的CORBA中间件ORB间通信方法专利类型:发明专利

发明人:邵龙,高逸龙,陈颖,钟瑜,方科

申请号:CN202011042983.7

申请日:20200928

公开号:CN112199211A

公开日:

20210108

专利内容由知识产权出版社提供

摘要:本发明公开的一种基于RapidIO的CORBA中间件ORB间通信方法,涉及软件无线电领域,本发明通过下述技术方案予以实现:基于IIOP协议提供的TCP/IP协议栈,通过协议覆盖方式,增加以太网到RapidIO网络的适配层,实现以太网数据包运行于RapidIO网络之上,将以太网物理层替换成RapidIO层,在以太网链路层和RapidIO层之间增加一层适配层;通过TCP/IP协议栈和以太网链路层将IIOP数据层层封装,成为以太网帧,适配层将映射后的RapidIO源ID、目的ID填入RapidIO头,将RapidIO头添加到以太网帧最前面,组合成RapidIO数据格式,通过RapidIO层发送出去。

申请人:西南电子技术研究所(中国电子科技集团公司第十研究所)

地址:610036 四川省成都市金牛区茶店子东街48号

国籍:CN

代理机构:成飞(集团)公司专利中心

代理人:郭纯武

更多信息请下载全文后查看。

通用RapidIO控制器的DMA高速传输方案设计

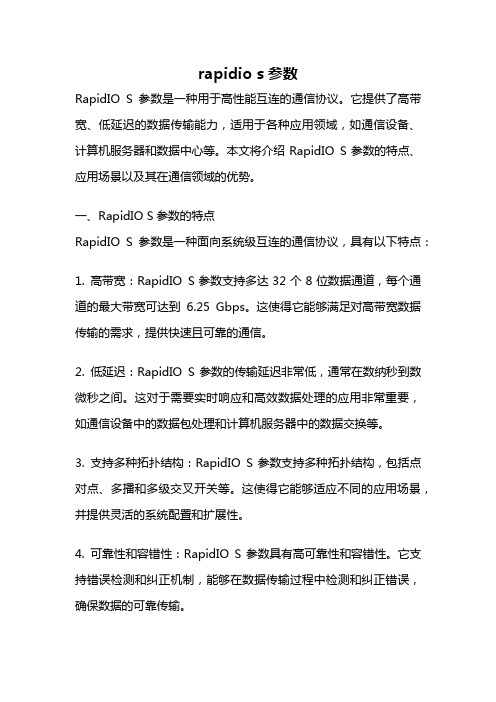

通用R a p i d I O控制器的D M A高速传输方案设计沈俊材(西南交通大学信息科学与技术学院,成都611756)摘要:本文旨在设计一款面向通信领域的高性能S o C,要求能够实现板与板的高速互连通信㊂此S o C设计基于R a p i d I O2.2协议规范,集成了G R I O,单通道速率可达6.25G b a u d,足以满足大部分通信应用的数据传输需求㊂同时考虑到大批量数据传输对系统性能的影响,本设计在R A B内部集成了D MA控制器,以减少处理器资源占用和系统性能损失㊂本文主要对G R I O和R A B两部分关键设计内容进行了详细说明㊂最后,基于裸板实现驱动程序设计,并与自带R a p i d I O软核的X i l i n x Z y n q7000Z C706开发板点对点连接测试,结果显示D MA读写带宽可达理论有效数据带宽的90%以上㊂关键词:S o C;R a p i d I O;D MA;Z y n q7000Z C706中图分类号:T N47文献标识码:AD e s i g n o f D M A H i g h-s p e e d T r a n s m i s s i o n S c h e m e B a s e d o n G e n e r a l R a p i d I O C o n t r o l l e rS h e n J u n c a i(I n f o r m a t i o n S c i e n c e a n d T e c h n o l o g y A c a d e m y,S o u t h w e s t J i a o t o n g U n i v e r s i t y,C h e n g d u611756,C h i n a)A b s t r a c t:T h e p u r p o s e o f t h i s p a p e r i s t o d e s i g n a h i g h-p e r f o r m a n c e S o C f o r c o mm u n i c a t i o n f i e l d,w h i c h r e q u i r e s h i g h-s p e e d t r a n s m i s s i o n o f l a r g e c a p a c i t y d a t a b e t w e e n b o a r d s.T h i s S o C d e s i g n i n t e g r a t e s G R I O b a s e d o n R a p i d I O2.2p r o t o c o l s p e c i f i c a t i o n.T h e s i n g l e c h a n n e l r a t e c a n r e a c h6.25G b a u d,w h i c h m e e t s t h e d a t a t r a n s m i s s i o n r e q u i r e m e n t s o f m o s t a p p l i c a t i o n s.A t t h e s a m e t i m e,c o n s i d e r i n g t h e i m-p a c t o f m a s s d a t a t r a n s m i s s i o n o n s y s t e m p e r f o r m a n c e,t h i s d e s i g n i n t e g r a t e s D MA c o n t r o l l e r i n R AB t o r e d u c e p r o c e s s o r r e s o u r c e o c c u-p a t i o n a n d s y s t e m p e r f o r m a n c e l o s s.T h i s p a p e r m a i n l y i n t r o d u c e s t h e k e y d e s i g n c o n t e n t s o f G R I O a n d R A B i n d e t a i l.F i n a l l y,t h e d r i v e r i s d e s i g n e d b a s e d o n t h e b a r e b o a r d.T h r o u g h t h e p o i n t-t o-p o i n t t e s t w i t h R a p i d I O s o f t I P c o r e o n t h e X i l i n x Z y n q7000Z C706d e v e l o p-m e n t b o a r d,i t s h o w s t h a t D MA r e a d-w r i t e b a n d w i d t h c a n r e a c h o v e r90%o f t h e t h e o r e t i c a l e f f e c t i v e d a t a b a n d w i d t h.K e y w o r d s:S o C;R a p i d I O;D MA;Z y n q7000Z C706引言近年来,嵌入式系统不断发展,对互连设备间的数据传输能力要求越来越高,计算机I/O技术作为高性能计算技术发展中的重要技术,决定了系统设备间的通信性能㊂传统的并行总线很难满足高带宽㊁高灵活性以及高可靠性的需求,无法达到未来各种更高性能的嵌入式系统所需的I/O性能[1]㊂为了解决这个问题,业内相继提出了很多新兴的串行互联技术[4]㊂目前比较流行的有P C I e㊁以太网和R a p i d I O㊂其中R a p i d I O主要定位于超高性能系统中芯片之间和模块之间的互连,其软件开销更低,传输效率更高,可显著节省功率和成本,此外,还提供了相当丰富的扩展功能,如误码管理㊁流量控制和灵活的拓扑路由[5]㊂正是R a p i d I O的高性能㊁高可靠性和结构灵活等特点,使其具有广泛的应用领域(如图像处理㊁视频会议㊁4G基站,甚至当前热门的5G技术等)㊂同时值得注意的是,在上述应用中,芯片要一直进行大量的数据交换,这会占用大量C P U资源,从而导致芯片性能降低[6]㊂D MA控制器可以替代C P U接管对总线的控制,完成传输后归还总线控制权,有助于减少处理器资源占用,适用于进行大批量数据传输并且对速度要求比较高的应用场景,以提升系统性能[7]㊂综合上述分析,本次设计S o C内部集成了R a p i d I O控制器,I P来源为M o b i v e i l的G R I O,支持R a p i d I O2.2㊂同时,采用了基于描述符的D MA传输方式,以进一步提升系统性能㊂1设计方案在处理器方面,系统采用高速R S I C内核A R M9㊂针对A R M核,总线设计方面采用经典的AM B A(A d v a n c e d M i c r o c o n t r o l l e r B u s A r c h i t e c t u r e,高级处理器总线架构)架构[8]㊂按照低速A P B㊁中速A H B㊁高速A X I的原则,将高速控制器R a pi d I O 挂载在A X I 总线上㊂R a p i d I O 模块主要分三部分:R A B [9]㊁G R I O [10]和S e r -d e s ,如图1所示㊂其中R A B 主要实现A X I 总线与G R I O 接口之间的数据转发;G R I O 主要实现R a pi d I O 协议的逻辑层[11]㊁传输层[12]以及物理层[13]中的P C S 子层;S e r d e s主要实现信号的串并转换和差分收发㊂图1 S R I O 结构图1.1 G R I O 设计R a pi d I O 采用三层分级体系结构㊂逻辑层定义全部R a pi d I O 事务包的格式,为端点器件发起和完成事务提供必要的信息㊂传输层定义R a p i d I O 地址空间和在端点器件间传输包所需的路由格式㊂物理层定义电气特性㊁链路控制和纠错重传等[14-15]㊂1.1.1 G R I O 结构M o b i v e i l 的G R I O 是一个灵活可配置的I P ,可作为端点㊁交换机和桥实现,结构如图2所示㊂图2 G R I O 结构图G R I O 基于R a pi d I O 2.2协议规范实现,分为两个实现层:逻辑层和物理层㊂逻辑层实现R a pi d I O 协议的逻辑层和传输层;物理层实现R a pi d I O 协议的物理协议层和P C S (P h y s i c a l C o d i n g S u b l a ye r ,物理编码子层)子层㊂I P 核在物理层支持串行和并行两种接口形式,本设计采用应用更加广泛的L P S e r i a l 串行接口,单通道数据速率可达6.25G b a u d㊂按照数据传输路径,G R I O 分为I n b o u n d 方向和O u t -b o u n d 方向㊂在O u t b o u n d 方向,U L (U s e r L o gi c ,用户逻辑)通过S U L I (S i m p l i f i e d U s e r L o gi c I n t e r f a c e ,简化的用户逻辑接口)提供数据包的标头信息和数据内容到G R I O ,再层层下发至外部的S e r d e s 发送器,最后到达R a p i d I O 链路㊂在I n b o u n d 方向,外部的S e r d e s 从R a p i d I O 链路上恢复出接收到的数据,再向上转发至逻辑层,逻辑层进行错误检测并将正确的数据包通过U L I 最终递交给U L ㊂1.1.2 I /O 事务与包R a pi d I O 操作是基于请求和响应事务的㊂包是系统中端点器件间的基本通信单元㊂R a p i d I O 事务被封装在包中,包含了确保事务可靠传输到目标端点所需的各个字段㊂表1列举了G R I O 支持的I /O 事务,其中f t y pe 表示事务包格式类型,t t y pe 表示事务类型㊂表1 G R I O 支持的I /O 事务I /O 事务f t y pe t t y p e 状 态说 明N R E A DA T OM I C i n cA T OM I C d e cA T OM I C s e t A T OM I C c l rNWR I T ENWR I T E _R S WR I T E0010010101100100110011011110111101000101N /A N /A 读带响应读后增带响应读后减带响应读后置一带响应读后清零无响应写带响应写流写F L OW C O N T R O L0111N /A N /A 流控MA I N T r e a dMA I N T w r i t e MA I N T r e a d r e s po n s e MA I N T w r i t e r e s po n s e MA I N T p o r t w r i t e100000000001001000110100N /A 0000011100000111N /A 维护读维护写维护读完成响应错误响应维护写完成响应错误响应维护端口写S t r e a m i n g 1001N /AN /A 数据流D o o r b e l l 1010M e s s a ge 10110000N /A 门铃消息数据消息R E S P O N S Ew i t h o u t d a t a R E S P O N S E w i t h d a t a1101000010000000I /O 完成响应0111I /O 错误响应0000带数据I /O完成响应对于用户来说,只需理解各类格式包的组成和时序,而无需关注协议的过多细节㊂有关各类事务包字段的详细描述可参见G R I O D a t a s h e e t㊂1.2 R A B 设计R A B 不属于R a p i d I O 协议规范的内容,它一端连接到R a pi d I O ,另一端连接到AM B A 总线系统,用于实现A X I 协议和R a pi d I O 协议间的数据转换㊂1.2.1 R A B 结构A X I R I O 桥结构图如图3所示㊂除可选功能模块外,R A B 内部主要包括:①A X I M a s t e r :A X I 写和读M a s -t e r ㊂②A X I S l a v e :A X I 写和读S l a v e ㊂③A P B S l a v e :A P B写和读S l a v e ,用于寄存器访问㊂④G R I O t o A X I C o n v e r -t o r :从G R I O 转换数据包到A X I ㊂⑤G R I O t o A X I C o n v e -r t o r :从A X I 转换数据包到G R I O㊂图3 A X I R I O 桥结构图1.2.2 配置访问配置空间访问图如图4所示,R A B 提供了16M B 的配置空间,包括标准R a pi d I O 配置空间寄存器㊁G R I O 特有C S R (C o mm a n d a n d S t a t u s R e g i s t e r ,命令状态寄存器)寄存器和R A B 特有C S R 寄存器,可供R I O 主机和AM -B A 主机访问㊂R a pi d I O 主机通过维护请求或常规的N R E A D 和NWR I T E 请求访问整个16M B 配置空间㊂AM B A 主机通过专用的A P B S l a v e 接口访问C S R ㊂I P 核的A P B 可访问地址空间仅4K B 或8K B ,为了访问到完整的16M B 空间,采用了页访问机制㊂1.2.3 地址映射R A B 作为桥,需要在AM B A 域和R I O域的地址间进图4 配置空间访问图行映射[16]㊂本设计A X I 地址位宽为38位,R a pi d I O 寻址支持34位和50位,默认为34位㊂A X I 到R I O 的地址映射如图5所示㊂图5 A X I 到R I O 的地址映射图示当R A B 接收到一个A X I 总线上的读写请求时,如果请求的地址落在A X I 地址映射窗口内,则进行A X I P I O地址映射,否则该请求被丢弃㊂对于A X I P I O 事务,A X I基址和R I O 基址必须1K B 边界对齐㊂R I O 到A X I 的地址映射如图6所示㊂首先,根据寄存器B y pa s s 使能位的值决定4位索引是来源于8位源器件I D ,还是34位或50位的R I O 地址㊂确定索引后,选择对应的查找表,然后通过查找表得到R I O P I O 窗口基址㊁窗口大小以及A X I 地址的高位地址㊂高位地址结合R I O 地址的低位地址共同构成最终的A X I 地址㊂1.3 D M A 设计P I O 模式为最基本的传输模式,进行大批量数据传输时会占用大量资源,影响系统性能㊂本设计在R A B 内部图6 R I O 到A X I 的地址映射图示集成了D MA 控制器,以代替C P U 接管总线控制权,实现AM B A 总线系统和R I O 系统间的大批量数据传输,减少系统性能损失[17]㊂1.3.1 读/写D M A 引擎本次D MA 设计采用多引擎工作方式,共有8个WD -MA (W r i t e D MA ,写D MA )引擎和8个R D MA (R e a dD MA ,读D MA )引擎㊂WD MA 引擎用于从AM B A 系统发送数据到R I O 系统㊂R D MA 引擎用于从R I O 系统发送数据到AM B A 系统㊂引擎核心组成部分包括发送/接收引擎㊁接口访问控制模块㊁D MA 传输控制模块㊁描述符访问控制模块㊁控制状态寄存器㊁多D MA 通道控制模块㊁D MA 通道缓存等㊂与普通D MA 控制器不同的是,本设计引入了描述符访问控制模块,用于实现D MA 描述符信息与A X I 内存描述符信息的交互㊂考虑到本地内存足够大,所以通常把大量描述符信息存放在本地A X I M e m o r y,然后引擎将配置好的描述符信息取出,更新到描述符寄存器,待传输完成后,更新描述符状态㊂1.3.2 描述符描述符共128位,包含了D MA 传输所需的全部信息,结构如表2所列㊂描述符有两种组织方式:链式和块式㊂块式描述符是一种特殊的链式描述符㊂如图7和图8所示,每个描述符都直接或间接地给出了下一个描述符的地址,因此D MA控制器无需频繁地向C P U 申请总线控制权,直至完成所图7链式描述符结构图8 块式描述符结构表2 描述符结构信 号B i t 说 明v a l i d 0指示描述符是否有效n e x t _p t r 1指示下一描述符地址是由n e x t _d e s c _w o r d_a d d r 指定或紧跟在当前描述符之后n e x t _e x t _a d d r 14:2在32b i t A X I 地址模式下作为保留域;在38b i t A X I 地址模式下作为高三位t r a n s _l e n 22:5传输长度,单位为4Ba x i _e x t _a d d r 123在32b i t A X I 地址模式下作为保留域;在38b i t A X I 地址模式下作为最高位d o n e24指示传输是否完成a x i _e r r o r 25指示A X I 错误r i o _e r r o r26指示R I O 错误d e s c _f e t c h _e r r o r 27指示获取描述符错误d e s c _u pd a te _e r r o r 28指示更新描述符错误a x i _e x t _a d d r 031:29在32b i t A X I 地址模式下作为保留域;在38b i t A X I 地址模式下作为b i t [36:34]s r c _w o r d _a d d r 63:32源地址d e s t _w o r d _a d d r 95:64目的地址n e x t _d e s c_w o r d _a d d r125:96下一描述符的地址n e x t _e x t _a d d r 0127:126在32b i t A X I 地址模式下作为保留域;在38b i t A X I 地址模式下作为b i t [34:33]有传输或出现错误后才交还控制权给C P U ,减少了建立D MA 申请的时间,适用于大批量数据搬移的场景㊂2 驱动编写与测试完成系统集成之后,接下来工作重点是仿真验证,以确保设计电路功能的正确性㊂在系统验证平台动态仿真,受软件资源和系统内存限制,仿真速度很慢,所以本次驱动程序设计基于裸机环境开发,即无操作系统的支持㊂虽然增加了驱动开发难度,但是减少了导入操作系统的漫长时间,有效提升了仿真效率㊂基于描述符的D MA 传输模式的软件配置流程如图9所示㊂为了尽可能真实地模拟出实际芯片的硬件场景,本次验证还引入了F P G A 进行辅助验证㊂通过资源评估,选用S t r a t i x V F P G A 作为验证版,以模拟真实的电路,并与自带R a p i d I O 软核的X i l i n x Z y n q7000Z C 706开发板点对点连接测试㊂测试结果显示,在4通道6.25G b a u d 模式下,D MA 读操作带宽可达2163.3536M b ps ,D MA 写操作带宽可达2017.4464M b ps ㊂考虑到高速串行通信8B /10B 编码以及协议本身的开销(以传输最大256字节数据为例,打包效率通常为92%~94%),在4通道6.25G b a u d 模式下,理论有效数据图9 D M A 传输模式软件配置流程图带宽为6.25G b p s ˑ4ˑ(8/10)ˑ0.92,即2355.2M b ps ㊂在不考虑链路维护和系统开销的情况下,D MA 读写带宽最高达到了理论有效数据带宽的91%左右㊂结 语本文提出了一种基于R a pi d I O 的高速传输方案,利用当前流行的串行互联技术,并结合基于描述符的D MA 传输模式解决高性能嵌入式系统设备互联通信问题,具有一定的实用价值,为此类问题提供一个解决方案示例㊂参考文献[1]郦伟,肖鹏.基于R a pi d I O 协议的网络路径分配策略[J ].计算机工程与设计,2017,38(11):29772982.[2]李少龙,高俊,娄景艺,等.基于S R I O 总线的数字信号处理系统的实现通信技术[J ].通信技术,2012,45(5):101103.[3]张康.通信S o c R a pi d I O 验证平台设计[D ].西安:西安电子科技大学,2018.[4]李胤.高速串行总线应用研究[D ].北京:北京理工大学,2014.[5]祝树生,解春雷,仇公望,等.以太网㊁P C I e 和R a pi d I O 高速总线比较分析[J ].电子测试,2016(11):100102.[6]谢俊.实时图像处理系统中的D MA 控制器的设计与实现[D ].上海:上海交通大学,2006.[7]王之光,高清运.基于F P G A 的P C I e 总线接口的D MA 控制器的设计[J ].电子技术应用,2018,44(1):912.[8]AM B A A X I P r o t o c o l V 1.0S pe c if i c a t i o n ,2004.[9]R a p i d I O t o A X I B r i d ge C o n t r o l l e r D a t a s h e e t ,2014.[10]G R I O (2.2)D a t a s h e e t ,2014.[11]R a p i d I O T r a d e A s s o c i a t i o n .R a p i d I O I n t e r c o n n e c t S pe c if i c a t i o n R e v .2.1.P a r t 1:I n p u t /O u t p u t L og i c a l S pe c if i c a t i o n ,2009.[12]R a p i d I O I n t e r c o n n e c t S p e c i f i c a t i o n :C o mm o n T r a n s po r t S p e c i f i c a t i o n R e v 2.2,2011.[13]R a p i d I O I n t e r c o n n e c t S p e c i f i c a t i o n :P h y s i c a l L a y e r S pe c if i -c a t i o n R e v 2.2,2011.[14]F u l l e r S .R a pi d I O 嵌入式系统互连[M ].王勇,等译.北京:电子工业出版社,2006.[15]孙吉元.R a pi d I O 2.1I P 核设计[D ].南京:东南大学,2016.[16]Y o u n g K y o o n S u h ,B o n g k i M o o n ,A l o n E f r a t ,e t a l .M e m o r ye f f i c i e n t a n d s c a l a b l e a d d r e s s m a p p i n g f o r f l a s h s t o r a ge d e -v i c e s [J ].J o u r n a l of s ys t e m s a r c h i t e c t u r e ,2014,60(4).[17]张娟娟.R a pi d I O 高速串行总线的研究与实现[D ].长沙:国防科学技术大学,2011.沈俊材(硕士研究生),主要研究方向为嵌入式系统㊂(责任编辑:薛士然 收稿日期:2020-03-03)艾睿电子㊁松下工业联合S T 推出I o T 智能设备模组艾睿电子㊁松下工业和意法半导体联合推出了面向智能工厂㊁智能家居和智能生活的低功耗无线多传感器边缘智能解决方案㊂该物联网解决方案模组整合艾睿电子的工程设计和全球分销能力与松下工业基于意法半导体B l u e T i l e (S T E V A LB C N 002V 1B )多传感器开发套件开发的物联网模组,使客户能够轻松地测试产品设计,将新的物联网产品更快地推向市场㊂该物联网解决方案模组板载意法半导体最新的低功耗蓝牙系统芯片(S o C )B l u e N R G B L E 5.0以及惯性㊁环境和音频等多个传感器,使设备厂商能够推出各种经济实惠㊁面积紧凑㊁物超所值的物联网产品,满足智能工厂㊁智能家居和智能生活市场的需求㊂全方位的服务和功能验证流程有助于降低物料清单成本㊂在一个有蓝牙通信功能的高能效的低功耗设计中,模组整合加速度计和陀螺仪,以及飞行时间测距传感器㊁压力传感器和湿度传感器,并经过标准化组织测试认证,使O E M 客户能够极大地缩短产品上市时间,降低设计成本和复杂性㊂这些模组是松下工业基于功能和设计出色的S T B l u e T i l e 传感器节点开发套件开发的,是加快创建适用于所有物联网的各种边缘节点传感器的理想选择,目前这些模块由艾睿电子代理销售, 意法半导体E M E A 市场与应用副总裁P h i l i p Lo l i e s 表示㊂松下工业欧洲公司物联网团队负责人S a r a G h a e m i 博士表示: 从S T B l u e T i l e 获得灵感,松下物联网解决方案模组帮助客户在这个快节奏时代缩短产品研发周期㊂松下工业能够提供优质的客户服务,贯穿产品生命周期从设计㊁开发㊁验证到售后的各个阶段㊂这些模组帮助客户减少开发工作量和产品总成本,同时确保产品质量达到最高水准,取得所需的产品认证㊂这一新的解决方案将满足智能工厂㊁智能家居和智能生活市场客户的需求㊂。

RapidIO高性能通信中间件设计

RapidIO高性能通信中间件设计

潘灵

【期刊名称】《电子技术应用》

【年(卷),期】2014(040)012

【摘要】针对RapidIO总线互联系统中网络节点间高效端对端通信功能的缺失,实现了基于消息机制的RapidIO通信中间件,以虚通道的方式为应用提供数据传输功能.虚通道采用HOST节点集中控制的管理方式,易于实现系统功能的迁移与重构.实物环境中的带宽、时延测试表明,RapidIO通信中间件具有很高的传输效率.

【总页数】3页(P107-109)

【作者】潘灵

【作者单位】中国电子科技集团公司第十研究所,四川成都610036

【正文语种】中文

【中图分类】TN911

【相关文献】

1.一种应用于高性能DSP的RapidIO控制器IP [J], 胡孔阳;韩琼磊

2.基于RapidIO的高性能通信接口的设计与实现 [J], 梁基;金亨科;徐炜民;郑衍衡;沈文枫

3.全球首家RapidIO互操作性实验室RIOLAB开始为采用RapidIO技术进行设计的供应商和原始设备制造商提供互操作性测试服务 [J],

4.RapidIO总线的嵌入式异构平台通信中间件 [J], 高逸龙

5.新一代高性能RapidIO互连技术及应用 [J], 雷蕾

因版权原因,仅展示原文概要,查看原文内容请购买。

基于RapidIO协议的高速数据互联模块设计

基于RapidIO协议的高速数据互联模块设计作者:上官珠范国忠高文昀来源:《现代电子技术》2014年第15期摘要: RapidIO技术是目前世界上第一个、也是惟一的嵌入式系统互连国际标准,可以简单、高效、可靠地实现从单板到全系统的互连,在高性能数字信号处理系统中得到广泛的应用。

介绍了基于RapidIO协议的高速数据互联模块的设计方案、高速数据传输设计中的难点、以及模块的信号完整性分析。

该模块现已在雷达信号处理系统中得到应用验证,各项性能指标均能够满足应用需求,实现了可靠稳定的高速数据传输。

关键词: RapidIO; EDK; RocketIO; LWIP;信号完整性分析中图分类号: TN911.7⁃34 文献标识码: A 文章编号: 1004⁃373X(2014)15⁃0028⁃04 High speed data interconnection module base on RapidIO protocolSHANGGUAN Zhu, FAN Guo⁃zhong, GAO Wen⁃yun(Nanjing Research Institute of Electronics Technology, Nanjing 210039, China)Abstract:RapidIO technology is the world′s first and only one international standard of embedded system interconnection, which can simply and efficiently implement the interconnection from the single board to entire system, and is widely used in digital signal processing system. The design scheme of high⁃speed data interconnection module based on RapidIO protocal, the difficulties in the design of high⁃speed data transmission, and signal integrity analysis of module are introduced in this paper. This module has been used and verified in the radar signal processing system. The results indicate that each performance index of the module can meet the application requirements, and the module can achieve reliable and stable high⁃speed data transmission.Keywords: RapidIO; EDK; RocketIO; LWIP; signal integrality analysis0 引言随着军事电子技术的迅猛发展,现代雷达技术日新月异,电子设备之间的数据传输率越来越高,尤其在现代雷达系统中,需要高速的数据传输、采集和大吞吐量的数据传输,来实现数据高速实时处理,传统用于数据传输所采用的低速并行总线已经无法满足系统的要求。

rapidio s参数

rapidio s参数RapidIO S参数是一种用于高性能互连的通信协议。

它提供了高带宽、低延迟的数据传输能力,适用于各种应用领域,如通信设备、计算机服务器和数据中心等。

本文将介绍RapidIO S参数的特点、应用场景以及其在通信领域的优势。

一、RapidIO S参数的特点RapidIO S参数是一种面向系统级互连的通信协议,具有以下特点:1. 高带宽:RapidIO S参数支持多达32个8位数据通道,每个通道的最大带宽可达到6.25 Gbps。

这使得它能够满足对高带宽数据传输的需求,提供快速且可靠的通信。

2. 低延迟:RapidIO S参数的传输延迟非常低,通常在数纳秒到数微秒之间。

这对于需要实时响应和高效数据处理的应用非常重要,如通信设备中的数据包处理和计算机服务器中的数据交换等。

3. 支持多种拓扑结构:RapidIO S参数支持多种拓扑结构,包括点对点、多播和多级交叉开关等。

这使得它能够适应不同的应用场景,并提供灵活的系统配置和扩展性。

4. 可靠性和容错性:RapidIO S参数具有高可靠性和容错性。

它支持错误检测和纠正机制,能够在数据传输过程中检测和纠正错误,确保数据的可靠传输。

二、RapidIO S参数的应用场景RapidIO S参数广泛应用于各种领域,包括通信设备、计算机服务器和数据中心等。

1. 通信设备:RapidIO S参数在通信设备中用于数据包处理、交换机和路由器等关键功能。

它能够提供高带宽、低延迟的数据传输,满足对实时性和可靠性的要求。

2. 计算机服务器:RapidIO S参数在计算机服务器中用于高速数据交换和互连。

它能够提供快速的数据传输,支持大规模并行计算和分布式存储系统,提高系统性能和可扩展性。

3. 数据中心:RapidIO S参数在大规模数据中心中用于服务器之间的高速互连。

它能够提供高带宽、低延迟的数据传输,支持数据中心内部的快速数据交换和分布式计算。

三、RapidIO S参数在通信领域的优势RapidIO S参数在通信领域具有以下优势:1. 高性能:RapidIO S参数提供高带宽、低延迟的数据传输能力,能够满足对高性能通信的需求。

利用RapidIO技术搭建的可重构信号处理平台

利用RapidIO技术搭建的可重构信号处理平台在雷达、声纳、电子对抗等军用电子设备中,数字信号处理机作为实现信号处理算法的平台,起着至关重要的作用。

在传统的信号处理平台中,军事领域多选用ADI 公司的TigerShark 系列的DSP 芯片作为信号处理单元,在PCB 的板内和板间采用高速的LINK 口进行互联。

LINK 口是一种源同步接口,可以达到很高的传输速度。

但是,由于LINK 口是基于电路交换的接口,连接的双方独占一条通路,LINK 口一旦在硬件上连接起来,系统中的DSP 网络拓扑就固定不变了。

由于信号处理算法的多样性,系统中数据流的方向也很不确定,固定的DSP 拓扑网络只能针对一定的算法达到最优,当数据流方向改变较大时,同样的信号处理平台的传输效率就会大大降低。

这时,如果能够重新调整DSP 网络的拓扑结构,会大大提高平台的性能。

为了实现系统可重构的特性,需要利用专门的FPGA 芯片,将基于电路交换的LINK 口转换成基于(带有路由信息的)包交换的其他格式的接口进行传输。

现在比较流行的基于包交换的接口有串行RapidIO 接口、PCI Express 接口和千兆以太网接口等。

串行RapidIO、PCI Express 和千兆以太网技术都可以提供高速、可靠的点对点互联。

串行RapidIO 技术是专门为嵌入式系统互联而设计的,只要有足够多的交换机,就可以实现任意结构的拓扑。

PCI Express 技术是着眼于最大的兼容PCI 总线技术而设计,为了能够兼容传统的PCI 总线技术,PCI Express 的拓扑结构只能是树形结构。

这种结构在PC 机和服务器内非常适用,如果合适的话,也能用在嵌入式系统内。

但在PCI Express 的结构中除了要有交换机,还需要有一个根联合体来做统一的管理,这增加了硬件的开销。

千兆以太网技术是百兆以太网技术的升级,最初用于局域网内和广域网内的互联,是非常可靠的互联选择。

串行 RapidIO 高中性能嵌入式互连技术

串行 RapidIO: 高性能嵌入式互连技术摘要串行RapidIO针对高性能嵌入式系统芯片间和板间互连而设计,它将是未来十几年中嵌入式系统互连的最佳选择。

本文比较RapidIO和传统互连技术的优点;介绍RapidIO协议架构,包格式,互连拓扑结构以及串行RapidIO物理层规范。

介绍串行RapidIO在无线基础设施方面的应用。

RapidIO 与传统嵌入互连方式的比较随着高性能嵌入式系统的不断发展,芯片间及板间互连对带宽、成本、灵活性及可靠性的要求越来越高,传统的互连方式,如处理器总线、PCI总线和以太网,都难以满足新的需求。

处理器总线主要用作外部存储器接口,如德州仪器(TI) C6000系列DSP的外部存储器接口,可支持外接同步SDRAM、SBSRAM及FIFO,也可支持异步SRAM、FLASH等。

外部存储器接口也可用作与板内FPGA或ASIC芯片互连,这种情况下,FPGA或ASIC模拟一个DSP支持的存储器接口,DSP则把FPGA或ASIC当作存储器来访问。

这类同步接口带宽可达10Gbps,如德州仪器TMS320C6455 DSP的DDR2接口最大带宽为17.066Gbps,SBSRAM接口最大带宽为8.533Gbps。

然而,这种接口也存在一些局限性:1. 接口管脚多,硬件设计困难。

常见的DDR2接口有70~80个管脚;2. 只能用于板内互连,无法用于板间互连;3. 不是点对点的对等互连,DSP始终是主设备,其它器件只能做从设备。

PCI是广泛用于计算机内器件互连的技术。

传统PCI技术也采样类似于上述存储器接口的并行总线方式,如TMS320C6455 DSP的PCI接口,有32bits数据总线,最高时钟速度为66MHz,共有42个管脚。

最新的串行PCI Express技术采用与串行RapidIO(SRIO, Serial RapidIO)类似的物理层传输技术,使得带宽达到10Gbps左右。

但由于其主要的应用仍是计算机,而且为了兼容传统PCI技术,使得它在嵌入式设备方面的应用具有一定的局限性,如不支持点对点对等通信等。

rapidIO介绍

rapidIO介绍RapidIO是一种高性能、高可靠性、低延迟的总线架构,旨在加速多处理器系统中的数据传输。

它是专门为通信和数据处理应用而设计的,被广泛应用于网络路由器、数据中心、通信基础设施、工业自动化和军事领域等。

RapidIO的设计目标是提供高效的数据交换能力,以满足现代通信、计算和存储系统对高带宽、低延迟和可扩展性的需求。

RapidIO总线架构采用点对点的连接方式,具有多阶层的拓扑结构,可以支持高达128个节点的系统,并且允许多个节点同时进行数据传输。

RapidIO的最大特点之一是其低延迟和高带宽。

因为它是基于硬件的实现,数据可以在多个节点之间直接传输,而不需要通过软件来处理,从而大大降低了传输延迟。

此外,RapidIO的架构还支持传送一次提取多次复制(single copy/multiple copy),可以有效减少数据的复制和重复传输,提高数据传输的效率。

RapidIO还具有高可靠性和可靠性的优点。

它采用了流控制机制和数据完整性校验,可以确保数据传输的正确性和完整性。

此外,RapidIO还支持热插拔和热冗余的功能,可以在系统运行时动态添加或替换节点,而不会影响整个系统的正常运行。

RapidIO还具有良好的扩展性和灵活性。

它的拓扑结构可以根据应用的需求进行灵活的配置和扩展。

RapidIO还定义了一套标准接口和协议,可以与其他标准总线和协议兼容,使得它可以轻松地与其他硬件和软件系统集成。

RapidIO的应用非常广泛。

在通信领域,RapidIO被广泛应用于网络路由器、交换机、无线基站和光传输设备等,用于实现高速数据传输和实时数据处理。

在数据中心和云计算环境中,RapidIO可以用于构建高性能计算集群和分布式存储系统,提供快速和可扩展的数据传输能力。

在工业自动化和军事领域,RapidIO可以用于构建大规模的实时控制系统和传感器网络,用于高速数据采集和分析。

总的来说,RapidIO是一种为高性能、高可靠性和低延迟应用而设计的总线架构。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

RapidIO高性能通信中间件设计

摘要:针对RapidIO总线互联系统中网络节点间高效端对端通信功能的缺失,实现了基于消息机制的RapidIO通信中间件,以虚通道的方式为应用提供数据传输功能。

虚通道采用HOST 节点集中控制的管理方式,易于实现系统功能的迁移与重构。

实物环境中的带宽、时延测试表明,RapidIO通信中间件具有很高的传输效率。

关键词: RapidIO;通信中间件;虚通道;集中控制

0 引言

近年来,RapidIO总线作为嵌入式领域的总线互联标准,以其高性能、低延迟、低引脚数和低功耗等特点得到了广泛关注,基于RapidIO总线互联的嵌入式系统硬件技术日益成熟[1-3]。

在系统应用方面,目前有两种数据传输方式:(1)直接使用RapidIO逻辑层功能;(2)将RapidIO逻辑层功能与通用协议适配。

前者由于缺乏节点间端到端互联功能,很难应对多任务并发的系统应用;对于第二种方式,Linux平台上采用了设备抽象的方式,将消息与门铃功能接入TCP/IP协议[4-5],vxWorks平台通过内存映射机制提供了对TIPC协议的支持[6-7]。

采用第二种方式虽然能够支持复杂的应用,但冗余的协议处理使其很难应付对带宽、时延都要求特别高的场合。

本文针对RapidIO逻辑层消息机制的传输特点,设计实现了采用HOST节点集中控制的RapidIO通信中间件,解决了PE节点间高效的端对端数据传输问题。

1 RapidIO通信中间件

RapidIO通信中间件采用了分层的设计思想,RIO消息驱动层负责对RapidIO总线接口进行管理,包括收发邮箱的初始化、硬件收发队列的管理、中断的响应等操作。

逻辑链路层实现对节点之间点对点链路的维护,将邮箱功能映射为数据包发送与数据包接收队列。

虚通道层将逻辑链路层单个收发队列复用为多个虚通道,提供给逻辑事务层使用。

控制代理使用控制虚通道进行HOST节点与PE节点之间控制信息的交互,应用程序使用应用虚通道传输数据。

RapidIO通信中间件采用工作进程进行各类任务的处理,逻辑链路层与虚通道层各部署了一个工作队列,图1给出了RapidIO通信中间件层次模型。

1.1 虚通道状态

RapidIO通信中间件为每个虚通道维护了一个虚通道状态,在虚通道对象创建时处于UC 状态,并主动向对端发送请求包;然后根据收到请求包、应答包的先后顺序,分别经过URP、UBB向正常状态NM跃迁,虚通道上的超时定时器避免握手时发生死锁。

处于NM状态的虚通道可正常收发数据,当发送处于拥塞状态时,会切换到拥塞状态CGST,待拥塞恢复后方能继续发送数据。

挂起状态HG使得HOST节点能够根据当前系统需求,暂停、恢复PE节点上的虚通道数据传输功能,删除态DEL使得虚通道对象能够在资源释放完毕后正常销毁。

图2给出了虚通道状态的变迁。

1.2 虚通道的建立

RapidIO通信中间件中应用虚通道的建立采用了对等握手的机制。

PE节点中虚通道控制代理负责接收HOST指令,发起对等握手过程,并将结果反馈给HOST节点。

控制虚通道的建立采用HOST节点主动发起、PE节点被动建立的方式。

图3给出了控制虚通道与应用虚通道的建立过程。

1.3 虚通道句柄映射

RapidIO通信中间件采用通信句柄对虚通道进行标识,应用程序通过预分配的虚通道名称获取通信句柄进行数据传输。

获取通信句柄时,若对应的虚通道已经建立,则将分配的句

柄结构与虚通道对象进行双向关联;若虚通道未建立,则将虚通道名称保存在分配的句柄结构中,待对应的虚通道建立后,扫描通道句柄映射表,实现通信句柄的延迟绑定。

图4给出了通道句柄与通道对象映射关系。

1.4 数据包传输

RapidIO通信中间件采用了M_BLK与CLUSTER两类缓存对象进行内部数据包的传递,CLUSTER作为存放数据包内容的载体,M_BLK负责对CLUSTER中的包头信息进行描述,并通过单向指针与CLUSTER一对一关联。

每个M_BLK有相互索引的双向指针,可方便地挂接到逻辑链路层与虚通道层的传输队列上。

为提高搜索效率,缓存池中的M_BLK采用固定64 B长度,而CLUSTER则在长度2N(5≤N≤12)中取值,每种CLUSTER所占比例可根据系统应用进行配置。

数据包在各层之间传递时,只需修改M_BLK中的双向指针,避免了数据的拷贝。

同时,RapidIO 通信中间件启用了硬件消息队列模式,CPU提交数据包到队列后,不必等待消息发送完毕,从而达到CPU与硬件接口并行工作的目的。

1.5 流控机制

RapidIO通信中间件基于消息目的端流控,采用ACK包交互实现了源端流控功能。

ACK 包向对端通报本地端接收队列的信息,包括接收队列总共已接收包个数(TotalRcvPacks)、还可以接收包个数(AllowRcvPacks)。

定义发送端允许发送包个数AllowSendPacks,发送端总共已发送包个数TotalSendPacks,则有AllowSendPacks=Allow-RcvPacks-(TotalSendPacks-TotalRcvPacks)。

当AllowSend-Packs=0时发送端将进入拥塞状态直至收到对端ACK包使AllowSendPacks>0。

接收端在接收队列中包个数为队列长度的1/2时,将向发送端发送ACK包,图5给出了AllowSendPacks在传输过程中的变化过程。

2 RapidIO通信中间件性能评估

基于RapidIO通信中间件的设计思想,实现了RapidIO通信中间件的vxWorks版本,支持vxWorks5.5.1。

测试环境为3个MPC8548E节点通过2个TSI578交换节点互联的系统,RapidIO物理层工作在1X模式,频率为1.25 GHz,其中一个MPC8548E作为HOST节点,其余两个MPC8548E作为PE节点。

HOST节点配置两个PE节点之间的物理路径[8]与应用虚通道,两个PE节点在虚通道上传输数据进行性能测试。

测试数据长度在2n基础上减去了8 B的数据帧头,使消息能够以最高效的方式传输。

在带宽指标测试中,RapidIO物理层1.25 GHz的工作频率8 B/10 B转换后,提供给RapidIO 逻辑层的极限带宽为125 MB/s,RapidIO消息层损失了大约10%的传输带宽,经过RapidIO 通信中间件的虚通道层后,测试的极限带宽达102 MB/s。

在时延指标测试中,不超过64 B 的短数据传输时延都在25 s以下。

图 6与图 7分别给出了传输不同长度数据时的带宽与时延。

3 结束语

RapidIO总线技术作为新一代芯片级互联总线的代表,在嵌入式领域具有广泛的应用前景,然而,缺少基于逻辑层业务的端对端通信功能大大限制了该总线在复杂系统中的应用。

设计的RapidIO通信中间件在消息机制上提供了虚通道数据传输功能。

高带宽、低时延以及易于实现功能迁移与重构的特性使其具备很强的工程应用价值。

可以看出,在本文采用的流控机制中,接收端回复ACK包的策略没有考虑传输特征因子的影响,造成ACK包的占比偏高,需要在后期工作中进一步优化。