301KD20NX中文资料

ZL30120GGG中文资料

1A full Design Manual is available to qualified customers.To register, please send an email to TimingandSync@.Features•Synchronizes with standard telecom system references and synthesizes a wide variety of protected telecom line interface clocks that are compliant with Telcordia GR-1244-CORE, GR-253-CORE, ITU-T G.813, and compatible with ITU-T G.8261 (formerly G.pactiming)•Internal low jitter APLL provides SONET/SDHclocks including 6.48MHz, 19.44MHz, 38.88MHz, 51.84MHz and 77.76MHz, or 25MHz and 50MHz Synchronous Ethernet output clocks•Programmable output synthesizers (P0, P1)generate general purpose clock frequencies from any multiple of 8kHz up to 100MHz•Jitter performance of <8 ps RMS on the low jitter APLL outputs, and <20 ps RMS on the programmable synthesizer outputs.•Provides 8 reference inputs which support clock frequencies with any multiples of 8kHz up to 77.76MHz in addition to 2kHz•Provides two DPLLs which have independent modes of operation (locked, free-run, holdover) and optional hitless reference switching.•Flexible input reference monitoring automatically disqualifies references based on frequency and phase irregularities•Provides 3 sync inputs for output frame pulse alignment•Generates several styles of output frame pulses with selectable pulse width, polarity, and frequency •Configurable input to output delay, and output to output phase alignment•Supports IEEE 1149.1 JTAG Boundary ScanMay 2006Figure 1 - Block DiagramZL30120SONET/SDH/EthernetMulti-Rate Line Card SynchronizerData SheetOrdering InformationZL30120GGG 100 Pin CABGA Trays ZL30120GGG2100 Pin CABGA**Trays**Pb Free Tin/Silver/Copper-40o C to +85o CZL30120Data SheetApplications•AMCs for AdvancedTCA TM and MicroTCA Systems•Synchronous Ethernet•Multi-Service Edge Switches or Routers•DSLAM Line Cards•WAN Line Cards•RNC/Mobile Switching Center Line Cards•ADM Line CardsZL30120Data SheetTable of Contents1.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111.1 DPLL Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111.2 DPLL Mode Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121.3 Ref and Sync Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131.4 Ref and Sync Monitoring. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141.5 Output Clocks and Frame Pulses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151.6 Configurable Input-to-Output and Output-to-Output Delays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .172.0 Software Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183.0 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25ZL30120Data SheetList of FiguresFigure 1 - Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Automatic Mode State Machine. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 3 - Reference and Sync Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 4 - Output Frame Pulse Alignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 5 - Behaviour of the Guard Soak Timer during CFM or SCM Failures. . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 6 - Output Clock Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 7 - Phase Delay Adjustments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17ZL30120Data SheetList of TablesTable 1 - DPLL1 and DPLL2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Table 2 - Set of Pre-Defined Auto-Detect Clock Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 3 - Set of Pre-Defined Auto-Detect Sync Frequencies. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 4 - Output Clock and Frame Pulse Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16ZL30120Data Sheet Pin DescriptionPin # Name I/OType DescriptionInput ReferenceC1 B2 A3 C3 B3 B4 C4 A4ref0ref1ref2ref3ref4ref5ref6ref7I d Input References (LVCMOS, Schmitt Trigger). These are input referencesavailable to both DPLL1 and DPLL2 for synchronizing output clocks. All eightinput references can be automatically or manually selected using softwareregisters. These pins are internally pulled down to Vss.B1 A1 A2sync0sync1sync2I d Frame Pulse Synchronization References (LVCMOS, Schmitt Trigger).These are the frame pulse synchronization inputs associated with inputreferences 0, 1 and 2. These inputs accept frame pulses in a clock format (50%duty cycle) or a basic frame pulse format with minimum pulse width of 5ns.These pins are internally pulled down to V ss.Output Clocks and Frame PulsesD10apll_clk0O APLL Output Clock 0 (LVCMOS). This output can be configured to provide anyone of the available SONET/SDH clock outputs up to 77.76MHz, or 25MHz and50MHz. The default frequency for this output is 77.76MHz.G10apll_clk1O APLL Output Clock 1 (LVCMOS). This output can be configured to provide anyone of the available SONET/APLL clock outputs up to 77.76MHz, or 25MHz and50MHz. The default frequency for this output is 19.44MHz.E10apll_fp0O APLL Output Frame Pulse 0 (LVCMOS). This output can be configured toprovide virtually any style of output frame pulse synchronized with an associatedAPLL output clock. The default frequency for this frame pulse output is 8kHz.F10apll_fp1O APLL Output Frame Pulse 1 (LVCMOS). This output can be configured toprovide virtually any style of output frame pulse synchronized with an associatedAPLL output clock. The default frequency for this frame pulse output is 2kHz.K9p0_clk0O Programmable Synthesizer 0 - Output Clock 0 (LVCMOS). This output can beconfigured to provide any frequency with a multiple of 8kHz up to 100MHz inaddition to 2kHz. The default frequency for this output is 2.048MHz.K7p0_clk1O Programmable Synthesizer 0 - Output Clock 1 (LVCMOS). This is aprogrammable clock output configurable as a multiple or division of the p0_clk0frequency within the range of 2kHz to 100MHz. The default frequency for thisoutput is 8.192MHz.K8p0_fp0O Programmable Synthesizer 0 - Output Frame Pulse 0 (LVCMOS). This outputcan be configured to provide virtually any style of output frame pulse associatedwith the p0 clocks. The default frequency for this frame pulse output is 8kHz.J7p0_fp1O Programmable Synthesizer 0 - Output Frame Pulse 1 (LVCMOS). This outputcan be configured to provide virtually any style of output frame pulse associatedwith the p0 clocks. The default frequency for this frame pulse output is 8kHz.ZL30120Data SheetJ10p1_clk0OProgrammable Synthesizer 1 - Output Clock 0 (LVCMOS). This output can be configured to provide any frequency with a multiple of 8kHz up to 100MHz in addition to 2kHz. The default frequency for this output is 1.544MHz (DS1).K10p1_clk1OProgrammable Synthesizer1 - Output Clock 1 (LVCMOS). This is aprogrammable clock output configurable as a multiple or division of the p1_clk0 frequency within the range of 2kHz to 100MHz. The default frequency for this output is 3.088MHz (2x DS1).H10fb_clk OFeedback Clock (LVCMOS). This output is a buffered copy of the feedback clock for DPLL1. The frequency of this output always equals the frequency of the selected reference.E1dpll2_ref ODPLL2 Selected Output Reference (LVCMOS). This is a buffered copy of the output of the reference selector for DPLL2. Switching between input reference clocks at this output is not hitless.Control H5rst_bIReset (LVCMOS, Schmitt Trigger). A logic low at this input resets the device. To ensure proper operation, the device must be reset after power-up. Reset should be asserted for a minimum of 300ns.J5dpll1_hs_enI uDPLL1 Hitless Switching Enable (LVCMOS, Schmitt Trigger). A logic high at this input enables hitless reference switching. A logic low disables hitless reference switching and re-aligns DPLL1’s output phase to the phase of the selected reference input. This feature can also be controlled through software registers. This pin is internally pulled up to Vdd.C2D2dpll1_mod_sel0dpll1_mod_sel1I uDPLL1 Mode Select 1:0 (LVCMOS, Schmitt Trigger). During reset, the levels on these pins determine the default mode of operation for DPLL1 (Automatic, Normal, Holdover or Freerun). After reset, the mode of operation can becontrolled directly with these pins, or by accessing the dpll1_modesel register through the serial interface. This pin is internally pulled up to Vdd.Status H1dpll1_lockOLock Indicator (LVCMOS). This is the lock indicator pin for DPLL1. This output goes high when DPLL1’s output is frequency and phase locked to the input reference.J1dpll1_holdover OHoldover Indicator (LVCMOS). This pin goes high when DPLL1 enters the holdover mode.Serial Interface E2sck I Clock for Serial Interface (LVCMOS). Serial interface clock.F1si I Serial Interface Input (LVCMOS). Serial interface data input pin.G1so O Serial Interface Output (LVCMOS). Serial interface data output pin.E3cs_bI uChip Select for Serial Interface (LVCMOS). Serial interface chip select. This pin is internally pulled up to Vdd.Pin # Name I/O Type DescriptionZL30120Data Sheet G2int_b O Interrupt Pin (LVCMOS). Indicates a change of device status prompting theprocessor to read the enabled interrupt service registers (ISR). This pin is anopen drain, active low and requires an external pulled up to VDD.APLL Loop FilterA6apll_filter A External Analog PLL Loop Filter terminal.B6filter_ref0A Analog PLL External Loop Filter Reference.C6filter_ref1A Analog PLL External Loop Filter Reference.JTAG and TestJ4tdo O Test Serial Data Out (Output). JTAG serial data is output on this pin on thefalling edge of tck. This pin is held in high impedance state when JTAG scan isnot enabled.K2tdi I u Test Serial Data In (Input). JTAG serial test instructions and data are shifted inon this pin. This pin is internally pulled up to Vdd. If this pin is not used then itshould be left unconnected.H4trst_b I u Test Reset (LVCMOS). Asynchronously initializes the JTAG TAP controller byputting it in the Test-Logic-Reset state. This pin should be pulsed low on power-up to ensure that the device is in the normal functional state. This pin is internallypulled up to Vdd. If this pin is not used then it should be connected to GND.K3tck I Test Clock (LVCMOS): Provides the clock to the JTAG test logic. If this pin is notused then it should be pulled down to GND.J3tms I u Test Mode Select (LVCMOS). JTAG signal that controls the state transitions ofthe TAP controller. This pin is internally pulled up to V DD. If this pin is not usedthen it should be left unconnected.Master ClockK4osci I Oscillator Master Clock Input (LVCMOS). This input accepts a 20MHzreference from a clock oscillator (TCXO, OCXO). The stability and accuracy ofthe clock at this input determines the free-run accuracy and the long termholdover stability of the output clocks.K5osco O Oscillator Master Clock Output (LVCMOS). This pin must be left unconnectedwhen the osci pin is connected to a clock oscillator.MiscellaneousA9 A10 B5 B9 B10 C5 D1 D3 G3NC No Connection. Leave unconnected.Pin # Name I/OType DescriptionZL30120Data Sheet J2J6H7K1IC Internal Connection. Connect to ground.F2F3K6IC Internal Connection. Leave unconnected.Power and GroundD9 E4 G8 G9 J8 J9 H6 H8V DD PPPPPPPPPositive Supply Voltage. +3.3V DC nominal.E8 F4V CORE PPPositive Supply Voltage. +1.8V DC nominal.A5 A8 C10AV DD PPPPositive Analog Supply Voltage. +3.3V DC nominal.B7 B8 H2AV CORE PPPPositive Analog Supply Voltage. +1.8V DC nominal.D4 D5 D6 D7 E5 E6 E7 F5 F6 F7 G4 G5 G6 G7 E9 F8 F9 H9V SS GGGGGGGGGGGGGGGGGGGround. 0 Volts.Pin # Name I/OType DescriptionZL30120Data SheetI - InputI d -Input, Internally pulled down I u -Input, Internally pulled up O -Output A -Analog P -Power G -GroundA7C7C8C9D8H3AV SSG G G G G GAnalog Ground. 0 Volts.Pin # Name I/O Type DescriptionZL30120Data Sheet1.0 Functional DescriptionThe ZL30120 Multi-Rate Line Card Synchronizer is a highly integrated device that provides timing and synchronization for network interface cards. It incorporates two independent DPLLs, each capable of locking to one of eight input references and provides a wide variety of synchronized output clocks and frame pulses.1.1 DPLL FeaturesThe ZL30120 provides two independently controlled Digital Phase-Locked Loops (DPLL1, DPLL2) for clock and/or frame pulse synchronization. DPLL1 is the main DPLL and is always enabled. To save on power, DPLL2 is disabled by default. For applications where DPLL2 is required, it must be enabled using the dpll_en bit of the dpll2_ctrl_0register (0x2A). Table 1 shows a feature summary for both DPLLs.FeatureDPLL1DPLL2Modes of Operation Free-run, Normal (locked), Holdover Free-run, Normal (locked), Holdover Loop Bandwidth User selectable: 14Hz, 28Hz, or wideband 1 (890Hz / 56Hz / 14Hz)1. In the wideband mode, the loop bandwidth depends on the frequency of the reference input. For reference frequencies equal to or greater than 64kHz, the loop bandwidth = 890Hz. For reference frequencies equal to or greater than 8kHz and less than 64 kHz, the loop bandwidth = 56Hz. For reference frequencies equal to 2kHz, the loop bandwidth is equal to 14Hz.Fixed: 14HzPhase Slope Limiting User selectable: 885ns/s, 7.5µs/s, 61µs/s, or unlimited User selectable: 61µs/s, or unlimited Pull-in Range Fixed: 130ppmFixed: 130ppmHoldover ParametersSelectable Update Times: 26ms, 1s, 10s, 60s, and Selectable Holdover Post Filter BW: 18mHz, 2.5Hz, 10Hz. Fixed Update Time: 26ms No Holdover Post FilteringHoldover Frequency AccuracyBetter than 1ppb (Stratum 3E) initial frequency offset. Frequency drift depends on the 20MHz external oscillator.Better than 50ppb (Stratum 3) initial frequency offset. Frequency drift depends on the 20MHz external oscillator.Reference Inputs Ref0 to Ref7Ref0 to Ref7Sync Inputs Sync0, Sync1, Sync2Sync inputs are not supported.Input Reference Selection/Switching Automatic (based on programmable priority and revertiveness), or manual Automatic (based on programmable priority and revertiveness), or manual Hitless Ref Switching Can be enabled or disabledCan be enabled or disabled Output Clocks apll_clk0, apll_clk1, p0_clk0, p0_clk1, p1_clk0, p1_clk1, fb_clk.p0_clk0, p0_clk1, p1_clk0, p1_clk1.Output Frame Pulses apll_fp0, apll_fp1, p0_fp0, p0_fp1 synchronized to active sync reference.p0_fp0, p0_fp1 not synchronized to sync reference.External Pins Status IndicatorsLock, HoldoverNoneTable 1 - DPLL1 and DPLL2 FeaturesZL30120Data Sheet1.2 DPLL Mode ControlBoth DPLL1 and DPLL2 independently support three modes of operation - free-run, normal and holdover. The mode of operation can be manually set or controlled by an automatic state machine as shown in Figure 2.Figure 2 - Automatic Mode State MachineFree-runThe free-run mode occurs immediately after a reset cycle or when the DPLL has never been synchronized to areference input. In this mode, the frequency accuracy of the output clocks is equal to the frequency accuracy of the external master oscillator. Lock AcquisitionThe input references are continuously monitored for frequency accuracy and phase regularity. If at least one of the input references is qualified by the reference monitors, then the DPLL will begin lock acquisition on that input. Given a stable reference input, the ZL30120 will enter in the Normal (locked) mode.Normal (locked)The usual mode of operation for the DPLL is the normal mode where the DPLL phase locks to a selected qualified reference input and generates output clocks and frame pulses with a frequency accuracy equal to the frequency accuracy of the reference input. While in the normal mode, the DPLL’s clock and frame pulse outputs comply with the MTIE and TDEV wander generation specifications as described in Telcordia and ITU-T telecommunication standards.HoldoverWhen the DPLL operating in the normal mode loses its reference input, and no other qualified references are available, it will enter the holdover mode and continue to generate output clocks based on historical frequency data collected while the DPLL was synchronized.ResetAnother reference is qualified and availablefor selectionPhase lock on the selected reference is achievedLock AcquisitionNormal (Locked)No references are qualified and available for selectionFree-RunHoldoverSelected referencefailsAll references are monitored for frequency accuracy and phase regularity, and at least one reference is qualified.Normal (Locked)ZL30120Data Sheet1.3 Ref and Sync InputsThere are eight reference clock inputs (ref0 to ref7) available to both DPLL1 and DPLL2. The selected reference input is used to synchronize the output clocks. Each of the DPLLs have independent reference selectors which can be controlled using a built-in state machine or set in a manual mode.Figure 3 - Reference and Sync InputsIn addition to the reference inputs, DPLL1 has three optional frame pulse synchronization inputs (sync0 to sync2)used to align the output frame pulses. The sync n input is selected with its corresponding ref n input, where n = 0, 1,or 2. Note that the sync input cannot be used to synchronize the DPLL, it only determines the alignment of the frame pulse outputs. An example of output frame pulse alignment is shown in Figure 4.Figure 4 - Output Frame Pulse Alignmentref7:0sync2:0DPLL2DPLL1ref napll/p0/p1_clk xapll/p0_fp xWithout a frame pulse signal at the sync input, the output frame pulses will align to any arbitrary cycle of its associated output clock.sync n - no frame pulse signal presentWhen a frame pulse signal is present at the sync input, the DPLL will align the output frame pulses to the output clock edge that is aligned to the input frame pulse.ref n apll/p0/p1_clk xapll/p0_fp xsync nn = 0, 1, 2x = 0, 1n = 0, 1, 2x = 0, 1ZL30120Data Sheet Each of the ref inputs accept a single-ended LVCMOS clock with a frequency ranging from 2kHz to 77.76MHz. Built-in frequency detection circuitry automatically determines the frequency of the reference if its frequency is within the set of pre-defined frequencies as shown in Table 2. Custom frequencies definable in multiples of 8kHz are also available.2 kHz8 kHz64 kHz1.544 MHz2.048 MHz6.48 MHz8.192 MHz16.384 MHz19.44 MHz38.88 MHz77.76 MHzCustom ACustom BTable 2 - Set of Pre-Defined Auto-Detect Clock FrequenciesEach of the sync inputs accept a single-ended LVCMOS frame pulse. Since alignment is determined from the rising edge of the frame pulse, there is no duty cycle restriction on this input, but there is a minimum pulse width requirement of 5ns. Frequency detection for the sync inputs is automatic for the supported frame pulse frequencies shown in Table 3.166.67 Hz(48x 125 µs frames)400 Hz1 kHz2 kHz8 kHz64 kHzTable 3 - Set of Pre-Defined Auto-Detect Sync Frequencies1.4 Ref and Sync MonitoringAll input references (ref0 to ref7) are monitored for frequency accuracy and phase regularity. New references are qualified before they can be selected as a synchronization source, and qualified references are continuously monitored to ensure that they are suitable for synchronization. The process of qualifying a reference depends on four levels of monitoring.Single Cycle Monitor (SCM)The SCM block measures the period of each reference clock cycle to detect phase irregularities or a missing clock edge. In general, if the measured period deviates by more than 50% from the nominal period, then an SCM failure (scm_fail) is declared.ZL30120Data SheetCoarse Frequency Monitor (CFM)The CFM block monitors the reference frequency over a measurement period of 30µs so that it can quickly detect large changes in frequency. A CFM failure (cfm_fail) is triggered when the frequency has changed by more than 3%or approximately 30000ppm.Precise Frequency Monitor (PFM)The PFM block measures the frequency accuracy of the reference over a 10 second interval. To ensure an accurate frequency measurement, the PFM measurement interval is re-initiated if phase or frequency irregularities are detected by the SCM or CFM. The PFM provides a level of hysteresis between the acceptance range and the rejection range to prevent a failure indication from toggling between valid and invalid for references that are on the edge of the acceptance range.When determining the frequency accuracy of the reference input, the PFM uses the external oscillator’s output frequency (f ocsi ) as its point of reference. Guard Soak Timer (GST)The GST block mimics the operation of an analog integrator by accumulating failure events from the CFM and the SCM blocks and applying a selectable rate of decay when no failures are detected.As shown in Figure 5, a GST failure (gst_fail) is triggered when the accumulated failures have reached the upper threshold during the disqualification observation window. When there are no CFM or SCM failures, the accumulator decrements until it reaches its lower threshold during the qualification window.Figure 5 - Behaviour of the Guard Soak Timer during CFM or SCM FailuresAll sync inputs (sync0 to sync2) are continuously monitored to ensure that there is a correct number of reference clock cycles within the frame pulse period.1.5 Output Clocks and Frame PulsesThe ZL30120 offers a wide variety of outputs including two low jitter LVCMOS (apll_clk0, apll_clk1) output clocks and four programmable LVCMOS (p0_clk0, p0_clk1, p1_clk0, p1_clk1) output clocks. In addition to the clock outputs, two LVCMOS frame pulse outputs (apll_fp0, apll_fp1) and two LVCMOS programmable frame pulses (p0_fp0, p0_fp1) are also available.The feedback clock (fb_clk ) of DPLL1 is available as an output clock. Its output frequency is always equal to DPLL1’s selected input frequency.refCFM or SCM failuresupper thresholdlower thresholdt d - disqualification timet q - qualification time = n * t dt dt qgst_failZL30120Data SheetThe output clocks and frame pulses derived from the low jitter APLL are always synchronous with DPLL1, and the clocks and frame pulses generated from the programmable synthesizers can be synchronized to either DPLL1 or DPLL2. This allows the ZL30120 to have two independent timing paths.Figure 6 - Output Clock ConfigurationThe supported frequencies for the output clocks and frame pulses are shown in Table 4.apll_clk0, apll_clk1(LVCMOS)11. The apll_clk x outputs can generate either SONET/SDH or Ethernet frequencies (25MHz, 50MHz). p0_clk0, p1_clk0(LVCMOS)p0_clk1, p1_clk1(LVCMOS)apll_fp0, apll_fp1, p0_fp0, p0_fp1(LVCMOS)22. apll_fp x frequencies are available only when the low jitter apll is generating SONET/SDH frequencies6.48 MHz 2 kHz p x _clk0 p x _clk1 =2M166.67 Hz (48x 125 µs frames)9.72 MHz N * 8 kHz (up to 100MHz)400 Hz 12.96 MHz 1 kHz 19.44 MHz 2 kHz 25.92 MHz 4 kHz 38.88 MHz 8 kHz 51.84 MHz 32 kHz 77.76 MHz 64 kHz25 MHz 50 MHzTable 4 - Output Clock and Frame Pulse Frequenciesp0_clk0p0_fp0p0_clk1p0_fp1 P0 Synthesizerp1_clk0p1_clk1P1 Synthesizerapll_clk0apll_fp0apll_clk1apll_fp1Low Jitter APLLFeedback Synthesizerfb_clkDPLL2DPLL1ZL30120Data Sheet1.6 Configurable Input-to-Output and Output-to-Output DelaysThe ZL30120 allows programmable static delay compensation for controlling input-to-output and output-to-output delays of its clocks and frame pulses.All of the output synthesizers (APLL, P0, P1, Feedback) locked to DPLL1 can be configured to lead or lag the selected input reference clock using the DPLL1 Fine Delay . The delay is programmed in steps of 119.2ps with a range of -128 to +127 steps giving a total delay adjustment in the range of -15.26ns to +15.14ns. Negative values delay the output clock, positive values advance the output clock. Synthesizers that are locked to DPLL2 are unaffected by this delay adjustment.In addition to the fine delay introduced in the DPLL1 path, the APLL, P0, and P1 synthesizers have the ability to add their own fine delay adjustments using the P0 Fine Delay , P1 Fine Delay , and APLL Fine Delay . These delays are also programmable in steps of 119.2ps with a range of -128 to +127 steps.In addition to these delays, the single-ended output clocks of the APLL, P0, and P1 synthesizers can be independently offset by 90, 180 and 270 degrees using the Coarse Delay . The output frame pulses (APLL, P0) can be independently offset with respect to each other using the FP Delay .Figure 7 - Phase Delay AdjustmentsDPLL1DPLL2P0 Fine Delayp0_clk0p0_clk1p0_fp0p0_fp1 P0 SynthesizerCoarse DelayCoarse Delay FP Delay FP Delay fb_clkp1_clk0p1_clk1P1 Fine DelayLow Jitter APLLapll_clk0apll_clk1apll_fp0apll_fp1APLL Fine DelayFeedback SynthesizerDPLL1 Fine DelayCoarse DelayCoarse Delay FP Delay FP DelayCoarse Delay Coarse DelayP1 SynthesizerZL30120Data Sheet 2.0 Software ConfigurationThe ZL30120 is mainly controlled by accessing software registers through the serial peripheral interface (SPI). The device can be configured to operate in a highly automated manner which minimizes its interaction with the system’s processor, or it can operate in a manual mode where the system processor controls most of the operation of the device.The following table provides a summary of the registers available for status updates and configuration of the device.Addr (Hex)RegisterNameResetValue(Hex)Description TypeMiscellaneous Registers00id_reg A4Chip and version identification and reset readyindication registerR01use_hw_ctrl00Allows some functions of the device to becontrolled by hardware pinsR/WInterrupts02ref_fail_isr FF Reference failure interrupt service register R 03dpll1_isr70DPLL1 interrupt service register StickyR 04dpll2_isr00DPLL2 interrupt service register StickyR 05ref_mon_fail_0FF Ref0 and ref1 failure indications StickyR 06ref_mon_fail_1FF Ref2 and ref3 failure indications.StickyR 07ref_mon_fail_2FF Ref4 and ref5 failure indications StickyR 08ref_mon_fail_3FF Ref6 and ref7 failure indications StickyR 09ref_fail_isr_mask00Reference failure interrupt service registermaskR/W 0A dpll1_isr_mask00DPLL1 interrupt service register mask R/W 0B dpll2_isr_mask00DPLL2 interrupt service register mask R/W 0C ref_mon_fail_mask_0FF Control register to mask each failure indicatorfor ref0 and ref1R/W0D ref_mon_fail_mask_1FF Control register to mask each failure indicatorfor ref2 and ref3R/W0E ref_mon_fail_mask_2FF Control register to mask each failure indicatorfor ref4 and ref5R/W。

蓝星COD说明书

1.1 接线端子说明LXWA-O安装固定完成后,即可进行电源线和信号输出线的接线。

LXWA-O 接线端子在控制器的接线盒内,打开接线盒盖板,对照接线端子说明,按照需要进行电源和信号输出线的接线。

接线端子说明见表4.3.1。

注意: * 通讯端口通过接口上方的跳线配置为RS232或RS485模式: RS232模式: 1-4 OFF, 5-8 ON;RS485模式: 1-4 ON, 5-8 OFF;** 这些端口带有可以对人体造成危险或伤害的高电压,为了您的生命安全,请断电操作。

*** LXWA-O接地线必须按照有关标准可靠接地。

如果没有接地或接地不可靠,有可能造成LXWA-O不稳定或意外危险。

2水样取样和排放蠕动泵对水样的最大自由提升高度为1.5米,样水软管可直接插入污水池中,或者连接到外部取样管路上。

水样排放求自由排放,排放口不带压力,无阻力排放。

图6.1为取样和排放示意图。

(a) 水池取样(b) 管路取样图6.1取样和排放示意图3系统运行在LXWA-O完成安装和外部接线工作,并且检查完水样取样和排放等外围连接,正确无误以后,LXWA-O即可以投入正常使用。

本章主要讲述LXWA-O投运的步骤。

3.1 生物反应器中初始水样的加入生物反应器中初始水样的加入,可以通过直接加入的的方式,即先拔出搅拌电机部分,用容器盛被测量水样400mL,直接倒入生物反应中。

图8.1.1 初始水样的加入初始水样加入后,插入搅拌电机部分,注意,搅拌桨插入时,桨叶应稍微向溶解氧探头相反的方向倾斜。

然后,再按照第5章所述的安装过程将生物反应器安装到LXWA-O上并完成LXWA-O内部的联接。

3.2 LXWA-O通电运行8.1节所述过程完成后,首先要确认供电电源是否正确,如果符合3.1节所述的要求,LXWA-O就可以通电运行。

LXWA-O通电后,有两分钟的初始化过程,然后,LXWA-O进正常的测量过程。

如果初始水样温度较低,LXWA-O有一个加温过程(到30℃约10~30分钟),在此过程中,LXWA-O读数错误或没有读数,如果初始水样是首次加入,还需要经过4~24小时的驯化过程,才能得到正确的读数。

德特威勒产品手册可编辑

DMD

内模板

外模板

模板

(5-8um半径)

(0-23um半径)

1

0.33ps/m

0.33ps/m

2

0.27ps/m

0.35ps/m

3

0.26ps/m

1300nm

台阶(双向平均值)

≤0.10

dB

不均匀性(整个光纤长度)和衰减点不连续性

≤0.10

dB

背向散射衰减系数差异(双向测试)

≤0.10

dB/km

几何特性

芯径

62.5±2.5

um

包层直径

125.0±1.0

um

包层不圆度

≤1.0

%

涂层直径

242±7

um

涂层/包层同心度误差

≤12.0

um

涂层不圆度

≤6.0

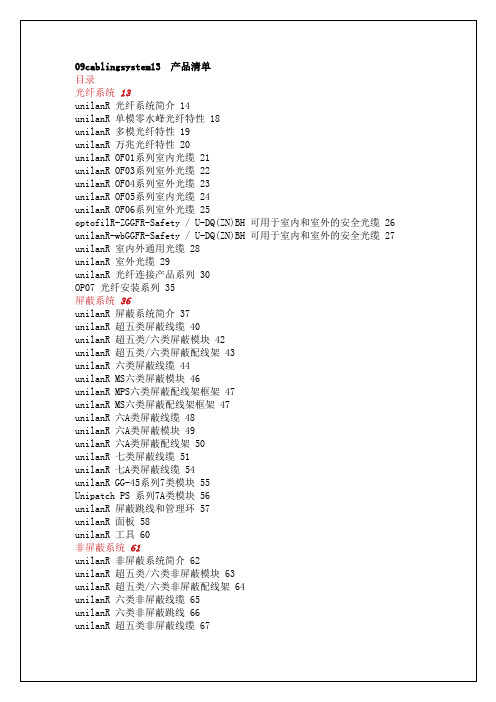

unilanR MPS六类屏蔽配线架框架47

unilanR MS六类屏蔽配线架框架47

unilanR六A类屏蔽线缆48R六A类屏蔽配线架50

unilanR七类屏蔽线缆51

unilanR七A类屏蔽线缆54

unilanR GG-45系列7类模块55

Unipatch PS系列7A类模块56

%

芯/包层同心度误差

≤1.5

um

Unilan?万兆光纤特性

Unilan?德特威勒万兆多模光纤特性:

满足IEC60793-2-10A1b、IEEE802.3ae、Bellcore、EIA/TIA-492AAAC、ISO11801OM3、TIA/EIA-455和TIA568C.3-2009标准,在850nm处可以支持万兆以太网速率达300米及支持1000Base-SX达900米距离,同时又可向下兼容目前的1G,100Mbps,10Mbps以太网应用。

新代20系列总线应用手册V1.7

20系列总线应用手册技术中心2012-12-15V1.7Contents1摘要 (3)2硬件规格 (4)2.1框架图 (4)2.2硬件明细 (4)2.3驱动器和电机选型 (5)2.4规格简介 (6)2.4.1引脚定义 (7)3配线 (8)3.1配线图 (8)3.2驱动器重电配线说明 (9)3.2.1急停不控制驱动器重电 (9)3.2.2急停控制驱动器重电 (10)4参数设定 (11)4.1控制器参数设定 (11)4.2驱动器参数设定 (14)4.3驱动器通讯地址设定 (16)5功能介绍 (17)5.1串列参数设置 (17)5.2自动调机 (20)5.3绝对值读取 (24)5.3.1绝对值编码器复位 (24)5.3.1.1绝对值编码器复位方法一 (24)5.3.1.2绝对值编码器复位方法二 (25)5.3.2绝对式原点设定 (26)5.3.2.1人机画面设定绝对式原点 (26)5.3.2.2PLC设定绝对式原点 (27)5.4驱动器警报内容显示 (28)5.5扭力控制(暂无此功能) (29)5.6主轴负载率显示 (30)6Q&A (31)7附件1.驱动器警报说明及处理对策 (33)摘要新代科技20系列控制器搭载安川Mechatrolink-II总线(串行)通讯控制方式,改善传统脉波式泛用型控制器配线及扩充性问题,使系统更简化,更有扩充性,装配更容易。

20系列最多可控制16轴伺服马达同动。

I/O接点除了控制器本身提供的32组Direct Input及Output外,还可透过RIO串行接口连接外部I/O模块。

依IO点需求决定是否增配RIO模块,选择更具弹性。

20系列控制器,除总线通讯外,可控制一组传统脉波式泛用型主轴,兼容P型、V型、变频命令输出,除总线主轴外,也可以有更经济的主轴方案选择总线泛用硬件配线简单复杂单位时间数据传输量多(1Mb/sec以上) 少(500 Kb/sec)各单元间的通信Yes No伺服分辨率高低DDA指令超过警报不用考虑需经计算评估来避免驱动器警报内容显示有无主轴负载率显示有无控制器设置驱动器参数有无驱动器参数备份有无扭力回路有无绝对值读取有无硬件规格2.1框架图2.2硬件明细⏹新代20系列控制器⏹安川SigmaV总线驱动器+电机SGDV-□□□□11A 型(M-II 型)。

IPD20N03L中文资料

IPD20N03L IPU20N03L

Symbol

Values

Unit

min.

typ. max.

RthJC RthJA RthJA

-

1.7

2.5 K/W

-

-

100

-

-

75

-

-

50

Electrical Characteristics, at Tj = 25 °C, unless otherwise specified

-

-

30 A

-

-

120

-

1.1

1.4 V

-

15

18 ns

-

2

3 nC

Page 3

2003-01-17

元器件交易网

IPD20N03L IPU20N03L

1 Power dissipation Ptot = f (TC)

2 Drain current ID = f (TC) parameter: VGS≥ 10 V

VDS=30V, VGS=0V, Tj=25°C VDS=30V, VGS=0V, Tj=125°C

Gate-source leakage current

VGS=20V, VDS=0V

Drain-source on-state resistance

VGS=4.5V, ID=15A

Drain-source on-state resistance

IPD20N03L

32 A

24

20

16

12

8

4

0

0 20 40 60 80 100 120 140 160 °C 190 TC

ISA-301D系列通讯接口设备技术使用说明书V1.00-081229

Ver 1.00

编写: 审核: 批准:

黎强 侯 林 陈远生 徐成斌

长园深瑞继保自动化有限公司 二〇〇八年九月

本说明书由长园深瑞继保自动化有限公司编写并发布,并具有对相关产品的最终解释权。 相关产品的后续升级可能会和本说明书有少许出入,说明书的升级也可能无法及时告知阁下, 对此我们表示抱歉!请注意核对实际产品与说明书的版本是否相符。 更多产品信息,请访问互联网:

7 装置软件功能 ..................................................................................................... 8

7.1 完善的规约库 ................................................................................................................. 8 7.2 遥控允许检查 ................................................................................................................. 9 7.3 遥控闭锁检查 ................................................................................................................. 9 7.4 遥测归一化转换 ............................................................................................................. 9 7.5 信号转换和合成 ........................................................................................................... 10 7.6 事件记录....................................................................................................................... 10 7.7 打印功能....................................................................................................................... 10 7.8 调试功能....................................................................................................................... 10 7.9 远程维护....................................................................................................................... 11

301温度控制器操作说明书

1 控制器和手册的介绍

1.1 该手册的使用

该手册介绍如何设置和操作 301 温度控制器;该手册必须与相关加热炉的使用手册结合起来阅 读理解。

对于复杂控制的加热炉,该手册不可避免地会出现一些技术专有名词。这些名词的解释在该手 册最后的“术语表”内。

1.2 PID 控制

301 控制器采用了 PID(比例 积分 微分)温度控制。该控制方式利用精确的数字控制系统来 调整加热元件的功率,使炉子温度能稳定保持在设定的温度。

或者

用上、下键调节数值。按一次,显示当前数值,再按一次或

者一直按就会改变当前数值(Hr:Min)。

不用进行任何操作,数值就会保存。

(更多的信息请参考第五章节,定时器)

6

3 高级操作

3.1 进入设置菜单

在常显示界面 按住翻页键 1.5 秒 显示出设置菜单的第一个参数界面

3.2 改变定时类型

在常显示界面

2.2 指示灯

输出显示

定时显示

当炉子正在加热时,此灯亮 计时器工作时,此灯亮

过温保护显示

通常情况下,绿灯亮。过温保护启动时,红灯闪烁。当 过温保护重起及等待温度降低时,红灯常亮。

2.3 系统菜单

301 温度控制器菜单分为 2 个部分:主菜单和设置菜单。主菜单包含所有的基本操作控制:温 度设置,升温速率设置和定时设置。设置菜单包括所有的参数设置:定时类型,定时段,输出功率 及用户校准。这些设置的改变取决于用户的输入以及产品的固有特性。

2.4 常显示界面

当打开控制器时,显示出常显示界面,其中显示炉子的实际温度和点相应键可以显示设置温度。 如果已进入某菜单,且 30 秒内没有按任何键,控制器会自动返回初始界面。

2.4.1 从主菜单到常显示界面

艾默生产品目录中文

17 主控配电柜 18 相位补偿

8 主轴

19 中央控制器

9 偏航齿轮 10 塔式气闸

20 输出变压器及配电

11 风机座

9

数据中心及IT解决方案

11 交流电源系统 (20KVA以上) 18 数据机房高压直流电源系统 21 精密制冷系统 30 服务器电源管理系统 31 谐波治理系统 32 交流电源系统 (20KVA以下) 40 服务器机柜 & 管理系统 49 Avocent® IT 管控系统 59 Trellis™ 动态基础设施优化平台

Instrum

Safety Lighting

光伏并网发电解决方案

集中式光伏发电解决方案

光伏组件

汇流箱

SSL系列 集中式逆变器

升压变压器

电网

分布式光伏发电解决方案

SPV系列 组串式逆变器

光伏组件

汇流箱

SSM系列 集中式逆变器

预装式光伏发电解决方案

SSO系列预装式光伏并网逆变站

辅助电源系统

动力配电箱 插座 照明

在线式双变换设计,完全隔离市电及油机可能存在的各类电网污染及电网故障对 负载的影响

输出功率因数提升至0.9,更适应大规模采用功率因数校正技术的服务器计算机及 网络中心比传统UPS带载能力增加10%以上

采用先进的第6代DSP及全数字控制技术,系统稳定性更高 标准内置D级防雷器 多种输入谐波抑制技术,提高电能利用率 零相移输出隔离变压器,减小零地电压和负载谐波电流对逆变器的影响 超强输出过载及短路能力,确保系统稳定性和极限状态的系统安全 可实现8台并联 标准内置LBS功能 超宽输入电压、频率范围,适应恶劣电网环境 智能化电池管理,自动维护电池,延长使用寿命 10.4英寸超大触摸屏彩色LCD显示,中英文等多种语言,方便用户使用 分层独立式风道和冗余风扇设计,电路板三防漆防护,内置防尘滤网,具有高效

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MCC

TM

Micro Commercial Components

omponents 20736 Marilla Street Chatsworth !"# $

% !"#

1 of 6

2006/09/09

元器件交易网

182KD20NX thru 180LD20NX

MCC

TM

Micro Commercial Components

Electrical Characteristics @ 25OC Unless Otherwise Noted

Maximum Allowable Voltage Part Number ACrms (V) 182KD20N X 112KD20N X 102KD20N X 911KD20N X 821KD20N X 781KD20N X 751KD20N X 681KD20N X 621KD20N X 561KD20N X 511KD20N X 471KD20N X 431KD20N X 391KD20N X 361KD20N X 331KD20N X 301KD20N X 271KD20N X 241KD20N X 221KD20N X 201KD20N X 181KD20N X 151KD20N X 121KD20N X 101KD20N X 820KD20N X 680KD20N X 560KD20N X 470KD20N X 390KD20N X 330KD20N X 270KD20N X 220KD20N X 180LD20N X 1000 680 625 550 510 485 460 420 385 350 320 300 275 250 230 210 195 175 150 140 130 115 95 75 60 50 40 35 30 25 20 17 14 10 DC (V) 1465 895 825 745 670 640 615 560 505 460 418 385 350 320 300 275 250 225 200 180 170 150 125 100 85 65 56 45 38 31 26 22 18 14 10/1000us (J) 695 496 448 408 376 368 360 344 328 312 296 280 264 240 208 184 168 158 134 124 114 104 88 64 56 44 24 20 17 14 12 10 8 7 2000 1000 0.2 6500 4000 1 1 time (A) 2 times (W) (V) 1800(1620-1980) 1100(990-1210) 1000(900-1100) 910(819-1001) 820(738-902) 780(702-858) 750(675-825) 680(612-748) 620(558-682) 560(504-616) 510(459-561) 470(423-517) 430(387-473) 390(351-429) 360(324-396) 330(297-363) 300(270-330) 270(243-297) 240(216-264) 220(198-242) 200(185-225) 180(162-198) 150(135-165) 120(108-132) 100(90-110) 82(74-90) 68(61-75) 56(50-62) 47(42-52) 39(35-43) 33(30-36) 27(24-30) 22(20-24) 18(15-21) (V) 2970 1815 1650 1500 1355 1290 1240 1120 1025 920 842 775 710 650 595 550 505 455 395 360 330 300 250 200 165 135 *135 *110 *93 *77 *65 *53 *43 *36 V1mA V100A Maximum Energy Withstanding Surge Current Rated Wattage Varistor Voltage Maximum Clamping Voltage

2000 1000 900 800 700 600 500 400 300 V 200

100 90 80 70 60 50 40 30 10

-6

Test current waveform 10-6 to 10-3 A: Direct current -1 -4 10 to 10 A: 8/20µs 10

-5

10

-4

10

-3

10

-2

10

-1

10

0

10

1

10

2

10

3

10

4

10

5

A

Revision: 2

3 of 6

2006/09/09

元器件交易网

182KD20NX thru 180LD20NX

V-I Curve (621K to 182K)

5000 Max. Leakage Current Max. Clamping Voltage

MCC

TM

Micro Commercial Components

4000

182KD20 152KD20 112KD20 102KD20 911KD20 821KD20 781KD20 751KD20 681KD20 621KD20

3000

2000 V 1000 700 600 500 400 300 200 10

182KD20NX* thru 180LD20NX*

11 to 1000 Volts Varistor 7.0 to 695.0 Joule

Features

• • • • • Radial-Lead Varistor Designed to be Operated Continuously Across AC Power Lines No Derating Up to 85к Ambient Available in Tape and Reel or Bulk Pack UL Recognized File # E306895(UL1449) and E306942(UL1414)

*

Hale Waihona Puke 'X' can be S, C, I or Y . 'S' 'C' 'I' 'Y' denotes denotes denotes denotes straight lead out crimped lead inner crimped lead kink lead

Revision: 2

3000 2000 1000 500 400 300 200 A 100 50 40 30 20 10 5 4 3 2 1 10 times 10 times 10 times 106 times

5 4 3

3000 2000 1000 10 times 1 time 2 times 10 times

-6

Test current waveform -6 -3 10 to 10 A: Direct current -1 4 10 to 10 A: 8/20µs 10

-5

10

-4

10

-3

10

-2

10

-1

10

0

10

1

10

2

10

3

10

4

10

5

A V-I Surge Life Time Ratings (330K to 680K) 10000 10000 V-I Surge Life Time Ratings (820K to 182K)

Max. Leakage Current Max. Clamping Voltage 561KD20 511KD20 471KD20 431KD20 391KD20 361KD20 331KD20 301KD20 271KD20 241KD20 221KD20 201KD20 181KD20 151KD20 121KD20 101KD20 820KD20

Max. Clamping Voltage 680KD20 560KD20 470KD20 390KD20 330KD20

TM

V-I Curve (330K to 680K)

400 300 200 100 70 60 680KD20 30 V 20 560KD20 470KD20 390KD20 330KD20 Max. Leakage Current

元器件交易网

182KD20NX thru 180LD20NX

MCC

Micro Commercial Components

TM

Note 2.

T

Part Code

182K 112K 102K 911K 821K 781K 751K 681K 621K 561K 511K 471K 431K 391K 361K 331K 301K 271K 241K 221K 201K 181K 151K 121K 101K 820K 680K 560K 470K 390K 330K 270K 220K 180L

10 9 6 5 Test current waveform -6 -3 10 to 10 A: Direct current -1 4 10 to 10 A: 8/20µs 10

-6

10

-5

10

-4

10

-3

10

-2

10

-1

10

0

10

1

10

2

10

3

104

105