第6章80C51单片机的串行口

单片机原理及应用第6章80C51单片机的串行口

单片机原理及应用第6章80C51单片机的串行口80C51单片机是一种基于哈佛架构的8位单片机,具有强大的串行口功能。

串行口是一种通信接口,可以通过单根线传输数据。

本章将介绍80C51单片机的串行口原理及其应用。

一、80C51单片机的串行口原理80C51单片机的串行口包含两个寄存器,分别是SBUF(串行缓冲器)和SCON(串行控制寄存器)。

SBUF寄存器用来存储待发送或接收到的数据,SCON寄存器用来配置和控制串行口的工作模式。

80C51单片机的串行口有两种工作模式:串行异步通信模式和串行同步通信模式。

1.串行异步通信模式串行异步通信是指通信双方的时钟频率不同步,通信的数据按照字符为单位进行传输,字符之间有起始位、数据位、校验位和停止位组成。

80C51单片机的串行口支持标准的RS-232通信协议和非标准通信协议。

在串行异步通信模式下,SCON寄存器需要配置为相应的工作模式。

首先,需要选择串行口的工作模式。

80C51单片机支持第9位,即扩展模式,可以用来检测通信错误。

其次,需要设置波特率。

波特率是指数据每秒传输的位数,用波特率发生器(Baud Rate Generator,BRGR)来控制。

然后,需要设置起始位、数据位和停止位的配置,包括数据长度(5位、6位、7位或8位)、停止位的个数(1位或2位)。

在发送数据时,将待发送的数据通过MOV指令传送到SBUF寄存器,单片机会自动将数据发送出去。

在接收数据时,需要检测RI(接收中断)标志位,如果RI为1,表示接收到数据,可以通过MOV指令将接收到的数据读取到用户定义的变量中。

2.串行同步通信模式串行同步通信是指通信双方的时钟频率同步,在数据传输时需要时钟信号同步。

80C51单片机的串行同步通信支持SPI(串行外设接口)和I2C(串行总线接口)两种协议。

在串行同步通信模式下,SCON寄存器需要配置为相应的工作模式。

首先,需要选择串行口的工作模式。

80C51单片机支持主从模式,可以作为主设备发送数据,也可以作为从设备接收数据。

2.3 80C51单片机的并行端口结构

80C51单片机的并行端口结构80C51共有4个8位的并行I/O口,分别记作P0、P1、P2、P3。

被归入专用寄存器。

I/O端口有串行和并行之分,串行I/O端口一次只能传送一位二进制信息,并行I/O端口一次能传送一组二进制信息。

(1)并行I/O口的功能①PO口:电路中包括一个数据输出锁存器和两个三态数据输入缓存器,另外还有一个数据输出的驱动和控制电路。

这两组端口用来作为CPU与外部数据存储器、外部程序存储器和I/O扩展口的总线接口,而不像P1、P3直接用做输出口。

P0.0~P0.7,P0口是8位双向I/O口,P0.i引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

该8位都是漏极开路(漏极开路即高阻状态,适用于输入/输出,其可独立输入/输出低电平和高阻状态)输出,每个引脚可以驱动8个LS型TTL负载且内部没有上拉电阻,执行输出功能时外部必须接上拉电阻(10K 即可)。

若要执行输入功能,必须先输出高电平方能读取该端口所连接的外部数据;若在访问外部存储器(RAM、ROM)和扩展的I/O口时,P0可作为地址总线(A0~A7)和数据总线(D0~D7),分时进行工作。

在指令的前半周期,P0口作为地址总线的低8位,在指令的后半周期为8位的数据总线。

P1口的各个单元:输入缓冲器:在P0口中,有两个三态的缓冲器,三态门有三个状态,即在其输出端可以是高电平、低电平和高阻状态(或称为禁止状态)。

上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为…读锁存器‟端)有效。

要读取P0.i引脚上的数据,也要使标号为…读引脚‟的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:存储器中可以存放电荷,加一个小的存储器的单元,并在它的面前加一个开关,要让这一位输出时,就把开关打开,信号就进入存储器的单元,然后马上关闭开关,这一位的状态就被保存下来,直到下一次命令让它把开关再打开为止,这就是锁存器。

单片机80C51

单片机80C5180C51单片机的典型产品有80C51﹑80C31和87C51,80C51是ROM型单片机,内部有4KB ROM;80C31无片内ROM;87C51片内有4KB EPROM。

除此外三者的内部结构和引脚完相同。

图1-1 为80C51的内部结构80C51的内部结构包括:【中央处理器(CUP)】主要完成运算和控制功能,80C51的CPU 是一个字节为8位的中央处理器,即它对数据的处理是按字节为单位的;【内部数据处理器(内部RAM】)80C51中共有256个RAM单元,但其中能作为寄存器供用户使用的仅有前面128个,后128个被专用寄存器占用;【内部程序储存器(内部ROM)】80C51共有4KB的掩膜ROM,用于存放程序、原始数据;【定时器/计数器】80C51有2个16位的定时器/计数器;【并行I/O口】80C51共有4个8位I/O口(P0P1P2P3)可实现数据并行输入输出;【串行口】80C51有1个全双工的可编程的串行口,以实现单片机与其他设备之间的串行数据传送;【时钟电路】80C51单片机内部有时钟电路,但晶振和微调电容要外接,为其产生时钟脉冲序列;【中断系统】它共有5个中断源:2个是外部中断源/INTO和/INT1,3个内部中断源,即2个定时/计数中断,1个串行口中断;还有驱动器、锁存器、缓冲器、地址寄存器等。

图1-2 为80C51的引脚图功能说明:主电源引脚Vss(20脚)和Vcc(40脚);时钟电路引脚XTAL1(19脚)和XTAL2(18脚),用法见图1-2;控制信号引脚如下:RST复位(9脚)输入24个时钟脉冲周期宽度以上H电平复位,接法见图1-3;ALE或/PROG、(30脚)锁存扩展地址低位字节控自信号,或EPROM编程时输入编程脉冲;/PSEN、(29脚)访问片外程序存储器是输出负脉冲作片选控制信号,12个始终周期2次生效,但访问片外RAM时无效,见时序图图1-3;/EA或Vpp(31)程序储存地址的选择,H时先选片内超址时自动跳到片外ROM,或编程时施加编程电压。

80C51单片机原理

80C51单片机原理RAM地址寄存器 RAM 128B 程序地址寄存器P0驱动器 P2锁存器 P2驱动器P1锁存器 暂存器2 B 寄存器 4KB ROM暂存器1ACC SP P0锁存器 PC PC 增1 缓冲器 P3锁存器 OSC中断、串行口及定时器PSW ALU DPTRP1驱动器 P3驱动器XTAL1XTAL2 P0.0~P0.7 P2.0~P2.7 P3.0~P3.7 P1.0~P1.7 RST ALEV CCV SS定时控制 指令译码器 指令寄存器 PSEN EA表2-1 P3口各引脚与第二功能表PSW 的各位定义见表80C51 P0~P3接口功能简见大多数口线都有双重功能,介绍如下: 1、P0口具有双重功能:(1) 作为通用I/O ,外接I/O 设备。

(2) 作为地址/数据总线。

在有片外扩展存储器的系统 中,低8位地址和数据由P0口分时传送。

PSW 位地址 PS W.7PSW .6PSW .5 PSW .4 PSW .3 PSW .2 PSW .1 PSW .0 位标志CY ACF0RS1RS0OVF1P2、P1口是唯一的单功能口:作为输入/输出口,P1口的每一位都可作为输入/输出口。

3、P2口具有双重功能:(1)作为输入/输出口。

(2)作为高8位地址总线。

在有片外扩展存储器的系统中,高8位地址由P2口传送。

4、P3口具有双重功能:(1)作第一功能使用时,其功能为输入/输出口。

(2)作第二功能使用时,每一位功能定义如表2.1所示。

80C51单片机的4个I/O口都是8位双向口,这些口在结构和特性上是基本相同的,但又各具特点,以下将分别介绍之。

图2-9 P0口某位的结构图2-10 P1口某位的结构1D CPQQ MUX& T1T2锁存器地址/数据控制信号C V CC内部总线写锁存器读锁存器读引脚P0.X引脚12DCPQQ T锁存器V CC内部总线写锁存器读锁存器读引脚P1.X引脚12图2-11 P2口某位的结构图2-12 P3口某位的结构P0~P3口使用时应注意事项1、如果80C51单片机内部程序存贮器ROM 够用,不需要扩展外部存贮器和I/O接口,80C51的四个口均可作I/O 口使用。

单片机原理及接口技术课后习题答案-李朝青

第一章1.什么是微处理器(CPU)、微机和单片机?答:微处理器本身不是计算机,但它是小型计算机或微机的控制和处理部分.微机则是具有完整运算及控制功能的计算机,除了微处理器外还包括存储器、接口适配器以及输入输出设备等。

单片机是将微处理器、一定容量的RAM、ROM以及I/O口、定时器等电路集成在一块芯片上,构成的单片微型计算机。

2.单片机具有哪些特点(1)片内存储容量越来越大。

(2抗干扰性好,可靠性高。

(3)芯片引线齐全,容易扩展。

(4)运行速度高,控制功能强。

(5)单片机内部的数据信息保存时间很长,有的芯片可以达到100年以上3。

微型计算机怎样执行一个程序?答:通过CPU指令,提到内存当中,再逐一执行.5.什么是嵌入式系统?他有哪些类型?为什么说单片机是典型的嵌入式系统?答;嵌入式系统是将先进的计算机技术、半导体技术和电子技术和各个行业的具体应用相结合后的产物,这一点就决定了它必然是一个技术密集、资金密集、高度分散、不断创新的知识集成系统。

它有嵌入式微处理器、嵌入式微控制器、嵌入式DSP处理器、嵌入式片上系统等.嵌入式系统的出现最初是基于单片机的。

它从体系结构到指令系统都是按照嵌入式应用特点专门设计的,能最好的满足面对控制对象,应运系统的嵌入、现场的可靠运行以及非凡的控制品质要求.因此,她是典型的嵌入式系统。

第二章1.89C51单片机内包含哪些主要逻辑功能部件?答:80C51系列单片机在片内集成了以下主要逻辑功能部件:(l)CPU(中央处理器):8位(2)片内RAM:128B(3)特殊功能寄存器:21个(4)程序存储器:4KB(5)并行I/O口:8位,4个(6)串行接口:全双工,1个(7)定时器/计数器:16位,2个(8)片内时钟电路:1个2。

89C51的EA端有何用途?答:/EA端接高电平时,CPU只访问片内flash Rom并执行内部程序,存储器./EA端接低电平时,CPU只访问外部ROM,并执行片外程序存储器中的指令。

单片机基础_80C51

5. 串行I/O口 目前高档 8 位单片机均设置了全双工串行 I/O 口,用以 实现与某些终端设备进行串行通信,或者和一些特殊功能 的器件相连接的能力,甚至用多个单片机相连构成多机系 统。随着应用的拓宽,有些型号的单片机内部还包含有二 个串行I/O口。 6. 定时器/计数器

3. 控制线:共4根。

· RST(VPD:备用电源引入端,当电源发生故障,电源降到下限值时, 备用电源经此端向内部 RAM提供电压,以保护内部RAM中的数据不 丢失)——复位输入信号,高电平有效。在振荡器工作时,在RST上 作用两个机器周期以上的高电平,将器件复位。 ·/EA(Vpp:编程电压,具体电压值视芯片而定)——片外程序存储 器访问允许信号,低电平有效。/EA=1,选择片内程序存储器(80C51 为4KB,80C52为8KB) ;/EA=0,则程序存储器全部在片外而不管片 内是否有程序存储器。 使用80C31时,必须接地,使用8751编程时,施加 21V的编程电 压。 · ALE(PROG:编程脉冲)——地址锁存允许信号,输出。 在访问片外存储器或 I/O 时,用于锁存低八位地址,以实现低八 位地址与数据的隔离。即使不访问外部存储器,ALE端仍以固定的频 率输出脉冲信号(此频率是振荡器频率的1/6)。在访问外部数据存储器 时,出现一个ALE脉冲。

在单片机中,常把寄存器(如工作寄存器、特殊功能 寄存器、堆栈等)在逻辑上划分在片内 RAM 空间中,所 以可将单片机内部 RAM 看成是寄存器堆,有利于提高运 行速度。

当内部 RAM 容量不够时,还可通过串行总线或并行 总线外扩数据存储器。

4. 并行I/O口

单片机往往提供了许多功能强、使用灵活的并行输入 /输出引脚,用于检测与控制。有些I/O引脚还具有多种功 能,比如可以作为数据总线的数据线、地址总线的地址线、 控制总线的控制线等。单片机 I/O 引脚的驱动能力也逐渐 增大,甚至可以直接驱动外扩的LED显示器。

单片机80c51引脚

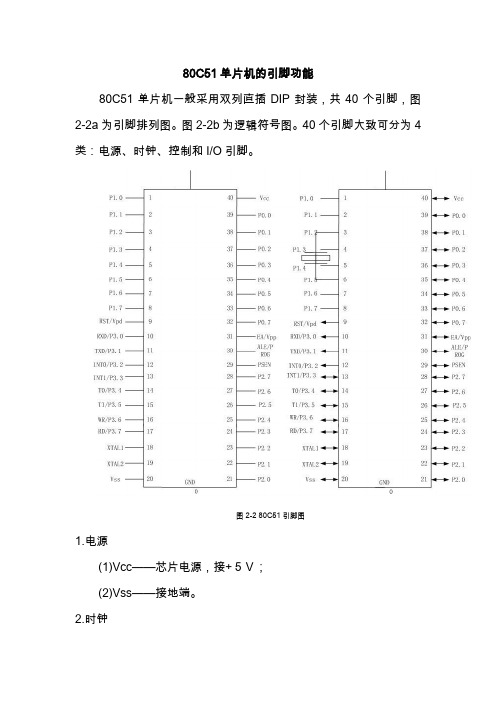

80C51单片机的引脚功能80C51单片机一般采用双列直插DIP封装,共40个引脚,图2-2a为引脚排列图。

图2-2b为逻辑符号图。

40个引脚大致可分为4类:电源、时钟、控制和I/O引脚。

图2-2 80C51引脚图1.电源(1)Vcc——芯片电源,接+5V;(2)Vss——接地端。

2.时钟XTAL1、XTAL2——晶体振荡电路反相输入端和输出端。

使用内部振荡电路时外接石英晶体。

3.控制线控制线共有4根,其中3根是复用线。

所谓复用线是指具有两种功能,正常使用时是一种功能,在某种条件下是另一种功能。

(1)ALE/PROG——地址锁存允许/片内EPROM编程脉冲。

①ALE功能:用来锁存P0口送出的低8位地址。

80C51在并行扩展外存储器(包括并行扩展I/O口)时,P0口用于分时传送低8位地址和数据信号,且均为二进制数。

那么如何区分是低8位地址还是8位数据信号呢?当ALE信号有效时,P0口传送的是低8位地址信号;ALE信号无效时,P0口传送的是8位数据信号。

在ALE信号的下降沿,锁定P0口传送的内容,即低8位地址信号。

需要指出的是,当CPU不执行访问外RAM指令(MOVX)时,ALE以时钟振荡频率1 / 6的固定频率输出,因此ALE信号也可作为外部芯片CLK时钟或其他需要。

但是,当CPU执行MOVX指令时,ALE将跳过一个ALE脉冲。

ALE端可驱动8个LSTTL门电路。

②PROG功能:片内有EPROM的芯片,在EPROM编程期间,此引脚输入编程脉冲。

(2)PSEN——外ROM读选通信号。

80C51读外ROM时,没个机器周期内PSEN两次有效输出。

PSEN可作为外ROM芯片输出允许OE的选通信号。

在读内ROM 或读外RAM时,PSEN无效。

PSEN可驱动8个LSTTL门电路。

(3) RST/Vpd——复位/备用电源。

①正常工作时,RST(Reset)端为复位信号输入端,只要在该引脚上连续保持两个机器周期以上高电平,80C51芯片即实现复位操作,复位后一切从头开始,CPU从0000H开始执行指令。

第6章 80C51单片机的系统扩展

80C51单片机的系统扩展 第6章 80C51单片机的系统扩展

6.1.2 常用程序存储器芯片

1、Flash(闪速 、 闪速)ROM 闪速

FlashROM是一种新型的电擦除式存储器,它是在EPROM工艺的基础上 增添了芯片整体电擦除和可再编程功能。它即可作数据存储器用,又可作程序 存储器用,其主要性能特点为: (1)电可擦除、可改写、数据保持时间长。 (2)可重复擦写/编程大于1万次。 (3)有些芯片具有在系统可编程ISP功能。 (4)读出时间为ns级,写入和擦除时间为ms级。 (5)低功耗、单一电源供电、价格低、可靠性高,性能比EEPROM优越。 FlashROM型号很多,常用的有29系列和28F系列。29系列有29C256 (32K×8)、29C512(64K×8)、29C010(128K×8)、29C020 (256K×8)、29040(512K×8)等,28F系列有28F512(64K×8)、 28F010(128K×8)、28F020(256K×8)、28F040(512K×8)等。

80C51单片机的系统扩展 第6章 80C51单片机的系统扩展

6.2.1 常用数据存储器芯片

静态存储器(SRAM)具有存取速度快、使用方便和价 格低等优点。但它的缺点是,一旦掉电,内部所有数据信 息都会丢失。常用的SRAM有6116(2KB×8)、6264 (8KB×8)、62128(16KB×8)、62256(32KB×8) 等芯片。常用SRAM芯片管脚和封装如图6-8所示,引脚功 能如下。 ① A0~A15:地址输入线。 ② D0~D7:双向三态数据总线,有时也用I/O0~I/O7表示。 ③CE:片选线,低电平有效。6264的26脚(CS)必须接高 电平,并且CE为低电平时才选中该芯片。 ④OE:读选通线,低电平有效。 ⑤WE:写选通线,低电平有效。 ⑥ VCC:电源线,接+5V电源。 ⑦ NC:空。 ⑧ GND:接地。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

5( 8 )

6( 6 ) 7( 5 )

CTS

DSR SGND

允许发送

DCE就绪(数据建立就绪) 信号接地

DTE←DCE

DTE←DCE

8( 1 )

20(4) 22(9) RI

DCD

DTR

载波检测

振铃指示

DTE←DCE

DTE←DCE

DTE就绪(数据终端准备就绪) DTE→DCE

2015-4-11

12

电气特性

D0 D1 D2 D3 D4 D5 D6 D7 TB8

停止位

串行接收:(置REN=1启动接收过程)

RXD 位采样脉冲 RI(中断标志) 起始

D0 D1 D2 D3 D4 D5 D6 D7 RB8

停止位

2015-4-11

29

6.2.4

80C51波特率确定与初始化步骤

波特率的确定 波特率的计算 固定波特率:

2015-4-11 8

代码和校验

发送方将所发数据块求和(或各字节异或), 产生的校验和字节附加到数据块的末尾。

接收方在接收数据时要对数据块(除校验字节 外)求和(或各字节异或),将所得的结果与 收到的“校验和”进行比较,相符则无差错, 否则就认为传送过程出现了差错。

2015-4-11

9

传输速率与传输距离

D1 D0

0 1

D2(1)

RXD

T0 T1 T2 T3 T4 T5 T6 T7

特点:传送控制复杂、速度慢,传输线少,成本低

2015-4-11 3

6.1.1

串行通信的基本概念

异步通信与同步通信

异步通信

以“0”作为起始 以“1”作为停止 各帧间隔时间任意

发送 设备

10100100 0

TXD

接收 设备

1 11100110

第6章 80C51单片机的串行口

6.1

计算机串行通信基础

6.2

80C51单片机的串行口

6.3

80C51单片机的串行口应用

2015-4-11

1

6.1 计算机串行通信基础

通信:并行通信与串行通信

并行通信

0 1 1 0 1 1 0 1 0 1 1 0 1 1 0 1

时钟 D7 0 1 1 D6 D5 : : : D1 D0

2015-4-11 18

6.2.2 80C51串行口的控制寄存器 串行口控制寄存器SCON

7 6 5 4 3 2 1 0 NhomakorabeaSCON SM0

SM1

SM2

REN

TB8

RB8

TI

RI

字节地址:98H

SM0和SM1:工作方式选择位

SM0 0 0 1 1

2015-4-11

SM1 0 1 0 1

方 式 0 1 2 3

方式1和方式3波特率与TH1初值的对应关系:

波特率/(b/s) TH1初值 SMOD 19.2 k FDH 1 9600 FDH 0 4800 FAH 0 2400 F4H 0 1200 E8H 0

2015-4-11

31

串行口初始化步骤

确定T1的工作方式(TMOD) 计算T1的初值,装载TH1、TL1 启动T1(置位TR1) 确定串行口工作方式(SCON) 串口中断设置(IE、IP)

REN:串行接收使能位,软件置1时,启动接收过程

2015-4-11 20

TB8:多机方式发送的第9位

多机方式的地址/数据帧标志。也可作为奇偶校验位。

RB8:多机方式接收的第9位

多机方式的地址/数据帧标志。也可作为奇偶校验位。

TI:发送中断标志位,要由软件清0 RI:接收中断标志位,要由软件清0

2015-4-11 21

起始位:1位 数据位:8位 停止位:1位

2015-4-11

26

串行发送:(写SBUF启动发送过程)

写入SBUF TXD TI(中断标志) 起始

D0 D1 D2 D3 D4 D5 D6 D7

停止位

串行接收:(置REN=1启动接收过程)

RXD 位采样脉冲 RI(中断标志) 起始

D0 D1 D2 D3 D4 D5 D6 D7

TXD(移位脉冲)

RXD 80C51 TXD

P1.0

Q

74LS165

CP S/L INH GND

S/L负脉冲将并行数 据装入,高电平时启 动单片机进行数据输 入。

2015-4-11

25

方式1:10位帧,用于双机通信

空 闲 起 始 位 D0 LSB 1帧共10位 数据位8位 D7 MSB 停 止 位 空 闲

说 移位寄存器

明

波特率 fosc/12 可变 可变

10位UART(8位数据) 11位UART(9位数据)

19

11位UART(9位数据) fosc/64或fosc/32

SM2:多机通信控制位

SM2=1时,接收机处于地址帧筛选状态。若RB8= 1,该地址帧信息可进入SBUF,并使RI为1,进 而在中断服务中再进行地址号比较;若RB8=0, 该帧不是地址帧,应丢掉,且保持RI=0。 SM2=0时,接收机处于地址帧筛选被禁止状态。 不论收到的RB8为0或1,均可以使收到的信息进 入SBUF,并使RI=1。此时的RB8通常为校验位。

方式0波特率= fosc/12 方式2波特率=(2SMOD/64)* fosc

可变波特率:

方式1波特率=(2SMOD/32)*(T1溢出率) 方式3波特率=(2SMOD/32)*(T1溢出率) T1 溢出率 = fosc /{12×[256 -(TH1)]}

30

2015-4-11

波特率的选择

波特率要选择标称值,由于TH1的初值是整数,为了 减小波特率计算误差,晶振频率要选为11.0592MHz。

特点

易于实现 效率不高

同步通信 (发、收时钟直接连接,效率高。板内元件间的 SPI接口)

2015-4-11 5

串行通信的传输方向

单工

发送 接收

半双工

发送

时间1

接收

接收

时间2

发送

全双工

发送 接收 发 送 接收

80C51有1个全双工串行口

2015-4-11

6

信号的调制与解调

RS-232C RS-232C

电话网

DCE DCE

DTE

调制解调器 调制 解调

DTE

DTE:数据终端设备 DCE:数据通信设备

2015-4-11

7

串行通信的错误校验

奇偶校验 发送字符时,数据位尾随1位奇偶校验位(1 或0)。奇校验时,数据中“1”的个数与校 验位“1”的个数之和应为奇数;偶校验时, 数据中“1”的个数与校验位“1”的个数之和 应为偶数。 接收字符时,对“1”的个数进行校验,若发 现不一致,则说明传输数据过程中出现了差 错。

2015-4-11

23

数据输出:

写入SBUF RXD(数据) TXD(移位脉冲) TI(中断标志) TCY

D0

D1

D2

D3

D4

D5

D6

D7

RXD 80C51 TXD

P1.0

A B CP

74LS164

CR GND

CLR用于对74LS164清0

2015-4-11

24

数据输入:

REN=1 RI=0 RXD(数据输入) D0 D1 D2 D3 D4 D5 D6 D7

TXD RXD 计 算 机 甲

TXD RXD 计 算 机 乙

无联络线方式

联络线短接(伪连接)方式

2015-4-11

15

RS-232C电平与TTL电平转换驱动电路

早期常用MC1488、MC1489

近期常用MAXM232:

片内带有自升压电路 仅需+5V电源 内含2个发送器,2个接收器

2015-4-11

RS-232C采用负逻辑电平,规定(-3~-25V)为逻辑“1”, (+3~+25V)为逻辑“0”。-3V~+3V是未定义的过渡区。 试比较:

V

+5 1 2 0.8 0 0

0 1 0 1

V

+25 +3 -3

0 1 0 1

0

t

t

1

-25 RS232电平

TTL电平

电平转换电路(如MAX232)。

2015-4-11 13

1个全双工串口:通信或接口扩展

6.2.1 80C51串行口的结构

99H

SBUF 写SBUF TH1 TL1 发送控制器 1 T1溢出率 读SBUF ÷2 0 SMOD ÷16 接收控制器

TXD 控制门 TI 去中断逻辑

≥1

RI RXD

SBUF 99H

移位寄存器

接收发送缓冲器逻辑同名、物理分开;接收双缓冲。

电源控制寄存器PCON

7 6 5 4 3 2 1 0

PCON

SMOD

字节地址:97H

SMOD:波特率倍增位。在串行口方式1、方式2、方式3 时,波特率与 SMOD 有关,当 SMOD=1 时,波特率提高一倍。 复位时,SMOD=0。

2015-4-11

22

6.2.3

80C51串行口的工作方式

方式0:同步移位寄存器,用于扩展并行口 RXD:输入或输出引脚 TXD:移位脉冲输出 接收和方式都是8位 波特率固定为:fosc/12

TXD

远程连接 (电平转换)

RXD 80C51

T1IN T1OUT MAX232A R2OUT R2IN

R1IN R1OUT GND MAX232A R2IN T2OUT T2IN GND

RXD TXD T2OUT 80C51