数字电子技术基础门电路习题解(精品)

数字电子技术基础课后答案全解

数字电子技术基础课后答案全解第3章逻辑代数及逻辑门【3-1】填空1、与模拟信号相比,数字信号的特点是它的离散性。

一个数字信号只有两种取值分别表示为0和12、布尔代数中有三种最基本运算:与、或和非,在此基础上又派生出五种基本运算,分别为与非、或非、异或、同或和与或非。

3、与运算的法则可概述为:有“0”出0,全“1”出1;类似地或运算的法则为有”1”出”1”,全”0”出”0”4、摩根定理表示为:AB=AB;AB=AB。

5、函数表达式Y=ABCD,则其对偶式为Y=(AB)CD。

6、根据反演规则,若Y=ABCDC,则Y(ABCD)C7、指出下列各式中哪些是四变量ABCD的最小项和最大项。

在最小项后的()里填入mi,在最大项后的()里填入Mi,其它填某(i为最小项或最大项的序号)。

(1)A+B+D(某);(2)ABCD(m7);(3)ABC(某)(4)AB(C+D)(某);(5)ABCD(M9);(6)A+B+CD(某);8、函数式F=AB+BC+CD写成最小项之和的形式结果应为成最大项之积的形式结果应为m(3,6,7,11,12,13,14,15),写M(0,1,2,4,5,8,9,10)9、对逻辑运算判断下述说法是否正确,正确者在其后()内打对号,反之打某。

(1)若某+Y=某+Z,则Y=Z;(某)(2)若某Y=某Z,则Y=Z;(某)(3)若某Y=某Z,则Y=Z;(√)【3-2】用代数法化简下列各式(1)F1=ABCAB1(2)F2=ABCDABDACDAD(3)F3ACABCACDCD(4)F4ABC(ABC)(ABC)ACD【3-3】用卡诺图化简下列各式ABC(1)F1BCABABC(2)F2ABBCBCABCAB(3)F3ACACBCBC(4)F4ABCABDACDCDABCACDABACBCAD第1页/共46页或ABACBC(5)F5ABCACABD(6)F6ABCDABCADABCABACBDABCCD(7)F7ACABBCDBDABDABCD(8)F8ACACBDBDABDBDABCDABCDABCDABCD(9)F9A(CD)BCDACDABCDCDCD(10)F10=F10ACABBCDBECDECABACBDEC【3-4】用卡诺图化简下列各式(1)P1(A,B,C)=m(0,1,2,5,6,7)ABACBCm(0,1,2,3,4,6,7,8,9,10,11,14)ACADBCDABBC ADBD(2)P2(A,B,C,D)=(3)P3(A,B,C,D)=m(0,1,,4,6,8,9,10,12,13,14,15)(4)P4(A,B,C,D)=M1M7ABCBCD【3-5】用卡诺图化简下列带有约束条件的逻辑函数(1)P1A,B,C,Dm(3,6,8,9,11,12)d(0,1,2,13,14,15)ACBDBCD(或ACD)(2)P2(A,B,C,D)=m(0,2,3,4,5,6,11,12)(8,9,10,13,14,15)dBCBCD(3)P3=ACDABCDABCDADACDBCD(或ABD)AB+AC=0(4)P4=ABCDABCDAB(ABCD为互相排斥的一组变量,即在任何情况下它们之中不可能两个同时为1)【3-6】已知:Y1=ABACBDY2=ABCDACDBCDBC用卡诺图分别求出Y1Y2,Y1Y2,Y1Y2。

《数字电子技术基本教程第》阎石习题详解

51Ω 1.5KΩ 100KΩ ∞

0

0

0 不定

5

5

5 不定

图 2.44 习题 2-3 电路图

图 2.45

3.16 答案:

RP(m a x)

VCC VOH nIOH IL

5 3.6 2 0.1103 3 20106 5.4K

RP(m in)

VOH mI IH

10106

5 3.5 3 1106

6

41.7K

RP(m in)

VDD VOL IOL(max) mI IL

5 0.3 4103 1106

6

1.2K

图 2.53 习题 2-17 图

3.13 答案:

图 2.44 习题 2-3 电路图

vI1/V 悬空 接地 51Ω 3.6 50KΩ 0.2 vI2/V 1.4V 0V 0V 1.4V 1.4V 0.2V

2.7 答案:

0

1

1

0

0

1

高阻态

0 0

1

2.8 答案: 1

1 0

0

1

0 0

1

2.9 答案:

图 2.48 习题 2-9 图

2.12 答案:

F A B AB AB 1 B 1 B B

最多可以接10个同样的门电路

图 2.55 习题 2-19 图

3.20 答案:

IOH(max) 0.4mA

IIH(max) 20 A

IOL(max) 8mA IIH(max) 0.4mA

2nIIH(max) IOH(max)

n

IOH (max) 2I IH(max)

数字电子技术基础试题及答案

数字电子技术基础试题及答案一、单项选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑门是()。

A. 与门B. 或门C. 非门D. 异或门答案:C2. 下列哪个不是TTL逻辑门的类型?()A. 与非门B. 或非门C. 同或门D. 非门答案:C3. 一个D触发器的初始状态为1,当输入D=0时,时钟脉冲上升沿到达后,输出Q的状态为()。

A. 0B. 1C. 不确定D. 无变化答案:A4. 以下哪个逻辑表达式是正确的?()A. A+A=AB. A·A=AC. A+A=0D. A·A=0答案:B5. 一个4位二进制计数器,从0000开始计数,当计数到1111时,下一个状态是()。

A. 0000B. 1000C. 10000D. 0111答案:A6. 在数字电路中,若要实现一个逻辑函数,下列哪种方法最为经济?()A. 使用与非门B. 使用或非门C. 使用与门D. 使用或门答案:A7. 一个三态输出门,当控制端为高电平时,输出状态为()。

A. 高阻态B. 低电平C. 高电平D. 低阻态答案:C8. 以下哪个是BCD码的特点?()A. 每个十进制数字对应一个唯一的二进制代码B. 每个二进制数字对应一个唯一的十进制数字C. 每个二进制数字对应一个唯一的十六进制数字D. 每个十进制数字对应多个二进制代码答案:A9. 在数字电路中,一个反相器的逻辑功能是()。

A. 与B. 或C. 非D. 异或答案:C10. 一个JK触发器在时钟脉冲上升沿到达时,如果J=1,K=0,则触发器的状态()。

A. 保持不变B. 翻转C. 置0D. 置1答案:D二、填空题(每题2分,共20分)1. 一个2输入的与门,当两个输入都为1时,输出为______。

答案:12. 在数字电路中,一个D触发器的D端输入为0,时钟脉冲上升沿到达后,输出Q的状态为______。

答案:03. 一个4位二进制计数器,如果初始状态为0101,下一个状态为______。

数字电子技术基础习题及答案

数字电子技术基础习题及答案..(总33页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--数字电子技术基础试题一、填空题 : (每空1分,共10分)1. 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

2图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>Ω)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC34.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2 A、并行A/D转换器 B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

4图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

《数字电子技术基础》课后习题答案

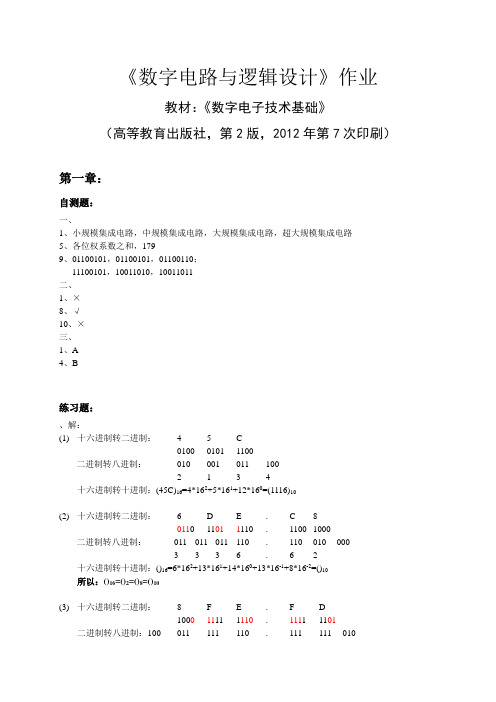

《数字电路与逻辑设计》作业教材:《数字电子技术基础》(高等教育出版社,第2版,2012年第7次印刷)第一章:自测题:一、1、小规模集成电路,中规模集成电路,大规模集成电路,超大规模集成电路5、各位权系数之和,1799、01100101,01100101,01100110;11100101,10011010,10011011二、1、×8、√10、×三、1、A4、B练习题:、解:(1) 十六进制转二进制: 4 5 C0100 0101 1100二进制转八进制:010 001 011 1002 13 4十六进制转十进制:(45C)16=4*162+5*161+12*160=(1116)10(2) 十六进制转二进制: 6 D E . C 80110 1101 1110 . 1100 1000 二进制转八进制:011 011 011 110 . 110 010 0003 3 3 6 . 6 2十六进制转十进制:()16=6*162+13*161+14*160+13*16-1+8*16-2=()10所以:()16=()2=()8=()10(3) 十六进制转二进制:8 F E . F D1000 1111 1110. 1111 1101二进制转八进制:100 011 111 110 . 111 111 0104 3 7 6 . 7 7 2十六进制转十进制:(8FE.FD)16=8*162+15*161+14*160+15*16-1+13*16-2=(2302.98828125)10 (4) 十六进制转二进制:7 9 E . F D0111 1001 1110 . 1111 1101二进制转八进制:011 110 011 110 . 111 111 0103 6 3 6 . 7 7 2十六进制转十进制:(79E.FD)16=7*162+9*161+14*160+15*16-1+13*16-2=(1950. 98828125)10 所以:()16.11111101)2=(363)8=(1950.98828125)10、解:(74)10 =(0111 0100)8421BCD=(1010 0111)余3BCD(45.36)10 =(0100 0101.0011 0110)8421BCD=(0111 1000.0110 1001 )余3BCD(136.45)10 =(0001 0011 0110.0100 0101)8421BCD=(0100 0110 1001.0111 1000 )余3BCD (374.51)10 =(0011 0111 0100.0101 0001)8421BCD=(0110 1010 0111.1000 0100)余3BCD、解(1)(+35)=(0 100011)原= (0 100011)补(2)(+56 )=(0 111000)原= (0 111000)补(3)(-26)=(1 11010)原= (1 11101)补(4)(-67)=(1 1000011)原= (1 1000110)补第二章:自测题:一、1、与运算、或运算、非运算3、代入规则、反演规则、对偶规则二、2、×4、×三、1、B3、D5、C练习题:2.2:(4)解:(8)解:2.3:(2)证明:左边=右式所以等式成立(4)证明:左边=右边=左边=右边,所以等式成立(1)(3)2.6:(1)2.7:(1)卡诺图如下:BCA00 01 11 100 1 11 1 1 1所以,2.8:(2)画卡诺图如下:BC A 0001 11 100 1 1 0 11 1 1 1 12.9:如下:CDAB00 01 11 1000 1 1 1 101 1 111 ×××10 1 ××2.10:(3)解:化简最小项式:最大项式:2.13:(3)技能题:2.16 解:设三种不同火灾探测器分别为A、B、C,有信号时值为1,无信号时为0,根据题意,画卡诺图如下:BC00 01 11 10A0 0 0 1 01 0 1 1 1第三章:自测题:一、1、饱和,截止7、接高电平,和有用输入端并接,悬空;二、1、√8、√;三、1、A4、D练习题:、解:(a)Ω,开门电阻3kΩ,R>R on,相当于接入高电平1,所以(e) 因为接地电阻510ΩkΩ,R<R off,相当于接入高电平0,所以、、解:(a)(c)(f)、解: (a)、解:输出高电平时,带负载的个数2020400===IH OH OH I I N G 可带20个同类反相器输出低电平时,带负载的个数78.1745.08===IL OL OL I I NG反相器可带17个同类反相器EN=1时,EN=0时,根据题意,设A为具有否决权的股东,其余两位股东为B、C,画卡诺图如下,BC00 01 11 10A0 0 0 0 01 0 1 1 1则表达结果Y的表达式为:逻辑电路如下:技能题::解:根据题意,A、B、C、D变量的卡诺图如下:CD00 01 11 10AB00 0 0 0 001 0 0 0 0 11 0 1 1 1 10 0 0 0 0电路图如下:第四章:自测题:一、2、输入信号,优先级别最高的输入信号7、用以比较两组二进制数的大小或相等的电路,A>B 二、 3、√ 4、√ 三、 5、A 7、C练习题:4.1;解:(a),所以电路为与门。

《数字电子技术基础》课后习题及参考答案

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)=177(2)=170(3)=241(4)=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=()2(3)(B1)16=(1011 0001)2(4)(AF)16=()2【题1-5】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)()2=(2)()2=(3)()2=【题1-6】将下列十进制数转换为二进制数。

(1);(2);(3);(4)解:(1)=()2(2)=()2(3)=()2(4)=()2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

(1)01101100;(2);(3);(4)解:(1)01101100是正数,所以其反码、补码与原码相同,为01101100(2)反码为,补码为(3)反码为,补码为(4)反码为,补码为【题1-8】将下列自然二进制码转换成格雷码。

000;001;010;011;100;101;110;111解:格雷码:000、001、011、010、110、111、101、100【题1-9】将下列十进制数转换成BCD码。

《数字电子技术》部分习题解答

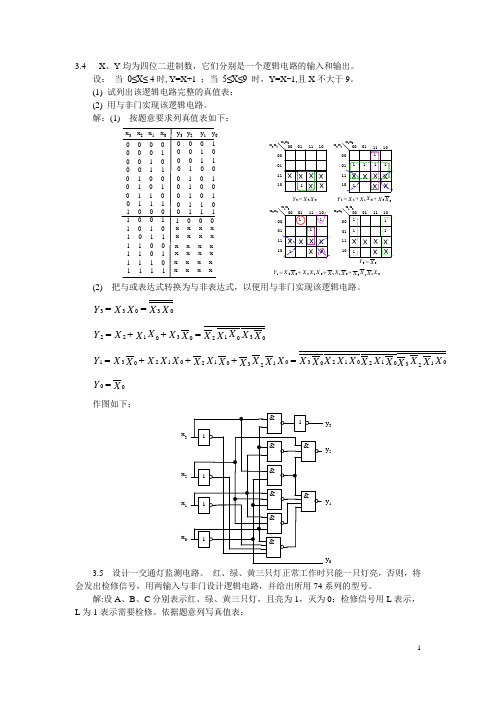

3.4 X 、Y 均为四位二进制数,它们分别是一个逻辑电路的输入和输出。

设: 当 0≤X≤ 4时, Y=X+1 ;当 5≤X≤9 时,Y=X -1,且X 不大于9。

(1) 试列出该逻辑电路完整的真值表; (2) 用与非门实现该逻辑电路。

解:(1) 按题意要求列真值表如下:0 0 0 0x 3x 2x 1x 0y 3y 2y 1y 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 10 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 0x x x x x x x x x x x x x x x x x x x x x x x xX X Y 033=x 3X X X X X Y 031022++=x 3X XX X X X X X X X X X Y 0132121231+++=x 3X Y 00=01001110000111101x 3x 2x 1x 01111(2) 把与或表达式转换为与非表达式,以便用与非门实现该逻辑电路。

X X X X Y 03033==X X X X X X X X X X Y 0310*******=++=X X X X X X X X X X X X X X X X X X X X X X X X Y 0132012012030132012012031=+++= X Y 00=作图如下:x 3x 2x 1x 0y 3y 2y 1y 03.5 设计一交通灯监测电路。

红、绿、黄三只灯正常工作时只能一只灯亮,否则,将会发出检修信号,用两输入与非门设计逻辑电路,并给出所用74系列的型号。

解:设A 、B 、C 分别表示红、绿、黄三只灯,且亮为1,灭为0;检修信号用L 表示,L 为1表示需要检修。

课后习题答案_第3章_门电路

数字电子技术基础第三章习题答案3-1 如图3-63a~d所示4个TTL门电路,A、B端输入的波形如图e所示,试分别画出F1、F2、F3和F4的波形图。

略3-2 电路如图3-64a所示,输入A、B的电压波形如图3-64b所示,试画出各个门电路输出端的电压波形。

略3-3 在图3-7所示的正逻辑与门和图3-8所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明F和A、B之间是什么逻辑关系。

答:(1)图3-7负逻辑真值表F与A、B之间相当于正逻辑的“或”操作。

(2)图3-8负逻辑真值表F与A、B之间相当于正逻辑的“与”操作。

3-4 试说明能否将与非门、或非门、异或门当做反相器使用?如果可以,各输入端应如何连接?答:三种门经过处理以后均可以实现反相器功能。

(1)与非门: 将多余输入端接至高电平或与另一端并联;(2)或非门:将多余输入端接至低电平或与另一端并联;(3) 异或门:将另一个输入端接高电平。

3-5 为了实现图3-65所示的各TTL 门电路输出端所示的逻辑关系,请合理地将多余的输入端进行处理。

答:a )多余输入端可以悬空,但建议接高电平或与另两个输入端的一端相连;b)多余输入端接低电平或与另两个输入端的一端相连;c) 未用与门的两个输入端至少一端接低电平,另一端可以悬空、接高电平或接低电平;d )未用或门的两个输入端悬空或都接高电平。

3-6 如要实现图3-66所示各TTL 门电路输出端所示的逻辑关系,请分析电路输入端的连接是否正确?若不正确,请予以改正。

答:a )不正确。

输入电阻过小,相当于接低电平,因此将Ω50提高到至少2K Ω。

b) 不正确。

第三脚V CC 应该接低电平。

c )不正确。

万用表一般内阻大于2K Ω,从而使输出结果0。

因此多余输入端应接低电平,万用表只能测量A 或B 的输入电压。

3-7 (修改原题,图中横向电阻改为6k Ω,纵向电阻改为3.5 k Ω,β=30改为β=80) 为了提高TTL 与非门的带负载能力,可在其输出端接一个NPN 晶体管,组成如图3-67所示的开关电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

+5V

3kΩ

uI

4.7kΩ

2kΩ uO

β =50

18kΩ

−8V

(b)

uI 5.1kΩi1

iB

5V 10V

20kΩ

i2

0.7V

(b1)

2.2 为什么说TTL与非门输入端在以下三种接法时,在逻辑上都属于 输入为0? (1)输入端接地; (2)输入端接低于0.8V的电源; (3)输入端接同类与非门的输出低电平0.3V。

20kΩ

uI 5.1kΩi1

−10V

(a)

iB

uI悬空,假设T截止,等效图(a1)中将左面回路断开 uB=-10V 假设成立,uO=10V

5V 10V

20kΩ

i2

0.7V

(a1)

2.1解续

(b)uI=0V,假设T截止, uB=(0-(-10))*20/(20+5.1)-10= -2V 假设成立,uO=10V

解(1)

N OL

=

IOL I IL

=

13 1

= 13

(2)

UNL=UOFF-UOL=0.8-0.35=0.45V UNH=UOH-UON=3-1.5=1.5V

R1 3kΩ

T1 A B

R2 750Ω

R4 100Ω

+UCC (+5V)

T3 T2

R3 360Ω

R5 3kΩ

T4 F

T5

2.6 电路如图2.45所示,已知OC门的输出低电平UOL=0.3V;TTL与非

(b) R>RON,电路输出为低电平 (c) R>RON,电路输出为低电平 (d) R=10kΩ>RON,电路输出为低电平 (e) 三态门EN=0,电路输出为高阻态

(f) R=10kΩ>RON,电路输出为低电平

2.5 图2.44所示为TTL与非门。设其输出低电平UOL≤0.35V,输出高电 平UOH≥3V,允许最大灌入电流IOL=13mA,关门电平UOFF=0.8V,开门电 平UON=1.5V。 (1)试求该TTL与非门的扇出系数No; (2)试求该TTL与非门的低电平噪声容限UNL和高电平噪声容限UNH。

解(a)uI=0V,假设T截止, uB=(0-(-10))*20/(20+5.1)-10= -2V 假设成立,uO=10V

uI 5.1kΩ

+10V 2kΩ

uO β=30

uI=5V,假设T导通,等效图(a1) i1=(5-0.7) /5.1=0.84mA, i2=(10+0.7) /20=0.535mA,iB=i1-i2=0.305mA iBSC=(10-0.3)/(2*30)=0.162mA iB> iBSC,T饱和导通, uO=0.3V

R2

(2)UA1=UA2=3.6V;

R1

UC

&

UF

(3)R1=∞ ,UA1=UA2=3.6V;

A1

&

(4)R2=∞ ,UA1=UA2=3.6V;

A2

UB

R3

(5)R3=∞ ,UA1=UA2=3.6V。

解(1)UB=3.6V, UC = 5 + RC (0.3 / R3 + 4×10−5 ) V ,UF=0.3V (2) UB=0.3V, T截止,UC=3.6V,UF=0.3V (3) UB=0.3V, T截止,UC=3.6V,UF=0.3V (4) UB=0.3V, T截止,UC=3.6V,UF=0.3V (5) UB=0.3V, T截止,UC=3.6V,UF=0.3V

第2章 逻辑门电路习题

课件主编:徐 梁 习题解

数

第1题

第6题

字 电

第2题

第7题

子 技

第3题

第8题

术

基

第4题

第9题

础

第5题

第10题

开关特性 TTL门 OC门 综合 MOS

作业 ★A组 ★B组

★★

2.1 在图2.42所示各电路中,当输入电压u1分别为0V、+5V、悬空时, 试计算输出电压uO的数值,并指出三极管工作状态。假设三极管导通时 的UBE=0.7V。

uI=5V,假设T导通,等效图(a1) i1=(5-0.7) /5.1=0.84mA, i2=(10+0.7) /20=0.535mA,iB=i1-i2=0.305mA iBSC=(10-0.3)/(2*30)=0.162mA iB> iBSC,T饱和导通, uO=0.3V

uI悬空,假设T截止,等效图(a1)中将左面回路断 开 uB=-10V 假设成立,uO=10V

解:TTL输入标准值 UIL=0.8V (1)uI=0<UIL,所以为逻辑0 (2)uI<0.8V=UIL,所以为逻辑0 (3)uI<0.3V<0.8V=UIL,所以为逻辑0

2.3 为什么说TTL与非门输入端在以下三种接法时,在逻辑上都属于 输入为1? (1)输入端悬空; (2)输入端接高于2V的电源: (3)输入端接同类与非门的输出高电平3.6V。

2.7 在图2.25所示电路中,已知OC门在输出低电平时允许的最大负载

电流IOL=12mA,在输出高电平时的漏电流IOH=200uA,与非门的高电平输 入电流IIH=50uA,低电平输入电流IIL=1.4mA,UCC=5V,RC=1kQ。 (1)试问OC门的输出高电平UOH为多少? (2)为保证OC门的输出低电平UOL不大于0.35V,试问最多可接几个与非 门?

门的内部电路如图2.7所示,其输出低电平UOL=0.3V,输出高电平

UOH=3.6V,Байду номын сангаас电平输入电流IIH=40μA,低电平输入电流IIL=1.5mA;三极

管导通时,UBE=0.7V,饱和管压降UCES=0.3V,UCC=5V。试分别求出在

下列情况下的UB、UC和UF值。

+UCC

(1)UA1=0.3V,UA2=3.6V:

解:TTL输入标准值 UIH=2V (1)以基本TTL与非门为例,当输入端悬空时,T1和射极电流 iE1=0,集电极正偏,T2,T5饱和导通,相当于输入高电平情况,即 等效逻辑1 (2)uI>2V=UIH,所以为逻辑1 (3)uI>3.6V>2V=UIH,所以为逻辑1

2.4 指出图2.43中各门电路的输出是什么状态(高电平、低电平或高阻

(3)为保证OC门的输出高电平UOH不低于3V,试问可接与非门的输入端

态)。假定它们都是T1000系列的TTL门电路。UIH

10kΩ

+UCC UIH

&

Y1

UIL

≥1

Y2

5.1kΩ

悬空

&

Y3

UIL 10kΩ

(a)

≥1

Y4

(d)

(b)

(c)

+UCC UIL

EN=0

&

Y5

(e)

5.1kΩ

+UCC

=1 Y6

UIL

(f)

解:TTL电路的开门电阻RON=2.5kΩ (a) 输入悬空相当于高电平,电路输出为低电平