Verilog HDL编程举例

数字电路应用之Verilog HDL语言常用经典程序例题(Quartus II软件)

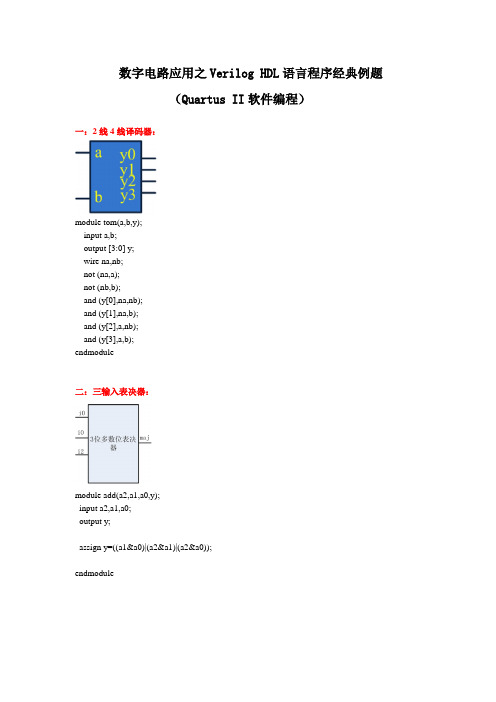

数字电路应用之Verilog HDL语言程序经典例题(Quartus II软件编程)一:2线4线译码器:module tom(a,b,y);input a,b;output [3:0] y;wire na,nb;not (na,a);not (nb,b);and (y[0],na,nb);and (y[1],na,b);and (y[2],a,nb);and (y[3],a,b);endmodule二:三输入表决器:module add(a2,a1,a0,y);input a2,a1,a0;output y;assign y=((a1&a0)|(a2&a1)|(a2&a0));endmodule三:3线8线译码器:module fulladd(a2,a1,a0,y);input a2,a1,a0;output [7:0] y;assign y[0]= ~( ~a2 & ~a1 & ~a0); assign y[1]= ~( ~a2 & ~a1 & a0); assign y[2]= ~( ~a2 & a1 & ~a0); assign y[3]= ~( ~a2 & a1 & a0); assign y[4]= ~( a2 & ~a1 & ~a0); assign y[5]= ~( a2 & ~a1 & a0); assign y[6]= ~( a2 & a1 & ~a0); assign y[7]= ~( a2 & a1 & a0);endmodule四:BIN2BCD码制转换:module fulladd(y,d,e);input [6:0] y;output [3:0] d,e;assign d=y/10;assign e=y%10;endmodule五:4位比较器:module tom(y,x,d);input [3:0] y,x;output [2:0] d;assign d[2]=(x>y)?1:0;assign d[1]=(x==y)?1:0;assign d[0]=(x<y)?1:0;endmodule六:四位全加器:法一:(调用程序法)module fulladd4(sum,c_in,c_out,a,b); output [3:0] sum;output c_out;input [3:0] a,b;input c_in;wire c1,c2,c3;fulladd fa0(sum[0],c1,a[0],b[0],c_in); fulladd fa1(sum[1],c2,a[1],b[1],c1); fulladd fa2(sum[2],c3,a[2],b[2],c2); fulladd fa3(sum[3],c_out,a[3],b[3],c3); endmodule//程序调用module fulladd(sum, c_out, a, b, c_in); output sum, c_out;input a, b, c_in;wire s1, c1, c2;xor (s1, a, b);and (c1, a, b);xor (sum, s1, c_in);and (c2, s1, c_in);xor (c_out, c2, c1);endmodule法二:(通用法)module fulladd4(A,B,Cin,SUM,Cout); input [3:0] A,B;input Cin;output [3:0] SUM;output Cout;assign {Cout,SUM}=A+B+Cin; endmodule七:七段显示译码器:法一:module bbc(a,d,g);input [3:0] a;output [6:0] d;output [3:0] g;reg [6:0] d;assign g=4'b0001;always @(a)begincase(a)4'b0000 :d=7'b100_0000;4'b0001 :d=7'b111_1001;4'b0010 :d=7'b010_0100;4'b0011 :d=7'b011_0000;4'b0100 :d=7'b001_1001;4'b0101 :d=7'b001_0010;4'b0110 :d=7'b000_0010;4'b0111 :d=7'b111_1000;4'b1000 :d=7'b000_0000;4'b1001 :d=7'b001_0000;default :d=7'b000_0000;endcaseendendmodule法二:module bbc(a,d,g);input [3:0] a;output [6:0] d;output [3:0] g;reg [6:0] d;assign g=4'b0001;always @(a)beginif (a==4'b0000) d=7'b100_0000;else if (a==4'b0001) d=7'b111_1001;else if (a==4'b0010) d=7'b010_0100;else if (a==4'b0011) d=7'b011_0000;else if (a==4'b0100) d=7'b001_1001;else if (a==4'b0101) d=7'b001_0010;else if (a==4'b0110) d=7'b000_0010;else if (a==4'b0111) d=7'b111_1000;else if (a==4'b1000) d=7'b000_0000;else if (a==4'b1001) d=7'b001_0000;else d=7'b000_0000; endendmodule八:8—3优先编码器:法一:module qq (y,d,g);input [7:0] y;output [2:0] d;output [3:0] g;reg [2:0] d;assign g=4'b0001;always @ ybeginif (y[7]==1) d=3'b111;else if (y[6]==1) d=3'b110;else if (y[5]==1) d=3'b101;else if (y[4]==1) d=3'b100;else if (y[3]==1) d=3'b011;else if (y[2]==1) d=3'b010;else if (y[1]==1) d=3'b001;else if (y[0]==1) d=3'b000;endendmodule法二:module encoder(none_on,outcode,a, b, c, d, e, f, g, h); output[2:0] outcode;output none_on;input a, b, c, d, e, f, g, h;reg[3:0] outtemp;assign {none_on, outcode} = outtemp;always @(a or b or c or d or e or f or g or h)begincasex ({a, b, c, d, e, f, g, h})8'B????_???1 : outtemp=4'b0_111;8'B????_??10 : outtemp=4'b0_110;8'B????_?100 : outtemp=4'b0_101;8'B????_1000 : outtemp=4'b0_100;8'B???1_0000 : outtemp=4'b0_011;8'B??10_0000 : outtemp=4'b0_010;8'B?100_0000 : outtemp=4'b0_001;8'B1000_0000 : outtemp=4'b0_000;8'B0000_0000 : outtemp=4'b1_000;endcaseendendmodule九:计数器:module bbc(clk,set,reset,d,y);input set,reset,clk;input [3:0] d;output [7:0] y;reg [7:0] y;always@(posedge clk or negedge reset or posedge set) if(~reset) y<=8'b0;else if (set) y[3:0]<=d[3:0];else y<=y+1'b1;endmodule十:移位寄存器:module asd (clk,set,reset,d,y,cin);input clk,set,reset,cin;input [3:0] d;output [7:0] y;reg [7:0] y;always@(posedge clk)beginif(~reset) y=0;else if(set)beginy[7:4]=y[3:0] ;y[3:0]=d[3:0];endelsebeginy=y<<1;y[0]=cin;endendendmodule十一:4位乘法:法一:module bbc(y,a,b);input [3:0] a;input [3:0] b;output [7:0] y;reg [7:0] y;reg[7:0] temp_a;reg[3:0] temp_b;integer i;always @(a or b)beginy=0;temp_a=a;temp_b=b;beginfor(i=0;i<=3;i=i+1)beginif(temp_b[0]) y=y+temp_a;temp_a=temp_a<<1;temp_b=temp_b>>1;endendendendmodule法二:module qq(outcome,a,b);output [8:1] outcome;input [4:1] a,b;reg [8:1] outcome;integer i;always@(a or b)beginoutcome=0;for(i=1;i<=4;i=i+1)if (b[1]) outcome=outcome + (a<<(i-1)); endendmodule十二:数码管跑马灯:module asd(cr,clk,a,b,c,d,e,f,g);input cr,clk;output a,b,c,d,e,f,g;reg a,b,c,d,e,f,g;integer i=0;always @ (posedge clk or negedge cr)beginif(~cr)begin{a,b,c,d,e,f,g}=7'b111_1111;i=0;endelse if(clk)begini=i+1;if(i==1) {a,b,c,d,e,f,g}=7'b011_1111;if(i==2) {a,b,c,d,e,f,g}=7'b101_1111;if(i==3) {a,b,c,d,e,f,g}=7'b110_1111;if(i==4) {a,b,c,d,e,f,g}=7'b111_0111;if(i==5) {a,b,c,d,e,f,g}=7'b111_1011;if(i==6) {a,b,c,d,e,f,g}=7'b111_1101;if(i==7) {a,b,c,d,e,f,g}=7'b111_1110;if(i==8) {a,b,c,d,e,f,g}=7'b000_0000;if(i==9)begin{a,b,c,d,e,f,g}=7'b111_1111;i=0;endendendendmodule十三:LED跑马灯:module add(cr,clk,y);input cr,clk;output [7:0] y;reg [7:0] y;integer i;always@(posedge clk or negedge cr) beginif(~cr)beginy=0;i=-1;endelse if (clk)begini=i+1;y=0;y[i]=1;beginif(i==7)i=-1;endendendendmodule。

veriloghdl程序大全

1.简单门电路的设计二输入与非门module nand_2(y,a,b);output y;input a,b;nand(y,a,b);endmodule二输入异或门module nand_2(y,a,b);output y;input a,b;reg y;always @(a,b)begincase({a,b})2’b00:y=1;2’b01:y=1;2’b10:y=1;2’b11:y=0;default:y=’bx;endcaseendendmodule二输入三态门module eda_santai(dout,din,en); output dout;input din,en;reg dout;alwaysif (en) dout<=din;else dout<=’bz;endmodule3-8译码器的设计module yimaqi(S1,S2,S3,A,Y); input S1;wire S1;input S2;wire S2;input S3;wire S3;input [2:0]A;wire [2:0]A;output[7:0]Y;reg [7:0]Y;reg s;always@(S,S1,S2,S3)begins<=S2|S3;Y <=8'b1111_1111;else if(S)Y <=8'b1111_1111;elsecase(A)3'b000:Y<=11111110;3'b001:Y<=11111101;3'b010:Y<=11111011;3'b011:Y<=11110111;3'b100:Y<=11101111;3'b101:Y<=11011111;3'b110:Y<=10111111;3'b111:Y<=01111111;endcaseendendmodule2.8-3编码器的设计module banjiaqi(a,b,count,sum);input a;wire a;input b;wire b;output count;wire count;output sum;wire sum;assign {count,sum}=a+b;endmodule4. D触发器的设计module Dchufaqi ( Q ,CLK ,RESET ,SET ,D ,Qn ); input CLK ;wire CLK ;input RESET ;wire RESET ;input SET ;wire SET ;input D ;wire D ;output Q ;reg Q ;output Qn ;wire Qn ;assign Qn = ~Q ;always @ ( posedge CLK or negedge SET or negedge RESET ) beginif ( !RESET)Q <= 0 ;else if ( ! SET)Q <= 1;else Q <= D;endendmodule5. 1位半加法器的设计module banjiafaqi(a,b,sum,count);input a;wire a;input b;wire b;output sum;wire sum;output count;wire count;assign {count,sum}=a+b;endmodule6. 4位计数器的设计module sihisjishuqi(CLK,RESET,out);input CLK;wire CLK;input RESET;wire RESET;output[3:0] out;reg[3:0] out;always @ ( posedge CLK or negedge RESET )beginif(!RESET)out<=4'b0000;elsebeginout<=out+1;if(out==4'b1010)out<=4'b0000;endendendmodule7.分频时序逻辑电路的设计module eda_fp_even(clk_out,clk_in,rst); input clk_in;input rst;wire rst;output clk_out;reg clk_out;reg [1:0]cnt;parameter N=6;always @(posedge clk_in or negedge rst) beginif(!rst)beginclk_out<=0;cnt<=0;endelsebegincnt<=cnt+1;if(cnt==N/2-1)beginclk_out=!clk_out;cnt<=0;endendendendmodule8.7段显示译码器的设计module eda_scan_seven(clk,dig,y,rst); input clk;wire clk;input rst;wire rst;output[7:0] dig;wire[7:0] dig;output [7:0]y;wire [7:0]y;reg clkout;reg [19:0]cnt;reg [2:0]wei;reg [3:0]duan;reg [6:0]Y_r;reg [7:0]dig_r;assign y = {1'b1,(~Y_r[6:0])};assign dig =~dig_r;parameter period= 1000000;always@(posedge clk or negedge rst) beginif(!rst)cnt<=0;else begincnt<=cnt+1;if(cnt==(period>>1)-1)clkout<=#1 1'b1;else if(cnt==period-1)beginclkout<=#1 1'b0;cnt<=#1 1'b0;endendendalways@(posedge clkout or negedge rst ) beginif(!rst)wei<=0;elsewei<=wei+1;endalways @(wei) //数码管选择begincase ( wei )3'b000 :begindig_r <= 8'b0000_0001;duan <= 1;end3'b001 :begindig_r <= 8'b0000_0010;duan<= 3;end3'b010 :begindig_r <= 8'b0000_0100;duan<= 5;end3'b011 :begindig_r <= 8'b0000_1000;duan <= 7;end3'b100 :begindig_r <= 8'b0001_0000;duan<= 9;end3'b101 :begindig_r <= 8'b0010_0000;duan<= 11;end3'b110 :begindig_r <= 8'b0100_0000;duan <= 13;end3'b111 :begindig_r <= 8'b1000_0000;duan<= 15;endendcaseendalways @ ( duan ) //译码begincase ( duan )0: Y_r = 7'b0111111; // 01: Y_r = 7'b0000110; // 12: Y_r = 7'b1011011; // 23: Y_r = 7'b1001111; // 34: Y_r = 7'b1100110; // 45: Y_r = 7'b1101101; // 56: Y_r = 7'b1111101; // 67: Y_r = 7'b0100111; // 78: Y_r = 7'b1111111; // 89: Y_r = 7'b1100111; // 910: Y_r = 7'b1110111; // A11: Y_r = 7'b1111100; // b12: Y_r = 7'b0111001; // c13: Y_r = 7'b1011110; // d14: Y_r = 7'b1111001; // E15: Y_r = 7'b1110001; // Fdefault: Y_r = 7'b0000000;endcaseendendmodule9.数据选择器的设计module eda_8xuanyi (A,D0,D1,D2,D3,D4,D5,D6,D7,G,Y); input D0,D1,D2,D3,D4,D5,D6,D7,G;input [2:0]A;wire [2:0]A;output Y;reg Y;always @(A, G)beginif (G==0)Y<=0;elsecase(A)3'b000:Y=D0;3'b001:Y=D1;3'b010:Y=D2;3'b011:Y=D3;3'b100:Y=D4;3'b101:Y=D5;3'b110:Y=D6;3'b111:Y=D7;endcaseendendmodule10.数据锁存器的设计module e da_suocunqi(q,d,oen,g); output[7:0] q;//数据输出端input[7:0] d;//数据输入端input oen,g;//三态控制端reg[7:0] q;always @(*)beginif (oen)beginq<="z";endelsebeginif(g)q<=d;elseq<=q;endendendmodule11.数据寄存器的设计module eda_jicunqi(r,clk,d,y); input r,clk;input [7:0]d;wire [7:0]d;output [7:0]y;reg [7:0]y;always @ (posedge clk or negedge r) beginif(!r)y<=8'b00000000;elsey<=d;endendmodule12.顺序脉冲发生器的设计module eda_shunxu(clk,clr,q);input clk,clr;output [7:0]q;reg [7:0]q;always @ ( posedge clk or posedge clr ) beginif ( clr==1)beginq<=8'b00000000; //赋初值endelsebeginif(q==0)q<=8'b00000001;elseq<=q<<1; //给初值进行移位endendendmodule13.1位全加法器的设计module quanjiaqi(a,b,sum,count,cin); input a;wire a;input b;wire b;input cin;wire cin;output sum;wire sum;output count;wire count;assign{sum,count}=a+b+cin; endmodule15.键控Led灯的设计module eda_led(led,key);input key;output led;reg led_out;assign led<=led_out;always@(key)beginif(key)led_out<=1;else if(!key)led_out<=0;endendmodule16.双向移位寄存器的设计module eda_yiweijicunqi( left_right ,load ,clr ,clk ,DIN ,DOUT );input left_right ;wire left_right ;input load ;wire load ;input clr ;wire clr ;input clk ;wire clk ;input [3:0] DIN ;wire [3:0] DIN ;output [3:0] DOUT ;wire [3:0] DOUT ;reg [3:0] data_r;assign DOUT = data_r ;always @ (posedge clk or posedge clr or posedge load)//敏感变量,看真值表beginif(clr==1)data_r <= 0;//判断是否清零else if (load )data_r<=DIN;//判断是否装载数据//判断进行左移位还是右移位elsebeginif(left_right)data_r<=DIN<<1;elsedata_r<=DIN>>1;endendendmodule17.8-3优先编码器的设计module youxianbianma( A ,I ,GS ,EO ,EI ); input [7:0] I ;wire [7:0] I ;input EI ;wire EI ;output [2:0] A ;reg [2:0] A ;output GS ;reg GS ;output EO ;reg EO ;always @ ( I or EI )if ( EI )beginA <= 3'b111;GS <= 1;EO <= 1;endelse if (I==8'b11111111)beginA <= 3'b111;GS <= 1;EO <= 0;endelse if ( I==8'b11111110 )beginA <= 3'b111;GS <= 0;EO <= 1;endelse if ( I==8'b1111110x )beginA <= 3'b110;GS <= 0;EO <= 1;endelse if ( I==8'b111110xx )beginA <= 3'b101;GS <= 0;EO <= 1;endelse if ( I==8'b11110xxx )beginA <= 3'b100;GS <= 0;EO <= 1;endelse if ( I==8'b1110xxxx )beginA <= 3'b011;GS <= 0;EO <= 1;endelse if ( I==8'b110xxxxx )beginA <= 3'b010;GS <= 0;EO <= 1;endelse if ( I==8'b10xxxxxx )beginA <= 3'b001;GS <= 0;EO <= 1;endelse if ( I==8'b0xxxxxxx )beginA <= 3'b000;GS <= 0;EO <= 1;endendmodule18.数据分配器的设计module shujufenpeiqi(y0,y1,y2,y3,din,a); output y0,y1,y2,y3;//4??êy?Yí¨μàinput din;//êy?Yê?è?input [1:0] a;reg y0,y1,y2,y3;always @(din,a)beginy0=0;y1=0;y2=0;y3=0; //3?ê??ˉ£á?case(a)00:y0=din;01:y1=din;02:y2=din;03:y3=din;endcase end endmodule。

FPGA 用Verilog HDL实现三角波,三相方波程序

FPGA——用Verilog HDL进行三角波和三相方波的编写三角波module triangle(inputsys_clk,output [2:0]sda);reg[3:0]a=0;regai=0;always@(posedgesys_clk)beginif(ai==0)begina=a+1;if(a==7)ai<=1;endelsebegina=a-1;if(a==0)ai<=0;endendassignsda[0]=a[0];assignsda[1]=a[1];assignsda[2]=a[2];endmodule三相方波第一种方法:modulepwmabc(inputsys_clk,output [2:0]abc);regtriga=0;regtrigb=1;regtrigc=0;reg[15:0] cnt1=0;reg[15:0] cnt2=20;reg[15:0] cnt3=40;always@(negedgesys_clk)beginif(cnt1>59)begintriga=~triga;cnt1<=1;endelsecnt1<=cnt1+1;if(cnt2>59)begintrigb=~trigb;cnt2<=1;endelsecnt2<=cnt2+1;if(cnt3>59)begintrigc=~trigc;cnt3<=1;endelsecnt3<=cnt3+1;endassignabc[0]=triga;assignabc[1]=trigb;assignabc[2]=trigc;endmodule第二种方法module fangbo0(inputsys_clk,output [2:0]sda);reg [31:0]halftemple_counter0=0;reg [31:0]halftemple_counter1=0;reg [31:0]halftemple_counter2=0;reg [1:0]temple_clk0=1;//第一相的初始值是高电平(初始的高低电平是根据我给你看的相位图来的)reg [1:0]temple_clk1=1;//第二相的初始值是高电平reg [1:0]temple_clk2=0;//第三相的初始值是底电平//我在设计三相方波的时候用的比较笨的方法,就是三相方波一项一项的来设置。

Verilog的135个经典设计实例

Verilog的135个经典设计实例1、立即数放大器:立即数放大器是一种用于将输入电平放大到更高电平的电路,它可以实现任意输入到输出的映射,并且可以在Verilog中使用。

立即数放大器的Verilog实现如下:module immedamp(in, out);input in;output out;reg [3:0] immed;assign out = immed[3];begincase (in)4'b0000: immed = 4'b1000;4'b0001: immed = 4'b1001;4'b0010: immed = 4'b1010;4'b0011: immed = 4'b1011;4'b0100: immed = 4'b1100;4'b0101: immed = 4'b1101;4'b0110: immed = 4'b1110;4'b0111: immed = 4'b1111;4'b1000: immed = 4'b1000;4'b1001: immed = 4'b1001;4'b1010: immed = 4'b1010;4'b1011: immed = 4'b1011;4'b1100: immed = 4'b1100;4'b1101: immed = 4'b1101;4'b1110: immed = 4'b1110;4'b1111: immed = 4'b1111;endcaseendendmodule2、多路复用器:多路复用器是一种用于将多个输入选择转换为单个输出的电路,它可以实现由多种方式选择的输出,并可以使用Verilog实现。

设计的IFFT模块使用Verilog HDL语言实现

//定义各输入输出端口名称

output rfd;

input start;

input fwd_inv;

output dv;

output done;

input clk;

output busy;

output edone;

input [15:0] xn_re;

output [20:0] xk_im;

output [3:0] xn_index;

经过 Check Syntax 正确无误,进行 Simulation 仿真,在 Implementation 和 Simulation 中选择 Simulation,点击要测试的文件后选择 Behavioral Checkhavioral Model,此时出现 Isim 的波形界面,如图 5-3 所示:

图 5-5 IFFT 的 RTL 级结构图

.clk(clk), .busy(busy), .edone(edone), .xn_re(xn_re), .xk_im(xk_im), .xn_index(xn_index), .xk_re(xk_re), .xn_im(xn_im), .xk_index(xk_index));

initial begin

图 5-1 操作流程

编程时有一点需要注意,因为我们已经调用了 IP 核,所以可以查看一下 ISE12.3 中自带的 IP 核程序,如图 5-2,就是此版本中 IP 核的调用:

图 5-2 ISE12.3 版本中 IP 核的调用

随后我们就可以分别编写 myfft 文件及测试波形文件 tb_myfft。先对 myfft

output [20:0] xk_re;

input [15:0] xn_im;

output [3:0] xk_index;

verilog hdl语言100例详解

verilog hdl语言100例详解Verilog HDL语言是一种硬件描述语言,用于描述数字电路和系统的行为和结构。

它是硬件设计工程师在数字电路设计中的重要工具。

本文将介绍100个例子,详细解释Verilog HDL语言的应用。

1. 基本门电路:Verilog HDL可以用于描述基本门电路,如与门、或门、非门等。

例如,下面是一个描述与门电路的Verilog HDL代码:```verilogmodule and_gate(input a, input b, output y);assign y = a & b;endmodule```2. 多路选择器:Verilog HDL也可以用于描述多路选择器。

例如,下面是一个描述2:1多路选择器的Verilog HDL代码:```verilogmodule mux_2to1(input a, input b, input sel, output y);assign y = sel ? b : a;endmodule```3. 寄存器:Verilog HDL可以用于描述寄存器。

例如,下面是一个描述8位寄存器的Verilog HDL代码:```verilogmodule register_8bit(input [7:0] d, input clk, input reset, output reg [7:0] q);always @(posedge clk or posedge reset)if (reset)q <= 0;elseq <= d;endmodule```4. 计数器:Verilog HDL可以用于描述计数器。

例如,下面是一个描述8位计数器的Verilog HDL代码:```verilogmodule counter_8bit(input clk, input reset, output reg [7:0] count);always @(posedge clk or posedge reset)if (reset)count <= 0;elsecount <= count + 1;endmodule```5. 加法器:Verilog HDL可以用于描述加法器。

verilog的15个经典设计实例

begin b=a; c=b; end endmodule

【例 5.11】模为 60 的 BCD 码加法计数器

module count60(qout,cout,data,load,cin,reset,clk);

【例 5.6】用 fork-join 并行块产生信号波形

`timescale 10ns/1ns module wave2; reg wave; parameter cycle=5; initial

fork wave=0;

#(cycle) wave=1; #(2*cycle) wave=0; #(3*cycle) wave=1; #(4*cycle) wave=0; #(5*cycle) wave=1; #(6*cycle) $finish; join initial $monitor($time,,,"wave=%b",wave); endmodule

else

out<=out+1;

end

endmodule

//同步复位 //计数

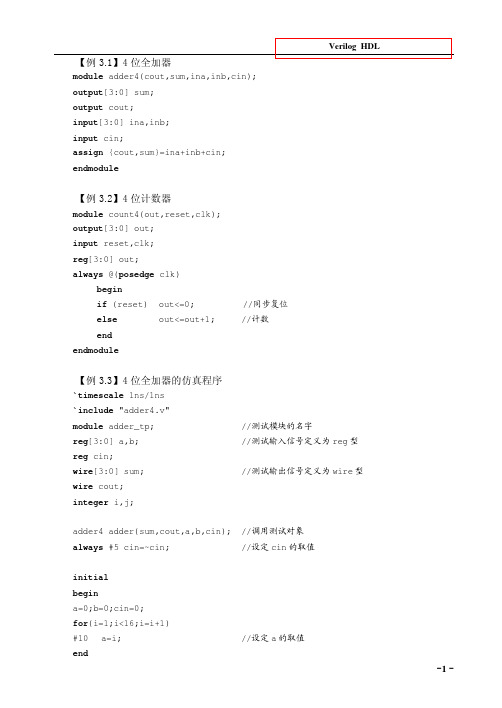

【例 3.3】4 位全加器的仿真程序

`timescale 1ns/1ns `include "adder4.v" module adder_tp; reg[3:0] a,b; reg cin; wire[3:0] sum; wire cout; integer i,j;

output[7:0] qout;

output cout;

input[7:0] data;

input load,cin,clk,reset;

verilog hdl除法

verilog hdl除法

在Verilog HDL中,除法运算通常使用“div”关键字表示。

但是,需要注意的是,除数必须是2的幂次方,这是因为大多数综合工具对于除法运算指令不能很好地综合。

因此,如果除数不是2的幂次方,则需要使用其他方法实现除法运算。

以下是一个使用Verilog HDL实现除法运算的简单示例:

```verilog

module divider(input [7:0] A, input [7:0] B, output [7:0] Q, output [7:0] R);

reg [7:0] temp;

assign temp = A;

assign Q = temp / B;

assign R = temp % B;

endmodule

```

在这个例子中,我们定义了一个名为“divider”的模块,该模块接受两个8位的输入A和B,并输出商Q和余数R。

该模块使用“div”关键字将A除以B,然后将商和余数分别输出。

这个例子中的除法运算仍然受到除数必须是2的幂次方的限制。

如果需要实现任意除数的情况,可以考虑使用其他算法,例如基于减法或基于乘法的算法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

设计示范和上机习题练习一.简单的组合逻辑设计//(方法一)://---------------文件名compare.v -----------------module compare(equal,a,b);input a,b;output equal;assign equal = (a==b)? 1 : 0;//a等于b时,equal输出为1;a不等于b时,equal输出为0。

endmodule//(方法二):module compare(equal,a,b);input a,b;output equal;reg equal;always @(a or b)if(a==b) //a等于b时,equal输出为1;equal =1;else //a不等于b时,equal输出为0。

equal = 0; //思考:如果不写else 部分会产生什么逻辑?endmodule//-------------------------------------------------------------//----------测试模块源代码(方法之一):`timescale 1ns/1ns // 定义时间单位。

`include "./compare.v" // 包含模块文件。

在有的仿真调试环境中并不需要此语句。

//而需要从调试环境的菜单中键入有关模块文件的路径和名称module t;reg a,b;wire equal;initial // initial常用于仿真时信号的给出。

begina=0;b=0;#100 a=0; b=1;#100 a=1; b=1;#100 a=1; b=0;#100 a=0; b=0;#100 $stop; //系统任务,暂停仿真以便观察仿真波形。

endcompare m(.equal(equal),.a(a),.b(b)); //调用被测试模块t.mendmodule//---------- 测试模块源代码(方法之二):-------------------------`timescale 1ns/1ns // 定义时间单位。

`include "./compare.v" // 包含模块文件。

在有的仿真调试环境中并不需要此语句。

//而需要从调试环境的菜单中键入有关模块文件的路径和名称module t;reg a,b;reg clock;wire equal;initial // initial常用于仿真时信号的给出。

begina=0;b=0;clock = 0; //定义一个时钟变量endalways #50 clock = ~clock; //产生周期性的时钟always @ (posedge clock) //在每次时钟正跳变沿时刻产生不同的a 和 bbegina = {$random}%2; // 每次a是0还是1是随机的。

b = {$random}%2; // 每次b是0还是1是随机的。

endinitialbegin #100000 $stop; end //系统任务,暂停仿真以便观察仿真波形。

compare m(.equal(equal),.a(a),.b(b)); //调用被测试模块t.mendmodule练习二. 简单分频时序逻辑电路的设计//------------------------- 文件名:half_clk.v --------------------------------module half_clk(reset,clk_in,clk_out);input clk_in,reset;output clk_out;reg clk_out;always @(posedge clk_in)beginif(!reset) clk_out=0;else clk_out=~clk_out;endendmodule//---------- 测试模块的源代码:------------------------//------------------- 文件名top.v -----------------------------`timescale 1ns/100ps`define clk_cycle 50module top;reg clk,reset;wire clk_out;always #`clk_cycle clk = ~clk; //产生测试时钟initialbeginclk = 0;reset = 1;#10 reset = 0;#110 reset = 1;#100000 $stop;endhalf_clk m0(.reset(reset),.clk_in(clk),.clk_out(clk_out)); endmodule练习三. 利用条件语句实现计数分频时序电路//-------------- 模块源代码:-----------------------------// --------------- fdivision.v -----------------------------module fdivision(RESET,F10M,F500K);input F10M,RESET;output F500K;reg F500K;reg [7:0]j;always @(posedge F10M)if(!RESET) //低电平复位。

beginF500K <= 0;j <= 0;endelsebeginif(j==19) //对计数器进行判断,以确定F500K 信号是否反转。

beginj <= 0;F500K <= ~F500K;endelsej <= j+1;endendmodule//------------- 测试模块源代码:------------------------- //--------------- fdivision_Top.v ------------------------ `timescale 1ns/100ps`define clk_cycle 50module division_Top;reg F10M,RESET;wire F500K_clk;always #`clk_cycle F10M = ~ F10M;initialbeginRESET=1;F10M=0;#100 RESET=0;#100 RESET=1;#10000 $stop;endfdivision fdivision(.RESET(RESET),.F10M(F10M),.F500K(F500K_clk)); endmodule练习四. 阻塞赋值与非阻塞赋值的区别// ---------- 模块源代码:----------------------// ------------- blocking.v ---------------module blocking(clk,a,b,c);output [3:0] b,c;input [3:0] a;input clk;reg [3:0] b,c;always @(posedge clk)beginb = a;c = b;$display("Blocking: a = %d, b = %d, c = %d ",a,b,c);endendmodule//------------- non_blocking.v -------------------module non_blocking(clk,a,b,c);output [3:0] b,c;input [3:0] a;input clk;always @(posedge clk)beginb <= a;c <= b;$display("Non_Blocking: a = %d, b = %d, c = %d ",a,b,c); endendmodule// ---------- 测试模块源代码:--------------------------//------------- compareTop.v -----------------------------`timescale 1ns/100ps`include "./blocking.v"`include "./non_blocking.v"module compareTop;wire [3:0] b1,c1,b2,c2;reg [3:0] a;initialbeginclk = 0;forever #50 clk = ~clk; //思考:如果在本句后还有语句,能否执行?为什么?endinitialbegina = 4'h3;$display("____________________________");# 100 a = 4'h7;$display("____________________________");# 100 a = 4'hf;$display("____________________________");# 100 a = 4'ha;$display("____________________________");# 100 a = 4'h2;$display("____________________________");# 100 $display("____________________________");$stop;endnon_blocking non_blocking(clk,a,b2,c2); blocking blocking(clk,a,b1,c1);endmodule练习五. 用always块实现较复杂的组合逻辑电路//---------------文件名alu.v --------------------------`define plus 3'd0`define minus 3'd1`define band 3'd2`define bor 3'd3`define unegate 3'd4module alu(out,opcode,a,b);output[7:0] out;reg[7:0] out;input[2:0] opcode;input[7:0] a,b; //操作数。