51汇编语言指令集符号定义表 (1)

汇编指令

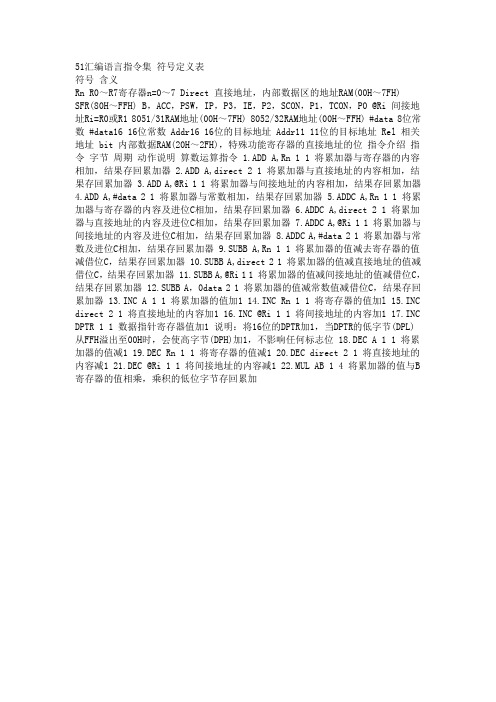

51汇编语言指令集符号定义表符号含义Rn R0~R7寄存器n=0~7 Direct 直接地址,内部数据区的地址RAM(00H~7FH) SFR(80H~FFH) B,ACC,PSW,IP,P3,IE,P2,SCON,P1,TCON,P0 @Ri 间接地址Ri=R0或R1 8051/31RAM地址(00H~7FH) 8052/32RAM地址(00H~FFH) #data 8位常数 #data16 16位常数 Addr16 16位的目标地址 Addr11 11位的目标地址 Rel 相关地址 bit 内部数据RAM(20H~2FH),特殊功能寄存器的直接地址的位指令介绍指令字节周期动作说明算数运算指令 1.ADD A,Rn 1 1 将累加器与寄存器的内容相加,结果存回累加器 2.ADD A,direct 2 1 将累加器与直接地址的内容相加,结果存回累加器 3.ADD A,@Ri 1 1 将累加器与间接地址的内容相加,结果存回累加器4.ADD A,#data 2 1 将累加器与常数相加,结果存回累加器 5.ADDC A,Rn 1 1 将累加器与寄存器的内容及进位C相加,结果存回累加器 6.ADDC A,direct 2 1 将累加器与直接地址的内容及进位C相加,结果存回累加器 7.ADDC A,@Ri 1 1 将累加器与间接地址的内容及进位C相加,结果存回累加器 8.ADDC A,#data 2 1 将累加器与常数及进位C相加,结果存回累加器 9.SUBB A,Rn 1 1 将累加器的值减去寄存器的值减借位C,结果存回累加器 10.SUBB A,direct 2 1 将累加器的值减直接地址的值减借位C,结果存回累加器 11.SUBB A,@Ri 1 1 将累加器的值减间接地址的值减借位C,结果存回累加器 12.SUBB A,0data 2 1 将累加器的值减常数值减借位C,结果存回累加器 13.INC A 1 1 将累加器的值加1 14.INC Rn 1 1 将寄存器的值加l 15.INC direct 2 1 将直接地址的内容加1 16.INC @Ri 1 1 将间接地址的内容加1 17.INC DPTR 1 1 数据指针寄存器值加1 说明:将16位的DPTR加1,当DPTR的低字节(DPL)从FFH溢出至00H时,会使高字节(DPH)加1,不影响任何标志位 18.DEC A 1 1 将累加器的值减1 19.DEC Rn 1 1 将寄存器的值减1 20.DEC direct 2 1 将直接地址的内容减1 21.DEC @Ri 1 1 将间接地址的内容减1 22.MUL AB 1 4 将累加器的值与B 寄存器的值相乘,乘积的低位字节存回累加器,高位字节存回B寄存器说明:将累加器A和寄存器B内的无符号整数相乘,产生16位的积,低位字节存入A,高位字节存入B寄存器。

51单片机汇编语言入门教程

51单片机汇编语言入门教程什么是51单片机

51单片机指的是英特尔公司推出的一种单片机芯片种类,其名字为“AT89S52”。

后来,这种芯片因其使用广泛,被人们简称为“51单片机”。

为什么要研究汇编语言

研究汇编语言能够让我们更好地理解机器是如何执行指令的,

从而更好地优化程序,提高程序运行效率。

汇编语言基础知识

数据类型

- 字节:一个字节是8位二进制数,可以表示0~255之间的数。

- 字:一个字是16位二进制数,可以表示0~之间的数。

- 双字:一个双字是32位二进制数,可以表示0~之间的数。

指令集

51单片机有大约100条汇编指令,这些指令可以完成各种操作,如运算、数据传输、中断处理等。

寄存器

51单片机有4个8位的通用寄存器(寄存器0~3)和2个16

位的通用寄存器(DPTR和PC)。

程序结构

51单片机只有一种程序结构——线性结构。

程序从0地址开始执行,一条一条地执行,直到程序结束。

编写第一个汇编程序

以下是一个简单的汇编程序示例:

ORG 0H ;设置程序起始地址为0H

MOV P1, #55H ;将55H赋值给P1口

END ;程序结束指令

这个程序的作用是将55H赋值给P1口。

总结

通过学习本教程,我们了解了基本的汇编语言知识,包括数据

类型、指令集、寄存器、程序结构以及编写程序的基本步骤。

希望

这份教程可以帮助初学者顺利掌握51单片机汇编语言编程的基础。

51单片机汇编指令及伪指令小结

51单片机汇编指令及伪指令小结51单片机汇编指令及伪指令小结51单片机是一种广泛应用的基于汇编语言的微控制器。

它的汇编指令集非常丰富,包括了基本的数据处理、逻辑运算、分支跳转、数据存储和输入输出等指令。

汇编指令的灵活运用可以实现各种复杂的功能,因此掌握51单片机的汇编指令是开发嵌入式系统的重要基础。

1. 基本数据处理指令51单片机汇编指令集包括了一系列基本的数据处理指令,如加法(add)、减法(sub)、乘法(mul)、除法(div)等。

这些指令用于实现对数据的基本运算操作。

2. 逻辑运算指令逻辑运算指令用于实现各种逻辑运算,如与(and)、或(or)、非(not)、异或(xor)等。

这些指令通常用于处理数据的开关控制、状态判断等功能。

3. 分支跳转指令分支跳转指令用于实现程序的流程控制。

常用的分支跳转指令包括无条件跳转(jmp)、条件跳转(jz、jnz、jc、jnc等)、循环跳转(loop)等。

这些指令可以根据条件和需求设置程序的执行流程,实现各种循环、分支等功能。

4. 数据存储指令数据存储指令用于实现数据的存储和加载操作。

常用的存储指令包括将数据存储到寄存器或内存中(mov)、将数据从寄存器或内存中加载(ld)等。

这些指令通过对数据的存储和加载,实现对数据的读写操作。

5. 输入输出指令输入输出指令用于实现与外设的数据通信。

常用的输入输出指令包括从端口输入(instr)、输出到端口(outstr)等。

这些指令通过与外部设备的数据交互,实现嵌入式系统与外设的连接。

除了以上的基本指令外,51单片机还提供了一些伪指令,用于程序的组织和调试。

这些伪指令包括宏指令、条件编译指令、调试指令等。

1. 宏指令宏指令是一种通过宏展开的方式来扩展汇编代码的指令。

它通过提前定义一些宏,并在代码中使用这些宏来生成更复杂的汇编代码。

宏指令的好处是可以简化代码的书写,使得程序的逻辑更清晰。

2. 条件编译指令条件编译指令用于根据编译时的条件来选择性地编译代码。

单片机常用指令

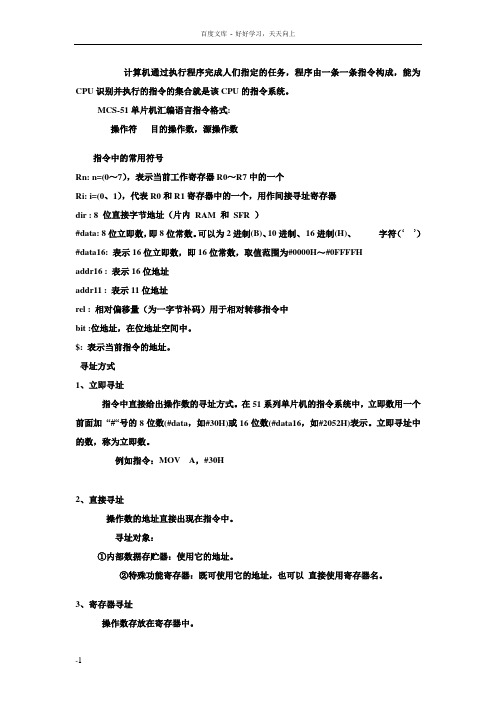

计算机通过执行程序完成人们指定的任务,程序由一条一条指令构成,能为CPU识别并执行的指令的集合就是该CPU的指令系统。

MCS-51单片机汇编语言指令格式:操作符目的操作数,源操作数指令中的常用符号Rn: n=(0~7),表示当前工作寄存器R0~R7中的一个Ri: i=(0、1),代表R0和R1寄存器中的一个,用作间接寻址寄存器dir : 8 位直接字节地址(片内RAM 和SFR )#data: 8位立即数,即8位常数。

可以为2进制(B)、10进制、16进制(H)、字符(‘ ’)#data16: 表示16位立即数,即16位常数,取值范围为#0000H~#0FFFFHaddr16 : 表示16位地址addr11 : 表示11位地址rel : 相对偏移量(为一字节补码)用于相对转移指令中bit :位地址,在位地址空间中。

$: 表示当前指令的地址。

寻址方式1、立即寻址指令中直接给出操作数的寻址方式。

在51系列单片机的指令系统中,立即数用一个前面加“#“号的8位数(#data,如#30H)或16位数(#data16,如#2052H)表示。

立即寻址中的数,称为立即数。

例如指令:MOV A,#30H2、直接寻址操作数的地址直接出现在指令中。

寻址对象:①内部数据存贮器:使用它的地址。

②特殊功能寄存器:既可使用它的地址,也可以直接使用寄存器名。

3、寄存器寻址操作数存放在寄存器中。

寻址对象:A,B,DPTR,R0~R7 。

B 仅在乘除法指令中为寄存器寻址,在其他指令中为直接寻址。

A 可以寄存器寻址又可以直接寻址,直接寻址时写作ACC例如:MOV A,R0 ;R0→A,A、R0均为寄存器寻址,机器码E8MUL AB ;A*B→BA,A、B为寄存器寻址,机器码A4MOV B,R0 ;R0→B,R0为寄存器寻址,B为直接寻址机器码88F0,其中F0为B的字节地址(见表1-2)PUSH ACC ;A的内容压入堆栈机器码C0E04、寄存器间址操作数存放在以寄存器内容为地址的单元中。

汇编语言指令集

汇编语言指令集1 数据传送指令集MOV功能: 把源操作数送给目的操作数语法: MOV 目的操作数,源操作数格式: MOV r1,r2MOV r,mMOV m,rMOV r,dataXCHG功能: 交换两个操作数的数据语法: XCHG格式: XCHG r1,r2 XCHG m,r XCHG r,mPUSH,POP功能: 把操作数压入或取出堆栈语法: PUSH 操作数 POP 操作数格式: PUSH r PUSH M PUSH data POP r POP m PUSHF,POPF,PUSHA,POPA功能: 堆栈指令群格式: PUSHF POPF PUSHA POPALEA,LDS,LES功能: 取地址至寄存器语法: LEA r,m LDS r,m LES r,mXLAT(XLATB)功能: 查表指令语法: XLAT XLAT m算数运算指令ADD,ADC功能: 加法指令语法: ADD OP1,OP2 ADC OP1,OP2格式: ADD r1,r2 ADD r,m ADD m,r ADD r,data影响标志: C,P,A,Z,S,OSUB,SBB功能:减法指令语法: SUB OP1,OP2 SBB OP1,OP2格式: SUB r1,r2 SUB r,m SUB m,r SUB r,data SUB m,data影响标志: C,P,A,Z,S,OINC,DEC功能: 把OP的值加一或减一语法: INC OP DEC OP格式: INC r/m DEC r/m影响标志: P,A,Z,S,ONEG功能: 将OP的符号反相(取二进制补码)语法: NEG OP格式: NEG r/m影响标志: C,P,A,Z,S,OMUL,IMUL功能: 乘法指令语法: MUL OP IMUL OP格式: MUL r/m IMUL r/m影响标志: C,P,A,Z,S,O(仅IMUL会影响S标志)DIV,IDIV功能:除法指令语法: DIV OP IDIV OP格式: DIV r/m IDIV r/mCBW,CWD功能: 有符号数扩展指令语法: CBW CWDAAA,AAS,AAM,AAD功能: 非压BCD码运算调整指令语法: AAA AAS AAM AAD影响标志: A,C(AAA,AAS) S,Z,P(AAM,AAD)DAA,DAS功能: 压缩BCD码调整指令语法: DAA DAS影响标志: C,P,A,Z,S位运算指令集AND,OR,XOR,NOT,TEST功能: 执行BIT与BIT之间的逻辑运算语法: AND r/m,r/m/data OR r/m,r/m/data XOR r/m,r/m/data TESTr/m,r/m/data NOT r/m影响标志: C,O,P,Z,S(其中C与O两个标志会被设为0) NOT指令不影响任何标志位SHR,SHL,SAR,SAL功能: 移位指令语法: SHR r/m,data/CL SHL r/m,data/CL SAR r/m,data/CL SAL r/m,data/CL影响标志: C,P,Z,S,OROR,ROL,RCR,RCL功能: 循环移位指令语法: ROR r/m,data/CL ROL r/m,data/CL RCR r/m,data/CL RCL r/m,data/CL影响标志: C,P,Z,S,O程序流程控制指令集CLC,STC,CMC功能: 设定进位标志语法: CLC STC CMC标志位: CCLD,STD功能: 设定方向标志语法: CLD STD标志位: DCLI,STI功能: 设定中断标志语法: CLI STI标志位: ICMP功能: 比较OP1与OP2的值语法: CMP r/m,r/m/data标志位: C,P,A,Z,OJMP功能: 跳往指定地址执行语法: JMP 地址JXX功能: 当特定条件成立则跳往指定地址执行语法: JXX 地址注: A: ABOVE,当C=0,Z=0时成立 B: BELOW,当C=1时成立 C: CARRY,当弁时成立 CXZ: CX寄存器的值为0(ZERO)时成立 E: EQUAL,当Z=1时成立 G: GREATER(大于),当Z=0且S=0时成立 L: LESS(小于),当S不为零时成立 N: NOT(相反条件),需和其它符号配合使用 O: OVERFLOW,O=1时成立 P: PARITY,P=1时成立 PE: PARITY EVEN,P=1时成立 PO: PARITY ODD,P=0时成立 S: SIGN,S=1时成立 Z: ZERO,Z=1时成立LOOP功能: 循环指令集语法: LOOP 地址LOOPE(Z)地址 LOOPNE(Z) 地址标志位: 无CALL,RET功能: 子程序调用,返回指令语法: CALL 地址 RET RET n标志位: 无INT,IRET功能: 中断调用及返回指令语法: INT n IRET标志位: 在执行INT时,CPU会自动将标志寄存器的值入栈,在执行IRET时则会将堆栈中的标志值弹回寄存器字符串操作指令集MOVSB,MOVSW,MOVSD功能: 字符串传送指令语法: MOVSB MOVSW MOVSD标志位: 无CMPSB,CMPSW,CMPSD功能: 字符串比较指令语法: CMPSB CMPSW CMPSD标志位: C,P,Z,S,OSCASB,SCASW功能: 字符串搜索指令语法: SCASB SCASW标志位: C,P,Z,S,OLODSB,LODSW,STOSB,STOSW功能: 字符串载入或存贮指令语法: LODSB LODSW STOSB STOSW标志位: 无REP,REPE,REPNE功能: 重复前缀指令集语法: REP 指令S REPE 指令S REPNE 指令S标志位: 依指令S而定 对于IBM PC机它有它的指令系统,其中包括:数据传送指令、串处理指令、算术指令、控制移动指令、逻辑指令、处理机控制指令。

单片机伪指令和指令详解

ASM-51汇编伪指令一、伪指令分类1.符号定义SEGMENT, EQU, SET, DATA, IDATA, XDATA, BIT, CODE2.存储器初始化/保留DS, DB, DW, DBIT3.程序链接PUBILC, EXTRN, NAME4.汇编程序状态控制ORG, END5.选择段的伪指令RSEG, CSEG, DSEG, XSEG, ISEG, BSEG, USING二、伪指令具体说明1.符号定义伪指令1)SEGMENT伪指令格式:段名SEGMENT 段类型说明:SEGMENT 伪指令说明一个段。

段就是一块程序代码或数据存储器。

允许使用的段类型为:●CODE代码空间●DATA 可以直接寻址的内部数据空间●XDATA外部数据空间●IDATA可以间接寻址的整个内部数据空间●BIT位空间例子:(段符号用于表达式时,代表被连接段的基地址)STACK SEGMENT IDATARSEG STACKDS 10H ;保留16字节做堆栈MOV SP , #STACK-1 ;堆栈指针初始化2)EQU伪指令格式:符号名 EQU 表达式符号名 EQU 特殊汇编符号说明:EQU表示把一个数值或特殊汇编符号赋予规定的名字。

一个表达式赋予一个符号,必须是不带向前访问的表达式。

例子:N27 EQU 27;ACCUM EQU A ;定义ACCUM代替特殊汇编符号A(累加器)HERE EQU $; HERE为当前位置计数器的值3)SET伪指令格式:符号名 SET 表达式符号名 SET 特殊汇编符号说明:SET类似EQU,区别在于可以用另一个SET伪指令在以后对定义过的符号重新定义。

例子:COUNT SET 0COUNT SET COUNT+14)BIT伪指令格式:符号名 BIT 位地址说明: BIT伪指令把一个地址赋予规定的符号名。

该符号类型取段类型BIT.例子:RSEG DATA_SEG;CONTROL: DS 1ALATM BIT CONTROL.0;OPEN_BOARD BIT ALATM+1 ;下一位RESET_BOARD BIT 60H ;下一个绝对的位5)DATA伪指令格式:符号名 DATA 表达式说明:DATA伪指令把片内的数据地址赋予所规定的符号名。

C51汇编语言指令集

51汇编语言指令集一、符号定义表符号含义Rn R0~R7寄存器n=0~7Direc t 直接地址,内部数据区的地址RAM(00H~7FH)SFR(80H~FFH) B,ACC,PSW,IP,P3,IE,P2,SCON,P1,TCON,P0@Ri 间接地址Ri=R0或R1 8051/31RAM地址(00H~7FH) 8052/32RAM地址(00H~FFH)#data 8位常数#data1616位常数Addr16 16位的目标地址Addr11 11位的目标地址Rel 相关地址bit 内部数据RAM(20H~2FH),特殊功能寄存器的直接地址的位二、指令介绍指令字节周期动作说明算数运算指令1.ADD A,Rn 1 1 将累加器与寄存器的内容相加,结果存回累加器2.ADD A,direct 2 1 将累加器与直接地址的内容相加,结果存回累加器3.ADD A,@Ri 1 1 将累加器与间接地址的内容相加,结果存回累加器4.ADD A,#data 2 1 将累加器与常数相加,结果存回累加器5.ADDC A,Rn 1 1 将累加器与寄存器的内容及进位C相加,结果存回累加器6.ADDC A,direct 2 1 将累加器与直接地址的内容及进位C相加,结果存回累加器7.ADDC A,@Ri 1 1 将累加器与间接地址的内容及进位C相加,结果存回累加器8.ADDC A,#data 2 1 将累加器与常数及进位C相加,结果存回累加器9.SUBB A,Rn 1 1 将累加器的值减去寄存器的值减借位C,结果存回累加器10.SUBB A,direct 2 1 将累加器的值减直接地址的值减借位C,结果存回累加器11.SUBBA,@Ri1 1 将累加器的值减间接地址的值减借位C,结果存回累加器12.SUBBA,0data2 1 将累加器的值减常数值减借位C,结果存回累加器13.INC A 1 1 将累加器的值加114.INC Rn 1 1 将寄存器的值加l15.INCdirect2 1 将直接地址的内容加116.INC@Ri1 1 将间接地址的内容加117.INCDPTR1 1 数据指针寄存器值加1说明:将16位的DPTR加1,当DPTR的低字节(DPL)从FFH溢出至00H时,会使高字节(DPH)加1,不影响任何标志位18.DEC A 1 1 将累加器的值减119.DEC Rn 1 1 将寄存器的值减120.DEC direct 2 1 将直接地址的内容减121.DEC@Ri1 1 将间接地址的内容减122.MUL AB 1 4 将累加器的值与B寄存器的值相乘,乘积的低位字节存回累加器,高位字节存回B寄存器说明:将累加器A和寄存器B内的无符号整数相乘,产生16位的积,低位字节存入A,高位字节存入B寄存器。

C51(8051)指令集

符号定义表

序 号 1 2 3 4 5 6 7 8 9 符号 Rn Direct @Ri #data #data16 Addr16 Addr11 Rel bit 含义 R0~R7寄存器n=0~7 直接地址,内部数据区的地址RAM(00H~7FH) SFR(80H~FFH) B,ACC,PSW,IP,P3,IE,P2,SCON,P1,TCON,P0 间接地址Ri=R0或R1 8051/31RAM地址(00H~7FH) 8052/32RAM地址(00H~FFH) 8位常数 16位常数 16位的目标地址 11位的目标地址 相关地址 内部数据RAM(20H~2FH)、特殊功能寄存器的直接地址的位

指令介绍

算术运算指令

1 ADD A,Rn 1 1 2 ADD A,direct 2 1 3 ADD A,@Ri 1 1 4 ADD A,#data 2 1 5 ADDC A,Rn 1 1 6 ADDC A,direct 2 1 7 ADDC A,@Ri 1 1 8 ADDC A,#data 2 1 9 SUBB A,Rn 1 1 10 SUBB A,direct 2 1 11 SUBB A,@Ri 1 1 12 SUBB A,0data 2 1 13 INC A 1 1 14 INC Rn 1 1 15 INC direct 2 1 16 INC @Ri 1 1 17 INC DPTR 1 1 说明:将16位的DPTR加1,当DPTR的低字节(DPL)从FFH溢出至00H时,会使高字节(DPH)加1,不影响任何标志位 18 DEC A 1 1 19 DEC Rn 1 1 20 DEC direct 2 1 21 DEC @Ri 1 1 22 MUL AB 1 4 说明:将累加器A和寄存器B内的无符号整数相乘,产生16位的积,低位字节存入A,高位字节存入B寄存器。如果积大于FFH,则溢出标志位(OV)被设定为1,而进 位标志位为0 23 DIV AB 1 4 说明:无符号的除法运算,将累加器A除以B寄存器的值,商存入A,余数存入B。执行本指令后,进位位(C)及溢出位(OV)被清除为0 24 DA A 1 1 序 指令 号 字节 周期

51指令集

传送指令是指令系统中最基本,使用最多的一类指令,主要用于数据的传送、保存以及交换等场合。

1.以累加器A为目的操作数的指令(4条)这组指令的功能是把源操作数指定的内容送入累加器A中。

有寄存器、直接、寄存器间接和立即4种寻址方式。

MOV A, Rn MOV A, dataMOV A,@Rn MOV A,#data2.以寄存器Rn为目的的操作数的指令(3条)这组指令的功能是把源操作数指定的内容送到所选定的工作寄存器Rn中。

有寄存器、直接和立即3种寻址方式。

MOV Rn, A MOV Rn,dataMOV Rn,#data3.以直接地址为目的操作数的指令(5条)这组指令的功能是把源操作数指定的内容送到由直接地址data所指定的片内RAM中。

有寄存器、直接、寄存器间接和立即4种寻址方式。

MOV data,A MOV data,RnMOV data1,data2 MOV data,@RiMOV data,#data4.以间接地址为目的操作数的指令(3条)这组指令的功能是把源操作数指定的内容送到以Ri中的内容为地址的片内RAM中。

有寄存器、直接和立即3种寻址方式。

MOV @Ri,A MOV @Ri,dataMOV @Ri,#data5.查表指令(2条)这组指令的功能是对存放于程序存储器中的数据表格进行查找传送。

使用变址寻址方式。

MOVC A,@A+DPTR MOVC A, @A+PC6.累加器A与片外AM传送指令(4条)这组指令的功能为累加器A与片RAM间的相互传送。

由于MCS-51指令系统中没有专门的输入/输出指令,且片外扩展的I/O口与片外RAM是统一编址的,故以下4条指令也可作为输入/输出指令。

使用寄存器间接寻址方式。

MOVX A,@DPAR MOVX @DPTR,AMOVX A,@Ri MOVX @Ri,A7.堆栈操作类指令(2条)该类指令的功能是把直接寻址单元的内容传送到堆栈指针SP所指的单元中,以及把SP所指单元的内容送到直接寻址单元中。

汇编语言指令集

mova,b 把b的值送给aret 返回主程序no p 无作用,英文“n o ope ratio n”的简写,意思是“do no thing”(机器码90)***机器码的含义参看上面(解释:u ltrae dit打开编辑exe文件时你看到90,等同于汇编语句nop)c all 调用子程序je或jz若相等则跳(机器码74 或0F84) jne或jnz若不相等则跳(机器码75或0F85) jmp无条件跳(机器码E B)jb 若小于则跳ja若大于则跳jg 若大于则跳jge若大于等于则跳jl若小于则跳j le 若小于等于则跳p op 出栈p ush 压栈三.常见修改(机器码)74=>7574=>90 74=>EB 75=>74 75=>90 75=>EBjnz->nop75->90(相应的机器码修改)jn z ->jmp 75-> EB(相应的机器码修改)j nz -> jz 75->74 (正常) 0F 85-> 0F 84(特殊情况下,有时,相应的机器码修改)四.两种不同情况的不同修改方法1.修改为jm pje(jn e,jz,jnz)=>jmp相应的机器码EB (出错信息向上找到的第一个跳转)jmp 的作用是绝对跳,无条件跳,从而跳过下面的出错信息xxxx xxxxx xxx 出错信息,例如:注册码不对,so rry,未注册版不能...,"Funct ion N ot Av aible in D emo"或"Comm and N ot Av aible" 或"Can't save in S harew are/D emo"等(我们希望把它跳过,不让它出现)<。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

51汇编语言指令集符号定义表符号含义Rn R0~R7寄存器n=0~7Direct 直接地址,内部数据区的地址RAM(00H~7FH)SFR(80H~FFH) B,ACC,PSW,IP,P3,IE,P2,SCON,P1,TCON,P0@Ri 间接地址Ri=R0或R1 8051/31RAM地址(00H~7FH) 8052/32RAM地址(00H~FFH)#data 8位常数#data16 16位常数Addr16 16位的目标地址Addr11 11位的目标地址Rel 相关地址bit 内部数据RAM(20H~2FH),特殊功能寄存器的直接地址的位指令介绍指令字节周期动作说明算数运算指令1.ADD A,Rn 将累加器与寄存器的内容相加,结果存回累加器2.ADD A,direct 将累加器与直接地址的内容相加,结果存回累加器3.ADD A,@Ri 将累加器与间接地址的内容相加,结果存回累加器4.ADD A,#data 将累加器与常数相加,结果存回累加器5.ADDC A,Rn 将累加器与寄存器的内容及进位C相加,结果存回累加器6.ADDC A,direct 将累加器与直接地址的内容及进位C相加,结果存回累加器7.ADDC A,@Ri 将累加器与间接地址的内容及进位C相加,结果存回累加器8.ADDC A,#data 将累加器与常数及进位C相加,结果存回累加器9.SUBB A,Rn 将累加器的值减去寄存器的值减借位C,结果存回累加器10.SUBB A,direct 将累加器的值减直接地址的值减借位C,结果存回累加器11.SUBB A,@Ri 将累加器的值减间接地址的值减借位C,结果存回累加器12.SUBB A,#data 将累加器的值减常数值减借位C,结果存回累加器13.INC A 将累加器的值加114.INC Rn 将寄存器的值加l15.INC direct 将直接地址的内容加116.INC @Ri 将间接地址的内容加117.INC DPTR 数据指针寄存器值加1说明:将16位的DPTR加1,当DPTR的低字节(DPL)从FFH溢出至00H时,会使高字节(DPH)加1,不影响任何标志位18.DEC A 将累加器的值减119.DEC Rn 将寄存器的值减120.DEC direct 将直接地址的内容减121.DEC @Ri 将间接地址的内容减122.MUL AB 将累加器的值与B寄存器的值相乘,乘积的低位字节存回累加器,高位字节存回B寄存器说明:将累加器A和寄存器B内的无符号整数相乘,产生16位的积,低位字节存入A,高位字节存入B寄存器。

如果积大于FFH,则溢出标志位(OV)被设定为1,而进位标志位为0 23.DIV AB 将累加器的值除以B寄存器的值,结果的商存回累加器,余数存回B寄存器说明:无符号的除法运算,将累加器A除以B寄存器的值,商存入A,余数存入B。

执行本指令后,进位位(C)及溢出位(OV)被清除为024.DA A 将累加器A作十进制调整,若(A) 3-0>9或(AC)=1,则(A) 3-0←(A)3-0+6若(A) 7-4>9或(C)=1,则(A) 7-4←(A)7-4+6逻辑运算指令25.ANL A,Rn 将累加器的值与寄存器的值做AND的逻辑判断,结果存回累加器26.ANL A,direct 将累加器的值与直接地址的内容做AND的逻辑判断,结果存回累加器27.ANL A,@Ri 将累加器的值与间接地址的内容做AND的逻辑判断,结果存回累加器28.ANL A,#data 将累加器的值与常数做AND的逻辑判断,结果存回累加器29.ANL direct,A 将直接地址的内容与累加器的值做AND的逻辑判断,结果存回该直接地址30.ANL direct,#data 将直接地址的内容与常数值做AND的逻辑判断,结果存回该直接地址31.ORL A,Rn 将累加器的值与寄存器的值做OR的逻辑判断,结果存回累加器32.ORL A,direct 将累加器的值与直接地址的内容做OR的逻辑判断,结果存回累加器33.ORL A,@Ri 将累加器的值与间接地址的内容做OR的逻辑判断,结果存回累加器34.ORL A,#data 将累加器的值与常数做OR的逻辑判断,结果存回累加器35.ORL direct,A 将直接地址的内容与累加器的值做OR的逻辑判断,结果存回该直接地址36.ORL direct,#data 将直接地址的内容与常数值做OR的逻辑判断,结果存回该直接地址37.XRL A,Rn 将累加器的值与寄存器的值做XOR的逻辑判断,结果存回累加器38.XRL A,direct 将累加器的值与直接地址的内容做XOR的逻辑判断,结果存回累加器39.XRL A,@Ri 将累加器的值与间接地扯的内容做XOR的逻辑判断,结果存回累加器40.XRL A,#data 将累加器的值与常数作XOR的逻辑判断,结果存回累加器41.XRL direct,A 将直接地址的内容与累加器的值做XOR的逻辑判断,结果存回该直接地址42.XRL direct,#data 将直接地址的内容与常数的值做XOR的逻辑判断,结果存回该直接地址43.CLR A 清除累加器的值为044.CPL A 将累加器的值反相45.RL A将累加器的值左移一位46.RLC A 将累加器含进位C左移一位47.RR A 将累加器的值右移一位48.RRC A 将累加器含进位C右移一位49.SW AP A 将累加器的高4位与低4位的内容交换。

(A)3-0←(A)7-4数据转移指令50.MOV A,Rn 将寄存器的内容载入累加器51.MOV A,direct 将直接地址的内容载入累加器52.MOV A,@Ri 将间接地址的内容载入累加器53.MOV A,#data 将常数载入累加器54.MOV Rn,A 将累加器的内容载入寄存器55.MOV Rn,direct 将直接地址的内容载入寄存器56.MOV Rn,gdata 将常数载入寄存器57.MOV direct,A 将累加器的内容存入直接地址58.MOV direct,Rn 将寄存器的内容存入直接地址59.MOV direct1, direct2将直接地址2的内容存入直接地址160.MOV direct,@Ri将间接地址的内容存入直接地址61.MOV direct,#data将常数存入直接地址62.MOV @Ri,A将累加器的内容存入某间接地址63.MOV @Ri,direct 将直接地址的内容存入某间接地址64.MOV @Ri,#data 将常数存入某间接地址65.MOV DPTR,#data16 将16位的常数存入数据指针寄存器66.MOVC A,@A+DPTR 1 2 (A) ←((A)+(DPTR))累加器的值再加数据指针寄存器的值为其所指定地址,将该地址的内容读入累加器67.MOVC A,@A+PC 1 2 (PC)←(PC)+1;(A)←((A)+(PC))累加器的值加程序计数器的值作为其所指定地址,将该地址的内容读入累加器68.MOVX A,@Ri 将间接地址所指定外部存储器的内容读入累加器(8位地址) 69.MOVX A,@DPTR 将数据指针所指定外部存储器的内容读入累加器(16位地址) 70.MOVX @Ri,A 将累加器的内容写入间接地址所指定的外部存储器(8位地址) 71.MOVX @DPTR,A 将累加器的内容写入数据指针所指定的外部存储器(16位地址) 72.PUSH direct 将直接地址的内容压入堆栈区73.POP direct 从堆栈弹出该直接地址的内容74.XCH A,Rn 将累加器的内容与寄存器的内容互换75.XCH A,direct 将累加器的值与直接地址的内容互换76.XCH A,@Ri 将累加器的值与间接地址的内容互换77.XCHD A,@Ri 将累加器的低4位与间接地址的低4位互换布尔代数运算78.CLR C 清除进位C为079.CLR bit 清除直接地址的某位为080.SETB C 设定进位C为181.SETB bit 设定直接地址的某位为182.CPL C 将进位C的值反相83.CPL bit 将直接地址的某位值反相84.ANL C,bit 将进位C与直接地址的某位做AND的逻辑判断,结果存回进位C 85.ANL C,/bit 将进位C与直接地址的某位的反相值做AND的逻辑判断,结果存回进位C86.ORL C,bit将进位C与直接地址的某位做OR的逻辑判断,结果存回进位C87.ORL C,/bit 将进位C与直接地址的某位的反相值做OR的逻辑判断,结果存回进位C 88.MOV C,bit 将直接地址的某位值存入进位C89.MOV bit,C 将进位C的值存入直接地址的某位90.JC rel若进位C=1则跳至rel的相关地址91.JNC rel 若进位C=0则跳至rel的相关地址92.JB bit,rel 若直接地址的某位为1,则跳至rel的相关地址93.JNB bit,rel 若直接地址的某位为0,则跳至rel的相关地址94.JBC bit,rel 若直接地址的某位为1,则跳至rel的相关地址,并将该位值清除为0程序跳跃95.ACALL addr11 调用2K程序存储器范围内的子程序96.LCALL addr16 调用64K程序存储器范围内的子程序97.RET 从子程序返回98.RETI 从中断子程序返回99.AJMP addr11 绝对跳跃(2K内)100.LJMP addr16 长跳跃(64K内)101.SJMP rel 短跳跃(2K内)-128~+127字节102.JMP @A+DPTR 跳至累加器的内容加数据指针所指的相关地址103.JZ rel 累加器的内容为0,则跳至rel所指相关地址104.JNZ rel 累加器的内容不为0,则跳至rel所指相关地址105.CJNE A,direct,rel 将累加器的内容与直接地址的内容比较,不相等则跳至rel所指的相关地址106.CJNE A,#data,rel 将累加器的内容与常数比较,若不相等则跳至rel所指的相关地址107.CJNE @Rn,#data,rel 将寄存器的内容与常数比较,若不相等则跳至rel所指的相关地址108.CJNE @Ri,#data,rel 将间接地址的内容与常数比较,若不相等则跳至rel所指的相关地址109.DJNZ Rn,rel 将寄存器的内容减1,不等于0则跳至rel所指的相关地址110.DJNZ direct,rel 将直接地址的内容减1,不等于0则跳至rel所指的相关地址111.NOP 无动作。