cad设计二输入讲解

cad课程设计文字显示

cad课程设计文字显示一、教学目标本课程的教学目标是使学生掌握CAD软件的文字显示功能,包括文字的输入、编辑、排版和打印。

具体目标如下:1.了解CAD软件的基本操作和界面布局。

2.掌握CAD软件中文字的输入和编辑方法。

3.熟悉CAD软件中文字的排版和打印技巧。

4.能够熟练使用CAD软件进行文字输入和编辑。

5.能够合理排版和打印CAD图纸中的文字。

6.能够根据设计需求,合理选择和使用CAD软件中的文字样式和字体。

情感态度价值观目标:1.培养学生对CAD软件的兴趣和好奇心,提高学生对计算机辅助设计的认识。

2.培养学生团队合作意识和沟通能力,通过小组合作完成文字显示设计任务。

3.培养学生对设计工作的敬业精神和责任心,意识到设计工作对工程和建筑领域的重要性。

二、教学内容根据教学目标,本课程的教学内容主要包括以下几个方面:1.CAD软件的基本操作和界面布局:介绍CAD软件的启动、界面布局、工具栏和菜单栏的使用。

2.文字的输入和编辑:讲解如何在CAD软件中输入文字、编辑文字内容、调整文字样式和字体。

3.文字的排版:介绍如何调整文字的大小、位置、对齐方式以及文字的层叠和遮挡效果。

4.文字的打印技巧:讲解如何在CAD软件中设置打印参数、调整打印比例和打印样式。

三、教学方法为了提高教学效果,本课程将采用多种教学方法相结合的方式进行教学:1.讲授法:教师通过讲解CAD软件的基本操作和文字显示功能的相关知识,帮助学生建立基本概念。

2.案例分析法:通过分析实际案例,让学生了解和掌握CAD软件在实际设计中的应用方法和技巧。

3.实验法:安排实验课程,让学生亲自动手操作CAD软件,进行文字显示设计,培养学生的实际操作能力。

4.小组讨论法:学生进行小组讨论和合作,分享学习心得和设计经验,提高学生的团队合作意识和沟通能力。

四、教学资源为了支持本课程的教学,我们将准备以下教学资源:1.教材:选用权威、实用的CAD软件教程,作为学生学习的基本参考资料。

cad中基于基点的复制输入命令

CAD中基于基点的复制输入命令一、概述CAD软件作为一种专业的设计工具,为工程师和设计师提供了高效的绘图和设计功能。

在CAD软件中,基于基点的复制输入命令是一种常用的操作方式,能够帮助用户快速、精确地复制图形和元素,提高工作效率。

本文将就CAD中基于基点的复制输入命令进行详细介绍,包括命令的使用方法、注意事项和实际应用技巧。

二、基于基点的复制输入命令的使用方法1. 选择复制命令在CAD软件中,复制命令通常是通过键盘快捷键或菜单栏中的命令按钮进行选择。

用户可以使用“Ctrl+C”快捷键或者在菜单栏中点击“编辑”-“复制”命令来选择复制操作。

2. 指定基点在选择了复制命令后,用户需要指定一个基点来作为复制操作的参考点。

基点的选择对于复制操作至关重要,它决定了复制的位置和方向。

用户可以通过点击鼠标或者输入坐标值的方式来指定基点。

3. 指定目标位置在指定了基点后,用户需要指定复制的目标位置。

用户可以通过点击鼠标或者输入坐标值的方式来指定复制的目标位置,从而完成复制操作。

三、基于基点的复制输入命令的注意事项1. 确保基点选择准确在进行复制操作时,用户需要确保选择的基点准确无误,以免导致复制位置不准确或者出现错误。

2. 加强对目标位置的确认在指定目标位置时,用户需要仔细确认目标位置,避免因为位置选择错误导致复制的图形或元素位置不准确。

3. 注意坐标值的输入格式用户在输入坐标值时,需要注意坐标值的格式,确保输入的坐标值符合CAD软件的要求,避免输入错误导致操作失败。

四、基于基点的复制输入命令的实际应用技巧1. 多重复制在CAD软件中,用户可以使用基于基点的复制输入命令进行多次复制操作,只需要在完成一次复制后再次选择复制命令并指定新的目标位置即可,从而快速复制多个相同的图形或元素。

2. 镜像复制通过指定基点和目标位置的方式,用户可以实现图形或元素在不同方向上的镜像复制,从而满足不同方向的设计需求。

3. 圆心对称复制在CAD中,用户可以通过指定圆心和目标位置的方式实现圆心对称的复制操作,这种操作方式常用于圆形或弧形图形的复制。

cad软件工程制图课件教案教学设计AutoCAD建筑园林室内教程第2章绘制二维图形

(9)若设置动态数据输入方式(按下状态栏上“DYN”按钮),则可以 动态输入坐标值或长度值。下面的命令同样可以设置动态数据输入方式, 效果与非动态数据输入方式类似。除了特别需要,以后不再强调,而只 按非动态数据输入方式输入相关数据。

ห้องสมุดไป่ตู้

2.1.2 射线

射线是以某点为起点,且在单方向上无限延长的直线。 【执行方式】 命令行:RAY 菜单:“绘图”→“射线” 【操作格式】 命令: RAY↙ 指定起点:(给出起点) 指定通过点:(给出通过点,画出射线) 指定通过点:(过起点画出另一条射线,用回车结束命令)

1. 定义多线样式 【执行方式】 命令行:MLSTYLE 【操作格式】 命令: MLSTYLE↙ 系统自动执行该命令,打开如图所示的“多线样式”对话框。在该对话框中,用

户可以对多线样式进行定义、保存和加载等操作。

2. 绘制多线 【执行方式】 命令行:MLINE 菜单:“绘图”→“多线” 【操作格式】 命令:MLINE↙ 当前设置:对正 = 上,比例 = 20.00,样式 = STANDARD 指定起点或 [对正(J)/比例(S)/样式(ST)]:(指定起点) 指定下一点:(给定下一点) 指定下一点或 [放弃(U)]:(继续给定下一点绘制线段。输入“U”,则

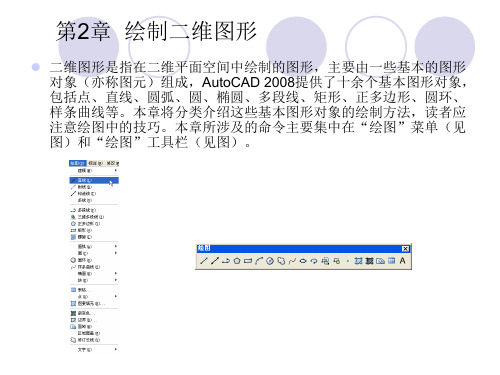

第2章 绘制二维图形

二维图形是指在二维平面空间中绘制的图形,主要由一些基本的图形 对象(亦称图元)组成,AutoCAD 2008提供了十余个基本图形对象, 包括点、直线、圆弧、圆、椭圆、多段线、矩形、正多边形、圆环、 样条曲线等。本章将分类介绍这些基本图形对象的绘制方法,读者应 注意绘图中的技巧。本章所涉及的命令主要集中在“绘图”菜单(见 图)和“绘图”工具栏(见图)。

cad软件工程制图课件教案教学设计AutoCAD建筑园林室内教程第3章二维绘制命令

图3-3 构造线

图3-4 构造线辅助绘制三视图

3.2 圆类命令

圆类命令主要包括“圆”、“圆弧”、“圆环”、 “椭圆”以及“椭圆弧”命令,这几个命令是 AutoCAD中最简单的曲线命令。

3.2.1 圆 1.执行方式

命令行:CIRCLE(快捷命令:C)。 菜单栏:选择菜单栏中的“绘图”→“圆”命令。 工具栏:单击“绘图”工具栏中的“圆”按钮 。

图3-1所示标高符号。

图Hale Waihona Puke -1 标高符号图3-2 动态输入

绘制步骤: 命令: _line 指定第一点: 100,100↙(1点) 指定下一点或 [放弃(U)]: @40,-135↙ 指定下一点或 [放弃(U)]: u↙(输入错误,取消上次操作) 指定下一点或 [放弃(U)]: @40<-135↙(2点,也可以按下状

同内外径的圆环 按<Enter>、<space>键或右击,结束命令,如图3-8(a)所示。

3.选项说明

(1)若指定内径为零,则画出实心填充圆,如图3-8(b)所示。 (2)用命令FILL可以控制圆环是否填充,具体方法如下。 命令: FILL↙ 输入模式 [开(ON)/关(OFF)] <开>:(选择“开”表示填充,选择

第3章 二维绘制命令

二维图形是指在二维平面空间绘制的图形, AutoCAD提供了大量的绘图工具,可以帮助用户完 成二维图形的绘制。用户利用AutoCAD提供的二维 绘图命令,可以快速方便地完成某些图形的绘制。 本章主要介绍直线、圆和圆弧、椭圆与椭圆弧、 平面图形和点的绘制。

3.1 直线类命令

直线类命令包括直线段、射线和构造线。这几个 命令是AutoCAD中最简单的绘图命令。

3.1.1 直线段 1.执行方式

CAD命令 文字输入全攻略

CAD命令文字输入全攻略AutoCAD软件的应用中,设计人员均需要输入各种字型的文字,以满足图形设计的需要。

我们能输入文字,但是我们输入的文字正确吗?能实现我们理想的效果吗?笔者就实践中对文字输入的一些经验提出来供大家探讨。

一、AutoCAD R14软件的“文字样式”AutoCAD R14软件中输入的文字均有一个文字的样式名,不同的样式名可设置成相同或不相同的字体。

改变文字的字体,就需要选择不同的文字样式。

文字样式的设置可在AutoCAD R14菜单的“格式文字样式”下拉菜单命令中设置。

1、样式名:显示文字的样式名称,增加、重命名、删除样式。

样式名最多可以包括 31 个字符。

字符中可以包含字母、数字、美元符号 ($)、下划线 (_)、连字符 (-) 和中文字符。

AutoCAD 将样式名中的小写字母自动转换为大写字母。

考虑到人们的使用习惯,建议用直观的中文字符样式名。

2、字体: 通过改变不同的字体名、字体样式、高度来修改文字样式使用的字体。

“字体名”列表框内列出了在WINDOWS9.X系统中已注册的 TrueType 所有字体(字体名前以T符号标示)和AutoCAD软件 Fonts 目录下已编译的所有形 (SHX) 字体的字体名。

TrueType字体为微软公司和Apple公司共同研制的字型标准。

图形中的 TrueType 字体是以填充的方式显示出来,在打印时,TEXTFILL 系统变量控制该字体是否填充。

TEXTFILL 系统变量的缺省设置为1,这时打印出填充的字体。

SHX形字体属于“矢量字形”,是一种用形状或方程来描述字符轮廓的字符形式。

这种字形的优点是在显示时字符可以任意缩小或放大,缺点是需要作大量处理。

在选择SHX字体后,应选取“大字体”选项指定亚洲语言(包括简、繁体汉语、日语、韩语等)的大字体文件,已便使用正确的亚洲语言字体。

只有在“字体名”中指定SHX 文件,才可以使用“大字体”选项,只有 SHX 文件可以创建“大字体”。

CAD建筑设计实例解析与讲解

CAD建筑设计实例解析与讲解一、引言CAD建筑设计软件是现代建筑师必备的工具之一,它可以在设计和制图过程中提供高效且准确的支持。

本文将通过解析一个建筑设计实例,来讲解CAD软件的使用技巧和设计方法。

二、设计实例解析下面我们以一座办公楼的设计为例,来进行CAD建筑设计实例的解析。

1. 建筑平面设计在进行建筑平面设计时,我们可以通过CAD软件来进行多种操作。

首先,可以绘制建筑物的立面图,以确定其形状和结构。

其次,可以绘制建筑物的平面布局,包括办公室、会议室、厕所等功能区域的设计。

此外,还可以进行灯光和电气布局、通风系统设计等。

2. 三维建模CAD软件可以将平面图转化为三维模型,使设计师能够更加直观地观察建筑物的外观和内部结构。

通过添加材质、颜色和纹理等,可以更加真实地呈现建筑物的细节。

3. 可视化仿真CAD软件还可以进行可视化仿真,用于模拟建筑物在不同光照、气候条件下的效果。

这有助于设计师更好地评估建筑物的外观和功能,并进行必要的调整。

4. 施工图制作CAD软件对建筑施工图的制作具有很大的支持作用。

通过CAD软件,可以将设计图纸转化为施工图,包括各种工程标注和细节设计。

此外,CAD软件还可以与其他工程软件进行集成,以提供更全面的施工信息。

5. 数据分析与优化CAD软件还可以进行建筑物的数据分析和优化。

通过输入建筑物的材料、结构和环境参数,CAD软件可以进行力学分析、能耗分析等,以评估建筑物的性能,并提供改进建议。

三、使用技巧在进行CAD建筑设计时,我们还需掌握一些使用技巧,以提高工作效率和设计质量。

1. 快捷键的使用掌握CAD软件的各种快捷键可以大大提高绘图效率。

在绘制过程中,可以使用快捷键来选择工具、调整视图、复制和移动对象等操作。

2. 图层管理合理的图层管理可以使绘图更加清晰和易于修改。

将不同类型的对象分配到不同的图层中,可以方便地对其进行编辑和显示。

3. 块的使用块是将多个对象组合成一个整体以便复用的对象。

CAD常用特殊符号输入

CAD常用特殊符号输入在使用 CAD 软件进行绘图设计的过程中,经常会遇到需要输入特殊符号的情况。

这些特殊符号可能是一些数学符号、标注符号、电气符号等等。

熟练掌握这些特殊符号的输入方法,能够大大提高我们的绘图效率和质量。

接下来,就为大家详细介绍一下 CAD 中常用特殊符号的输入方法。

一、数学符号1、直径符号“Φ”在 CAD 中,输入直径符号“Φ”可以通过以下几种方式:(1)在单行文字输入时,输入“%%C”,然后回车,即可得到直径符号“Φ”。

(2)在多行文字输入框中,选择“符号”选项,在弹出的符号列表中找到直径符号“Φ”进行插入。

2、度数符号“°”要输入度数符号“°”,可以这样操作:(1)在单行文字中输入“%%D”,回车即可。

(2)在多行文字中同样通过“符号”选项插入。

3、正负号“±”输入正负号“±”的方法为:(1)单行文字输入“%%P”,回车。

(2)多行文字中从“符号”里选择。

二、标注符号1、粗糙度符号粗糙度符号在 CAD 中的输入相对复杂一些。

通常需要先创建一个块,将粗糙度符号定义为块,然后在需要的位置插入该块。

也可以通过加载专门的粗糙度符号库来直接调用。

2、焊接符号焊接符号的输入也需要借助特定的符号库或者通过自定义块来实现。

在一些专业的 CAD 插件中,会提供丰富的焊接符号供选择和输入。

三、电气符号1、电阻符号“Ω”输入电阻符号“Ω”,可以使用以下方法:(1)单行文字输入“%%O”,回车。

(2)多行文字中从“符号”里选取。

2、电容符号电容符号在 CAD 中的输入方式与电阻符号类似,也是通过特定的代码或者从符号列表中选择。

四、其他特殊符号1、分数在 CAD 中输入分数,可以使用“堆叠”功能。

例如,要输入“1/2”,先输入“12”,然后选中“12”,点击堆叠按钮(通常在多行文字编辑框的格式选项中),就可以得到分数“1/2”的效果。

2、上标和下标对于需要输入上标或下标的情况,同样在多行文字编辑框中进行操作。

在cad中输入坐标的方法步骤

在cad中输入坐标的方法步骤

cad是应用最广泛的计算机辅助设计软件,学会cad如何输入坐标是必不可少的,那么大家知道怎么在cad中输入坐标吗?下面是店铺整理的怎么在cad中输入坐标的方法,希望能帮到大家!

在cad中输入坐标的方法一

1.想要学会cad如何输入坐标就要知道cad绝对坐标和cad相对坐标。

绝对坐标就是相对于cad原点的坐标。

2.cad如何输入绝对坐标呢,在cad工具栏中选择直线工具,或者输入cad直线工具快捷键L,然后按回车键确定。

3.现在需要指定直线的第一点,在命令行中输入绝对坐标“100,100”,然后按回车键确定。

4.此时cad直线的第一点就定位在绝对坐标“100,100”处了。

在cad中输入坐标的方法二

以A(3934023.475,495715.674),B(3926619.74,495404.801)为公路线性区域的起终点为例,坐标系原点宜建立在区域的中间位置。

第一步:输入命令UCS回车,出现提示,在后面输入坐标原点位置(-495400,-3930400,,0)回车(注:在CAD中输入时不带括号)。

第二步:会弹出提示输入X轴上一点,在提示后输入(495700,0,0)回车。

第三步:会弹出提示输入XY平面上一点,在提示后输入(0,3934000,0)回车坐标系建立成功希望对你能有所帮助。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《集成电路CAD》课程设计报告》——两输入或非门的设计班级:学号:姓名:指导教师:一、设计要求(1)绘制电路图a、明确电路结构;b、明确电路中器件的类型、数目;c、明确电路中端口的数目以及所联接的信号类型;d、确定MOS的宽长比,确定MOS管的尺寸,沟长采用所用工艺规定的最小条宽的整数倍。

(2)根据电路结构绘制版图在正确的电路结构基础上,绘制版图:a、要求版图中电路的元件数目、类型以及尺寸与所画电路结构保持一致;b、要求元件之间连接正确,并与所确定电路结构保持一致;c、要求版图中电路的端口数目、位置与所确定电路保持一致;(3)DRC验证绘制版图后要进行DRC验证:a、采用DRC规则文件对绘制版图进行DRC校验;b、根据校验提示语句修改版图直至正确为止,提交正确的DRC校验结果。

(4)撰写课程设计报告按以下要求书写:a、报告严格按照以下提供模板格式书写;b、报告内容要含有原电路电路图以及所绘制版图的截图;c、报告内容要含有DRC校验结果(相关截图以及文件)。

二、设计目的1、熟悉candence软件,并掌握其各种工具的使用方法。

2、用cadence设计一个三输入或非门,并画出仿真电路、版图、并验证其特性。

三、设计的具体实现1.电路概述二输入或非门有两个输入端A和B以及一个输出端Q,当A端或B端为高电平时输出为低电平,当两个输入都为低电平输出才为高,表达式如下所示:=Y+AB或非门的电路符号和真值表如图1所示:图2由于此次是用CMOS管构建的二输入或非门,而CMOS管的基本门电路有非门、与非门、或非门等,所以直接用CMOS管搭建出二输或非门电路。

原理图如图二所示。

2.cadence简介:Cadence公司的电子设计自动化(Electronic Design Automation)产品涵盖了电子设计的整个流程,包括系统级设计,功能验证,IC综合及布局布线,模拟、混合信号及射频IC设计,全定制集成电路设计,IC物理验证,PCB设计和硬件仿真建模等。

本次设计是基于cadence工具的三输入或非门的电路和版图设计。

3.两输入或非门电路设计和逻辑仿真进入红帽4系统,打开终端输入cd Artist446进入Artist446目录,输入icms &命令运行Cadence软件。

在打开的CIW的窗口选择tools →Library Manager建立一个新的库文件myLib,在创建一个新的cellview(1)在schematic窗口中选择Tools →Analog Evironment,打开模拟窗口(2)setup →simulator /directory/host…,在弹出窗口中确认simulator项是spectre.单击ok。

(3)setup →Model Library setup,做如下输入,然后add。

选择Analyses →Choose,在坦诚的窗口中吧stop time设为50u(4)选择outputs →save all.1、选择outputs →to be plotted →select on schematic,然后在schematic窗口中依次选择A、B、C、Y为输入和输出,选择之后按ESC。

(5)选择完毕后窗口如下图所示(6)选择Simulation →Netlist →Create(7)选择Simulation →Run4.版图设计:登录Linux系统,启动终端,cd Layout进入版图目录,然后以layoutPlus &运行版图设计软件,进行版图设计。

nmos版图设计设计规则(允许的最小尺寸)1.n diff overlap of contact 0.9u2.c ontact minimum width 0.6u3.c ontact spacing 0.6u4.c ontact to gate spacing 0.6u5.p oly extension 0.6u6.m etal overlap of contact 0.4u[1]、在CIW窗口中,选择File →Open (若无nmos Cell,则建立New),打开nmos版图设计窗口,参数如下:Library Name designCell Name nmosView Name layoutOK[2]、画poly:在LSW窗口中选择poly dg为当前层,Create →Path 画出nmos的门极,按回车或双击鼠标完成绘制。

[3]、画ndiff:在LSW中选择ndiff dg为当前层,Create →Rectangle 画一矩形。

Edit →Move 移动ndiff层,把它放在合适的位置。

[4]、画nmos器件源、漏极的外连接contact:metal1 dg为当前层,在源、漏极画尺寸为1.4um*2.6um的矩形;contact dg为当前层,在源、漏极各画两个尺寸为0.6um*0.6um的contact。

[5]、选择Window →Create Ruler,并配合Stretch命令调整版图。

[6]、Save存盘,关闭nmos版图窗口。

pmos版图设计设计规则:1.nwell overlap of pdiff 0.4u2.pdiff overlap of contact 0.9u3.contact minmum width 0.6u4.contact spacing 0.6u5.contact to gate spacing 0.6u6.poly extension 0.6u7.metal overlap of contact 0.4u[1]、利用已经画过的nmos来生成pmos,在CIW命令窗口中选择Tools ——Library Manager命令,选中nmos打开它的复制窗口,复制到pmos中。

[2]、打开pmos的版图,选中n型注入的矩形,利用Edit——Properties命令,将n型注入改成p型注入。

[3]、选中p型注入的矩形,利用Create——Layer Generation命令,在p型注入的矩形外生长0.4u的n阱。

[4]、根据设计规则调整pmos大小。

[5]、建立一个接触孔的平面数组来复制接触孔,使其生成最终符合规则的pmos器件并保存。

利用已生成的nmos和pmos的版图来绘制两输入或非门的版图1、打开nand3的空白版图设计窗口。

2、选择Create——Instance命令,在Create Instance窗口中设置成如下形式:在版图上点击一下,将nmos放置到版图上。

3、同样方法放置pmos,参数如下:4、将metal1置为当前层,根据设计规则画出电源和地线。

5、用Create——Path命令画出输出连接,用Create——Rectangle命令画出电源和地的连接。

6、将poly置为当前层,用Create——Path命令画出门极连接。

7、用Create——Pin命令在版图上加入A, B.C,Y的引脚。

8、用Create——Contact命令将NTAP和PTAP放置在电源线和地线上。

9、调整坐标位置并保存。

5.版图设计以及DRC校验首先打开Cadence16.5选择其中的Design Entry CIS子软件,在弹出的窗口中选择orCAD Capture CIS,如下图9所示:图9进入工作界面之后在菜单栏中选择File按钮然后选择New选项下面的子选项Project来建立新的工程,如下图10所示:图10点击OK之后就能进入工作界面,如下图11所示:图11点击菜单栏中的Place按钮选择Part选项调出元件库,然后点击右边中的处加载需要用到的一些元件库。

从组件库引用模块:编辑反相器电路会利用到NMOS, PMOS, Vdd 与Gnd 这4 个模块,所以要从组件库中复制NMOS, PMOS, Vdd 与Gnd 这4 个模块到文件,并在PAGE1编辑画面中引用。

最后画好的版图如下图3中所示:图3或非门版图选择Tools/DRC命令,打开Design Rule Check对话框,选中Write errors to files复选框将错误项目记录到yumen.drc文件或自行取文件名,单击“确定”按钮,进行设计规则检查,结果如图24中所示图24从图28中可以看到,整个与门电路的版图DRC没有错误,然后接下来就能生成SPC文件了。

执行Tools/Extract命令或单击图标,打开Extract对话框,在Extract definition file栏内选择X: \Ledit11.1\Samples\ SPR\example1\lights.ext文件,如下图所示。

选择Output标签页,在“Comments”栏中,选择Write nodes name选项,在“Write nodes and devices as”栏内选中Names项,即设定输出节点以名字出现,并在SPICE include statement栏内输入“.include X: \Tspice81\models\m12_125.md”,然后单击Run按钮,即可提取yumen.spc 文件,执行命令,打开yumen.spc文件。

四、结论与展望此次课程设计在老师的悉心指导,同学们的热情帮助下,我已圆满完成了本次课程设计的要求。

从课题选择到具体构思和内容以及数据的测试,我深刻体会到做事情不能急躁,从电路原理图的绘制到仿真,再到版图的制作,每一步都要要细心仔细的去完成。

在这周时间所经历的学习和生活,我深刻感受到老师的精心指导和无私的关怀,让我受益匪浅。

本次课程设计的名称为“二输入与门电路设计”,经过此次课设使我对Cadence软件和L-Edit软件的使用都有了更深刻的了解,这将对我以后的学习和工作带来莫大的帮助。

随着微电子技术的快速发展,人们生活水平不断提高,使得科学技术已融入到社会生活中每一个方面。

而对于现代信息产业和信息社会的基础来讲,集成电路是改造和提升传统产业的核心技术。

随着全球信息化、网络化和知识经济浪潮的到来,集成电路产业的地位越来越重要,它已成为事关国民经济、国防建设、人民生活和信息安全的基础性、战略性产业。

门电路是构成各种复杂数字电路的基本逻辑单元,CMOS门电路作为目前应用最广的门电路之一,掌握CMOS门电路的逻辑功能和电气特性,对于正确使用数字集成电路是十分必要的。

CMOS门电路是以金属—氧化物—半导体场效应晶体管作为开关器件的集成电路。

与TTL门电路相仿,在CMOS门电路的定型产品中有反相器(非门)、与门、或门、与非门、或非门、与或非门和异或门几种常见的类型。

输入端、输出端的电路结构也分为多种形式,比如单端输入单端输出、双端输入单端输出、三输入、四输入等。

五、致谢四年的大学生活接近尾声,首先,要感谢所有教过我的老师,不论是在学习,还是在生活上,谢谢您们付出的点点滴滴,指引我前进的道路。