网上下载的一个三分频电路说明

3分频电路

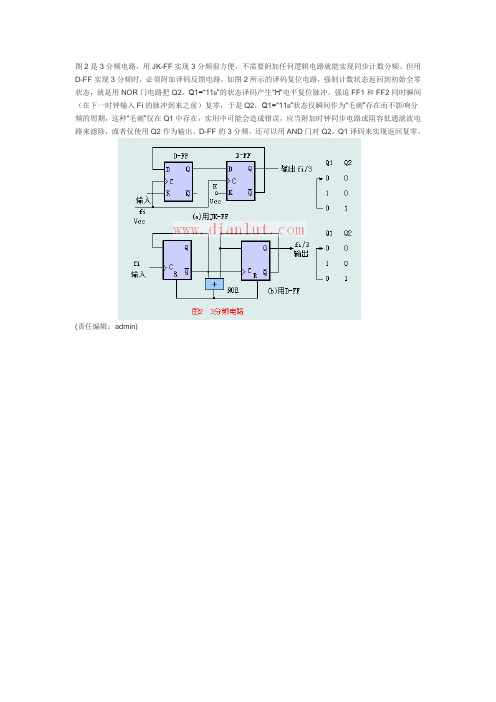

图2是3分频电路,用JK-FF实现3分频很方便,不需要附加任何逻辑电路就能实现同步计数分频。

但用D-FF实现3分频时,必须附加译码反馈电路,如图2所示的译码复位电路,强制计数状态返回到初始全零状态,就是用NOR门电路把Q2,Q1=“11B”的状态译码产生“H”电平复位脉冲,强迫FF1和FF2同时瞬间(在下一时钟输入Fi的脉冲到来之前)复零,于是Q2,Q1=“11B”状态仅瞬间作为“毛刺”存在而不影响分频的周期,这种“毛刺”仅在Q1中存在,实用中可能会造成错误,应当附加时钟同步电路或阻容低通滤波电路来滤除,或者仅使用Q2作为输出。

D-FF的3分频,还可以用AND门对Q2,Q1译码来实现返回复零。

(责任编辑:admin)。

自制前级三分频功放

自制前级三分频功放笔者介绍的是三分频功放,电路见图1,其缩小印板图见图2。

印刷电路的设计思路电子元件的定位以最短信号线布局,舍去为使阻容件列队好看而走曲径的做法。

为避免功放电源做在功放板上距分频电路过近造成干扰,电源单独制作,在距电源远点供电处增加滤波组件。

分频电路四周以地线与功放电路隔离,左右声道接地分开。

各功放元件接地后各行其道,汇一处后,各声道地及喇叭接地汇总于电源地。

因而,本电路噪声背景十分干净。

分频点的计算可用公式f=1/2πRC计算分频网络元件值,笔者用该公式在一些电路中得到了验证。

本电路取fL=800Hz,fH=5kHz,如R2取5.6k时,则C3=C4=1/(2πR2fL)=0.036uF。

IC1b、C6、C7、R6、R7和IC3a、R8、R9、C8、C9组成800Hz~5kHz的带通滤波器。

元器件的选取分频核心件IC选用OP275。

W为音量控制,w1、W2、W3分别为L、Z、H声道增益控制,用以调整整体音响的平衡度,一次调好不必再动。

首选音质细腻通透的TDA7294做L通道功放。

音色温暖亮丽的双功放LM4766做Z、H通道功放最为合适,实践证明,完全消除了用LM3886担当此任音质沉闷的感觉。

每块功放用8cmx8cm的肋式散热器,使用中没有明显的温升现象,全电路见图1。

试机及随想笔者曾按《电子报》刊出电路多次制作电路板,感受之深莫过于此。

本电路的制作是以《电子报》上刊登的《三声道功率放大器》(以下简称“三电路”)文中电路为据制板,当焊接完毕后通电试机,却立烧AC保险。

查知该板正负电源电路之间正反向电阻均为32Ω!切开TDA7294供电电路后分别测试又都正常,并接后再测依旧,再切开,仔细测量发现,TDA72942正负供电电路的正向电阻远大于反向电阻,怀疑正负脚反接。

查阅其他资料,是《三电路》的⑧、15脚及⑦、13脚分别错接到电源的正负极上,造成正反电阻异常,不得已切断铜箔,改接。

Verilog实现三分频的多种方法(附有代码)

Verilog实现三分频的多种方法(附有代码)用Verilog语言实现奇数倍分频电路 3分频 5分频 7分频分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如altera 的PLL,Xilinx的DLL.来进行时钟的分频,倍频以及相移。

但是对于时钟要求不高的基本设计,通过语言进行时钟的分频相移仍然非常流行,首先这种方法可以节省芯片内部的锁相环资源,再者,消耗不多的逻辑单元就可以达到对时钟操作的目的。

另一方面,通过语言设计进行时钟分频,可以看出设计者对设计语言的理解程度。

下面讲讲对各种分频系数进行分频的方法:第一,偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去,这种方法可以实现任意的偶数分频。

第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频有两种实现方法:首先,占空比不限定时,完全可以通过计数器来实现,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转。

这样实现的三分频占空比为1/3或者2/3。

如果要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

这种方法可以实现任意的奇数分频。

归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

分频电路

仿真波形

CLK

上பைடு நூலகம்沿Q1 上升沿Q0

下降沿Q1 下降沿Q0 Q1“相或” Q0 “相或”

举一反三

实现任意的奇数分频。归类的一般方法为:对 于实现占空比为50%的N倍奇数分频. 步骤:1. 进行上升沿触发进行模N计数,计数选 定到某一个值进行输出时钟翻转,然后经过(N1)/2再次进行翻转得到一个占空比为非50%的 奇数N分频时钟, 2.同时进行下降沿触发的模N计数,同理。 3.两个占空比非50%的N分频时钟相或运算 得到占空比为50%的奇数N分频时钟。 注意:“相或“的两端要适当选取,例如N=5时 选Q1;N=7时,选Q2;N=15时,选Q3。

分频电路部分:采用格雷码计数器,可有效的避免毛刺现象的发生。 格雷码跳变顺序:001—011—010—110—111—101 (Q2Q1Q0) 用卡诺图化简之后的逻辑表达式:Q*2=Q2Q1+Q1Q’0 Q1=Q’0Q1+Q’2Q0 Q0=Q’1Q0+Q2Q1

由于所选择的格雷码没有000状态,所以需保证起始状态不能为000, 则多了一个d高电平,用来控制起始状态。 q2的输出即是对时钟信号clk三分频之后的信号波形。

占空比为1:1的奇数分频电路的实现:

方法三:利用如下电路实现

输入时钟频率:CLK。器件:一个非与门,两个D触 发器,分别为D1(输入), Q1(输出)和D2,Q2 注意:开始要复位触发器。 D0=Q0*=A’ AND B’

D1=Q1*=A Clk3*=(CLK+B’)AND(A+clk3)

错位相或法

以3分频为例: 首先设计模三的计数器,其真值表如下:

最新三分频扬声器系统分频器电感的精确设计

三分频扬声器系统分频器电感的精确设计三分频扬声器系统分频器电感的精确设计1 引言扬声器系统的分频器分为前级分频和功率分频2类。

前级分频是前级电路中由电子元件产生的分频,再由各自的功放分别驱动高﹑中﹑低音扬声器系统,如图(1a)所示,属于小信号有源分频。

而功率分频则是由电感、电容、电阻元件构成的位于功放与扬声器之间的无源分频电路,如图(1b)所示。

采用功率分频的扬声器系统结构简单、成本低,而且又能获得很高的放音质量,因而在现代高保真放音系统中应用最为普遍。

其性能的好坏与扬声器的各项指标以及分频电路、电感元件的性能、精度有密不可分的关系,精确计算电感参数便是成功的关键。

2 对分频器电路、元件的要求(1)电路中电感元件直流电阻、电感值误差越小越好。

而且为使频响曲线平坦最好使用空心电感。

(2)电路中电容元件损耗尽可能小。

最好使用音频专用金属化聚丙烯电容。

(3)使各扬声器单元分配到较平坦的信号功率,且起到保护高频扬声器的作用。

(4)各频道分频组合传输功率特性应满足图2所示特性曲线的要求(P0为最大值,P1为对应分频点f1、f2的值)。

分频点处的功率与功率最大值之间幅度应满足P1(=0.3~0.5)P0的范围。

(5)整个频段内损耗平坦,基本不出现“高峰”和“深谷”。

3 分频电感电容参数值的计算下面以三分频分频器为例说明其参数的计算,如图3所示。

1)计算分频电感L1,L2,L3,L4和分频电容C1,C2,C3,C4。

为了得到理想的频谱特性曲线,理论计算时可取:C1=C4,C3=C2,L1=L3,L4=L2,分频点频率为f1,(f2见图2),则分频点ω1=2πf0,ω2=2πf2。

并设想高、中、低扬声器阻抗均相同为RL。

每倍频程衰减12 dB。

2)实验修正C1,C2,C3,C4,L1,L2,L3,L4的值为精确起见,可用实验方法稍微调整C1,C2,C3,C4,L1,L2,L3,L4的值,以满足设计曲线﹙见图2﹚的要求。

三段音调电路的分频点

三段音调电路的分频点1.引言1.1 概述概述部分的内容:音调电路是一种常见的电子设备,广泛应用于音乐器材、配音设备和音频处理等领域。

在音乐制作和音频处理过程中,分频点是一个重要的参数,它决定了音频信号在频域上的划分和处理方式。

三段音调电路是一种常见的分频电路,它能够将输入的音频信号按照频率划分成三个不同的频段,并对每个频段进行独立的调节。

本文将在引言部分对三段音调电路的概念和作用进行介绍。

随后的正文部分将详细阐述三段音调电路的原理和分频点的定义与作用。

最后的结论部分将对三段音调电路的特点进行总结,并探讨不同分频点对音调产生的影响。

通过本文的阅读,读者将能够深入了解三段音调电路的工作原理和分频点的重要性。

同时,读者还将了解到不同分频点对音调的影响,并能够根据实际需求进行合理的选择和调节。

希望本文能够为读者提供有关三段音调电路的全面理解和应用指导。

1.2 文章结构文章结构指的是文章的组织框架和内容安排,它对于读者理解文章的逻辑结构和脉络十分重要。

本文的结构分为三个主要部分:引言、正文和结论。

在引言部分,首先对三段音调电路的概述进行了介绍,说明了该电路的主要特点和应用背景。

接着,明确了本文的结构和内容安排,即引言、正文和结论。

最后,阐明了本文的目的,即探讨分频点对三段音调电路的影响。

在正文部分,首先对三段音调电路的原理进行了阐述,介绍了音调电路的工作原理和基本组成部分。

其次,详细说明了分频点的定义和作用,解释了分频点在音调电路中的重要性和作用。

在结论部分,对三段音调电路的特点进行了总结,简要概括了该电路的特点和优势。

同时,探讨了不同分频点对音调产生的影响,说明了分频点选择对音调效果的重要性。

通过以上的文章结构,读者能够清晰地了解到本文的思路和组织,有助于更好地理解和把握文章的内容和要点。

1.3 目的本文旨在探讨三段音调电路的分频点对音调产生的影响,并分析不同分频点选取的理由。

通过对三段音调电路原理和分频点的定义与作用的介绍,我们可以更深入地理解和认识这一电路设计中的关键要素。

通用型音箱三分频器的制作

通用型音箱三分频器的制作音箱是音频设备中的关键组成部分,负责将信号转换为声音输出。

在音箱中,三分频器是一种重要的电路组件,用于将输入的音频信号分成低频、中频和高频三个频段进行处理,从而使音质更加清晰和平衡。

本文将介绍如何制作一个通用型音箱三分频器。

材料准备:1.电容器:选择合适的电容器用于分频电路的设计,常见的有陶瓷电容、薄膜电容和电解电容等。

2.电感器:选择适合的电感器用于分频电路的设计,常见的有蜡线电感和铁氧体电感等。

3.电阻器:选择合适的电阻器用于分频电路的设计,常见的有金属膜电阻和炭膜电阻等。

4.音箱和喇叭单元:选择合适的音箱和喇叭单元,以满足所需的音频输出要求。

5.音频线:用于连接音源和音箱的音频线。

步骤:1.确定频率范围:根据所需的音频输出要求,确定低频、中频和高频的分界频率。

通常情况下,低频分界频率为20Hz-200Hz,中频为200Hz-2kHz,高频为2kHz-20kHz。

2.计算电容器和电阻器数值:根据所选定的分界频率,使用以下公式计算所需的电容器和电阻器数值:-低频段:C=1/(2πfL)-中频段:C=1/(2πfL)-高频段:C=1/(2πfL)其中C为电容器的值,f为分界频率,L为电感器的值。

3.搭建分频电路:根据计算得到的数值,使用电容器、电感器和电阻器在电路板上搭建三个分频电路。

分频电路的原理是通过电容器、电感器和电阻器的组合,将不同频率的信号分到不同的通道中。

4.连接音箱和喇叭单元:将制作好的分频电路连接到音箱和相应的喇叭单元上。

低频信号通过低频分频电路传递到低音单元,中频信号通过中频分频电路传递到中音单元,高频信号通过高频分频电路传递到高音单元。

5.连接音源:将音源通过音频线连接到音箱的输入端口上,确保音箱与音源正常连接。

注意事项:1.在制作分频电路时,应选用合适的组件,以确保电容器和电感器的功能和性能符合所需的要求。

2.在连接分频电路和音箱时,应确保连接的稳固可靠,以确保音频信号的正常传输。

三分频器电路

三分频器电路三分频器是一种常用的电路,用于将输入信号分成三个相等的输出信号。

它在很多电子设备中都有广泛的应用,比如音频放大器、通信系统和信号处理器等。

三分频器电路的基本原理是利用滤波器和分频器的组合。

滤波器用于分离不同频率的信号,而分频器则将输入信号分成多个频率相等的信号。

三分频器电路一般由低通滤波器、带通滤波器和高通滤波器组成。

低通滤波器用于传递低频信号,带通滤波器用于传递中频信号,高通滤波器用于传递高频信号。

在三分频器电路中,输入信号首先经过一个低通滤波器。

低通滤波器的作用是将高频信号滤除,只保留低频信号。

然后,低通滤波器的输出信号经过一个带通滤波器。

带通滤波器的作用是将中频信号滤除,只保留高频信号和低频信号。

最后,带通滤波器的输出信号再经过一个高通滤波器。

高通滤波器的作用是将低频信号滤除,只保留高频信号。

三分频器电路的设计需要考虑滤波器的特性和频率范围。

滤波器的特性可以通过选择合适的电容和电感来实现。

频率范围则是根据应用需求来确定的,可以根据需要选择不同的滤波器参数。

三分频器电路的应用非常广泛。

在音频放大器中,三分频器可以将音频信号分成低频、中频和高频三个部分,分别经过不同的放大电路进行放大,然后再合并成一个完整的音频信号。

在通信系统中,三分频器可以将信号分成不同的频率段,分别进行处理和传输。

在信号处理器中,三分频器可以将输入信号分成不同频率的信号,然后进行不同的处理操作。

三分频器是一种重要的电路,它可以将输入信号分成三个相等的输出信号。

它在音频放大器、通信系统和信号处理器等电子设备中都有广泛的应用。

通过合理设计滤波器和分频器,可以实现不同频率信号的分离和处理。

三分频器的应用范围非常广泛,可以满足各种不同的需求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

always@( negedge resetn or posedge clk or negedge clk) begin

if (resetn==1'b0)

begin

counter[2:0]<=3'd0;

out_clk<=1'b0;

end

else

begin

if (counter[2:0]==3'd5)

begin

counter[2:0]<=3'd0;

end

else

beign

counter[2:0]<= counter[2:0]+1;

end

////////////////////////////////////////////////////

if (counter[2:0]==3'd5 || counter[2:0]==3'd2)

begin

out_clk<=~out_clk;

end

end

end

其仿真结果是正确的

这个逻辑无法综合。

存在半导体工艺问题。

2.下面给出一个逻辑图。

逻辑是用器件画出来的,保证不存在物理上的实现问题。

仿真图如下:

也许有人要问,既然仿真都是对的,那么为什么要说实际中是80%工作呢?

看到波形图上的clk1(黄色)上的那些毛刺了么,毛刺并不可怕,但是这个电路工作的基础却是那些毛刺,准确地说,那些毛刺是必须有的,是工作过程的比不可少的部份。

这样的电路是否能正常工作就很让人匪夷所思了。

我们能不能让电路的正常功能不依赖于毛刺呢?

小结一下:

以上的思路都是试图在输入的clk上做改造,试图在恰当的地

方取正沿,恰当的地方取反沿。

但是要知道,这一定会导致竞争和冒险。

虽然逻辑上是可性的,但是实践中却没有那么简单。

这个时候,我们需要调整一下思路了:

能不能营造一个安全的时机来切换时钟沿的选择?显然,这需要在切换时钟沿时,强制时钟输出固定电平,当切换完成后,在取消这个强制条件。

对么?我们来试试看。

3. 看看以下的代码,也是一段有趣的东西。

always@(negedge resetn or posedge clk)

begin

if (resetn==1'b0)

begin

cnt1[1:0]<=2'd0;

end

else

begin

if(cnt1[1:0]==2'd2)

begin

cnt1[1:0]<=2'd0;

end

else

begin

cnt1[1:0]<=cnt1[1:0]+1;

end

end

end

always@(negedge resetn or negedge clk)

begin

if (resetn==1'b0)

begin

cnt2[1:0]<=2'd0;

end

else

begin

if(cnt2[1:0]==2'd2)

begin

cnt2[1:0]<=2'd0;

end

else

begin

cnt2[1:0]<=cnt2[1:0]+1;

end

end

end

always@*

begin

if (cnt1[1:0]==2'd2 || cnt2[1:0]==2'd0)

begin

clk1 = 1'b0;

end

else if (cnt1[1:0]==1'b1)

begin

clk1 = ~clk;

end

else

begin

clk1 = clk;

end

end

always@(negedge resetn or posedge clk1)

begin

if (resetn==1'b0)

begin

clk_out<=1'b0;

end

else

begin

clk_out<=~clk_out;

end

end

最后用的时钟clk1是clk和clk的反,但是在切换之间加上的强制为0的逻辑。

这段代码肯定是可综合的,而且简单的约束一下时序就可以生产。

但重要的是看了这段逻辑后我们突然明白了一件事情:要想长生质量好的3分频时钟,我们似乎必须要用到clk的下降沿来做点控制逻辑,这是被反复求证后逼出来的(不知道其它人是否有同感)。

那么我们为什么不愿意用下降沿触发的的寄存器呢?因为有些库里可能没有这样的器件,而必须在时钟树上上加反向。

如果有下降沿的寄存器,那么今后的扫瞄链又要多一些麻烦,虽然这些麻烦都可以客服,但是作为一个成熟的工程师要明白:尽量不要给自己找麻烦。

在工程上,最平常的东西最可靠。

4. 到这里我们的命题似乎解决了,但是我们的思考还不应该停止。

既然我们要用clk的下降沿,呢就完全可以打破以前的思路,来看看这个新的手段能给我们带来什么。

always@(negedge resetn or posedge clk)

begin

if (resetn==1'b0)

begin

cnt1[1:0]<=2'd0;

clk1<=1'b0;

end

else

begin

if(cnt1[1:0]==2'd2)

begin

cnt1[1:0]<=2'd0;

clk1<=1'b1;

end

else

begin

cnt1[1:0]<=cnt1[1:0]+1;

clk1<=1'b0;

end

end

end

always@(negedge resetn or negedge clk)

begin

if (resetn==1'b0)

begin

clk2<=2'd0;

end

else

begin

clk2<=clk1;

end

end

assign clk_out = clk1 | clk2;

代码似乎更简单了,思路也完全变了。

这回的思路是:先做一个简单的3分频电路,然后再调整占空比。

以这个思路,所有的1/N分频都可以解决。