相关导通阻抗标准

电阻、电感、电容的等效阻抗计算及应用

--是一单向导电器件(无正向阻断能力);

--为不可控器件,由其两断电压的极性控制通断,无其它外部控制;

--普通二极管的功率容量很大,但频率很低;

--开关二极管有三种,其稳态特性和开关特性不同:

--快恢复二极管;

--超快恢复,软恢复二极管;

--萧特基二极管(反向阻断电压降<<200V,无反向恢复问题);

功率MOSFET的反向导通等效二极管的等效电路,可用一电压降等效,此二极管为MOSFET的体二极管,多数情况下,因其特性很差,要避免使用。

功率MOSFET的反向导通等效电路(2)

(1):等效电路(门极加控制)

(2):说明:功率MOSFET在门级控制下的反向导通,也可用一电阻等效,该电阻与温度有关,温度升高,该电阻变大;它还与门极驱动电压的大小有关,驱动电压升高,该电阻变小。详细的关系曲线可从制造商的手册中获得。此工作状态称为MOSFET的同步整流工作,是低压大电流输出开关电源中非常重要的一种工作状态。

功率MOSFET的正向截止等效电路

(1):等效电路

(2):说明:功率MOSFET正向截止时可用一电容等效,其容量与所加的正向电压、环境温度等有关,大小可从制造商的手册中获得。

功率MOSFET的稳态特性总结

(1):功率MOSFET稳态时的电流/电压曲线

(2):说明:功率MOSFET正向饱和导通时的稳态工作点:

当门极不加控制时,其反向导通的稳态工作点同二极管。

(3):稳态特性总结:

--门极与源极间的电压Vgs控制器件的导通状态;当VgsVth时,器件处于导通状态;器件的通态电阻与Vgs有关,Vgs大,通态电阻小;多数器件的Vgs为12V-15V,额定值为+-30V;

FPC可靠度测试规范

FPC可靠度测试规范1. 目的建立本公司产品可靠度验证标准。

2. 适用范围:a. 新产品开发可靠度验证b. 新材料评鉴时可靠度验证c. 制程变更之可靠度验证d. 其它必要之成品、半成品或原材料之可靠度验证当客户对我司所交付之产品可靠度验证另有要求且与本文所列不一致时,应依客户的规格或要求执行相关的测试及检验。

本规范中部分测试因公司暂不具备测试资源,客户有要求时须委外测试或委托客户代为测试。

3. 参考文件:3.1 JIS C 50163.2 JIS C 64713.3 IPC-60133.4 IPC –TM-6504. 职责:4.1 实验室可靠度测试人员:负责进行可靠度测试的操作,结果判定,出具报告。

测试人员必须经过相关培训,掌握本文所列之各种测试方法及判定标准,并经实验室主管考核评定合格后方可具备测试资格。

4.2 实验室主管负责可靠度测试的监督管理,报告审核,以及人员培训,资格鉴定。

可靠度测试不合格时的改善措施追踪等。

6. 可靠度测试内容6.1 镀层密着性测试(Adhesion of plating)6.1.1 测试目的验证产品镀层密着性。

6.1.2 测试设备无6.1.3 取样镀金、化金、镀锡、化锡、化银等表面处理后的FPC成品或半成品,每次测试数量不少于5pcs。

6.1.4 测试方法及条件参考JIS C 5016-8.4将3M600 胶带粘着在试样表面,粘着长度不小于50 mm,用手指按压使其没有气泡, 然后, 约经过10s, 迅速垂直撕起胶带. 检查试样表面。

6.1.5 判定标准镀层表面不可有脱落。

6.2 印刷防焊与文字密着性测试(Adhesion of solder resist and symbol mark)6.2.1 测试目的验证产品上印刷的防焊油墨,文字油墨以及银浆的密着性。

6.2.2 测试设备无6.2.3 取样印刷防焊油墨、文字油墨、银浆后的FPC成品或半成品,每次测试数量不少于5pcs。

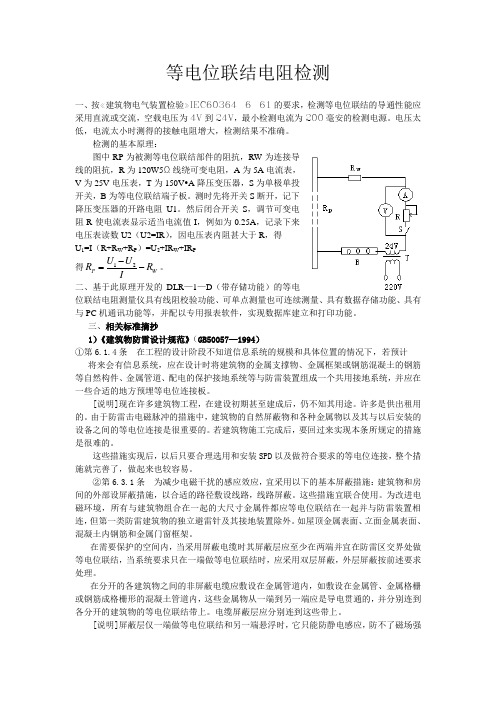

等电位连接电阻检测原理

等电位联结电阻检测一、按«建筑物电气装置检验»IEC60364-6-61的要求,检测等电位联结的导通性能应采用直流或交流,空载电压为4V 到24V ,最小检测电流为200毫安的检测电源。

电压太低,电流太小时测得的接触电阻增大,检测结果不准确。

检测的基本原理:图中RP 为被测等电位联结部件的阻抗,RW 为连接导线的阻抗,R 为120W5Ω线绕可变电阻,A 为5A 电流表,V 为25V 电压表,T 为150V A 降压变压器,S 为单极单投开关,B 为等电位联结端子板。

测时先将开关S 断开,记下降压变压器的开路电阻U1。

然后闭合开关S ,调节可变电阻R 使电流表显示适当电流值I ,例如为0.25A ,记录下来电压表读数U2(U2=IR ),因电压表内阻甚大于R ,得 U 1=I (R+R W +R P )=U 2+IR W +IR P 得W P R IU U R --=21。

二、基于此原理开发的DLR —1—D (带存储功能)的等电位联结电阻测量仪具有线阻校验功能、可单点测量也可连续测量、具有数据存储功能、具有与PC 机通讯功能等,并配以专用报表软件,实现数据库建立和打印功能。

三、相关标准摘抄 1)《建筑物防雷设计规范》(GB50057—1994)①第6.1.4条 在工程的设计阶段不知道信息系统的规模和具体位置的情况下,若预计 将来会有信息系统,应在设计时将建筑物的金属支撑物、金属框架或钢筋混凝土的钢筋等自然构件、金属管道、配电的保护接地系统等与防雷装置组成一个共用接地系统,并应在一些合适的地方预埋等电位连接板。

[说明]现在许多建筑物工程,在建设初期甚至建成后,仍不知其用途。

许多是供出租用的。

由于防雷击电磁脉冲的措施中,建筑物的自然屏蔽物和各种金属物以及其与以后安装的设备之间的等电位连接是很重要的。

若建筑物施工完成后,要回过来实现本条所规定的措施是很难的。

这些措施实现后,以后只要合理选用和安装SPD 以及做符合要求的等电位连接,整个措施就完善了,做起来也较容易。

MOSFET导通电阻偏高因素的测试分析和解决途径的研究

通常有两个方法可以提升功率MOSFET的导通电阻性能。一种是提高给定尺寸芯片 上面的晶体管的密度。第二个方法更简单些,是增加芯片的面积,但后果可能是设备的尺 寸更大。由于尺寸的增加,导致使用该功率MOSFET的终端设备成本的增加,面l临的挑战

英飞凌科技公司的研究表明,随着肖特基二极管零反向恢复电荷整流技术成为现实,因

此可以利用现代功率MOSFET器件的快速导通速度来减小丌关损耗.随着超级结(SJ)原

理的应用,功率MOSFET(如CoolMOS)在性能方面也取得了令人印象深刻的进步。2005 年推向市场的最新技术使得采用T0220封装的CoolMOS CS系列600V额定电压的 MOSFET的导通电阻RDSON降到了100m Q以下。由于MOS单元密度的提高以及更低

3

是在晶体管单元密度增加的同时,提高封装电阻,这是一个在导通电阻,芯片实际尺寸和

外壳热阻之『白J很难做出取舍的过程。解决这个问题的一个途径是对现有封装进行改进,提 高器件热性能。例如,热性能增强的D2PAK封装版本,采用了专有的引线框设计,实现了

采用这种封装器件的业界最低的热阻,这也依赖于使用的芯片尺寸。与常规使用的D2PAK 封装器件相比,采用热性能增强的封装版本的器件可提升29%的最大电流,达到100A; 提升了75%的散热,达到437、『\『,导通电阻仅有2.3mQ。

of three parts:Assembly 40%,30%each of Silicon circuit and base.In some of the latest

阻抗制作规范

规范制作阻抗PCB的阻抗计算和阻抗图形设计方法,确保成品的阻抗符合规定。

2、适用范围:

适用于本厂客户要求阻抗控制的PCB的阻抗设计及之CAM制作的阻抗图形设计。

3、名词解释:

3.1特性阻抗(Characteristic Impedance):当一条导线与大地绝缘后,导线与大地彼此之间的阻抗。

7.2.9外层方形PAD对应接地层为Thermal Pad或直接与铜面导通。

7.2.10线宽/线距必须符合流程单要求。

7.2.11两层板设计如下:

6.2.12四层板设计如下:

7.2.13六层板设计如下:

7.2.14八层板设计如下:

ቤተ መጻሕፍቲ ባይዱ7.3特殊阻抗设计:

特殊阻抗设计时除了一般注意事项以外须根据实际情况进行修改。

4.3.3特性阻抗:成品60欧姆±10%

4.3.3.1要求理论值计算特性阻抗控制的范围为60欧姆±8%:

4.3.3.2产品的制作参数要求如下:

1)客户原本设计的特性阻抗线线宽:150um,

2)客户原本设计的与特性阻抗线相邻的线距最小为:100um

3)与特性阻抗线相邻的介层的厚度要求为:105um±15um

RC% 68压合后的介质厚度为71±8UM,RC%62压合后的介质厚度为65±8UM

5)当选用几种Prepreg同时压合时,则采用最高的介电常数与最低的介电常数的平均值进行计算。

6)内层板材铜厚计算数据:

板材铜厚是70um用62um计算,板材铜厚是35um用30um计算,板材铜厚是18um用16um计算.

3) 2116 Prepreg

A、介电常数为4.3±0.2

B、压合后的介质厚度为(内层100%残铜理论值):

电厂接地网交接试验标准及接地线焊接要求

接地线焊接要求

铜材接地网接地阻抗较低,有效散流范围大,地网用钢材比用铜 材接地电阻约增加180%,因此在电站的接地设计中,主要采用铜材作 为接地网散流导体。

钢接地材料的最小尺寸

铜或铜履钢接地材料的最小尺寸

接地线的连接一般采用焊接方式,有色金属接地线不能采用焊接 时可用螺栓连接、压接、热剂焊(放热焊接)方式连接。焊接时要求 牢固无虚焊,用螺栓连接时应设防松螺帽或防松垫片,并压接紧密。 1.接地线焊接采用搭接焊时,其搭接长度满足下列规定: 1.1 扁钢为其宽度的2倍(且至少2个棱边焊接); 1.2 圆钢为其直径的6倍; 1.3 圆钢与扁钢连接时,其长度为圆钢直径的6倍; 1.4扁钢与钢管、扁钢与角钢焊接时,为了连接可靠,除在接触部位两 侧进行焊接外,并焊以钢带弯成的弧形卡子或直接由钢带本身弯成弧 形与钢管焊接。

30Ω。

明敷接地线安装要求

1.接地线的安装位置应合理,便于检查,无碍设备检修和运行巡视; 2.接地线的安装应美观,防止因加工方式造成接地线截面减小、强度减 弱、容易生锈; 3.支持件间的距离,在水平直线部分宜为0.5m~1.5m,垂直部分宜为 1.5m~3m,转弯部分宜为0.3m~0.5m; 4.接地线应水平或者垂直敷设,亦可与建筑物倾斜结构平行敷设,在直 线段上,不应有高低起伏及弯曲现象。

独 立 的 燃 油 、 易 爆 接地阻抗不宜大于30Ω( 无独立避雷针保护的露天储罐不 气体储罐及其管道 应超过10Ω)

露 天 配 电 装 置 的 集 接地阻抗不宜大于10Ω 中接地装置及独立 避雷针(线)

有 架 空 地 线 的 线 路 当杆塔高度在40m 以下时,按下列要求;当杆塔高度≥40m

杆塔

8.在接地线引向建筑物的入口处和在检修用临时接地点处,均应刷白色 底漆并标以黑色标识,其代号为“ ”; 9.GIS室内应敷设环形接地母线,室内各种设备需接地的部位应以最短 路径与环形接地母线连接; 10. GIS机座上的每一根接地母线,应采用分设其两端的接地线与电厂 接地装置连接,接地线应与GIS区域环形接地母线连接; 11.GIS机座下的钢筋混凝土地板中的钢筋应焊接成网,并和环形接地 母线连接。

UL电线标准介绍

2019/3/0

2、测量工具,读数显微镜

取样时,小心抽取全部导体芯线,沿导线绝缘体方向垂直切片, 在显微镜下测量最薄处的厚度,作为导体绝缘层的最小厚度。 通常将读数显微镜(精度为0.001mm)的测量结果作为最终的参 考标准。实际测量时发现一卷电线测量的最小厚度小于规定值 多过2Mils,判定该卷电线不合格。若测量值小于规定值不超过 2Mils,应在该卷电线上相距1英尺处抽取两个样测量,如果其中1 个结果小于最小值,该卷电线判为不合格,若两个测量值均达 标,判为合格。

常见电线的平均厚度和最小厚度的对照表。见UL62, Table:16.2,16.4,16.6,16.8.

2019/3/10

8

绞距

芯线绞距 取芯线10个绞合的间距的平均值作为芯线平均绞距,测量时去 除大约十个绞合长度的绝缘外皮,取任何一支芯线为对象进行 测量。注意在去皮时不要损伤芯线,造成芯线断线。 导线绞距 同样取导线的10个绞距长度进行平均,作为平均导线绞距,取 样时要注意由于导线绞合时的内应力一扭力很大,去除外被时 可能造成原绞合结构的松散。为此,取样时先预留一段护套线 不去除外被,再沿线缆方向用利刀片拉掉部分外被,最好是以 能看到待测导线,而导线与外被结合得仍很紧密为宜。将样品 平放拉直,量取某一导线十个绞合点之间的距离作为绞距,因 为成缆时由于应力的关系,成形外被后原绞合距离会增加。 各种芯线最大绞距参见UL62。各种线径的导线最大绞距参见 UL62

2019/3/10 18

3、测试样品的制备 步骤:截取一段待测试 (1)测量其导体直径,绝缘(或外被)层厚度; (2)小心去除绝缘层包裹的导线和其它填充物,检查绝缘表皮完好无损。 对于外被样品,用抛光磨平机小心磨平外被的内表面,直至内表面凹 凸部位平滑即可。对于周长分别为4mm或6mm的外被,可用ASTM dieD或 ASTM dieC的哑铃片器制备哑铃状样品。 (3)样品上相距1英寸两端作标记,以便测试过程中测量其拉伸情况。测试 机的上下拉爪的夹持位置距离标记线均匀,不超过1/2英寸。 4、计算 (1)对于规则的管状试样,截面积A为: A=00.7854(D2-d2) D:导线外径,d:导体直径

CAN总线终端电阻的作用?为什么是120Ω?为什么是0.25W?

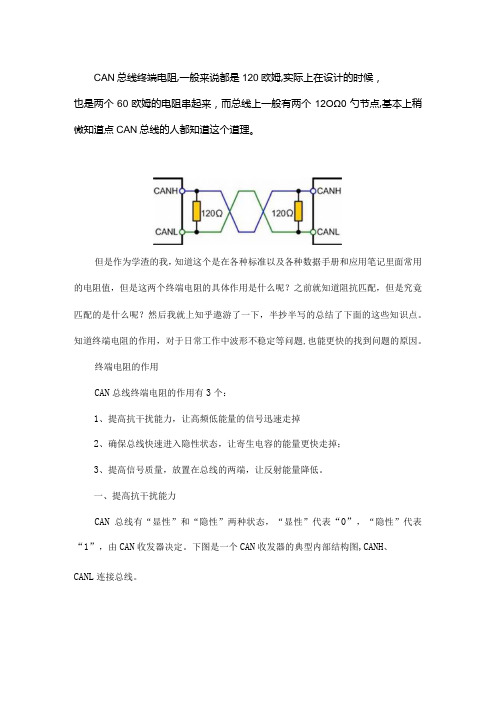

CAN总线终端电阻,一般来说都是120欧姆,实际上在设计的时候,也是两个60欧姆的电阻串起来,而总线上一般有两个12OΩ0勺节点,基本上稍微知道点CAN总线的人都知道这个道理。

但是作为学渣的我,知道这个是在各种标准以及各种数据手册和应用笔记里面常用的电阻值,但是这两个终端电阻的具体作用是什么呢?之前就知道阻抗匹配,但是究竟匹配的是什么呢?然后我就上知乎遨游了一下,半抄半写的总结了下面的这些知识点。

知道终端电阻的作用,对于日常工作中波形不稳定等问题,也能更快的找到问题的原因。

终端电阻的作用CAN总线终端电阻的作用有3个:1、提高抗干扰能力,让高频低能量的信号迅速走掉2、确保总线快速进入隐性状态,让寄生电容的能量更快走掉;3、提高信号质量,放置在总线的两端,让反射能量降低。

一、提高抗干扰能力CAN总线有“显性”和“隐性”两种状态,“显性”代表“0”,“隐性”代表“1”,由CAN收发器决定。

下图是一个CAN收发器的典型内部结构图,CANH、CANL连接总线。

总线显性时,收发器内部QI、Q2导通,CANH、CANL之间产生压差;隐性时,QkQ2截止,CANH.CANL处于无源状态,压差为0。

总线若无负载,隐性时差分电阻阻值很大,内部的MOS管属于高阻态,外部的干扰只需要极小的能量即可令总线进入显性(一般的收发器显性门限最小电压仅50OmV)O这个时候如果有差模干扰过来,总线上就会有明显的波动,而这些波动没有地方能够吸收掉他们,就会在总线上创造一个显性位出来。

所以为提升总线隐性时的抗干扰能力,可以增加一个差分负载电阻,且阻值尽可能小,以杜绝大部分噪声能量的影响。

然而,为了避免需要过大的电流总线才能进入显性,阻值也不能过小。

二、确保快速进入隐性状态在显性状态期间,总线的寄生电容会被充电,而在恢复到隐性状态时,这些电容需要放电。

如果CANH、CANL之间没有放置任何阻性负载,电容只能通过收发器内部的差分电阻放电,这个阻抗是比较大的,按照RC滤波电路的特性,放电时间就会明显比较长。