实验三 3-8译码器的功能测试及仿真

3-8译码器实验报告

3-8译码器实验报告

班级:121 姓名:连森学号:02

1.实验目标与实验要求:

1.理解译码器的概念和意义

2.理解译码器在计算机电路里的作用。

2.实验器材:

Altair 80C31Small 教学实验平台杜邦线

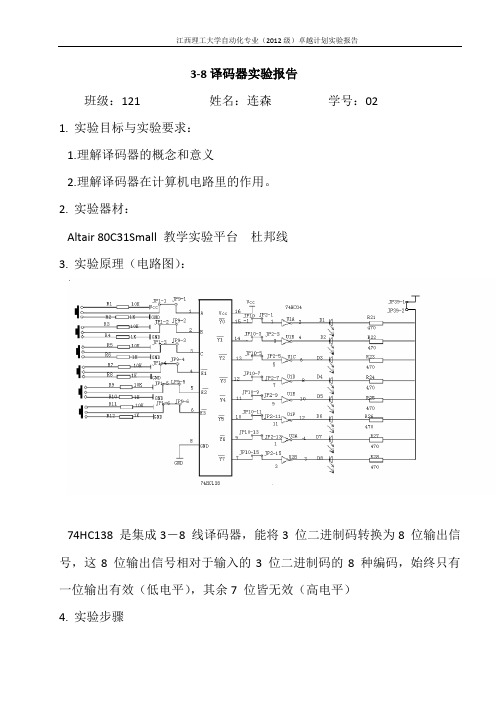

3.实验原理(电路图):

74HC138 是集成3-8 线译码器,能将3 位二进制码转换为8 位输出信号,这8 位输出信号相对于输入的3 位二进制码的8 种编码,始终只有一位输出有效(低电平),其余7 位皆无效(高电平)

4.实验步骤

首先用杜邦线将A3实验区与逻辑开关K1~K6相连的JP1-1~JP1-6,连接到A7实验区与74HC138相连的JP9单号插针;接着在74HC138的输出端连接绿色LED显示器;然后用跳线连接JP39-1与JP39-2,即可接通电源。

5.实验结果(现象):

当K4、K5、K6 打到0、0、1时,译码器74HC138 的逻辑功能有效,相应引脚输出低电平,对应LED 熄灭。

否则,74HC138 始终输出高电平(无效电平),LED 全亮。

实验三-quartus-ii的设计处理(3-8译码器设计)

实验三-quartus-ii的设计处理(3-8译码器设计)

《可编程逻辑器件的设计与仿真》

实验报告

实验项目实验三Quartus II的设计处理(3-8译码器设计)

实验目的1.设计一个3-8译码器;

2.学习用VHDL进行逻辑描述。

实验器材PC机,Quartus II

授课形式集中训练任课教师:彭铁牛实验时间:2013-03-17

实验说明本设计实现一个3-8译码器,其逻辑功能如表所示

C B A Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0

0 0 0 1 1 1 1 1 1 1 0

0 0 1 1 1 1 1 1 1 0 1

***********

0 1 1 1 1 1 1 0 1 1 1

1 0 0 1 1 1 0 1 1 1 1

1 0 1 1 1 0 1 1 1 1 1

1 1 0 1 0 1 1 1 1 1 1

1 1 1 0 1 1 1 1 1 1 1

本设计练习用VHDL语言描述仿真译码器。

要求编写3-8译码器的VHDL设计文件。

注意VHDL文件的结构和语法,并掌Quartus II 平台中文本编辑器的使用方法。

实验内容和体会

1

Ⅰ.VHDL源程序Ⅱ.仿真波形Ⅲ.元件符号Ⅳ.实验体会。

3 8译码器

试验一组合逻辑3线-8线译码器设计试验一、试验目的1、了解并初步掌握ModelSim软件的使用;2、了解使用ModelSim进行组合数字电路设计的一般步骤;3、掌握组合逻辑电路的设计方法;4、掌握组合逻辑电路3线-8线译码器的原理;5、掌握门级建模的方法;二、试验原理译码器(Decoder)的逻辑功能是将每个输入的二进制代码译成对应得输出高、低电平或另外一个代码。

因此,译码是编码的反操作。

常用的译码器电路有二进制译码器、二-十进制译码器和显示译码器等。

二进制译码器的输入是一组二进制代码,输出是一组与输入代码一一对应得高、低电平信号。

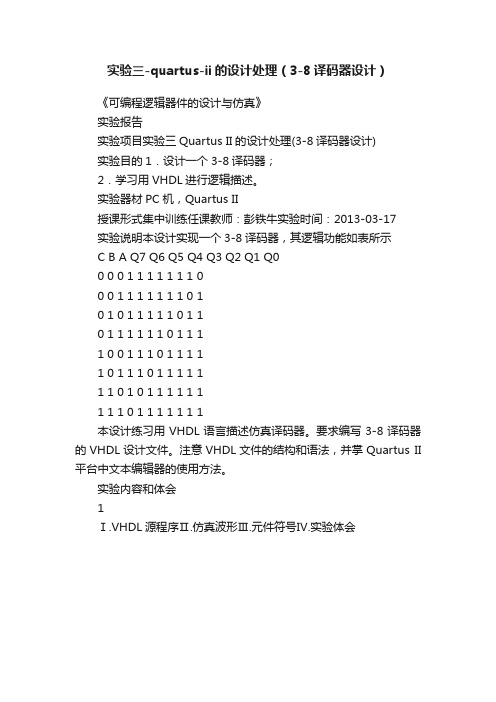

例如,典型的3线-8线译码器功能框图图1-1所示。

输入的3位二进制代码共有8种状态,译码器将每个输入代码译成对应的一根输出线上的高、低电平信号。

图1-1 3线-8线译码器框图74HC138是用CMOS门电路组成的3线-8线译码器,它的逻辑图图1-2所示。

表1-1是74HC138的逻辑功能表。

当门电路G S的输出为高电平时,可以由逻辑图写出。

图1-2 74HC138逻辑功能图表1-1 74HC138逻辑功能表由上式可以看出,由''07Y Y -同时又是210,,A A A 这三个变量的全部最小项的译码输出,所以也将这种译码器称为最小项译码器。

74HC138有3个附加的控制端''123,S S S 和。

当''123S 1,S S 0=+=时,s G 输出为高电平,译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁为高电平。

这3个控制端也称为“片选”输入端,利用片选的作用可以将多片连接起来以扩展译码器的功能;三、 预习要求1、数字电子技术基础组合逻辑电路设计一般设计方法;2、74HC138的逻辑功能;3、门级建模的一般方法和基本语句;4、ModelSim 软件的一般使用方法(ModelSim SE Tutorial);四、 实验步骤(一)、熟悉ModelSim 软件环境 1、建立一个新Project1-1双击左面快捷方式或者电击[程序]/[ModelSim SE 6.1f]/[ModelSim]启动ModelSim 6.1(如图1-3);注意:必须首先关闭IMPORTANT Information 对话框才能开始其它操作;图1-31-2 [File]/[New]/[Project…]新建一个project,会弹出Create Project对话框(如图1-4);图1-4⏹Project Name(项目名称)需要填入你所建立的项目的名称;⏹指定项目所在路径;如果所指定的目录不存在,会弹出对话框提示是否建立这个目录;一般选择是;⏹缺省的工作库名;注意:1、路径一般不应包含汉字;2、逻辑应在ModelSim的安装目录下指定;3、缺省的工作库的名称一般不需要改动;2、载入HDL元文件2-1设定好1-2步骤的每项内容后,点击OK,弹出Add items to the Projects对话框;如图1-5所示。

实验三 3-8译码器的功能测试及仿真

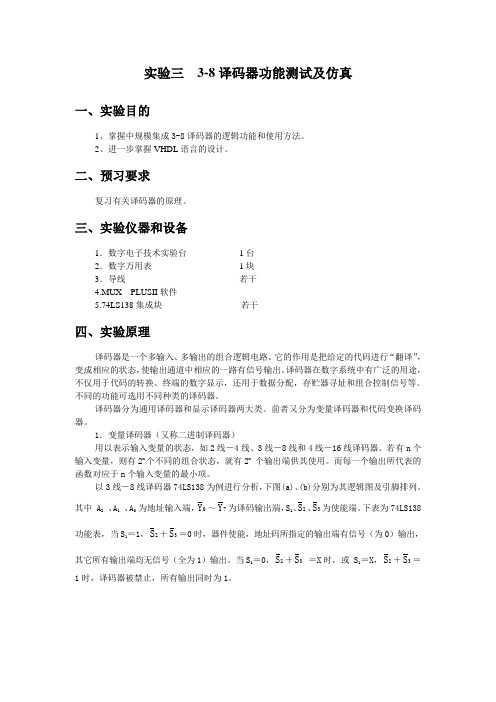

实验三3-8译码器功能测试及仿真一、实验目的1、掌握中规模集成3-8译码器的逻辑功能和使用方法。

2、进一步掌握VHDL语言的设计。

二、预习要求复习有关译码器的原理。

三、实验仪器和设备1.数字电子技术实验台1台2.数字万用表1块3.导线若干4.MUX PLUSII软件5.74LS138集成块若干四、实验原理译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。

不同的功能可选用不同种类的译码器。

译码器分为通用译码器和显示译码器两大类。

前者又分为变量译码器和代码变换译码器。

1.变量译码器(又称二进制译码器)用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。

若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端供其使用。

而每一个输出所代表的函数对应于n个输入变量的最小项。

以3线-8线译码器74LS138为例进行分析,下图(a)、(b)分别为其逻辑图及引脚排列。

其中 A2、A1、A0为地址输入端,0Y~7Y为译码输出端,S1、2S、3S为使能端。

下表为74LS138功能表,当S1=1,2S+3S=0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。

当S1=0,2S+3S=X时,或 S1=X,2S+3S=1时,译码器被禁止,所有输出同时为1。

3-8线译码器74LS138逻辑图及引脚排列图74LS138功能表输入输出S12S+3S A2A1A00Y1Y2Y3Y4Y5Y6Y7Y1 0 0 0 0 0 1 1 1 1 1 1 11 0 0 0 1 1 0 1 1 1 1 1 11 0 0 1 0 1 1 0 1 1 1 1 11 0 0 1 1 1 1 1 0 1 1 1 11 0 1 0 0 1 1 1 1 0 1 1 11 0 1 0 1 1 1 1 1 1 0 1 11 0 1 1 0 1 1 1 1 1 1 0 11 0 1 1 1 1 1 1 1 1 1 1 00 ×××× 1 1 1 1 1 1 1 1× 1 ××× 1 1 1 1 1 1 1 1二进制译码器实际上也是负脉冲输出的脉冲分配器。

实验三+3-8译码器仿真及实现

实验三3-8译码器仿真及实现姓名:学号:班级:日期:一、实验目的和要求本次实验使用Verilog 硬件描述语言在DE1开发平台上设计一个基本组合逻辑电路3-8 译码器,并完成功能仿真和时序仿真。

二、实验环境1、PC机,Pentium 4 2.0G以上,内存1G以上,硬盘500G以上,1024×768彩显,USB接口,网络接口,串口。

2、友晶DE1开发板和相关配件。

3、软件:Windows XP或者Windows 7操作系统,DE1配套光盘。

三、实验内容1、编写3-8的Verilog程序。

2、构建仿真波形文件,实现QuartusII的功能仿真和时序仿真。

3、下载设计到DE1,观察译码输出。

四、实验步骤1、建立Quartus 工程:1)打开Quartus II 工作环境。

2)点击菜单项File->New Project Wizard 帮助新建工程。

3)输入工程目录、工程文件名以及顶层实体名。

自己起名字,例如学号加38等。

注意:输入的顶层实体名必须与之后设计文件的顶层实体名相同,默认的顶层实体名与工程文件名相同,本类实验均采用这种命名方法以便于管理。

不要使用Quartus II的根目录作为工程目录。

4)添加设计文件。

如果用户之前已经有设计文件(比如.v 文件)。

那么直接添加相应文件,如果没有完成的设计文件,点击Next 之后添加并且编辑新的设计文件。

5)选择设计所用器件。

由于本次实验使用 Altera 公司提供的DE1 开发板,用户必须选择与之相对应的FPGA 器件型号,如下图:6)设置 EDA 工具。

设计中可能会用到的EDA 工具有综合工具、仿真工具以及时序分析工具。

本次实验中不使用这些工具,因此点击Next 直接跳过设置。

7)查看新建工程总结。

在基本设计完成后,Quartus II 会自动生成一个总结让用户核对之前的设计,确认后点击Finish 完成新建。

8)培养良好的文件布局。

Quartus II 默认把所有编译结果放在工程的根目录,为了让Quartus II 像Visual Studio 等IDE 一样把编译结果放在一个单独的目录中,需要指定编译结果输出路径。

实验一3-8译码器

3-8译码器的仿真

一:实验名称:3-8译码器仿真

二:实验要求:熟悉对max+plusⅡ10.0的使用,并且能简单的使用进行3-8译码器的仿真和论证。

三:实验步骤:

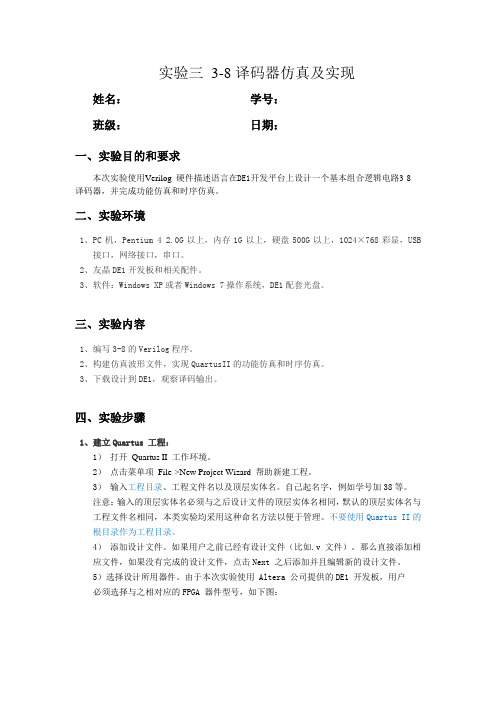

1:使用max+plusⅡ10.0软件,设计3-8译码器的实验原理图如下所示:

图1 实验原理图

2:波形的仿真与分析

启动max+plusⅡ10.0\Waveform editor菜单,进入波形编辑窗口,选择欲仿真的所有I\O管脚。

如下图所示:

图2 波形编辑

为输入端口添加激励波形,使用时钟信号。

选择初始电平为“0”,时

钟周期倍数为“1”。

添加完后,波形图如下所示:

图3 添加激励后的波形

打开max+plusⅡ10.0\Simulator菜单,确定仿真时间,单击Start开始仿真,如下图所示:

图4 仿真过程

图5 仿真结果

四:实验结论:使用max+plusⅡ10.0能很好的完成很多电路的仿真与工作。

3-8线译码器实验内容

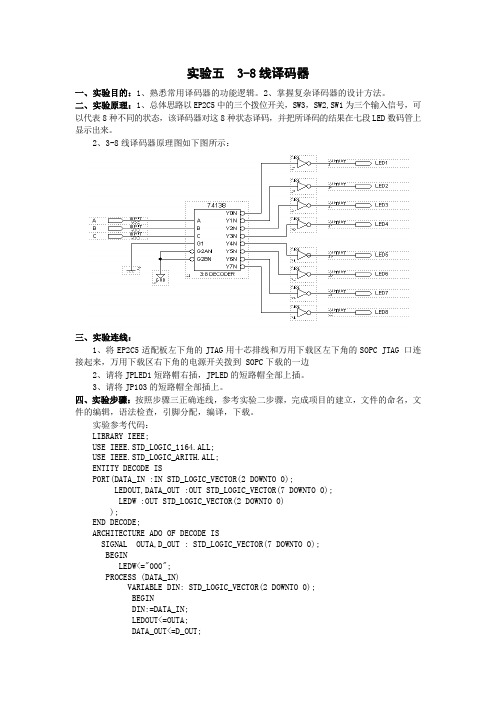

实验五 3-8线译码器一、实验目的:1、熟悉常用译码器的功能逻辑。

2、掌握复杂译码器的设计方法。

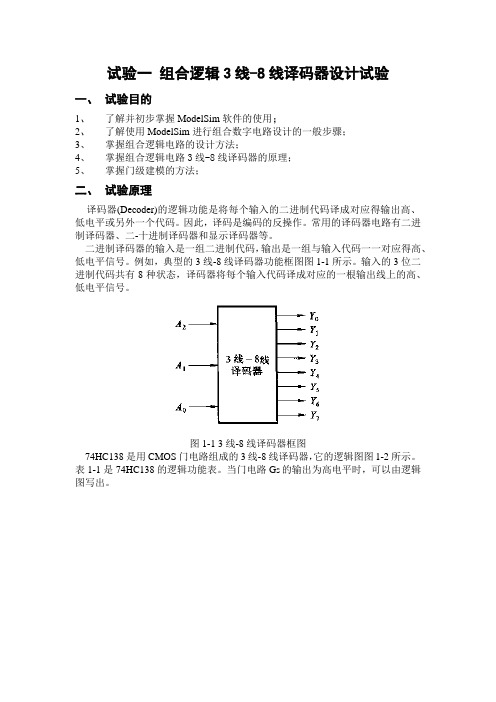

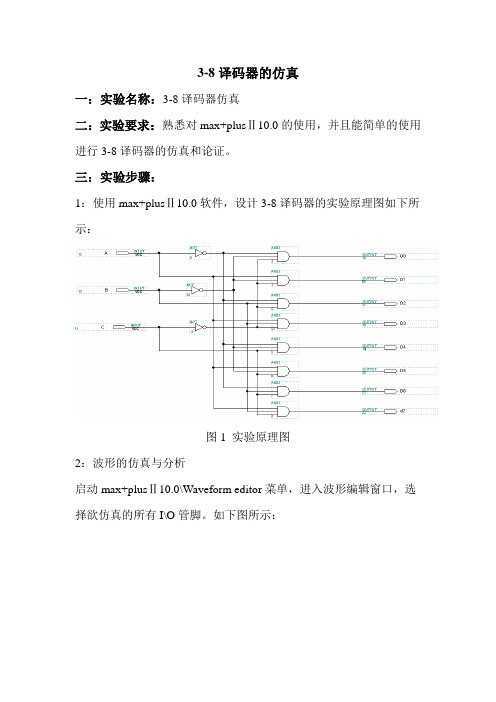

二、实验原理:1、总体思路以EP2C5中的三个拨位开关,SW3,SW2,SW1为三个输入信号,可以代表8种不同的状态,该译码器对这8种状态译码,并把所译码的结果在七段LED数码管上显示出来。

2、3-8线译码器原理图如下图所示:三、实验连线:1、将EP2C5适配板左下角的JTAG用十芯排线和万用下载区左下角的SOPC JTAG 口连接起来,万用下载区右下角的电源开关拨到 SOPC下载的一边2、请将JPLED1短路帽右插,JPLED的短路帽全部上插。

3、请将JP103的短路帽全部插上。

四、实验步骤:按照步骤三正确连线,参考实验二步骤,完成项目的建立,文件的命名,文件的编辑,语法检查,引脚分配,编译,下载。

实验参考代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY DECODE ISPORT(DATA_IN :IN STD_LOGIC_VECTOR(2 DOWNTO 0);LEDOUT,DATA_OUT :OUT STD_LOGIC_VECTOR(7 DOWNTO 0);LEDW :OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END DECODE;ARCHITECTURE ADO OF DECODE ISSIGNAL OUTA,D_OUT : STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINLEDW<="000";PROCESS (DATA_IN)VARIABLE DIN: STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINDIN:=DATA_IN;LEDOUT<=OUTA;DATA_OUT<=D_OUT;CASE DIN ISwhen "000" => OUTA<="00111111" ; --"0"when "001" => outa<="00000110" ; --"1"when "010" => outa<="01011011"; --"2"when "011" => outa<="01001111"; --"3"when "100" => outa<="01100110"; --"4"when "101" => outa<="01101101"; --"5"when "110" => outa<="01111101"; --"6"when "111" => outa<="00000111"; --"7"WHEN OTHERS => OUTA<="XXXXXXXX";END CASE;CASE DIN ISWHEN "000" => D_OUT<="00000000";WHEN "001" => D_OUT<="00000001";WHEN "010" => D_OUT<="00000010";WHEN "011" => D_OUT<="00000100";WHEN "100" => D_OUT<="00001000";WHEN "101" => D_OUT<="00010000";WHEN "110" => D_OUT<="00100000";WHEN "111" => D_OUT<="01000000";WHEN OTHERS=> D_OUT<="XXXXXXXX";END CASE;END PROCESS;END ADO;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY shiyan5 ISPORT(DATA_IN :IN STD_LOGIC_VECTOR(2 DOWNTO 0);LEDOUT,DATA_OUT :OUT STD_LOGIC_VECTOR(7 DOWNTO 0);LEDW :OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END shiyan5;ARCHITECTURE ADO OF shiyan5 ISSIGNAL OUTA,D_OUT : STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINLEDW<="000";PROCESS (DATA_IN)VARIABLE DIN: STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINDIN:=DATA_IN;LEDOUT<=OUTA;DATA_OUT<=D_OUT;IF(DIN="000") THEN OUTA<="00111111" ;D_OUT<="00000000"; --"0"ELSIF(DIN="001") THEN outa<="00000110" ;D_OUT<="00000001"; --"1" ELSIF(DIN="010") THEN outa<="01011011";D_OUT<="00000010"; --"2" ELSIF(DIN="011") THEN outa<="01001111";D_OUT<="00000100"; --"3" ELSIF(DIN="100") THEN outa<="01100110";D_OUT<="00001000"; --"4" ELSIF(DIN="101") THEN outa<="01101101";D_OUT<="00010000"; --"5" ELSIF(DIN="110") THEN outa<="01111101";D_OUT<="00100000"; --"6"ELSIF(DIN="111") THEN outa<="00000111";D_OUT<="01000000"; --"7"ELSE OUTA<="XXXXXXXX";D_OUT<="XXXXXXXX";END IF;END PROCESS;END ADO;五、实验现象:(程序:EP2C5\dencode\dencode.sof)3-8线译码器的三个输入C、B、A分别对应拨位开关SW3,SW2,SW1,改变SW3,SW2,SW1的位置,以改变C、B、A 的状态,于LED1上观察译码实验结果。

仿真用与非门组成的3-8译码器(74HC138)

贵州大学

电路EDA电路技术课程考

核报告

姓名:田泽民

学号:PZ082014131 班级:08级计维班

一、实验目的:

1、会PSpice软件的仿真应用。

2、知道全加器的原理,进行仿

真。

二、实验名称:

仿真用与非门组成的3-8译码器(74HC138)。

三、实验内容:

画出电路图,进行参数的设置,截图,分析得到仿真结果。

四、实验原理:

译码器74HC138有三个附加的控制端,当状态为(1,0,0)时,译码器工作。

输入端A2,A1,A0;输出端Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7.

五、实验过程:

1、实验电路:

2、参数设置:

DSTM4、DSTM5、DSTM6高低电平交互的时间分别设为:4ms、2ms 和1ms,0—30ms,步长为5ms

3、仿真结果:

从上图可以看出,当输入端为000的时候选择Y0输出,当输入端为001的时候选择Y1输出……

010 Y2 011 Y3 100 Y4

101 Y5 110 Y6 111 Y7

4、真值表对照:

5、结果截图(与理论值相符):

六、实验结论:

本次实验,所得到的显示结果与预计:完全相同,因而证明本次实验是正确的。

七、实验总结:

进行参数设置的时候,时间不能设得太短,最好是以(ms)为单位。

在输入端时间设置应该注意取到每个输入组合,否则实验就不一定仿真出真实的结果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验三3-8译码器功能测试及仿真

一、实验目的

1、掌握中规模集成3-8译码器的逻辑功能和使用方法。

2、进一步掌握VHDL语言的设计。

二、预习要求

复习有关译码器的原理。

三、实验仪器和设备

1.数字电子技术实验台1台

2.数字万用表1块

3.导线若干

4.MUX PLUSII软件

5.74LS138集成块若干

四、实验原理

译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。

不同的功能可选用不同种类的译码器。

译码器分为通用译码器和显示译码器两大类。

前者又分为变量译码器和代码变换译码器。

1.变量译码器(又称二进制译码器)

用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。

若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端供其使用。

而每一个输出所代表的函数对应于n个输入变量的最小项。

以3线-8线译码器74LS138为例进行分析,下图(a)、(b)分别为其逻辑图及引脚排列。

其中 A2、A1、A0为地址输入端,0Y~7Y为译码输出端,S1、2S、3S为使能端。

下表为74LS138功能表,当S1=1,2S+3S=0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。

当S1=0,2S+3S=X时,或 S1=X,2S+3S=1时,译码器被禁止,所有输出同时为1。

3-8线译码器74LS138逻辑图及引脚排列图

74LS138功能表

输入输出

S12S+3S A2A1A00Y1Y2Y3Y4Y5Y6Y7Y

1 0 0 0 0 0 1 1 1 1 1 1 1

1 0 0 0 1 1 0 1 1 1 1 1 1

1 0 0 1 0 1 1 0 1 1 1 1 1

1 0 0 1 1 1 1 1 0 1 1 1 1

1 0 1 0 0 1 1 1 1 0 1 1 1

1 0 1 0 1 1 1 1 1 1 0 1 1

1 0 1 1 0 1 1 1 1 1 1 0 1

1 0 1 1 1 1 1 1 1 1 1 1 0

0 ×××× 1 1 1 1 1 1 1 1

× 1 ××× 1 1 1 1 1 1 1 1

二进制译码器实际上也是负脉冲输出的脉冲分配器。

若利用使能端中的一个输入端输

入数据信息,器件就成为一个数据分配器(又称多路分配器),如图3-2所示。

若在S1输入

端输入数据信息,2S=3S=0,地址码所对应的输出是S1数据信息的反码;若从2S端输入

数据信息,令S1=1、3S=0,地址码所对应的输出就是2S端数据信息的原码。

若数据信息是时

钟脉冲,则数据分配器便成为时钟脉冲分配器。

根据输入地址的不同组合译出唯一地址,故可用作地址译码器。

接成多路分配器,可

将一个信号源的数据信息传输到不同的地点。

二进制译码器还能方便地实现逻辑函数,如下图所示,实现的逻辑函数是 Z =C B A C B A C B A +++ABC

作数据分配器图 实现逻辑函数图

利用使能端能方便地将两个 3/8译码器组合成一个4/16译码器,如下图所示。

用两片74LS138组合成4/16译码器图

五、实验内容及步骤

1.74LS138译码器逻辑功能测试

将译码器使能端S 1、2S 、3S 及地址端A 2、A 1、A 0 分别接至逻辑电平开关输出口,八个

Y⋅⋅⋅依次连接在逻辑电平显示器的八个输入口上,拨动逻辑电平开关,按下表逐输出端0

7Y

项测试74LS138的逻辑功能。

输入输出

S12S3S A2A1A00Y1Y2Y3Y4Y5Y6Y7Y 1 0 0 0 0 0

1 0 0 0 0 1

1 0 0 0 1 0

1 0 0 0 1 1

1 0 0 1 0 0

1 0 0 1 0 1

1 0 0 1 1 0

1 0 0 1 1 1

0 ×××××

× 1 1 ×××

2.3-8译码器的VHDL仿真

1)运行该软件,在主菜单中选择File中的New中的Text Editor file文本编辑框,输入与门的VHDL文本:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY decoder3_8 IS

PORT(a: IN STD_LOGIC_ VECTOR(DOWNTO 0);

y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END decoder3_8;

ARCHITECTURE one OF decoder3_8 IS

BEGIN

PROCESS (a)

BEGIN

CASE a IS

WHEN "000"=>Y<="00000001";

WHEN "001"=>Y<="00000010";

WHEN "010"=>Y<="00000100";

WHEN "011"=>Y<="00001000";

WHEN "100"=>Y<="00010000";

WHEN "101"=>Y<="00100000";

WHEN "110"=>Y<="01000000";

WHEN "111"=>Y<="10000000";

WHEN OTHERS =>null;

END CASE;

END PROCESS ;

END one;

3进行波形仿真

4.波形分析

六、实验报告要求

1.画出实验线路,把观察到的波形画出来,并标上对应的地址码。

2.对仿真实验结果进行分析,说明译码器的特点。