光纤实验报告--数字光纤通信线路编译码CPLD仿真实验

通信原理实验一实验报告 CPLD 可编程数字信号发生器实训

11脚

10脚

9脚

8脚

6脚

5脚

4脚

81脚

80脚

79脚

77脚

76脚

75脚

74脚

73脚

70脚

69脚

68脚

12脚

3.CPLD可编程模块电路

图1CPLD可编程模块电路图

三、

1.打开电源总开关,电源指示灯亮,系统开始工作;

2.用示波器测出下面所列各测量点波形,并对每一测量点的波形加以分析;

(2)CPLD可编程模块组成:ALTERA公司的EPM7128(或Xilinx公司的XC95108)、编程下载接口电路(J101)和一块晶振(OSC1)。

(3)晶振:产生系统内的16.384MHz主时钟。

2.各种信号的功用及波形

(1)CPLD型号为EPM7128由计算机编好程序从J101下载写入芯片,OSC1为晶体,频率为16.384MHz,经8分频得到2.048MHz主时钟。

(2)取样时钟、编码时钟、同步时钟、时序信号还将被接到需要的单元电路中。

(3)PN32kHz、PN2kHz伪随机码的码型均为111100010011010,不同的是码元宽度不一样,PN2kHz的码元宽度T=1/2K=0.5ms,PN32kHz的码元宽度T=0.03125ms。

面板测量点与EPM7128各引脚信号对应关系如下:

五

图21CPLD可编程ຫໍສະໝຸດ 字信号发生器模块512Hz的时钟信号。(图3上)

(4)TP104

256KHz的时钟信号。(图3下)。

图3

(5)TP105

128KHz的时钟信号,作FSK调制模块中产生载波信号。(图4上)

(6)TP106

64KHz的时钟信号,作为FSK调制模块中产生载波信号。(图4下)

数字光纤通信系统线路编译码实验

1、了解线路码型在光纤传输系统中的作用2、掌握线路码型CMI码的编译码过程以及电路实现原理二、实验仪器1、ZY12OFCom23BH1型光纤通信原理实验箱 1台2、20MHz双踪模拟示波器 1台3、FC-FC单模光跳线 1根4、连接导线 20根三、实验原理线路码型变换电路主要是适应数字光纤通信传输的需要而设置的,因此,数字光纤通信传输过程的前后必须有线路码型变换与反变换电路。

线路码型是指信道码的码型,它是将二进制的数字串变换为适合于特定传输媒介的形式。

因此,对于不同的传输媒介,有不同类型的线路码型。

对于光纤数字传输系统,不仅要考虑其传输媒介光纤的特性,还需考虑光电转换器件即光源器件和光检测器件的特性,例如光纤线路的带宽(色散)特性影响着对线路码型速率变化的选择,光源器件的非线性影响着对线路码型是单极性还是多极性的选择,一般说来,对光纤传输线路码型的选择主要考虑如下要求:(1)比特序列独立性(2)能提供足够的定时信息(3)减小功率谱密度中的高低频分量(4)误码倍增小(5)便于实现不中断业务的误码监测(6)易于在传送主信息(业务信息)的同时,传送监控、公务、数据等维护管理信息,以及区间通信等辅助信号。

(7)易于实现光线路码型应该是两电平、基带、连续运行、固定长度组码。

由于CMI码有很多优点,它既为我国数字通信标准制式所规定的两种接口码型之一,又是数字光纤通信系统中所采用的线路码型,它属于mBnB码(1B2B码)。

所以,本实验中的线路码型就采用CMI码。

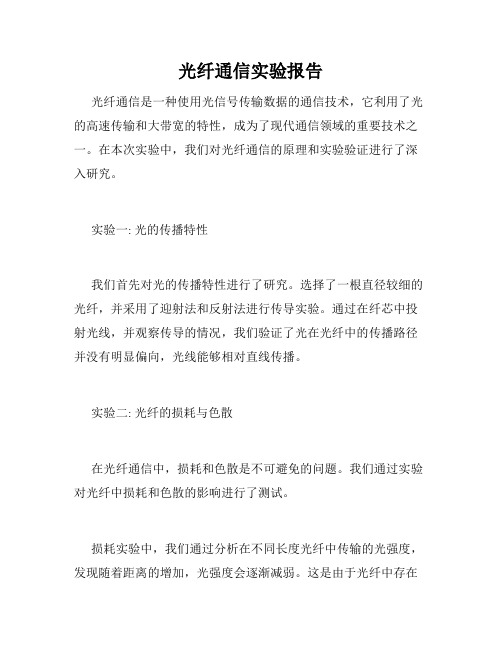

CMI码为信号反转码(Code Mark Inversion),是一种二电平不归零码,是PCM四次群的线路传输码型,也就是四次群数字光纤通信设备与四次群PCM设备之间的接口码型。

光纤数字基带信号CMI编码光发送光接收CMI译码图2-1 CMI编译码实验框图四、实验内容1、验证符合光纤传输系统的线路码型2、观察线路码型的编译码过程1、连接导线:数字基带信号产生模块T504与CMI编译码模块T701连接,T502与T702连接,T703与T151连接,T751与T161连接,T752与T502连接2、用FC-FC广信跳线将1550nmT与1550nmR连接,组成1550nm光纤传输系统3、连接好实验箱电源,先开交流电源开关,再开直流电源开关,即按下K01,K02 (电源模块)4、接通数字信号源(K50)、CMI编译码模块(K70)和发光模块(K15)的直流电源。

光纤通信实验报告

光纤通信实验报告实验报告:光纤通信技术引言:光纤通信技术是一种基于光传输原理的高速、大容量、低损耗的通信方式。

光纤通信以其优异的性能和广泛的应用领域受到了广泛的关注。

本次实验旨在探究光纤通信的基本原理和实验方法,以及光纤通信的特点和应用。

一、光纤通信的基本原理1.光纤通信的原理光纤通信是利用光纤作为传输介质,将光信号转换为电信号进行传输。

它主要包括光信号的产生、调制、传输和接收等过程。

光信号通过激光器发射端发出,经过光纤传输到接收端,然后通过光电转换器将光信号转换为电信号。

2.光纤的工作原理光纤是一种具有高折射率的细长光导纤维,主要由芯层、包层和包住层组成。

光信号在传输过程中会发生多次反射,利用全内反射原理将光信号在光纤内损耗尽可能小地传播。

二、光纤通信实验的步骤1.光信号的产生通过激光器发射端发出激光光束,光纤接收端接收光信号。

2.光信号的调制利用调制器对光信号进行调制,使其携带有用信息。

3.光信号的传输利用光纤的高折射率和全内反射的特点,将光信号传输到接收端。

4.光信号的接收通过光电转换器将光信号转换为电信号,进而进行信号处理,如放大、滤波等。

三、光纤通信的特点和应用1.高速传输光纤通信具有高传输速率和大容量的优势,可以满足现代通信的高速要求。

2.低损耗光纤通信中光信号的传输损耗非常小,可以远距离传输无衰减。

3.安全性强光信号在传输过程中不容易被窃听或干扰,保证了通信的安全性。

4.应用广泛结论:通过本次实验,我们深入了解了光纤通信的基本原理和实验方法。

光纤通信具有高速传输、低损耗、安全性强和应用广泛等特点,是现代通信领域的重要技术。

光纤通信的发展势头迅猛,未来有望取代传统的铜线通信,成为主流的通信技术。

光纤通信实验报告

光纤通信实验报告光纤通信是一种使用光信号传输数据的通信技术,它利用了光的高速传输和大带宽的特性,成为了现代通信领域的重要技术之一。

在本次实验中,我们对光纤通信的原理和实验验证进行了深入研究。

实验一: 光的传播特性我们首先对光的传播特性进行了研究。

选择了一根直径较细的光纤,并采用了迎射法和反射法进行传导实验。

通过在纤芯中投射光线,并观察传导的情况,我们验证了光在光纤中的传播路径并没有明显偏向,光线能够相对直线传播。

实验二: 光纤的损耗与色散在光纤通信中,损耗和色散是不可避免的问题。

我们通过实验对光纤中损耗和色散的影响进行了测试。

损耗实验中,我们通过分析在不同长度光纤中传输的光强度,发现随着距离的增加,光强度会逐渐减弱。

这是由于光纤中存在材料吸收和散射等因素造成的。

为了减小损耗,优化光纤的材料和结构是很重要的。

色散实验中,我们将不同波长的光信号通过光纤传输,并测量到达另一端的时间。

实验结果显示,不同波长的光信号到达时间存在差异。

这是由于光纤中折射率随波长变化而引起的色散效应。

为了减小色散,需要采用更先进的技术,如光纤衍生波导和光纤增益等手段。

实验三: 单模光纤与多模光纤光纤通信中,单模光纤和多模光纤是常用的两种类型。

通过实验,我们对这两种光纤的传输特性进行了研究。

我们首先测试了单模光纤。

结果显示,在单模光纤中,光信号会以单一光波传播,因此具有较低的色散和损耗,适用于远距离传输和高速通信。

然后我们进行了多模光纤的实验。

实验结果显示,多模光纤中存在多个模式的光信号传播,由于不同模式间的传播速度不同,会导致严重的色散和损耗问题。

因此,多模光纤适用于近距离传输和低速通信。

结论通过本次光纤通信实验,我们对光纤通信的原理和实际应用有了更深入的了解。

我们发现光纤通信具有高速率、低损耗和大带宽等优势,而不同类型的光纤对于不同的通信需求有着不同的适应性。

然而,我们也看到了光纤通信中存在的一些问题,如损耗、色散和设备成本等。

光纤宽带实验报告

一、实验目的本次实验旨在通过实际操作,了解光纤宽带的基本原理、技术特点及其在局域网中的应用。

通过实验,使学生掌握光纤宽带系统的搭建、配置及调试方法,提高学生在网络技术领域的实际操作能力。

二、实验原理光纤宽带是一种基于光纤传输媒介的高速宽带接入技术。

它将数据由电信号转换为光信号进行传输,具有传输速度快、距离远、抗干扰能力强等特点。

光纤宽带采用波分复用(WDM)技术,将多个用户的数据调制到不同波长的光信号,在同一根光纤中传输,从而实现高速、高效的数据传输。

三、实验设备1. 光纤宽带接入设备:包括光猫、光纤收发器、光纤分配器等。

2. 交换机:用于连接光猫和计算机,实现数据交换。

3. 计算机若干:用于进行实验操作和测试。

4. 光纤:用于连接设备,实现数据传输。

四、实验步骤1. 搭建光纤宽带系统(1)将光纤从光纤接入设备引出,连接至光纤分配器。

(2)将光纤分配器输出端连接至光猫。

(3)将光猫连接至交换机。

(4)将计算机连接至交换机。

2. 配置光纤宽带系统(1)在光猫上配置IP地址、子网掩码、网关等网络参数。

(2)在交换机上配置VLAN、端口镜像等功能。

(3)在计算机上配置IP地址、DNS等网络参数。

3. 测试光纤宽带系统(1)使用ping命令测试计算机与光猫之间的连通性。

(2)使用traceroute命令测试数据包传输路径。

(3)使用网络速度测试工具测试光纤宽带速度。

五、实验结果与分析1. 连通性测试通过ping命令测试,发现计算机与光猫之间的连通性良好,无丢包现象。

2. 数据传输路径测试通过traceroute命令测试,发现数据包传输路径符合预期,无异常。

3. 光纤宽带速度测试使用网络速度测试工具测试,发现光纤宽带速度达到预期,满足实际应用需求。

六、实验总结1. 光纤宽带具有传输速度快、距离远、抗干扰能力强等特点,是现代网络通信的理想选择。

2. 光纤宽带系统搭建简单,配置方便,易于维护。

3. 在实际应用中,光纤宽带能够满足高速、高效的数据传输需求,为用户提供优质的网络服务。

通信光缆与电缆线路工程实验报告

通信光缆与电缆线路工程实验报告通信光缆试验报告测验目的1、熟谙m序列NRZ码、任意周期产生原理以及光纤线路CMI编译码原理。

2、初步纯熟XXX公司XXX仿真平台的使用。

3、进一步熟谙数字电路设计技巧。

4、根本掌管如何举行CPLD的电路设计与仿真。

5、深入理解光纤线路编译码在光纤通信系统中的实际运用方法。

测验仪器安装MAXPLUS的计算机一台。

测验内容1、学习使用XXX公司XXX仿真平台举行CPLD数字电路的设计与仿真。

2、设计m序列NRZ码产生电路以及光纤线路CMⅡ编译码电路m 序列:伪随机序列;NRZ:不归零码;CMⅡ编码规矩:0码:01;1码:00/11交替。

3、通过CPLD仿真确保上述电路的正确设计。

4、总结光纤线路编译码在光纤通信系统中的实际运用。

电缆线路工程实验报告铭牌1、电缆型号YJV26/35kV-3×70额定电压26/35kV电缆起点41B箱变电缆终点43B箱变。

试验结果试验日期环境温度25?相对湿度2011/06/2629%2.1核对安装位置和相位:正确。

3、测量绝缘电阻M2:测量值MQ)测试部位耐压前耐压后A相对B、C相及地2500025000B相对A、C相及地2000020000 C相对A、B 相及地2500025000使用仪器:ZC11D-10型兆做表25009N0:0510246。

4、直流耐压试验及泄漏电流测量。

泄漏电流测试部位结果20kV40kV65kW70kV85kW85kV加压时间(分钟)1111115A相对B、C相及地707990105112112合格B相对A、C相及地909599100117117合格C相对A、B相及地869195 102109110合格使用仪器:KGF-200直流高压发生器。

结论合格。

光纤实验实训报告

1. 熟悉光纤的基本结构和光学特性。

2. 掌握光纤的连接方法和熔接技术。

3. 了解光纤通信系统的基本原理和应用。

4. 提高动手操作能力和实验技能。

二、实验内容1. 光纤的基本结构及光学特性2. 光纤熔接技术3. 光纤通信系统基本原理与应用三、实验原理1. 光纤的基本结构:光纤由纤芯、包层和涂覆层组成,纤芯的折射率高于包层,使得光在纤芯与包层的界面发生全反射,从而实现光的传输。

2. 光纤熔接技术:利用光纤熔接机将两根光纤的端面熔接在一起,形成低损耗的连接。

3. 光纤通信系统基本原理:利用光纤作为传输介质,将电信号转换为光信号,通过光纤传输,再将光信号转换为电信号。

四、实验仪器与材料1. 光纤熔接机2. 光纤测试仪3. 光纤跳线4. 光纤耦合器5. 光纤连接器6. 光纤7. 电源1. 光纤基本结构及光学特性观察- 观察光纤的结构,了解纤芯、包层和涂覆层的组成。

- 使用光纤测试仪测量光纤的折射率、衰减等参数。

2. 光纤熔接技术- 准备两根光纤,将光纤端面切割平整。

- 使用光纤熔接机将两根光纤熔接在一起。

- 使用光纤测试仪测试熔接点的衰减。

3. 光纤通信系统基本原理与应用- 搭建光纤通信系统,包括光发射机、光纤、光接收机等。

- 使用信号发生器发送信号,通过光纤传输,再由光接收机接收并恢复信号。

- 测试通信系统的传输速率、误码率等指标。

六、实验结果与分析1. 光纤基本结构及光学特性观察- 观察到光纤由纤芯、包层和涂覆层组成,纤芯的折射率高于包层。

- 光纤测试仪测量结果显示,光纤的衰减系数为0.2dB/km,折射率为1.5。

2. 光纤熔接技术- 熔接完成后,使用光纤测试仪测试熔接点的衰减,结果显示衰减小于0.1dB。

3. 光纤通信系统基本原理与应用- 搭建的光纤通信系统能够正常传输信号,传输速率达到10Mbps,误码率为0。

七、实验总结通过本次实验,我们熟悉了光纤的基本结构、光学特性,掌握了光纤熔接技术,了解了光纤通信系统的基本原理和应用。

光通信技术基础实验报告光纤通信系统综合与光线路码设计

光通信技术基础课程实验报告实验名称光纤通信系统综合与光线路码设计实验一数字光通信线路编译码实验一、实验目的:1. 熟悉指定序列NRZ 码产生原理以及光线路CMI 编译码原理。

2.熟练Altera 公司QUARTUS II 仿真平台的使用。

3.基本掌握进行FPGA 电路设计与仿真的方法。

4.了解FPGA 功能的物理验证。

二、实验环境QUARTUS II 13.0三、实验内容1. 学习使用Altera 公司QUARTUS II 设计平台与MODELSIM 仿真平台进行FPGA 数字电路的设计与仿真。

2. 设计指定序列NRZ 码产生电路以及光纤线路CMI 编译码电路。

NRZ: 不归零码;CMI 编码规则:0 码: 01;1 码: 00/11 交替;3. 通过FPGA 仿真确保上述电路的正确设计。

4. 总结光纤线路编译码在光纤信系统中的实际运用。

四、实验要求在QUARTUS II 软件仿真环境中1. 编写VERILOG 语言新工程,设计实现FPGA 内部功能:15 位学号序列(二进制表示的本组内某学号后四位(前面可补零))NRZ 码的生成;CMI 编码;CMI 译码电路(在实验室条件下使用统一系统时钟,输入为CMI 编码输出);2. 使用对所做设计完成正确编译。

3. 在ALTERA-MODELSIM 仿真环境中完成信号波形仿真。

FPGA 电路仿真的输入输出信号即各测试点信号要求如下:输入:系统时钟信号(1.92MC):1 路;(硬件匹配)输出:周期15 位二进制后四位学号序列:1 路;(240Kbps)CMI 编码输出信号:1 路;CMI 译码输出信号:1 路;4. 对仿真信号波形结果进行原理分析,发现可能的问题并加以解决,得到正确的仿真结果。

5. CMI 编译码的物理验证(实验室现场选做);五、实验程序代码六、仿真结果图1.1 仿真文件结果七、仿真结果分析对比理论分析结果与实际仿真结果无太大差异,只是输出信号有延迟,分析为输出信号与系统时钟不同步导致。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

光纤实验报告--数字光纤通信线路编译码CPLD仿真实验

数字光纤通信线路编译码

CMI实验

班级:

姓名:

一、实验目的:

1.熟悉m序列NRZ码、任意周期码产生原理以及光纤线路CMI编译码原理。

2.初步熟练Altera公司Maxplus II仿真平台的使用。

3.进一步熟悉数字电路设计技巧。

4.基本掌握如何进行CPLD的电路设计与仿真。

5.深入理解光纤线路编译码在光纤通信系统中的实际运用方法。

二、实验内容:

1.学习使用Altera公司Maxplus II仿真平台进行CPLD数字电路的设计与仿真。

2.设计m序列NRZ码产生电路以及光纤线路CMI编译码电路。

m序列: 伪随机序列;

NRZ: 不归零码;

CMI编码规则: 0码:01;

1码::00/11 交替;

3.通过CPLD仿真确保上述电路的正确设计。

4.总结光纤线路编译码在光纤通信系统中的实际运用。

三、实验要求:

在MAX+plus II软件仿真环境中,

1.用绘制原理图的方法建立新工程,设计CPLD内部下述电路:15位m序列NRZ码的生成电路;

CMI编码电路;

CMI编码输入的选择电路:周期15位m序列与由周期15位二进制码表示本组内某学号最后四位(前面可补零)分别选择作为CMI编码输入;

CMI译码电路(在实验室条件下使用统一系统时钟,输入为CMI编码输出)。

2.对所做设计完成正确编译。

3.使用仿真环境完成信号波形仿真。

CPLD电路仿真的输入输出信号即各测试点数

信号要求如下:

输入:电路的总复位信号:1路(位);

系统时钟信号(2Mbps):1路;

CMI编码输入的选择信号:1路;

输出:周期15位m序列NRZ码:1路;

周期15位二进制后四位学号:1路;

CMI编码输出信号:1路;

CMI译码输出信号:1路;

4.对仿真信号波形结果进行原理分析,发现可能的问题并加以解决,得到正确的仿真结果。

四、工作原理:

设计电路总图:

该电路由分频,15位学号序列产生,15位m 序列产生,选路部分,CMI编码以及CMI译码六部分组成

1.分频部分:

分频工作通过D触发器完成

2.学号序列产生电路:

采用计数型序列信号发生器,由74LS161计数器和8选1MUX 组合输出网络组成,序列组合码从组合输出网络输出。

采用C Q 置数法来实现,因M=15,有效状态位为0001~1111。

因为学号为050 二进制为:000 0000 0101 0000

由卡诺图可知 QD QC QA 为101时,可输出学号序列。

所以74151中D5接1,其他接0即可。

3.m 序列产生

要产生M=15的m 序列码,确定n=4,查表得反馈函数为41Q Q F ⊕=,在反

馈方程中加全0校正项4321Q Q Q Q ,使m 序列发生器具有自启动性。

4.选路部分

5.CMI编码部分

CMI编码原理图:

CMI码的编码规则是将二值码NRZ序列中的“1”和“0”状态进行分离,然后按各自的编码规则进行编码,最后由这两种状态的编码合成输出就成为CMI码。

根据CMI的编码规则,“1”交替编为“00”“11”;“0”编为“01”。

将所有的“0”求反,再与分频后脉冲序列相乘,则将所有的“0”编为了“01”。

然后,根据JK触发器的特点,其碰到“1”则翻转;碰到“0”则保持的特点,将所有的“1”交替编为“00”和“11”。

最后,合成输出。

编码电路部分:

6.CMI译码部分:

CMI译码原理图:

译码电路中也要有码分离电路,将过来的CMI码流两两分为高位码和低位码,将CMI码的高位与低位取同或,相同则译为“1”,不同则译为“0”。

译码电路部分:

五、实验结果:

通过仿真,可以发现,无论是对学号序列还是m 序列,都能准确的编码和译码。

只是编码和译码都产生一定得延时。