电子元器件应用-CPLD器件的配置与编程下载

第6章CPLD配置讲稿

在FPGA芯片的上述配置引脚上,在MAXPLUSⅡ开 发系统的支持下,就把配置数据写入到FPGA芯片中。

2)被动配置方式。 在这种配置方式下,由外部CPU或控制器(如单片机) 控制配置的过程。

中国矿大 信电学院

FLEXl0K/ EP1K系列器件有五种配置方式:

中国矿大 信电学院

中国矿大 信电学院

CPLD/FPGA器件的工作状态

CPLD/FPGA器件按照正常使用和下载的不同过程其 工作状态分为三种:

EPROM编程的数据文件, 从而可以将并行EPROM作 为数据源, 用微处理器对FLEX器件进行被动串行同步 (PS)配置或被动串行异步(PSA)配置。 ④ ASCII码文本格式(.ttf):

TTF格式文件适用于被动串行同步(PS)配置和被 动串行异步(PSA)配置类型, 它在配置数据之间以逗 号分隔。

中国矿大 信电学院

被动并行异步(PPA)配置方式

FLEX10K器件可以在其内部将每一个字节的配置数据串行 化。当FLEX10K器件准备接收下一个配置数据时,就使 RDYnBSY变高,而单片机检测该高电平信号后,再决定是否 送出下一个字节的配置数据。 同样,nRS信号决定了RDYnBSY信号出现在DATA7上。当nRS 为低时,不允许数据输出到数据总线上,因为那样可能会 在DATA7上引起竞争。如果nRS信号不用,它就必须为高电 平。 PPA方式同样可以用来配置多个FLEX10K器件。 同样,在用单片机来进行PPA配置时,需要对单片机进行恰

CPLD下载(CPLD选择pof文件下载)

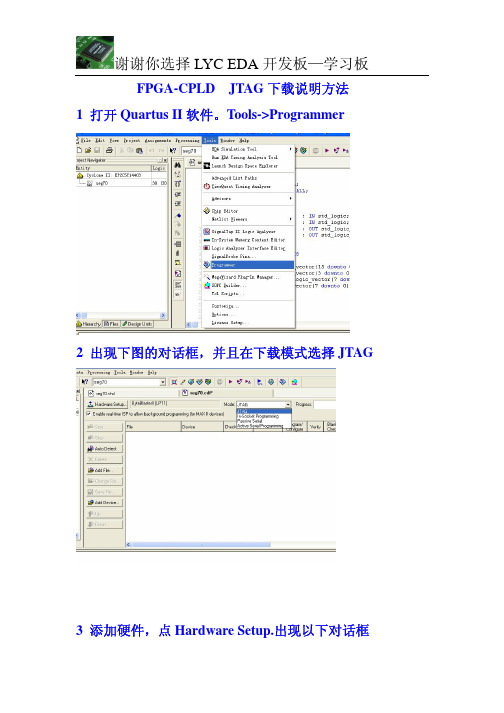

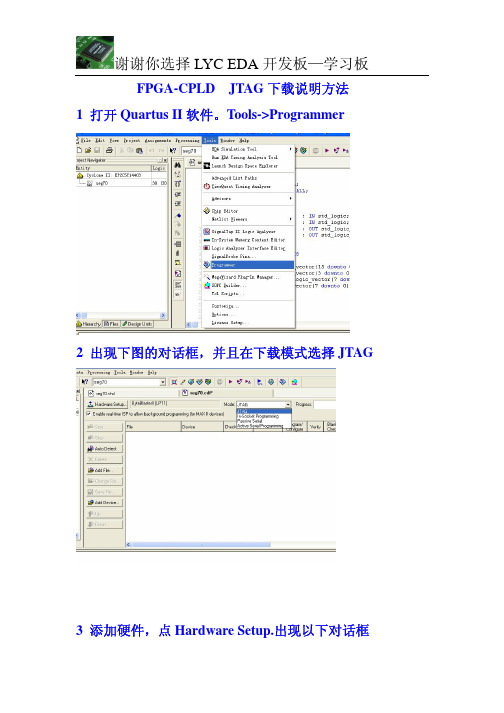

FPGA-CPLD JTAG下载说明方法

1 打开Quartus II软件。

Tools->Programmer

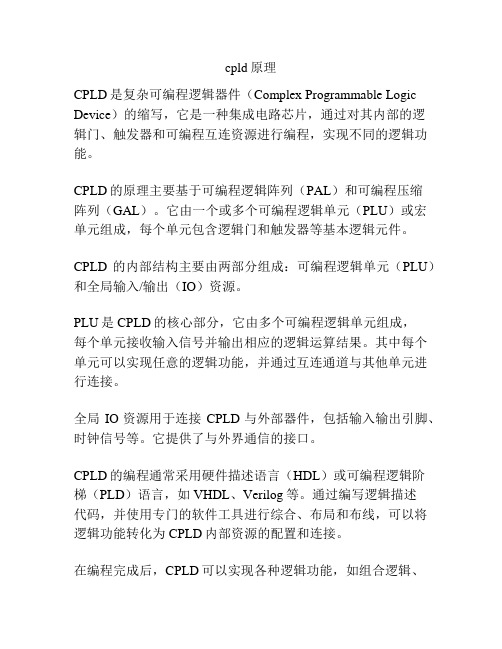

2 出现下图的对话框,并且在下载模式选择JTAG

3 添加硬件,点Hardware Setup.出现以下对话框

根据自己的现在方式。

如我现在用并的ByteBlasterII下载器。

注意:如果你没有看到ByteBlasterII这个选项,说明你的软件没有安装好。

他与硬件没有关系。

4 点Add File 添加要下载的文件,FPGA JTAG下载的是.SOF文件。

如下图: 如果你用的是CPLD开发板,则要下载的是.POF文件.

5 将如下图 Program/Configure打钩。

注意:Device要显示与你的开发板相对应的器件才行,如我们用的是EP2CT144,要显示EP2CT144才是正确的文件。

6点 Start 程序下载中

7下载完毕。

cpld原理

cpld原理

CPLD是复杂可编程逻辑器件(Complex Programmable Logic Device)的缩写,它是一种集成电路芯片,通过对其内部的逻

辑门、触发器和可编程互连资源进行编程,实现不同的逻辑功能。

CPLD的原理主要基于可编程逻辑阵列(PAL)和可编程压缩

阵列(GAL)。

它由一个或多个可编程逻辑单元(PLU)或宏单元组成,每个单元包含逻辑门和触发器等基本逻辑元件。

CPLD的内部结构主要由两部分组成:可编程逻辑单元(PLU)和全局输入/输出(IO)资源。

PLU是CPLD的核心部分,它由多个可编程逻辑单元组成,

每个单元接收输入信号并输出相应的逻辑运算结果。

其中每个单元可以实现任意的逻辑功能,并通过互连通道与其他单元进行连接。

全局IO资源用于连接CPLD与外部器件,包括输入输出引脚、时钟信号等。

它提供了与外界通信的接口。

CPLD的编程通常采用硬件描述语言(HDL)或可编程逻辑阶

梯(PLD)语言,如VHDL、Verilog等。

通过编写逻辑描述

代码,并使用专门的软件工具进行综合、布局和布线,可以将逻辑功能转化为CPLD内部资源的配置和连接。

在编程完成后,CPLD可以实现各种逻辑功能,如组合逻辑、

时序逻辑、状态机等。

它还可以实现多个逻辑块之间的通信和控制,具有较高的灵活性和可扩展性。

总而言之,CPLD原理是通过对其内部逻辑资源进行编程,实

现不同的逻辑功能。

它由可编程逻辑单元和全局IO资源组成,通过编写逻辑描述代码并使用专门的软件工具进行编程,可以实现各种逻辑功能,并与外部器件进行通信和控制。

CPLD下载(CPLD选择pof文件下载)

FPGA-CPLD JTAG下载说明方法

1 打开Quartus II软件。

Tools->Programmer

2 出现下图的对话框,并且在下载模式选择JTAG

3 添加硬件,点Hardware Setup.出现以下对话框

根据自己的现在方式。

如我现在用并的ByteBlasterII下载器。

注意:如果你没有看到ByteBlasterII这个选项,说明你的软件没有安装好。

他与硬件没有关系。

4 点Add File 添加要下载的文件,FPGA JTAG下载的是.SOF文件。

如下图: 如果你用的是CPLD开发板,则要下载的是.POF文件.

5 将如下图 Program/Configure打钩。

注意:Device要显示与你的开发板相对应的器件才行,如我们用的是EP2CT144,要显示EP2CT144才是正确的文件。

6点 Start 程序下载中

7下载完毕。

复杂可编程逻辑器件CPLD

- -进程语句,用a、b信号触发进程执行

MAX

65 64

23

63

24 25

EPM7128SLC84

62 61

26

60

27

59

28

58

29

57

30

56

31

55

32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54

CPU编程数据经过此端口下

GND

I/O.TD0 载到CPLD中旳

暂存数据。 如: VARIABLE a,b:STD_LOGIC;- -定义a,b为原则逻辑位变量

✓信号阐明语句: 信号有IN、OUT、INOUT、BUFFER4种流动方向。分外部端

口和内部信号,其作用是在设计旳单元电路之间实现互连 如:SIGNAL b:BIT; - -定义b为位逻辑型信号

3.变量与信号旳赋值语句

1脚: 全局清零端

2、83脚: 2个全局时钟输入端

VCCIO

GND VCCINT GND VCCIO

取得最高旳工作速度

专用输入脚,不用时不允许悬空,预防CMOS器件输 入击穿损坏。

VCCIO

GND INPUT/GCLK1

INPUT/OE1 INPUT/GCLRn INPUT/OE2/GCVLCCKIN2T

VHDL语言对硬件系统旳描述, 有三种描述方式:行为描述、 数据流描述、构造化描述。

输入端口描述

逻辑关系描述

输出端口描述

实体(ENTITY)描述

构造体 (ARCHITECTURE) 描述

VHDL 程序

库支持: 定义程序中所涉及旳数据类型、元件和子程序等。

ALTERA CPLD器件的配置与下载

ALTERA CPLD器件的配置与下载一、配置方式ALTERA CPLD器件的配置方式主要分为两大类:主动配置方式和被动方式。

主动配置方式由CPLD器件引导配置操作过程,它控制着外部存储器和初始化过程;而被动配置方式由外部计算机或控制器控制配置过程。

根据数据线的多少又可以将CPLD器件配置方式分为并行配置和串行配置两类。

经过不同组合就得到四种配置方式:主动串行配置(AS)、被动串行(PS)、被动并行同步(PPS)、被动并行异步(PPA)。

我们没有必要对每一种配置方式都进行讲述,而是详细地来讲讲我们实验室中经常使用的方式:被动串行配置方式(PS)。

以FLEX10K器件为例,我们首先对PS方式中使用到的引脚有个了解,它的主要配置引脚如下:MSEL1、MSEL0:输入;接地。

nSTATUS:双向漏极开路;命令状态下器件的状态输出。

加电后,FLEX10K立即驱动该引脚到低电位,然后在100ms内释放掉它,nSTATUS必须经过1.0k电阻上拉到Vcc,如果配置中发生错误,FLEX10K将其拉低。

nCONFIG:输入;配置控制输入。

低电位使FLEX10K器件复位,在由低到高的跳变过程中启动配置。

CONF_DONE:双向漏极开路;状态输出。

在配置期间,FLEX10K将其驱动为低。

所有配置数据无误差接收后,FLEX10K将其置为三态,由于有上拉电阻,所以将变为高电平,表示配置成功。

状态输入。

输入高电位引导器件执行初始化过程并进入用户状态。

CONF_DONE 必须经过1.0k电阻上拉到Vcc,而且可以将外电路驱动为低以延时FLEX10K初始化过程。

DCLK:输入;为外部数据源提供时钟。

nCE:输入;FLEX10K器件使能输入,nCE为低时使能配置过程,而且为单片配置时,nCE必须始终为低。

nCEO:输出(专用于多片器件);FLEX10K配置完成后,输出为低。

在多片级联配置时,驱动下一片的nCE端。

DATA0:输入;数据输入,在DATA0引脚上的一位配置数据。

FPGA and CPLD的配置与编程

各种规模的FPGA缺点: 1、电路面积比较大

CPLD和FPGA的编程与配置

10芯下载口 10芯下载口接口各引脚信号名称

引脚 PS 模式 JATG 模式 1 DCK TCK 2 GND GND 3 CONF_DONE TDO 4 VCC VCC 5 nCONFIG TMS 6 7 nSTA TUS 8 9 DATA0 TDI 10 GND GND

EPROM中 放置多个不 同功能的配 置文件

对FPGA进行配置

使用单片机配置FPGA

MCU用PPS模式配置FPGA电路

单片机使用PPS模式配置时序

用89C52进行配置

方案6:PS端口ASIC/CPLD硬件高速配置方案

大容量EPROM

ASIC/CPLD

I/ O 端 口

PS配置端口 DCLK CONF_DONE nCONFIG nSTATUS DATA0

PC机

POF硬件购建配 置文件 Nios工作软件

缺点: 1、只适合于Cyclone系列器件 2、无法用于实时多任务重配 置

方案5:PS端口单片机软件方式配置

EPROM或 串行EEROM

普通单片机

单 片 机 I/ O 端 口

PS配置端口 DCLK CONF_DONE nCONFIG nSTATUS DATA0

Altera公司的FPGA配置方式与器件系列

Altera FPGA常用配置器件

器 件 EPC2 EPC1 EPC1441 EPC1213 EPC1064 EPC1064V 功能描述 1695680×1 位,3.3/5V 供电 1046496×1 位,3.3/5V 供电 440 800×1 位,3.3/5V 供电 212 942×位,5V 供电 65 536×位,5V 供电 65 536×位,5V 供电 封装形式 20 脚 PLCC、32 脚 TQFP 8 脚 PDIP、20 脚 PLCC 8 脚 PDIP、20 脚 PLCC 8 脚 PDIP、20 脚 PLCC、32 脚 TQFP 8 脚 PDIP、20 脚 PLCC、32 脚 TQFP 8 脚 PDIP、20 脚 PLCC、32 脚 TQFP

第6章CPLD配置讲稿

第6章CPLD配置讲稿

用微处理器对FPGA进行PPS方式配置。

l 在PPS方式配置(被动并行同步配置)方式中,从PC机的并口发出编程数 据, nCONFIG引脚被智能主机(如单片机)所控制。

第6章CPLD配置讲稿

JTAG接口

l JTAG接口使用TDI、TDO、TCK、TMS四个管脚。 其中:

l TDI:串行数据输入端, l TDO:串行数据输出端, l TCLK:串行时钟, l TMS:JTAG状态机模式控制端。 l TDI、TDO、TMS的数据在TCLK时钟的配合下,将

数据串行移位到CPLD内部JTAG移位寄存器中。

第6章CPLD配置讲稿

第6章CPLD配置讲稿

第6章CPLD配置讲稿

第6章CPLD配置讲稿

第6章CPLD配置讲稿

第6章CPLD配置讲稿

第6章CPLD配置讲稿

被动串行配置(PS)方式

l 在被动串行配置(PS)方式中,从PC机的串口发出 编程数据,由BitBlaster下载电缆或接口微处理器产 生一个由低到高的跳变送到nCONFIG引脚,然后微 处理器或编程硬件将配置数据送到DATA0引脚,该 数据被琐存,直至CONF_DONE变为高电平。它先 将每字节的最低位LSB送到FPGA器件。

2)被动配置方式。 在这种配置方式下,由外部CPU或控制器(如单片机) 控制配置的过程。

第6章CPLD配置讲稿

FLEXl0K/ EP1K系列器件有五种配置方式:

第6章CPLD配置讲稿

cpld的应用原理

CPLD的应用原理什么是CPLDCPLD(Complex Programmable Logic Device)是一种高度集成的可编程逻辑器件。

它由一系列可编程逻辑单元(PLD)和可编程电路连通网络(Interconnect Network)组成。

CPLD具有较高的逻辑密度和较低的功耗,适用于各种应用领域,如嵌入式系统、通信设备、工业控制等。

CPLD的工作原理CPLD的工作原理是基于可编程逻辑单元(PLD)和可编程电路连通网络(Interconnect Network)的组合。

PLD包括可编程逻辑阵列(PLA)和可编程输入输出(PIO)两部分,用于实现具体的逻辑功能。

而Interconnect Network则负责连接和配置PLD的内部单元。

在CPLD中,逻辑功能是通过编程来实现的。

用户可以使用硬件描述语言(如VHDL或Verilog)来描述所需的逻辑功能,并通过专门的编程软件将描述好的逻辑功能加载到CPLD中。

加载完成后,CPLD即可按照用户的要求进行逻辑运算和数据处理。

CPLD的应用CPLD在各种应用领域都有广泛的应用,下面是一些常见的应用示例:1.嵌入式系统:CPLD可以用于控制、处理和管理嵌入式系统中的各种外围设备,如键盘、显示器、存储器等。

它可以实现数据的输入输出、时序控制、状态切换等功能。

2.通信设备:CPLD可以用于实现通信设备中的各种协议和接口,如串行通信、以太网、USB等。

它可以提供高速数据传输和高质量的信号处理能力。

3.工业控制:CPLD可以用于工业控制系统中的逻辑控制和信号处理。

它可以实现各种输入输出的逻辑运算、信号转换和测量控制,提高系统的可靠性和稳定性。

4.汽车电子:CPLD可以应用于汽车电子控制单元(ECU)中,实现各种车载系统的控制和监测。

它可以处理传感器数据、驱动执行器、协调各个子系统之间的交互等。

5.航空航天:CPLD在航空航天领域有着广泛的应用。

它可以用于飞机系统和卫星系统中的控制和通信,提供高度可靠和高性能的功能实现。

CPLD程序下载作业指导票

CPLD 程序下载作业指导票1、 目的指导CPLD 下载工具作业2、 适用范围CPLD 下载3、 程序要点3.1作业环境配备有电源、电脑、CPLD 下载工具、并口线以及电脑装有相关的程序下载软件。

4、 作业步骤4.1 作业前准备4.1.1打开电源和电脑4.1.3运行Device Propramming 应用程序4.2 固化程序烧入步骤4.2.1连接CPLD 的下载工具; CPLD 的下载工具的并口连至电脑的并口, CPLD 的单排6芯插针通过6芯线 连至PCB 板上的CPLD_JTAG(此处要注意方向)4.2.2将电源线接入主板,并接入电源4.2.3切换到Device Propramming 的界面,在Select Mode 栏选中JTAG Boundary Scan Mode 点击Next ,在Select Chain or File Mode 栏选中Atuomatically connect to cable and indentify boundary_Sdcan4.2.4此时跳出下载程序的一个默认路径,在这里可以选择想要下载的程序(.Jed 格式)4.2.5在XinLinx Impact 点击 “是”4.2.6选中下载图标(呈蓝色),Opertiong 点击 propram 在Propamopertions 里选中Erase Before Propramming 点击“OK ”拟 制审 核标记 数量 更改单号 签名 日期第 1 张 日期 签名 旧底图总号底图总号 媒体编号 格式(4a )描图: 幅面:4.2.7进入编程状态,此处需要几十秒,程序会显示下载的进度,程序下载好,会有下载成功的提示5、 注意事项5.1在程序下载时必须确保主板芯片和下载软件工具设置的芯片型号、晶振频率、存储空间设置一致5.3在程序下载过程中如果发现中途中断,则重新进行程序下载并擦除原先下载的程序5.2在程序下载过程中如有异常,立即断开电源6、 修改履历无拟 制审 核 标记 数量 更改单号签名 日期 第 2 张 日期 签名旧底图总号底图总号媒体编号格式(4a ) 描图: 幅面:。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第七章 CPLD器件的配置与编程下载7.1 概述当利用CPLD/FPGA开发系统完成数字电路或系统的开发设计并仿真校验通过之后,就需要将获得的CPLD/FPGA编程配置数据下载到CPLD/FPGA芯片中,以便最后获得所设计的硬件数字电路或系统,结合着用户的设计需求进行电路功能的硬件调试和应用。

1、器件编程分类:CPLD/FPGA编程配置数据下载的方式有多种,按使用计算机的通讯接口划分,有:串口下载(BitBlaster或MasterBlaster)、并口下载(ByteBlaster)、USB接口下载(MasterBlaster或APU)等方式。

若按使用的CPLD/FPGA器件划分,有:CPLD编程(适用于编程元件为EPROM、E2PROM和闪存的器件);FPGA下载(适用于编程元件为SDRAM的器件)。

若按CPLD/FPGA器件在编程下载过程中的状态划分,有:主动配置方式:在这种配置方式下,由CPLD器件引导配置操作的过程并控制着外部存贮器和初始化过程;被动配置方式:在这种配置方式下,由外部计算机或控制器(如单片机)控制配置的过程。

2、器件的工作状态:CPLD/FPGA器件按照正常使用和下载的不同过程其工作状态分为三种:1、用户状态(User mode)。

即电路中CPLD器件正常工作时的状态;2、配置状态(Configuration),指将编程数据装入CPLD/FPGA器件的过程,也可称之为下载状态;3、初始化状态(Initialization)。

此时CPLD/FPGA器件内部的各类寄存器复位,让I/O引脚为使器件正常工作作好准备。

对于使用Altera公司的CPLD器件的用户来说,若使用的是该公司编程元件为E2PROM或闪存的CPLD器件(如MAX5000、MAX7000、MAX9000系列等),由于这类器件是非易失性的CPLD 器件,所以只需简单的利用专门的下载电缆(ALTERA公司提供有名为ByteBlaster或BitBlaster的编程下载电缆,该电缆可以很容易由用户自行制作获得)将编程配置数据下载到芯片中去即可。

但是对于编程元件为SRAM的FPGA器件(如FLEX6000、 FLEX8000 、FLEX10K、 ACEX1K、 APEX20K系列等),由于这类器件具有编程数据易失性的特性,所以存在一个对于芯片的外部配置的问题,以将编程配置数据永久性的存储在外部的E2PROM或闪存中,供FPGA器件每次在系统通电时调入这些编程配置数据。

否则用户就需要在每次系统通电时都需要利用PC机进行对FPGA器件的编程写入的操作由于对Altera的CPLD/FPGA器件的编程配置操作与该公司的MAX+PLUS II开发系统密切相关,因此在介绍Altera CPLD/FPGA器件的配置与编程技术之前,先介绍MAX+PLUS II 的编程与下载步骤。

7.2 编程下载操作步骤1. 打开编程窗口连上编程器硬件,然后在MAX+PLUS II 菜单中选择Programmer项,打开编程器窗口,如图7-1所示。

图7-1 编程界面2.利用Altera编程器对MAX系列器件进行编程在Option菜单内选择Hardware Setup项,然后在Hardware Type 对话框内选择设定下载电缆的类型,如果下载电缆为ByteBlaster,设定后按下OK即可;如果是BitBlaster 类型还要选择相应的波特率,最后按下OK按钮,如图7-2所示图7-2 下载电缆的选择(1) 在编程器窗口中,检查所选择的编程文件和器件是否正确。

在对MAX系列器件进行编程时,使用的是扩展名是.POF的文件,如果选择的编程文件不正确,可在File菜单中选择Select Programming File命令选择编程文件,如图7-3所示。

图7-3 编程文件的选择(2) 将器件插到编程插座中。

(3) 按下Program按钮,编程器将检查器件,并将你的项目编程到器件中,而且还将检查器件中的内容是否正确。

3.通过JTAG实现在系统编程一个编程目标文件(.pof)可以通过Byteblaster电缆直接编程到器件中,如图7-4所示。

图7-4 通过JTAG接口对CPLD进行编程(1) 编译一个项目,MAX+PLUS II编译器将自动产生用于MAX器件的编程目标文件。

(2) 将Byteblaster电缆的一端与微机的并行口相连,另一端10针阴极头与装有可编程逻辑器件的PCB板上的阳极头插座相连。

该PCB板还必须为Byteblaster电缆提供电源。

(3) 打开MAX+PLUS II编程器(4) 在Option菜单中选择Hardware Setup命令,将出现Hardware Setup窗口 (5) 在下拉条中选择Byteblaster(6) 指定配置时使用的并行口(7) 按下OK按钮4.设置在系统多器件同时编程(1) 在MAX+PLUS II 菜单中选择并打开Programmer项,在JATG菜单中打开Multi—Device JATG Chain 并选择Multi—Device JATG Chain Setup项,进行多个器件的JATG链的设置。

对话框如图7-5所示。

图7-5 利用JTAG链进行多器件同时编程(2) 按下Add按钮。

(3) 选择Select Programming File 并选出编程文件,该框内显示你选择的编程文件。

如果你使用多个器件,重复(2)~(3)步,可确保与你电路板上的顺序相同。

(4) 完成设置后,按下ok按钮。

(5) 按下Program按钮,开始对JATG器件进行编程。

5.利用Byteblaster电缆配置FLEX系列器件可以在MAX+PLUS II中,通过Byteblaster电缆对多个FLEX器件进行在电路配置,过程如下:(1) 首先编译一个项目,MAX+PLUS II编译器将自动为FLEX器件产生一个SRAM目标文件(.pof)。

(2) 将Byteblaster电缆的一端与微机的并行口相连,另一端10针阴极头与装有可编程逻辑器件的PCB板上的阳极头插座相连。

该PCB板还必须为Byteblaster电缆提供电源。

(3) 打开MAX+PLUS II编程器窗口,在Option菜单中选择Hardware Setup命令,在该窗口中选择Byteblaster并设定相应的LPT端口。

(4) 如果只需配置一个FLEX器件,首先检查在编程器窗口中的编程文件和器件是否正确,如果不正确,在File菜单种选择Select Programming File命令来改变编程文件。

(5) 如果需要配置含多个FLEX器件的FLEX链,在FLEX菜单中打开Multi—Device FLEX Chain,然后选择Multi—Device FLEX Chain SETUP。

接着按你电路板上的顺序添加FLEX编程文件。

选定全部文件后,按下OK按钮。

(6) 在编程器窗口中按下Configure按钮。

除此之外,还可以用Multi—Device JATG Chain 来配置多个FLEX器件,也可以用Altera EPROM 或微处理器来配置FLEX器件。

7.3 Altera CPLD器件的配置与下载这里我们以FLEX 10K系列器件为例来说明器件的配置与下载原理及方法。

7.3.1配置类型1、分类在FLEX10K器件正常工作时,它的配置数据贮存在片内SRAM之中。

由于SRAM的易失性,所以每次加电期间,配置数据都必须重新加载。

当器件完成内部初始化之后便进入了用户状态,其各种工作状态的工作波形如图7-6所示:图7-6 器件配制时序图我们将FLEX10K分为以下四种配置方式,如表7.1所示:表7-1 FLEX10K器件的配置方式方式典型应用主动串行(AS) 利用EPC(PROM)配置被动串行(PS) 串行同步CPU接口,Bitblaster等被动并行同步(PPS) 并行同步CPU接口被动并行异步(PPA)并行异步CPU接口2、配置文件大小表7-2总结了各种FLEX10K器件配置文件的大小,如果要配置多个器件,则简单的将这些数据大小相加即得所需配置存储器的容量。

表7-2 FLEX10K器件配置文件的大小3、配置中将用到的引脚在介绍几种配置方式之前,有必要先介绍一下在配置过程中我们要用到的一些引脚,当然这些引脚在不同器件上的引脚号不同,但功能却是相同的。

见表7-34、主动串行配置或EPC1配置方式如图7-7所示,主动串行配置(AS,Active-Serial Configuration)由Altera提供的串行PROM存储芯片EPC1向FLEX10K器件输入串行位流的配置数据。

图7-7 单器件主动配制电气连线图表7-3 FLEX10K器件配置时使用的引脚说明引脚名 状态 配置方式引脚类型 描 述MSELl MSEL0 所有 输入OO:AS或PS, 10:PPSll:PPAnSTATUS 所有双向漏极开路命令状态下器件的状态输出位。

加电后,FLEXl0K立即驱动该引脚到低电平,约100 ms后释放,nSTATUS必须经过1.0K 电阻上拉到Vcc,如果配置中发生错误,CPLD/FPGA器件将其拉低nCONFIG 所有 输入 配置控制输入。

低电平使FLEXl0K器件复位,在由低变高的跳变过程中启动配制。

CONF_DONE 所有 双向漏极开路 状态输出:在配置期间,为低。

所有配置数据无误差接收后为三态。

状态输入:输入高电平引导器件执行初始化过程并进入用户状态。

CONF—DONE必须经由1.0 K的上拉电阻至Vcc,而且可以将外电路驱动为低以延时FLEX 10K初始化过程。

DCLK AS,PSPPS输入 由外部数据源提供时钟。

nCE 所有 输入 FLEXl0K器件使能输入。

nCE为低时使能配置过程。

单片配置时,nCE必须为低。

nCEO 用于多片器件 输出 FLEXl0K器件配置完成后,输出为低,在多片级连配置时,取得下一片的nCE端nWS I/O PPA 输入 写选通输入。

由低变高的跳变时锁存DATA[7..0]引脚上的字节数据。

,nRS I/0 PPA 输入 读选通输入。

低输入时引导FLEXl0K器件将 RDYnBSY信号置于 DATA7引脚。

当nRS不用时,必须将其置为高 RDYnBSY I/O PPA 输出 输出就绪信号。

输出为高时,表示FLEXl0K器件已经准备接收另外一个字节数据,而输出为低时表示还没准备好,尚无法接收数据。

nCS CS I/O PPA 输入 片选输入。

当nCS输入为低且CS输入为高时,选择某一个FLEX10K配置。

如果只用其中一个片选信号。

那么另一个必须接到有效电平(例如当使用CS时,nCS可以接地)CLKUSR I/O 所有 输入 可选的用户时钟输入。