CPU 指令大全

CPU常用操作指令

CPU常用操作指令汇编语言是一种低级别的计算机程序语言,用于直接控制和操作计算机的中央处理器(CPU)。

在编写汇编语言程序时,需要使用一系列的操作指令来完成各种任务。

下面是一些常用的CPU操作指令及其功能的汇编语言示例。

1.MOV:将数据从一个位置传输到另一个位置。

示例:MOVAX,BX;将BX寄存器的内容传送到AX寄存器2.ADD/SUB:进行加法或减法操作。

示例:ADDAX,BX;将BX寄存器的内容加到AX寄存器SUBAX,BX;从AX寄存器中减去BX寄存器的内容3.INC/DEC:将操作数的值增加或减少1示例:INCAX;将AX寄存器的值增加1DECBX;将BX寄存器的值减少14.CMP:比较两个操作数的值,设置标志寄存器的状态以供条件跳转指令使用。

示例:CMPAX,BX;比较AX和BX寄存器的值5.JMP:无条件跳转到指定地址。

6.JE/JNE:根据标志寄存器的状态,执行条件跳转。

7.AND/OR/XOR:进行逻辑与、逻辑或或逻辑异或操作。

示例:ANDAX,BX;将AX和BX寄存器的值进行逻辑与操作ORAX,BX;将AX和BX寄存器的值进行逻辑或操作XORAX,BX;将AX和BX寄存器的值进行逻辑异或操作8.PUSH/POP:将数据压入栈或从栈中弹出数据。

示例:PUSHAX;将AX寄存器的值压入栈中POPBX;从栈中弹出数据,并将其存入BX寄存器9.CALL/RET:调用子程序或从子程序返回。

示例:CALL subroutine ; 调用名为"subroutine"的子程序RET;从子程序返回到调用位置10.INT:触发中断。

示例:INTn;触发编号为n的中断这些是一些常用的CPU操作指令的示例,每个指令都有具体的功能和用法。

在汇编语言编程中,根据具体的需求选择合适的指令来完成要求的任务。

因为汇编语言直接与硬件进行交互,所以熟悉这些操作指令对于理解和优化程序性能非常重要。

IntelCPU的CPUID指令(三)

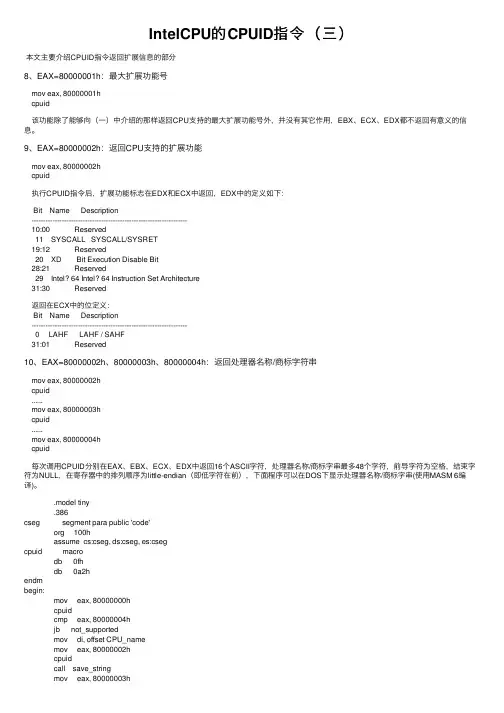

IntelCPU的CPUID指令(三)本⽂主要介绍CPUID指令返回扩展信息的部分8、EAX=80000001h:最⼤扩展功能号mov eax, 80000001hcpuid该功能除了能够向(⼀)中介绍的那样返回CPU⽀持的最⼤扩展功能号外,并没有其它作⽤,EBX、ECX、EDX都不返回有意义的信息。

9、EAX=80000002h:返回CPU⽀持的扩展功能mov eax, 80000002hcpuid执⾏CPUID指令后,扩展功能标志在EDX和ECX中返回,EDX中的定义如下:Bit Name Description-------------------------------------------------------------------10:00 Reserved11 SYSCALL SYSCALL/SYSRET19:12 Reserved20 XD Bit Execution Disable Bit28:21 Reserved29 Intel? 64 Intel? 64 Instruction Set Architecture31:30 Reserved返回在ECX中的位定义:Bit Name Description-------------------------------------------------------------------0 LAHF LAHF / SAHF31:01 Reserved10、EAX=80000002h、80000003h、80000004h:返回处理器名称/商标字符串mov eax, 80000002hcpuid......mov eax, 80000003hcpuid......mov eax, 80000004hcpuid每次调⽤CPUID分别在EAX、EBX、ECX、EDX中返回16个ASCII字符,处理器名称/商标字串最多48个字符,前导字符为空格,结束字符为NULL,在寄存器中的排列顺序为little-endian(即低字符在前),下⾯程序可以在DOS下显⽰处理器名称/商标字串(使⽤MASM 6编译)。

cpuinfo命令 cpuid level

cpuinfo命令 cpuid levelC P U ID L e v e l指的是C P U I D指令返回的信息中的一个字段,用于指示C P U支持的特定功能和功能级别。

本文将详细介绍CP U I D指令和CP U I DL e v e l的概念以及它们在计算机系统中的作用。

第一部分:C P U I D指令的介绍C P U I D指令是一条用于向CP U请求特定信息的指令,在x86架构的处理器中广泛使用。

它通常用于获取处理器的相关信息,如制造商、型号、插槽类型、支持的功能等。

C P U I D指令的格式为"C P U I D(E A X,E C X)",其中E A X和E C X是输入寄存器,用于指定查询的信息类别和子类别。

执行C P U I D指令后,处理器会将返回值存放在E A X、E B X、E C X和ED X这四个输出寄存器中。

第二部分:C P U I D L e v e l的概念C P U ID L e v e l是C P U I D指令返回的信息中的一个字段,用于指示C P U支持的特定功能和功能级别。

具体来说,C P U I D L e v e l字段标识了C P U支持的最高功能级别,即支持的最大子类别。

不同的C P U支持不同的功能和功能级别,在CP U I DL e v e l字段的值可以方便地确定C P U的支持能力。

第三部分:C P U I D L e v e l的解读C P U ID L e v e l字段的值以二进制形式表示,每一位都代表了一个具体的功能或功能级别。

例如,第0位表示第一个功能,第1位表示第二个功能,以此类推。

如果某一位上为1,表示该C P U支持对应的功能;如果某一位上为0,则表示该C P U不支持对应的功能。

第四部分:C P U I D L e v e l的应用C P U ID L e v e l对于操作系统和应用程序开发人员非常重要。

8086CPU指令和伪指令(中英文全解)

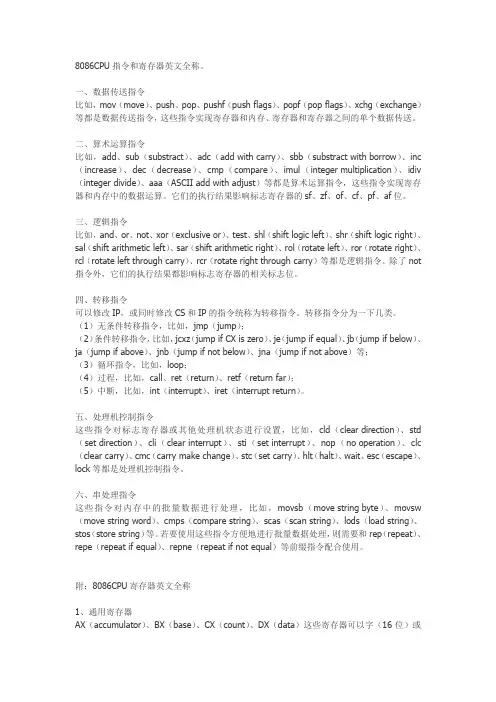

8086CPU指令和寄存器英文全称。

一、数据传送指令比如,mov(move)、push、pop、pushf(push flags)、popf(pop flags)、xchg(exchange)等都是数据传送指令,这些指令实现寄存器和内存、寄存器和寄存器之间的单个数据传送。

二、算术运算指令比如,add、sub(substract)、adc(add with carry)、sbb(substract with borrow)、inc (increase)、dec(decrease)、cmp(compare)、imul(integer multiplication)、idiv (integer divide)、aaa(ASCII add with adjust)等都是算术运算指令,这些指令实现寄存器和内存中的数据运算。

它们的执行结果影响标志寄存器的sf、zf、of、cf、pf、af位。

三、逻辑指令比如,and、or、not、xor(exclusive or)、test、shl(shift logic left)、shr(shift logic right)、sal(shift arithmetic left)、sar(shift arithmetic right)、rol(rotate left)、ror(rotate right)、rcl(rotate left through carry)、rcr(rotate right through carry)等都是逻辑指令。

除了not 指令外,它们的执行结果都影响标志寄存器的相关标志位。

四、转移指令可以修改IP,或同时修改CS和IP的指令统称为转移指令。

转移指令分为一下几类。

(1)无条件转移指令,比如,jmp(jump);(2)条件转移指令,比如,jcxz(jump if CX is zero)、je(jump if equal)、jb(jump if below)、ja(jump if above)、jnb(jump if not below)、jna(jump if not above)等;(3)循环指令,比如,loop;(4)过程,比如,call、ret(return)、retf(return far);(5)中断,比如,int(interrupt)、iret(interrupt return)。

中央处理器操作指令

工作过程

提取 解码

执行 写回

第一阶段,提取,从存储器或高速缓冲存储器中检索指令(为数值或一系列数值)。由程序计数器 (Program Counter)指定存储器的位置。(程序计数器保存供识别程序位置的数值。换言之,程序计数器记录了 CPU在程序里的踪迹。)

CPU根据存储器提取到的指令来决定其执行行为。在解码阶段,指令被拆解为有意义的片段。根据CPU的指令 集架构(ISA)定义将数值解译为指令。一部分的指令数值为运算码(Opcode),其指示要进行哪些运算。其它 的数值通常供给指令必要的信息,诸如一个加法(Addition)运算的运算目标。

基本概念

中央处理器(CPU,Central Processing Unit)是一块超大规模的集成电路,是一台计算机的运算核心 (Core)和控制核心( Control Unit)。它的功能主要是解释计算机指令以及处理计算机软件中的数据。

中央处理器主要包括运算器(算术逻辑运算单元,ALU,Arithmetic Logic Unit)和高速缓冲存储器 (Cache)及实现它们之间的数据(Data)、控制及状态的总线(Bus)。它与内部存储器(Memory)和输入/输 出(I/O)设备合称为电子计算机三大核心部件。

中央处理器操作指令

计算机操作系统

01 基本概念

03 工作过程

目录

02 处理指令流程 04 CPU指令集

中央处理器(CPU,Central Processing Unit)是一块超大规模的集成电路,是一台计算机的运算核心 (Core)和控制核心( Control Unit)。CPU操作指令的处理流程大概分为:取指、译码、执行、访存、写回 等几步。

取指 (fetch)

02

cpu空闲时执行的指令

cpu空闲时执行的指令

当CPU空闲时,执行的指令取决于操作系统的策略和系统负载情况。

以下是一些可能的执行指令:

1.等待中断:操作系统会让CPU处于空闲状态,以等待外部设备的中断信号。

当有中断请求时,CPU将会跳转到相应的中断处理程序。

2.执行空闲循环:操作系统可能会让CPU执行空闲循环,以节约能量并保持CPU的状态。

3.运行后台任务:操作系统可以利用CPU空闲时间来执行一些较低优先级的后台任务,例如垃圾回收、磁盘清理等。

4.进行预取:操作系统可以使CPU预取未来可能执行的指令,以加快系统响应速度。

5.睡眠:如果CPU长时间得不到使用,操作系统可以将其置于睡眠状态,以降低功耗并延长硬件寿命。

CPU常用操作指令

CPU常用操作指令CPU常用操作指令是指在汇编语言中使用的一些常见的指令,用于完成各种任务和操作。

这些指令可以用于数据传输、算术运算、逻辑运算、条件分支等各种操作。

下面我将列举一些常见的CPU操作指令,并介绍它们的用途和示例。

1.MOV指令:用于将数据从一个地方移动到另一个地方。

例如,将一个寄存器中的值移动到另一个寄存器中,或将一个内存单元中的值移动到一个寄存器中。

示例:MOVAX,BX;将BX中的值移动到AX中MOV[BX],10;将值10存储到BX所指向的内存单元中2.ADD指令:用于执行整数的加法操作。

可以将两个寄存器中的值相加,或将一个寄存器中的值与一个立即数相加。

示例:ADDAX,BX;将AX和BX中的值相加,并将结果存储到AX中ADDAX,10;将AX中的值与10相加,并将结果存储到AX中3.SUB指令:用于执行整数的减法操作。

可以将两个寄存器中的值相减,或将一个寄存器中的值与一个立即数相减。

示例:SUBAX,BX;将AX和BX中的值相减,并将结果存储到AX中SUBAX,10;将AX中的值减去10,并将结果存储到AX中4.MUL指令:用于执行无符号整数的乘法操作。

可以将一个寄存器中的值与另一个寄存器中的值相乘,并将结果存储到两个乘积寄存器中。

示例:MOVAX,10;将值10存储到AX中MOVBX,5;将值5存储到BX中MULBX;将AX中的值与BX中的值相乘,并将结果存储到AX和DX中5.DIV指令:用于执行无符号整数的除法操作。

可以将一个寄存器中的值与另一个寄存器中的值相除,并将商存储到一个寄存器中,余数存储到另一个寄存器中。

示例:MOVAX,20;将值20存储到AX中MOVBX,5;将值5存储到BX中DIVBX;将AX中的值除以BX中的值,并将商存储到AX中,余数存储到DX中6.AND指令:用于执行逻辑与操作。

可以将一个寄存器中的值与另一个寄存器中的值进行逻辑与运算,并将结果存储到一个寄存器中。

pdp1cpu指令集

pdp1cpu指令集PDP-1 CPU指令集PDP-1(Programmed Data Processor-1)是由Digital Equipment Corporation(DEC)于1960年开发的一台早期计算机。

它是DEC 推出的第一款商用计算机,也是世界上第一款成功销售的小型计算机之一。

PDP-1采用了16位字长,具有基本的CPU指令集。

以下是PDP-1 CPU指令集的详细介绍:I. 数据传输指令1. TAD(Transfer and Add):将一个内存地址处的值与累加器中的内容相加,并将结果存储回累加器。

2. DCA(Deposit and Clear Accumulator):将累加器中的值存储到一个内存地址处,并清除累加器。

3. ISZ(Increment and Skip if Zero):将一个内存地址处的值加一,并检查结果是否为零。

如果为零,则跳过下一条指令。

4. JMS(Jump to Subroutine):将当前程序计数器(PC)存储到一个内存地址处,并跳转到指定子程序。

II. 算术运算指令1. ADD(Add):将一个内存地址处的值与累加器中的内容相加,并将结果存储回累加器。

2. SUB(Subtract):将一个内存地址处的值从累加器中减去,并将结果存储回累加器。

3. MUL(Multiply):将一个内存地址处的值与累加器中的内容相乘,并将结果存储回累加器。

4. DIV(Divide):将一个内存地址处的值除以累加器中的内容,并将商存储回累加器。

III. 逻辑运算指令1. AND(Logical AND):将一个内存地址处的值与累加器中的内容进行逻辑与操作,并将结果存储回累加器。

2. OR(Logical OR):将一个内存地址处的值与累加器中的内容进行逻辑或操作,并将结果存储回累加器。

3. XOR(Exclusive OR):将一个内存地址处的值与累加器中的内容进行异或操作,并将结果存储回累加器。

CPU指令集

现今的电脑可以说已经非常普及,而CPU作为电脑不可或缺的核心硬件,就像人类的大脑一样,为电脑用户的日常使用提供了强大的处理能力,但对于这个至关重要的硬件许多用户并不十分了解,在以前的文章中,小编曾经介绍过一些关于CPU的知识,帮助许多刚接触电脑的用户更深层了解CPU,今天小编继续对CPU的另一个知识点——指令集进行介绍,彻底解析CPU所有参数含义。

1.MMX指令集1997年Inter公司推出了多媒体扩展指令集(MMX),其包括57条多媒体指令,MMX指令主要用于增强CPU对多媒体信息的处理能力,提高CPU处理3D 图形、视频和音频信息的能力。

2.SSE指令集早期的MMX指令并没有带来3D游戏性能的显著提升,因此于1999年Inter 公司在Pentium III CPU产品中推出了数据流单指令序列扩展指令(SSE)。

SSE 兼容MMX指令,可以通过SIMD(单指令多数据技术)和单时钟周期并行处理多个浮点进行有效地提高浮点运算速度,并且SSE指令寄存器可以全速运行,保证了与浮点运算的并行性。

3.SSE2指令集在奔腾4 CPU时代,Inter公司开发了新指令集SSE2,SSE2指令一共144条,包括浮点SIMD指令、整形SIMD指令、SIMD浮点和整形数据之间转换、数据在MMX寄存器中转换等几大部分,其中的重要改进包括引入新的数据格式,更好地利用了高速缓,并允许程序员控制已经缓存过的数据。

4.SSE3指令集SSE3指令集相对于SSE2,新增加了13条新指令,早期该系列指令集被统称为pni(prescott new instructions)。

SSE3指令集中的13条指令,一条用于视频解码,两条用于线程同步,其余用于复杂的数学运算、浮点到整数转换和SIMD 浮点运算。

5.SSE4指令集SSE4相对于以前的指令集,新增加了50条新的增加性能的指令,这些指令有助于编译、媒体、字符/文本处理和程序指向加速,SSE4指令集支持Clear Video 技术(CVT)与统一显示接口(UDI)支持等。

Intel系列CPU指令速查手册

21 /r

AND WORD Ptr [EA], AX

AND r/m32,r32

21 /r

AND DWORD Ptr [EA], EAX

AND r8,r/m8

22 /r

ANDAL, [EA]

AND r16,r/m16

23 /r

AND AX, [EA]

AND r32,r/m32

ADC r/m32,imm8

83 /2 ib

ADC DWORD Ptr [EA], 39

ADC r/m8,r8

10 /r

ADC [EA], AL

ADC r/m16,r16

11 /r

ADC [EA], AX

ADC r/m32,r32

11 / r

ADC [EA], EAX

ADC r8,r/m8

12 /r

减法后的ASCII码调整AL

AAS

ADC

ADC AL, imm8

14 ib

设置AF CF OF SF PF ZF

带进位加法

ADCAL,1F

ADC AX, imm16

15 iw

ADC AX,4F80

ADC EAX, imm32

15 id

ADC EAX,00004F80

ADC r/m8, imm8

80 /2 ib

E8 cd

子程序调用(32位相对寻址)

CALL r/m16

FF /2

子程序调用(16位间接寻址)

CALL r/m32

FF /2

子程序调用(32位间接寻址)

CALL ptr16:16

9Acd

子程序调用(直接绝对寻址)

CALL ptr16:32

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IntelSSE:SSE是指令集的简称,它包括70条指令,其中包含单指令多数据浮点计算、以及额外的SIMD整数和高速缓存控制指令。

其优势包括:更高分辨率的图像浏览和处理、高质量音频、MPEG2视频、同时MPEG2加解密;语音识别占用更少CPU资源;更高精度和更快响应速度。

SSE(Streaming SIMD Extensions)是英特尔在AMD的3D Now!发布一年之后,在其计算机芯片Pentium III中引入的指令集,是MMX的超集。

AMD后来在Athlon XP中加入了对这个指令集的支持。

这个指令集增加了对8个128位寄存器XMM0-XMM7的支持,每个寄存器可以存储4个单精度浮点数。

使用这些寄存器的程序必须使用FXSAVE和FXRSTR指令来保持和恢复状态。

但是在Pentium III对SSE的实现中,浮点数寄存器又一次被新的指令集占用了,但是这一次切换运算模式不是必要的了,只是SSE和浮点数指令不能同时进入CPU的处理线而已。

SSE2是Intel在P4的最初版本中引入的,但是AMD后来在Opteron 和Athlon 64中也加入了对它的支持。

这个指令集添加了对64位双精度浮点数的支持,以及对整型数据的支持,也就是说这个指令集中所有的MMX指令都是多余的了,同时也避免了占用浮点数寄存器。

这个指令集还增加了对CPU的缓存的控制指令。

AMD对它的扩展增加了8个XMM寄存器,但是需要切换到64位模式(AMD64)才可以使用这些寄存器。

Intel后来在其EM64T架构中也增加了对AMD64的支持。

SSE3是Intel在P4的Prescott版中引入的指令集,AMD在Athlon 64的第五个版本中也添加了对它的支持。

这个指令集扩展的指令包含寄存器的局部位之间的运算,例如高位和低位之间的加减运算;浮点数到整数的转换,以及对超线程技术的支持。

SSE4指令集将给英特尔下一代平台带来“相当大的视频性能提升”。

,其它视频增强技术还包括CVT(明晰视频技术)--英特尔对ATI Avivo的回应--和对UDI的支持。

上述两项技术基于英特尔965芯片组。

其它英特尔官方文件把CVT技术定义为:支持高级解码、拥有预处理和增强型3D 处理能力。

SSE4指令集是Conroe架构所引入的新指令集。

这项原本计划应用于NetBurst微架构Tejas核心处理器之上的全新技术也随着它的夭折最终没能实现,这不能不说是个遗憾,但是SSE4指令集出现在了Conroe上又让我们看到了希望。

SSE4指令集共包括16条指令,不过虽然扣肉处理器推出已经有一些时日,但目前英特尔仍没有公布SSE4指令集的具体资料。

这相当令人感到纳闷。

也许英特尔是基于特殊的考虑,仅让少数合作软件厂商取得数据,只是这种作法实在很没有说服力就是了,天底下没有哪家处理器厂商,希望自己新增的指令越少人用越好。

不过,从Intel Core微架构针对SSE指令所作出的修改被称之为“Intel Advanced Digital Media Boost”技术来看,未来SSE4将更注重针对视频方面的优化,我们认为SSE4主要改进之处可能将针对英特尔的Clear Video高清视频技术及UDI接口规范提供强有力的支持。

这两项技术基于965芯片组,Intel的官方把Clear Video技术定义为:支持高级解码、拥有预处理和增强型3D处理能力。

值得一提的是,在SSE4中另一个重要的改进就是提供完整128位宽的SSE执行单元,一个频率周期内可执行一个128位SSE指令。

Conroe中SSE的ADDPS(4D 32bit共128bit,单精度加法)、MULPS(4D 32bit共128bit,单精度乘法)和SSE2的ADDPD(2D 64bit共128bit,双精度加法)、MULPD(2D 64bit共128bit,双精度乘法),这四条重要SSE算术指令的吞吐周期都降低到1个周期,真正做到了英特尔宣称的每个周期执行一条128位向量加法指令和一条128位向量乘法指令的能力。

可以说 Conroe的向量单元已经全面引入了流水线化的设计。

而支持SSE3的NetBurst微处理器架构虽然提供128位宽执行单元,但仅有一组,性能孰高孰低一目了然。

更为重要的是,目前已经有相当多的软件针对SSE指令集进行了优化,其中包括2D制图、3D制图、视频播放、音频播放、文件压缩等方面,可见其应用范围相当广泛。

配合完整的128位SSE执行单元,以及庞大的执行单元数目,Conroe处理器可在一个频率周期内,同时执行128位乘法、128位加法、128位数据加载与128位数据回存,或着是4个32位单倍浮点精确度乘法与4个32位单倍浮点精确度加法运算,这将使其更利于多媒体应用。

因此,SSE4指令集能够有效带来系统性能上的提升,这一代在众多测试中早已被证实。

虽然其不会像当年SSE2指令集出现时那样带来巨大的性能提升,但是其在某些特殊方面的应用还是让我们对它充满了期待。

编辑本段后续版本SSE2SSE2是Intel在Pentium 4处理器的最初版本中引入的,但是AMD后来在Opteron 和Athlon 64处理器中也加入了SSE2的支持。

SSE2指令集添加了对64位双精度浮点数的支持,以及对整型数据的支持,也就是说这个指令集中所有的MMX指令都是多余的了,同时也避免了占用浮点数寄存器。

这个指令集还增加了对CPU快取的控制指令。

AMD对它的扩展增加了8个XMM寄存器,但是需要切换到64位模式(AMD64)才可以使用这些寄存器。

Intel后来在其EM64T架构中也增加了对AMD64的支持。

SSE3SSE3是Intel在Pentium 4处理器的 Prescott 核心中引入的第三代SIMD指令集,AMD在Athlon 64的第五个版本,Venice核心中也加入了SSE3的支持。

这个指令集扩展的指令包含寄存器的局部位之间的运算,例如高位和低位之间的加减运算;浮点数到整数的转换,以及对超执行绪技术的支持。

SSSE3SSSE3是Intel针对SSE3指令集的一次额外扩充,最早内建于Core 2 Duo处理器中。

SSE4SSE4是Intel在Penryn核心的Core 2 Duo与Core 2 Solo处理器时,新增的47条新多媒体指令集,并且现在更新至SSE4.2。

AMD也开发了属于自己的SSE4a多媒体指令集,并内建在Phenom 与Opteron等K10架构处理器中,不过无法与Intel的SSE4系列指令集相容。

SSE5SSE5]是AMD为了打破Intel垄断在处理器指令集的独霸地位所提出的,SSE5初期规划将加入超过100条新指令,其中最引人注目的就是三算子指令(3-Operand Instructions)及熔合乘法累积(Fused Multiply Accumulate)。

其中,三算子指令让处理器可将一个数学或逻辑函式库,套用到算子或输入资料。

借由增加算子的数量,一个 x86 指令能处理二至三笔资料, SSE5 允许将多个简单指令汇整成一个指令,达到更有效率的指令处理模式。

提升为三运算指令的运算能力,是少数 RISC 架构的水平。

熔合乘法累积让允许建立新的指令,有效率地执行各种复杂的运算。

熔合乘法累积可结合乘法与加法运算,透过单一指令执行多笔重复计算。

透过简化程式码,让系统能迅速执行绘图着色、快速相片着色、音场音效,以及复杂向量演算等效能密集的应用作业。

SSE5最快将内建于AMD下一代Bulldozer核心。

AVXAVX是Intel的SSE延伸架构,如IA16至IA32般的把暂存器XMM 128bit提升至YMM 256bit,以增加一倍的运算效率。

此架构支持了三运算指令(3-Operand Instructions),减少在编码上需要先复制才能运算的动作。

在微码部分使用了LES LDS这两少用的指令作为延伸指令Prefix。

FMAFMA是Intel的AVX扩充指令集,如名称上熔合乘法累积(Fused Multiply Accumulate)的意思一样。

intel的EM64T内存扩展技术EM64T本质上和AMD64一样都是IA-32的增强版本,Xeon借助于EM64T可实现高达1TB (40bit)的物理内存寻址和256TB(48bit)的虚拟内存寻址,并且良好地支持现有32位x86代码的执行,这一点跟AMD64无异,同时也是Intel开发EM64T的出发点—让现有的x86指令集能够执行64位代码,而继续保持对32位代码的良好兼容。

但由于多方面的限制,无论是EM64T还是AMD64均只能实现比32位指令集更大内存空间的寻址,而无法真正做到纯64位指令集的1PB (50bit)和16EB(64bit)的物理内存和虚拟内存寻址(IA-64就能做到这一点),其关键在于EM64T和AMD64本质上仍是基于32位的x86指令集,只是Intel和AMD分别采用不同的技术手段对x86指令集进行扩展,从而实现对64位的支持。

VT-xVT-x是intel运用Virtualization虚拟化技术中的一个指令集。

VT-x有助于提高基于软件的虚拟化解决方案的灵活性与稳定性。

通过按照纯软件虚拟化的要求消除虚拟机监视器(VMM)代表客户操作系统来听取、中断与执行特定指令的需要,不仅能够有效减少 VMM 干预,还为 VMM 与客户操作系统之间的传输平台控制提供了有力的硬件支持,这样在需要 VMM干预时,将实现更加快速、可靠和安全的切换。

此外,英特尔VT-x 具备的虚拟机迁移特性还可为您的 IT 投资提供有力保护,并进一步提高故障切换、负载均衡、灾难恢复和维护的灵活性。

AVX2倍浮点运算性能Intel全新的发展战略也表明,从2010年开始软件和新指令也将有更好的兼容,而SIMD 浮点运算并非决定因素,所以CPU的性能就变得更加困难。

而性能增强的同时,SIMD浮点运算在已有编码的基础上也必须会有更大的提升空间,特别是scalar整数运算部分。

目前单线程整数运算性能的提升也遇到了瓶颈,本次IDF展会上,确定了这一CPU开发方向的同时也表明了技术的进化趋势。

AMD 3DNOW由AMD公司提出的3Dnow!指令集应该说出现在SSE指令集之前,并被AMD广泛应用于其k6-2 、k6-3以及Athlon(k7)处理器上。

3Dnow!指令集技术其实就是21条机器码的扩展指令集。

3Dnow似乎与MMX同出一辙,但是两者的用途不完全相同。

MMX侧重于整数运算,因而主要用于图形绘描.数据压缩.音频处理等应用场合。

而 3Dnow侧重于浮点运算,因而主要针对三维建模.坐标变换.效果渲染.等三维应用场合。

3Dnow指令不但以SIMD方式运行,而且可以再两个暂存器的执行通道内以一个时钟周期同时执行两个 3Dnow指令的方式运行,即每个时钟周期可执行四个浮点运算。